Urządzenia techniki komputerowej

Chipset’y

komputerów

- podział, funkcje,

rodzaje

Uczeń powinien umieć:

•

wymienić funkcje chipset’ów,

• narysować z czego składa się chipset

i za co odpowiadają poszczególne

jego części,

• podać przykłady chipset’ów

stosowanych obecnie

Komputery PC pierwszej generacji składały się z procesora oraz sporej

liczby układów scalonych, z których każdy realizował pewien fragment

architektury. W miarę rozwoju technologii mikroelektronicznej, funkcje

poszczególnych bloków wchłaniane były przez układy scalone wyższej

generacji. Proces ten osiągnął w chwili obecnej, iż w chwili obecnej

takie stadium, że na płycie głównej montuje się oprócz samego

procesora nie więcej niż dwa układy scalone bardzo wysokiej skali

integracji oraz kilka chipów pomocniczych.

Omawiane układy wysokiej skali integracji nazywamy

chipset

’ami

lub układami otoczenia procesora (umożliwiają komunikację procesora

z innymi komponentami komputera PC).

Funkcje chipse’tów

• sprzężenie z procesorem nazywane magistralą FSB (Front Side Bus),

• realizacja kontrolera pamięci operacyjnej i obsługa magistrali

pamięciowej,

• sterowanie pamięcią podręczna L2 (lub L3) instalowanej na płytach

obsługujących procesory generacji 586 i wyższe,

• implementacja magistral PCI, AGP, ISA, itp.,

• integracja większości bloków architektury PC: kontrolera przerwań,

układów DMA, złączy szeregowych i równoległych, złącza Game

Port, magistral IDE i E-IDE, kontrolera klawiatury, kontrolera

dysków elastycznych oraz kolejnych rozszerzeń takich jak: USB,

IrDA, 1394 itd. Niektóre chipsety zawierają w swoim wnętrzu

również zegar czasu rzeczywistego.

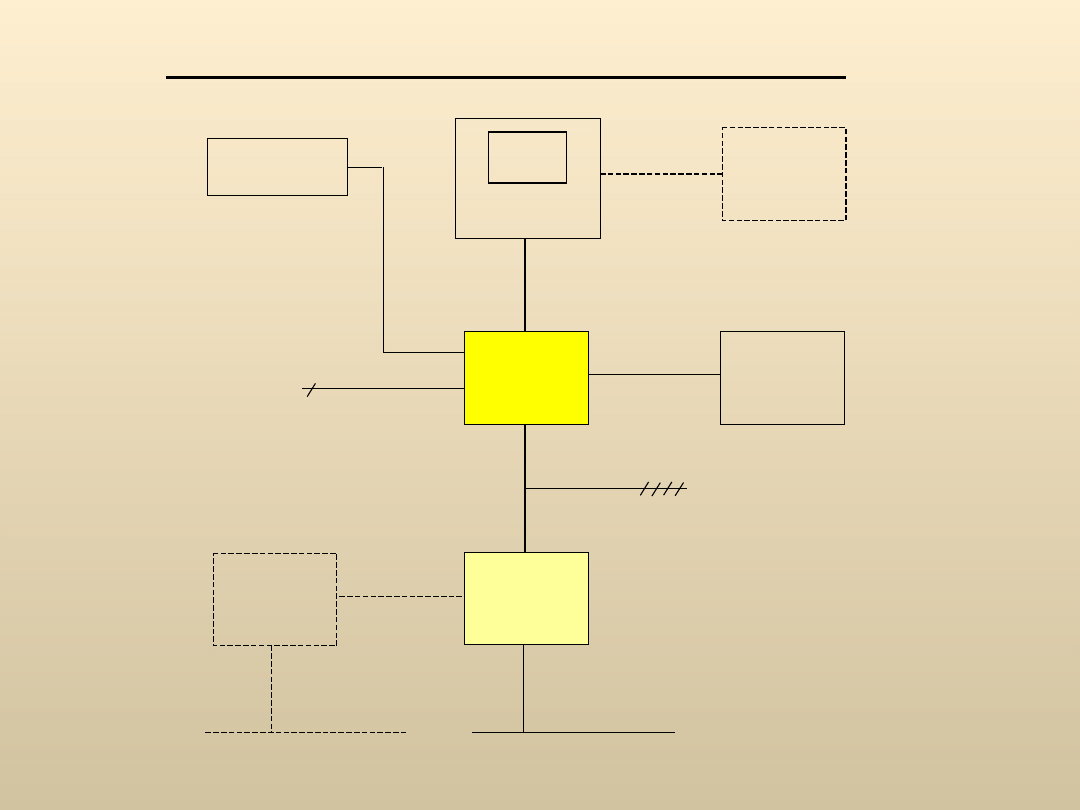

Schemat funkcjonalny chipset’u

CPU

North

Bridg

e

L1

FSB

Memor

y

Memory

Bus

AGP

L2 on

Chip

L2 on

Board

South

Bridg

e

PCI

I/O

ISA, EIDE,USB, Keyb, Ser, Par,

FireWire

Centralnym punktem zestawu jest układ, do którego podłącza się

procesor (North Bridge, Host Bridge lub CPU Bridge). Pamięć L1

zawarta jest przeważnie we wnętrzu struktury półprzewodnikowej

procesora i taktowana z jego pełną częstotliwością zegarową.

Lokalizacja pamięci podręcznej L2 zależy od typu procesora może być

ona osadzona na module, tak jak miało to miejsce w procesorach

Intel Pentium II/III lub AMD K6-III, lub w samej strukturze procesora

(Intel Pentium IV i AMD Athlon). Dodatkowo płyty klasy 586

dysponują z reguły pamięcią podręczną L2, więc jeśli instalowany jest

procesor zawierający własną pamięć L2, cache na płycie przechodzi

do poziomu L3. Z punktu widzenia systemu operacyjnego i aplikacji

nic się przy tym nie zmienia, bowiem obsługa pamięci podręcznych

przebiega na poziomie sprzętu. Dostęp do L2 na płytach odbywa się

za pośrednictwem magistrali FSB i w takt jej zegara. Dostęp do

zintegrowanej w obrębie procesora pamięci L2 może przebiegać z pełną

częstotliwością taktowania CPU (np. Intel Celeron, niektóre P III),

połową tej częstotliwości (P II, niektóre P III) lub jej ułamkiem (Athlon).

Drugi człon chipset’u realizuje większość funkcji pomocniczych

i nazywany jest South Bridge (ISA/IDE Bridge). Początkowo zawierał

w sobie tylko punkty przyłączeniowe dla magistral PCI i ISA. Układy

scalone ostatniej generacji pozwoliły na integrację większości złączy I/O.

Implementacja magistrali PCI zawarta jest w układzie North Bridge

i wyprowadzana najczęściej z wewnętrznej szyny łączącej ze sobą człony

North Bridge i South Bridge.

Magistrala FSB

Częstotliwość taktowania magistrali FSB odzwierciedla w pewnym

stopniu poziom rozwoju technologii samych procesorów. Pierwsze

modele Pentium 75 MHz przystosowane były do pracy z magistralą

50 MHz, a obecnie sprzedawane procesory AMD Barton pracują

z magistrala 166 MHz, Intel Pentium IV mają możliwość pracy nawet

z magistralą 200 MHz.

Manipulacje zegarem FSB znajdują swe odbicie nie tylko w prędkości

samego CPU. Częstotliwość ta stanowi także bazę dla przebiegów

sterujących magistrale PCI i AGP. Zegar magistrali PCI pozyskuje się

z podzielenia FSB. Magistrala PCI pracuje zawsze synchronicznie z FSB,

z wszelkimi tego skutkami. Również magistrala FSB pobiera swoją

bazową częstotliwość taktowania z szyny FSB. Z początku była ona

pobierana 1:1, obecnie również musi być dzielona.

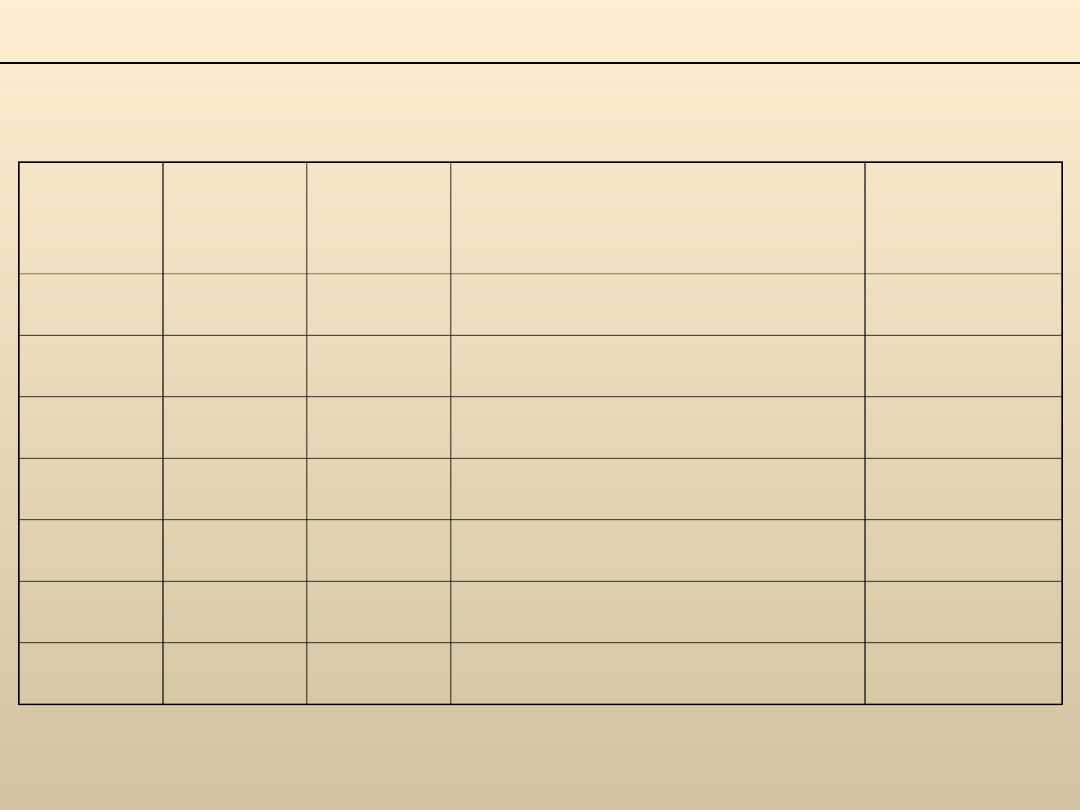

Efekt podnoszenia częstotliwości magistrali w chipsecie Intel 440BX

FSB

PCI

AGP

Magistrala

pamięciowa

ISA/EID

E

50

25

- (50)

50

6,2

66,7

33,3

66,7

66,7

8,3

75

37,5

75

75

9,4

83

41,5

83

83

10,4

100

33,3

66,7

100

8,3

112

37,5

74,7

112

9,3

133

44,3

88,7

133

11,1

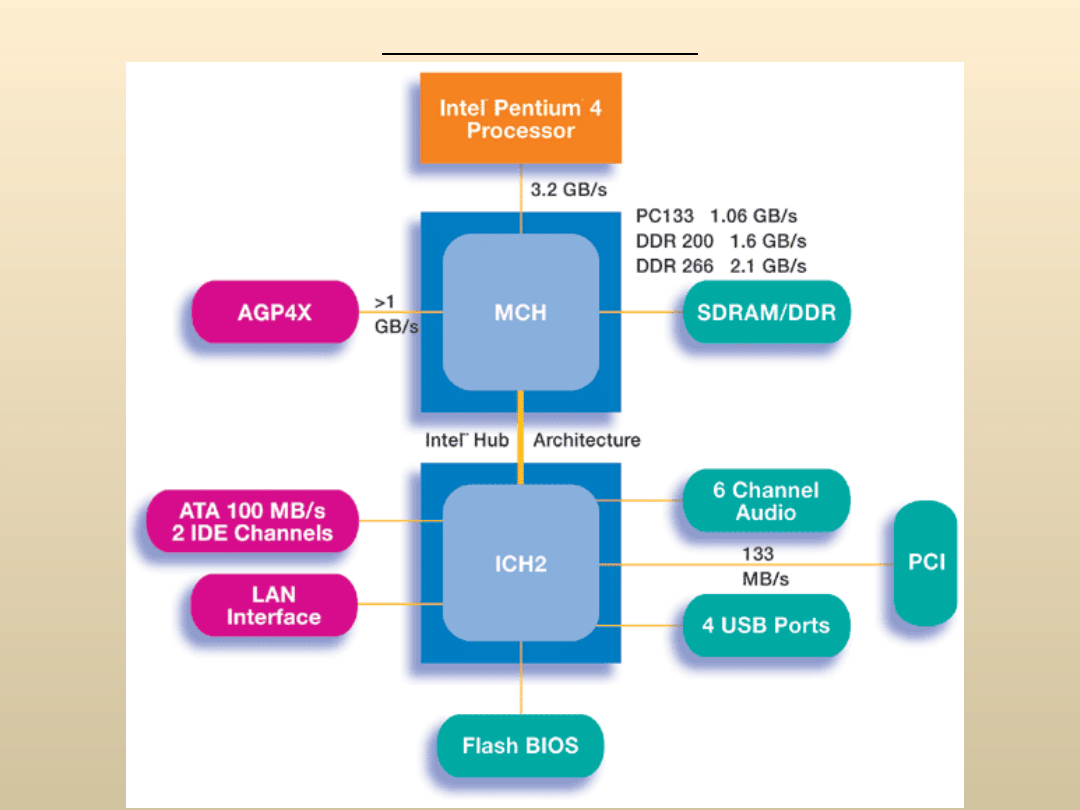

Chipset Intel 845

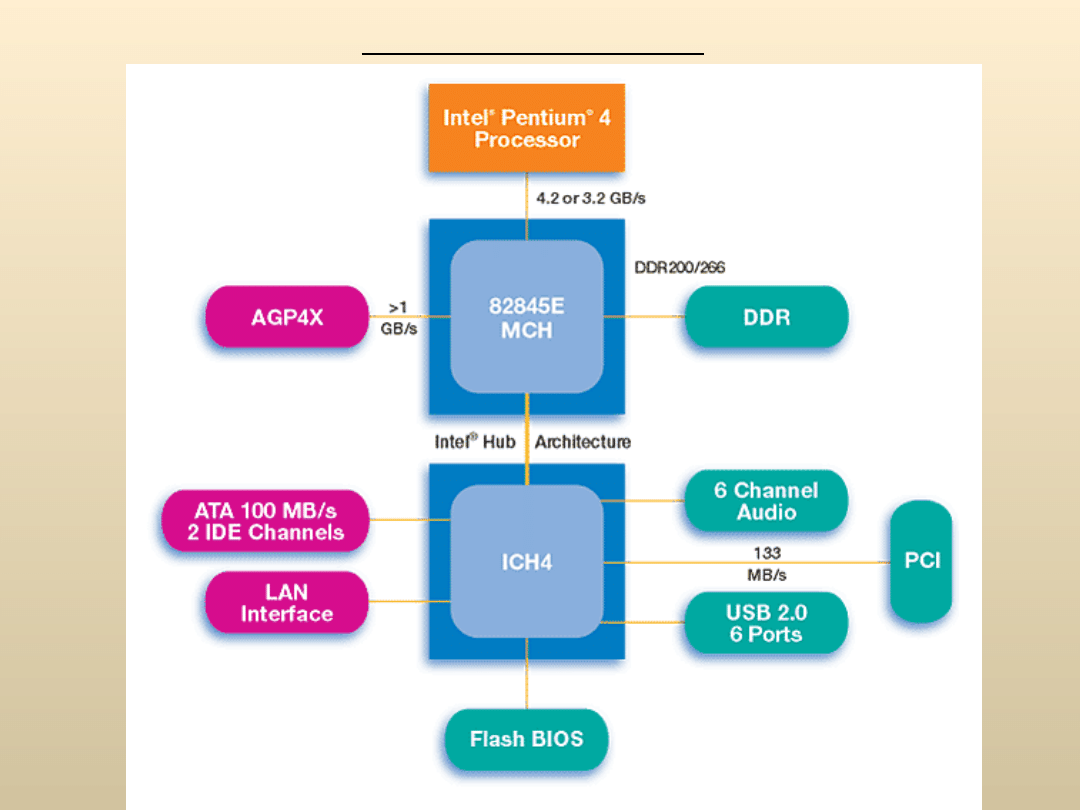

Chipset Intel 845E

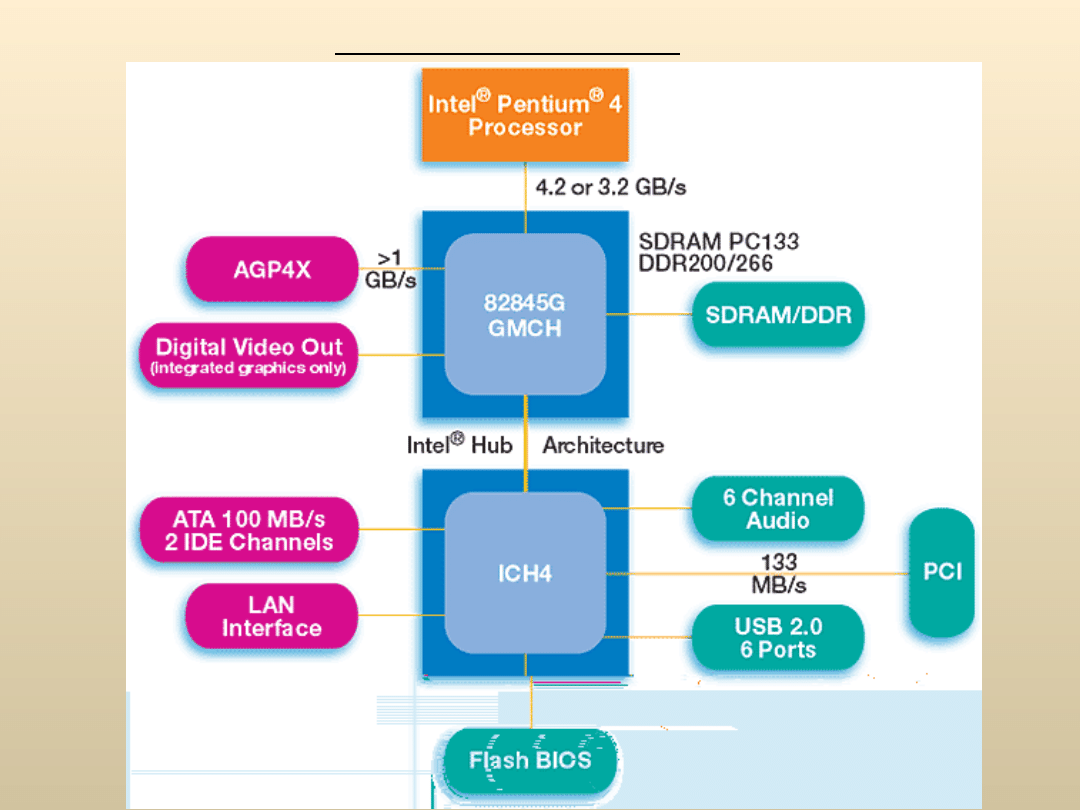

Chipset Intel 845G

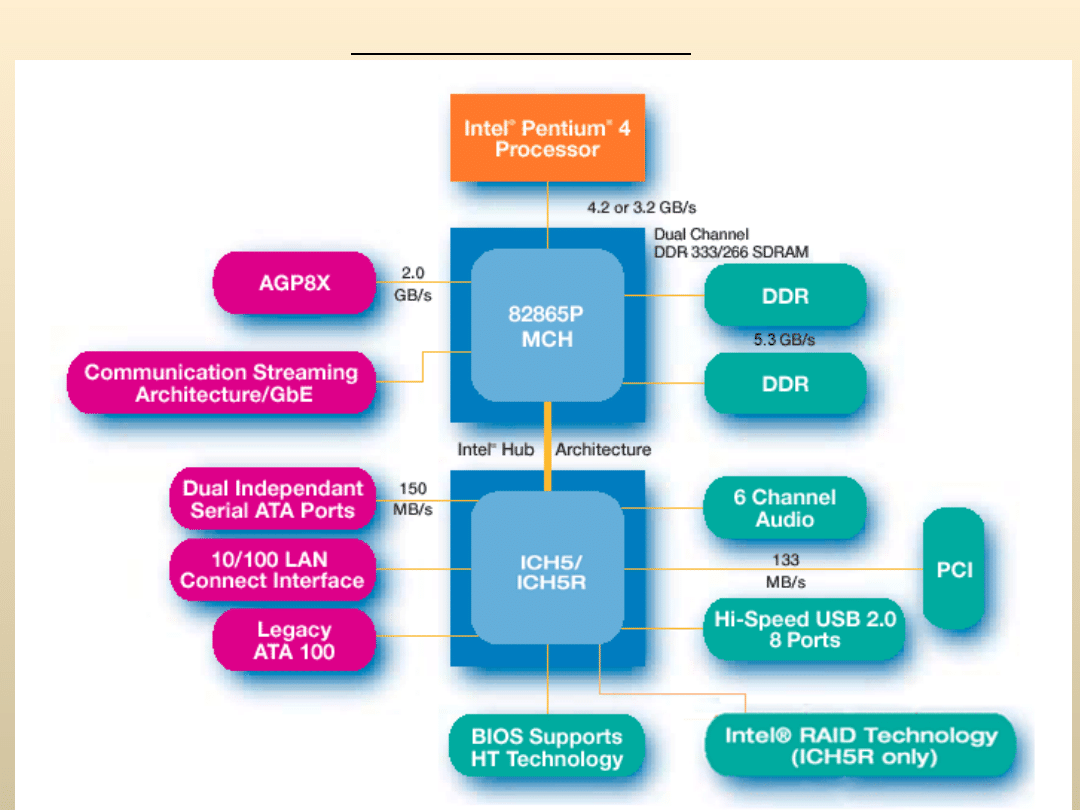

Chipset Intel 865P

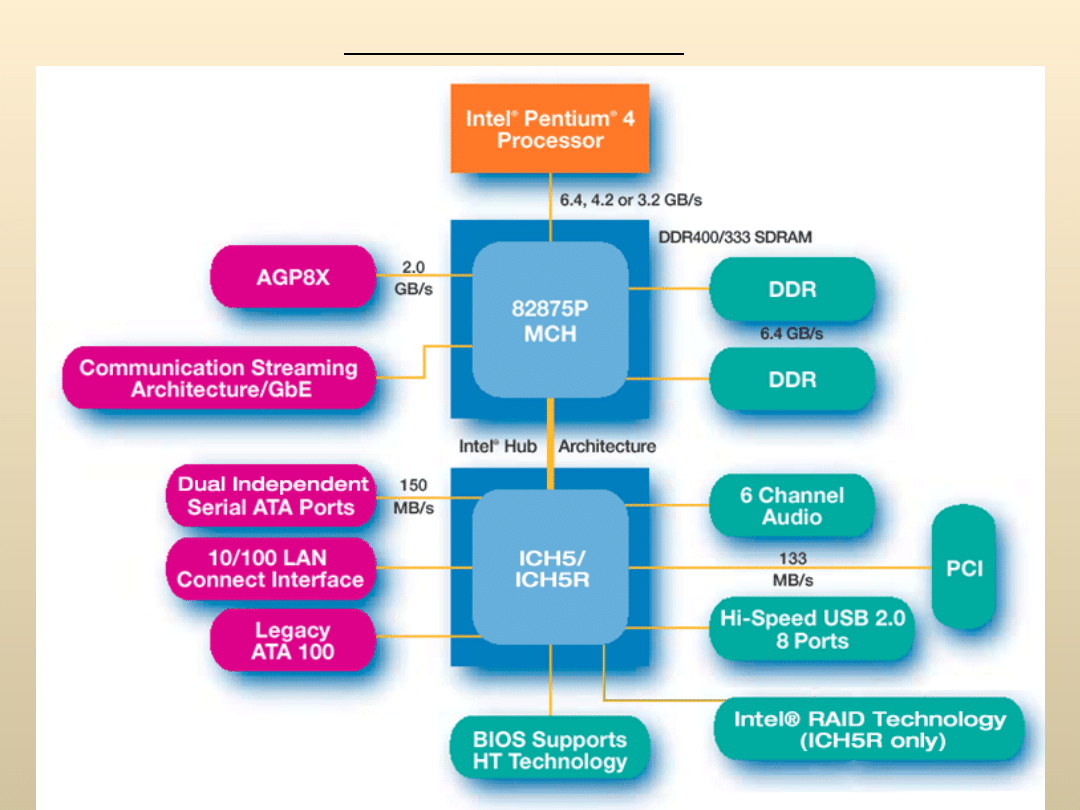

Chipset Intel 875P

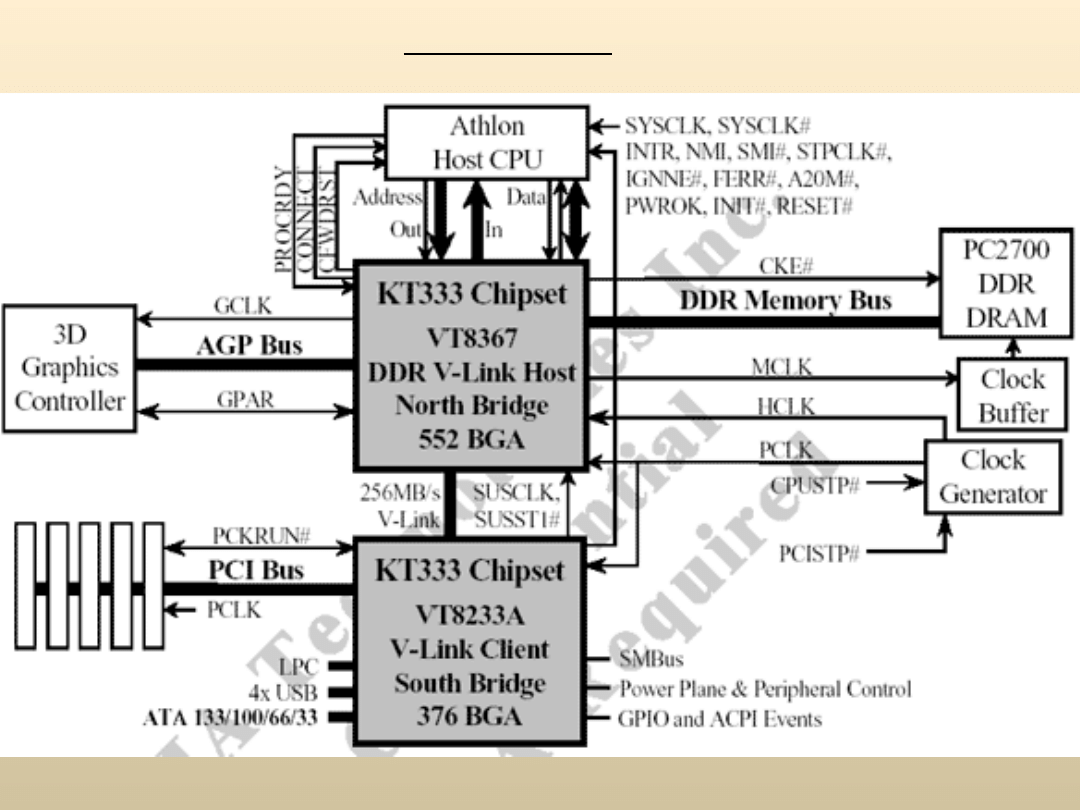

VIA KT 333

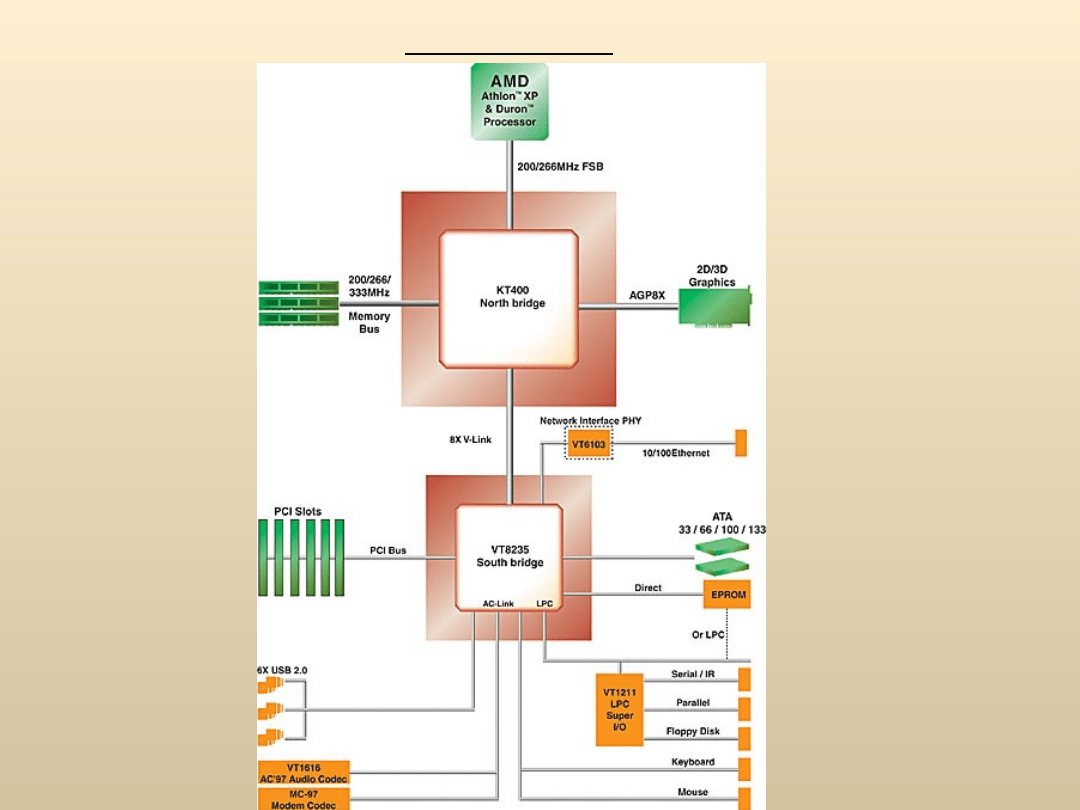

VIA KT 400

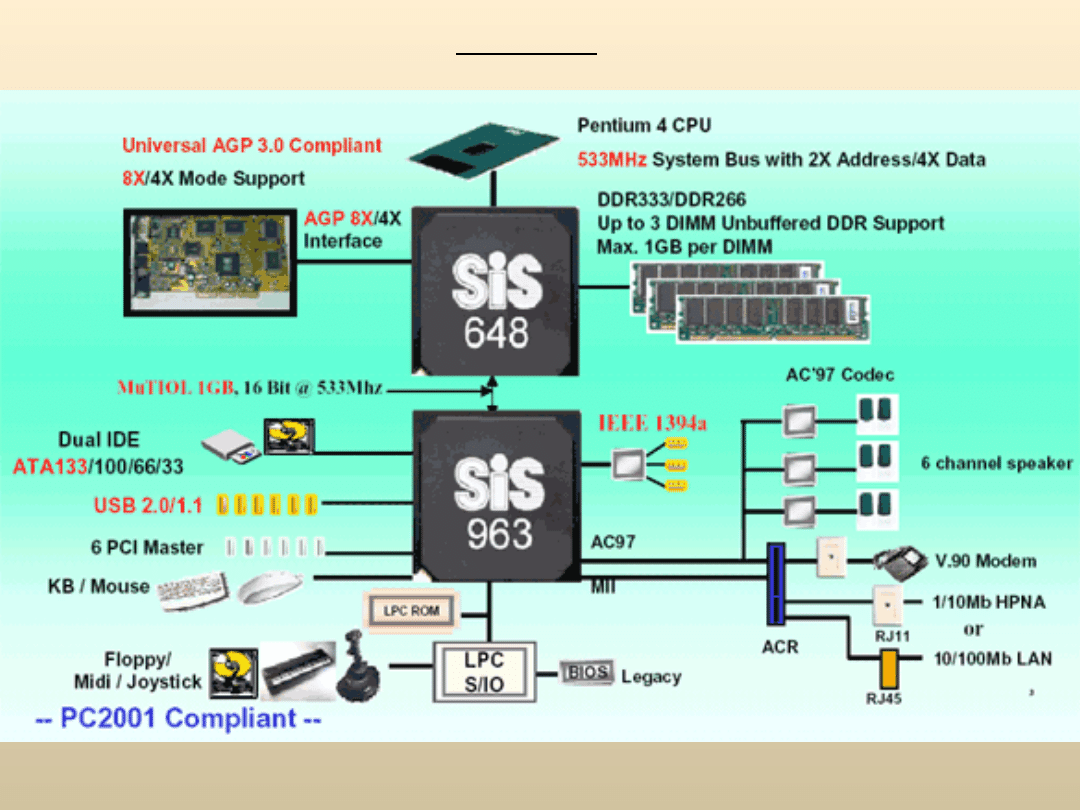

SiS 648

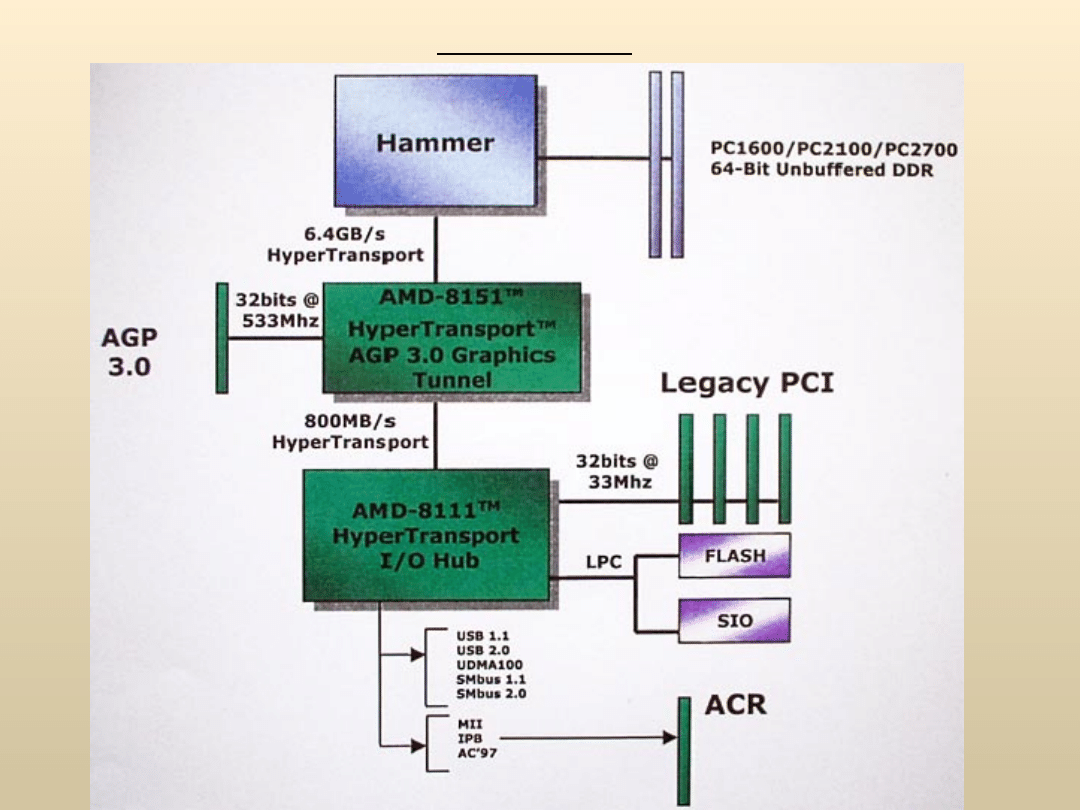

AMD 8000

Document Outline

- Slide 1

- Slide 2

- Slide 3

- Slide 4

- Slide 5

- Slide 6

- Slide 7

- Slide 8

- Slide 9

- Slide 10

- Slide 11

- Slide 12

- Slide 13

- Slide 14

- Slide 15

- Slide 16

- Slide 17

- Slide 18

Wyszukiwarka

Podobne podstrony:

funkcje i rodzaje celów w organizacji, zarzadzanie

PODZIAŁ FUNKCJONALNY MIĘŚNI

Miasto pojęcie, funkcje i rodzaje(1)

fazy procesu pamieciowego, funkcje i rodzaje pamieci1[1]

ORGANIZACJE MIĘDZYNARODOWE pojęcie, podział, funkcje

Strofika, dominanty kompoycyjne, kryteria podziału na rodzaje literackie

mięśnie podział funkcjonalny, fizjoterapia, anatonia

funkcje i rodzaje podręczników, Teoretyczne Podstawy Kształcenia

5 Pojęcie i klasyfikacja kosztów. Koszty w układzie funkcjonalnym i rodzajowym, Materiały - technik

Akcje - funkcje i rodzaje

podział na rodzaje i gatunki literackie, Język polski - opracowanie epok, pojęć i lektur

Akcje - funkcje i rodzaje, Testy

FUNKCJE I RODZAJE CEL W W O, Inne

pojęcie funkcje i rodzaje papierów wartościowych, [Finanse]

36.Cukry - podzial i funkcje, Notatki AWF, Biochemia

funkcje i rodzaje?lów w organizacji

więcej podobnych podstron