Teoria układów logicznych

Dekoder. Demultiplekser

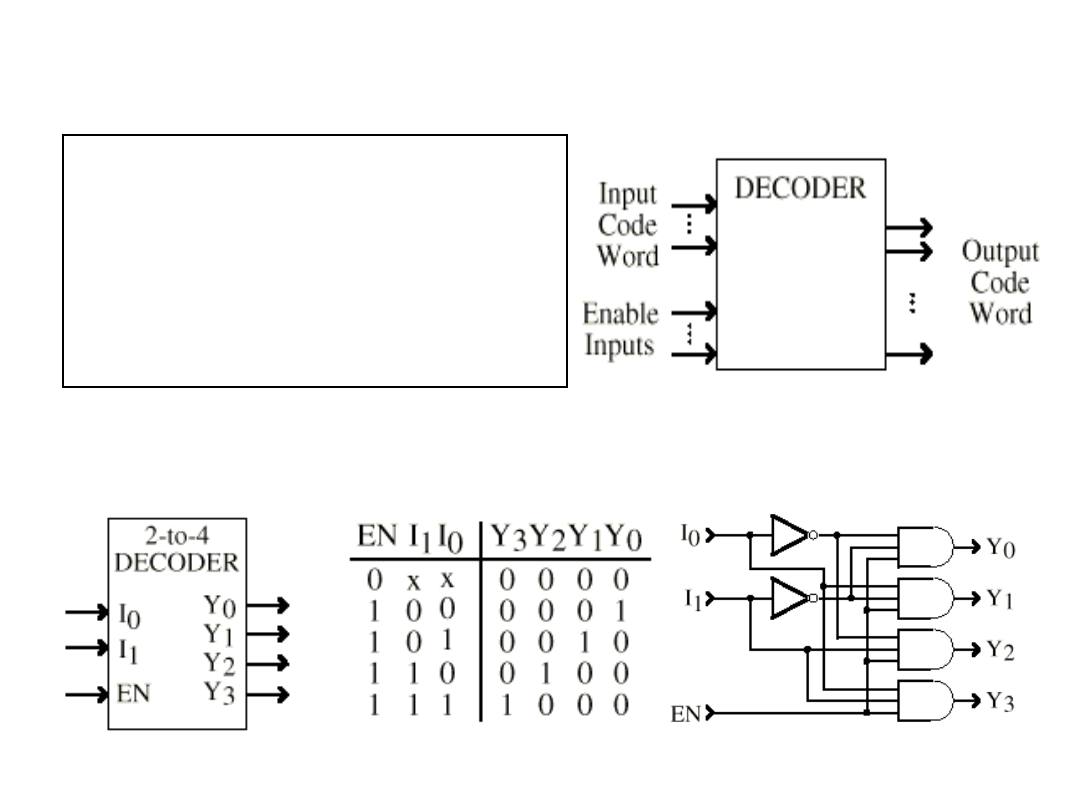

Dekoder jest elementem logicznym

służącym do zmiany jednego kodu na inny.

Dekodery oprócz sygnałów wejściowych i

wyjściowych mogą posiadać jeszcze sygnały

sterujące ( Enable ).

•Jeżeli którekolwiek z wejść sterujących jest

nieaktywne, to wszystkie wyjścia przyjmują

wartość niezależnie od stanu wejść.

Multiplekser jest to dekoder który dla każdej binarnej wartości wejściowej

uaktywnia jedną linię wyjściową. Dla m wejść posiada 2

m

wyjść.

Teoria układów logicznych

Demultiplekser zastosowania.

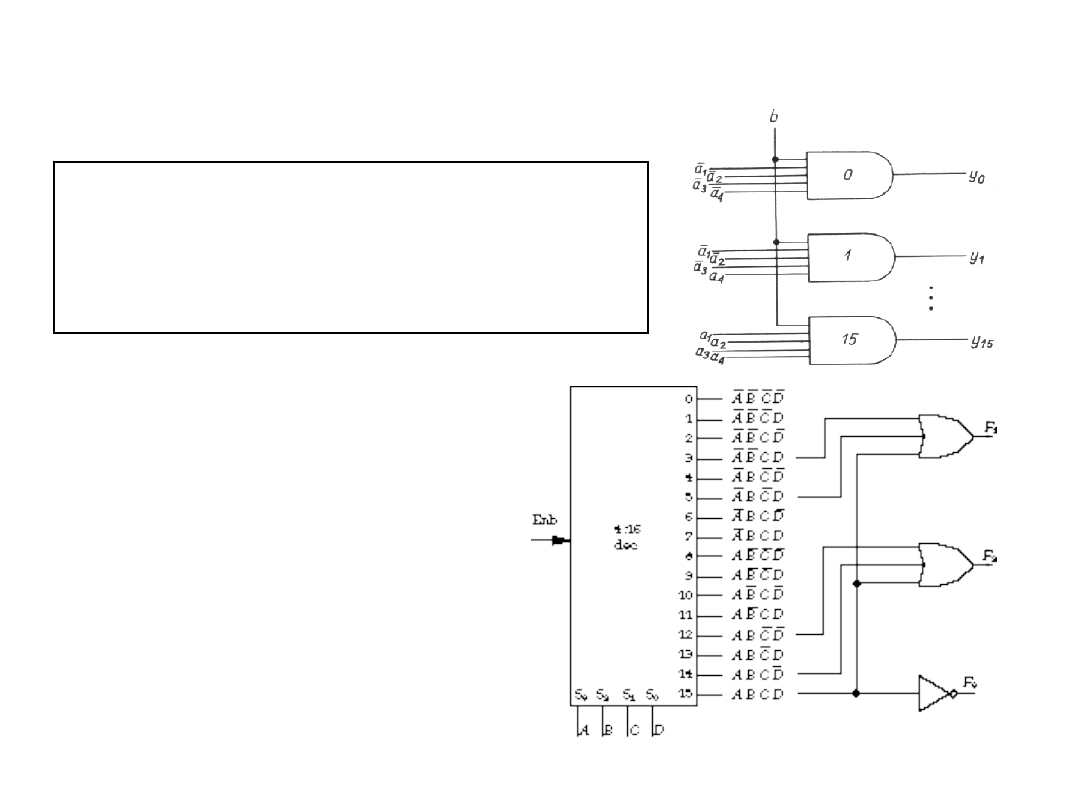

Sposób realizacji dekodera na przykładzie dekodera 4 linii

( a1, a2, a4, a4 ) wejściowych na 16 wyjściowych (y0 ... y15).

•Każdy sygnał wyjściowy jest aktywowany przez odpowiedni

minterm wybranego wektora wejściowego

•sygnał enable ( b ) bramkuje dodatkowo ( sygnałem 0 )

wszystkie wyjścia.

Realizacja funkcji logicznych przy

pomocy demultipleksera.

F1(A,B,C,D)=A’BC’D+A’B’CD.+ABCD

F2(A,B,C,D)=ABC’D’+ABC

F3(A,B,C,D)=A’+B’+C’+D’

Teoria układów logicznych

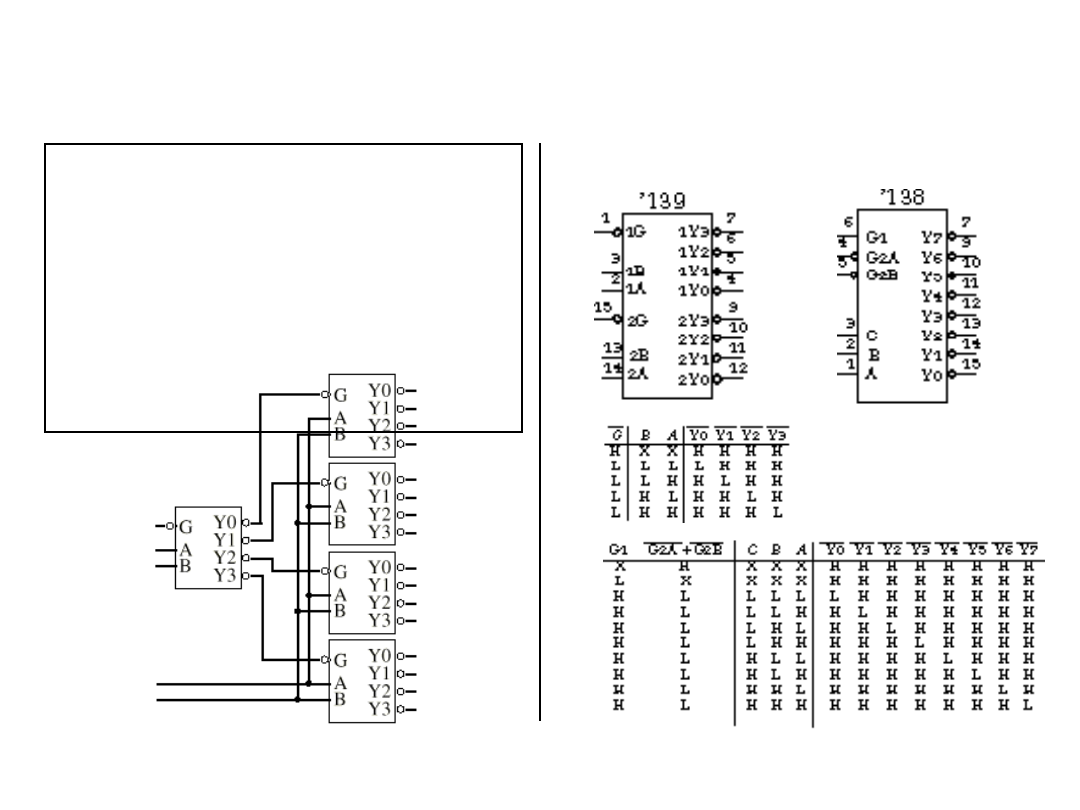

Demultiplekser: kaskadowanie, ‘138, ‘139

Praktycznie spotykane układy demultiplekserów

Możliwe jest kaskadowanie

demultiplekserów.

Przy pomocy 5 demultiplekserów 2 na 4

budujemy demultiplekser 4 na 16.

•linie sterujące pierwszego

demultipleksera tworzą starsze bity

numeru wybranego wyjścia

•linie sterujące pozostałych

demultiplekserów są połączone ze sobą

tworząc bity młodsze.

Teoria układów logicznych

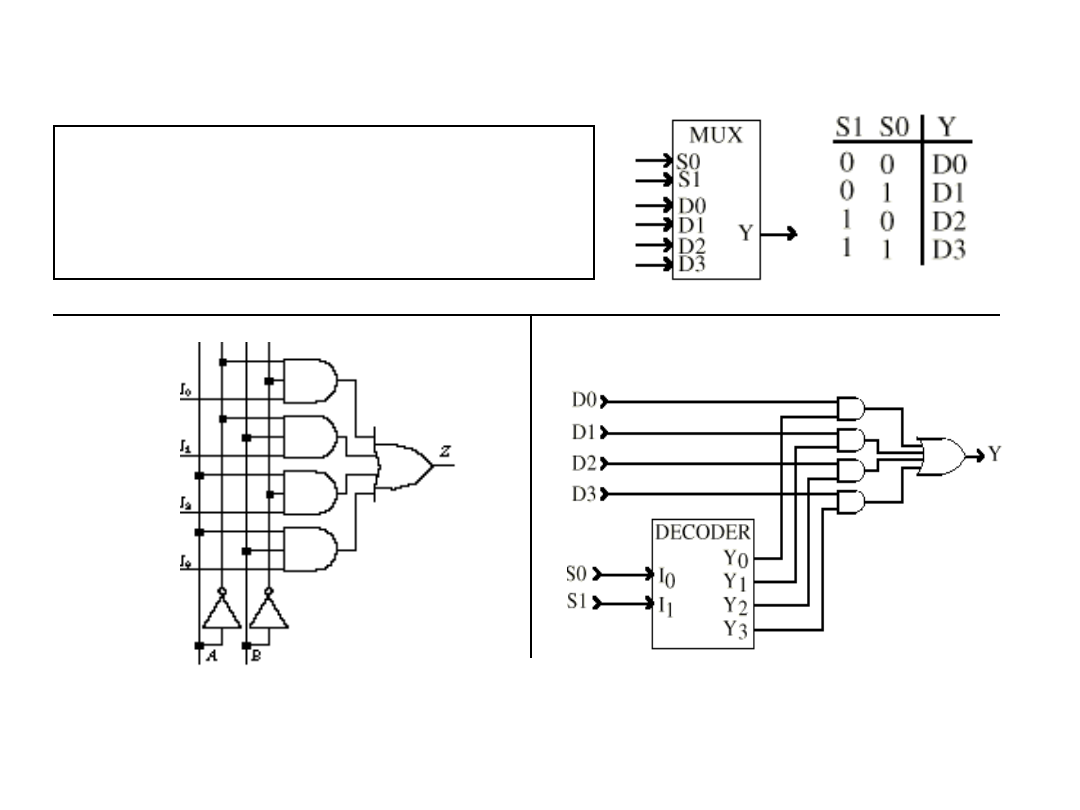

Multiplekser.

Multiplekserem nazywamy układ kombinacyjny o m

wejściach adresowych 2

m

wejściach informacyjnych

i jednym wyjściu. Sygnał pojawiający się na wyjściu

jest równy sygnałowi na wejściu o numerze

wybranym przez wejścia adresowe.

Sposoby realizacji

Teoria układów logicznych

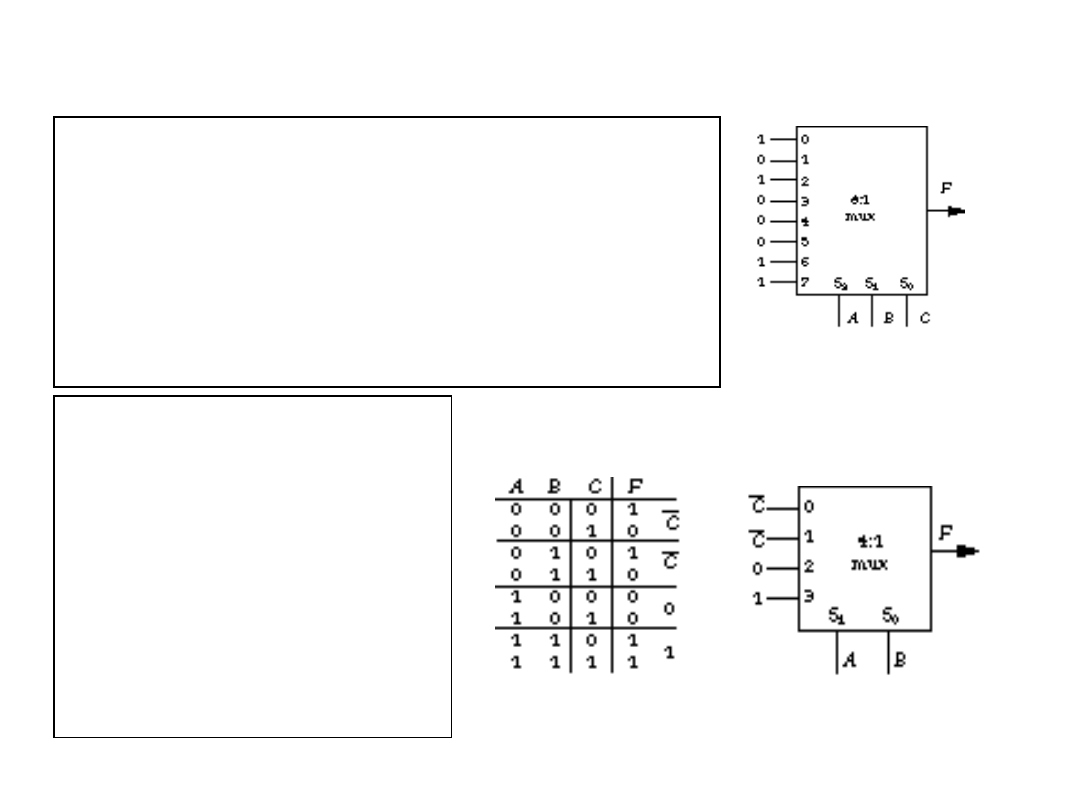

Multiplekser: zastosowanie.

Multiplekser jest elementem umożliwiającym bezpośrednią

realizację tablicy prawdy.

Zmienne funkcji są podłączone do wejść adresujących, a wejścia

danych są sterowane stałą wartością 0 lub 1 w zależności od

wartości w tablicy prawdy dla danego wektora zmiennych

funkcji.

Otrzymujemy realizację funkcji m zmiennych przy pomocy 2

m

wejściowego multipleksera.

Przykład:

F(A,B,C)={ m0, m2, m6, m7}

Możliwa jest realizacja funkcji

m zmiennych przy pomocy

multipleksera o m-1 wejściach

adresowych !

•Wybieramy m-1 kolumn sygnałów

wejściowych z tablicy prawdy.

•Grupujemy wybrane wektory w

pary takich zamych

•sygnał wyjściowy może przybierać

jedną z 4 wartości { 0,1, C, C’ },

gdzie C jest nie wybraną go

grupowania zmienną

Teoria układów logicznych

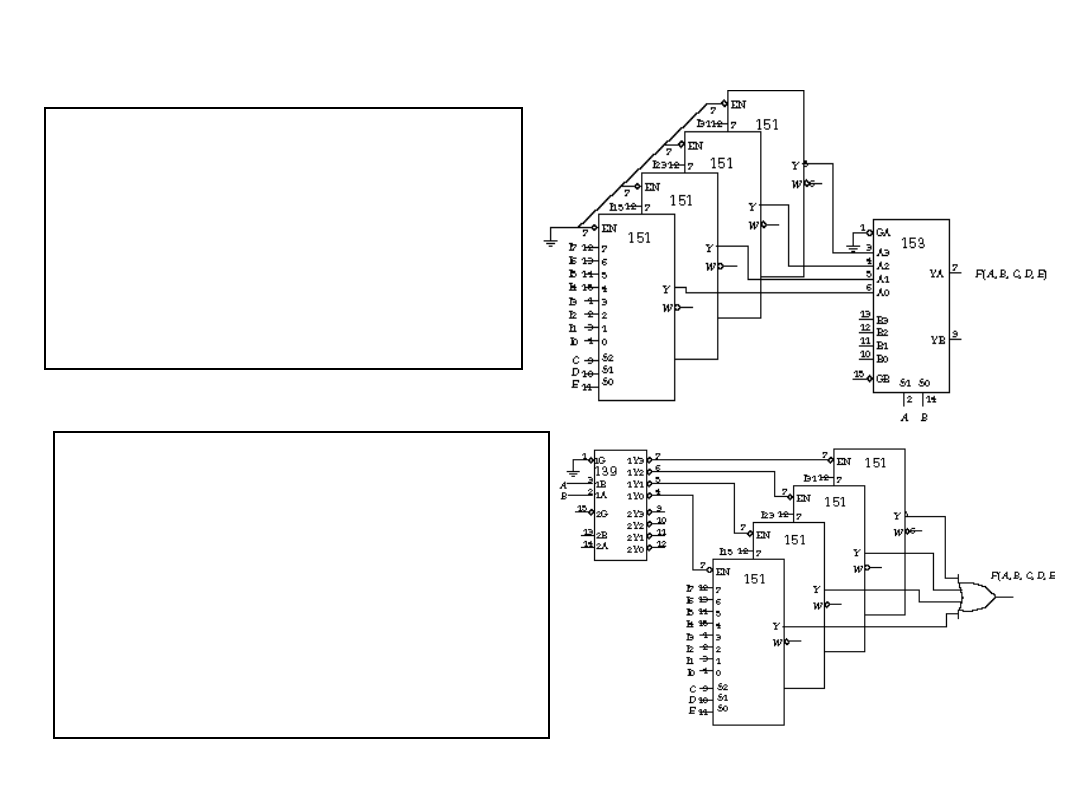

Multiplekser. Kaskadowanie.

Sposób realizacji multipleksera 32:1

przy pomocy dostępnych

multiplekserów.

Wybieramy wyjście jednego z 4

multiplekserów 8:1 przy pomocy

multipleksera 4:1.

Sposób realizacji multipleksera 32:1 przy

pomocy dostępnych multiplekserów i

dekodera 2:4 oraz 4 wejściowej bramki

OR.

Dekoder uaktywnia odpowiedni

multiplekser przy pomocy jego sygnału

EN. W danej chwili wybrany jest tylko

jeden multiplekser Kiedy EN=1 wyjście

multipleksera ‘151 jest 0 co powoduje,

brak wpływu wyjść nie wybranych

multiplekserów na wyjście bramki OR.

Teoria układów logicznych

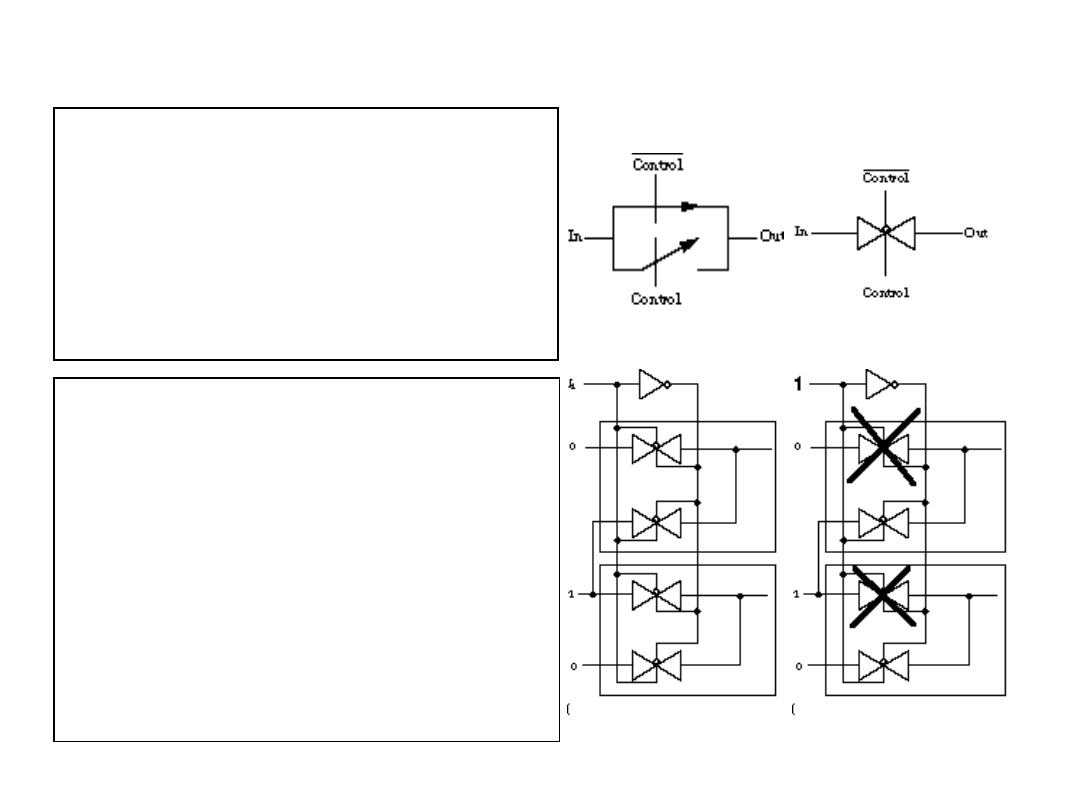

Bramki transmisyjne.

Bramki transmisyjne dostępne w technologii

CMOS stanowią alternatywę dla bramek

standartowych. Model bramki:

• dwa przełączniki połączone równolegle

•jeden zamknięty sterującym sygnałem ‘0’, drugi

sygnałem ‘1’

•aby bramka działała poprawnie ( przenosiła

sygnał z wejścia na wyjście ) obydwa klucze

muszą być zamknięte ( wynika to z technologii

CMOS )

Ze względu na swoją atrakcyjność

technologiczną

bramki transmisyjne wykorzystuje się do

budowy złożonych układów cyfrowych.

Przykład:

Podwójny multiplekser 2:1.

•kiedy sygnał sterujący jest 1 przewodzą

„dolne” bramki,

•kiedy sygnał sterujący jest ‘0’ przewodzą

„górne” bramki.

Należy pamiętać o prawidłowym sterowaniu

bramek. Niedopuszczalny jest przypadek

równoczesnego przewodzenia dwu bramek w

jednej parze.

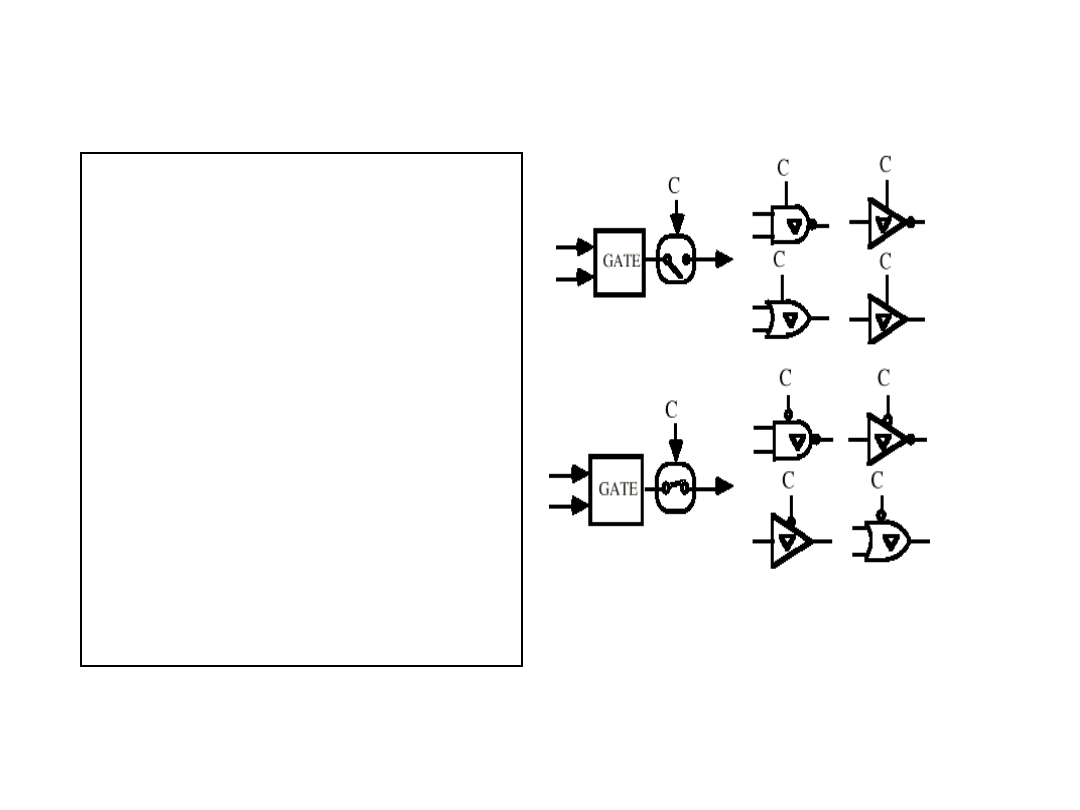

Teoria układów logicznych

Bramki trójstanowe

•Na wyjściu zamiast normalnych stanów

‘0’ i ‘1’ mogą dodatkowo przyjmować stan

‘Z’ (wysokiej impedancji ). Stan ‘Z’ nie

jest poziomem logicznym,

•Bramkę trójstanową można zrealizować

dodając klucz na wyjściu standardowej

bramki. Klucz ten jest kontrolowanyprzez

dodatkowy sygnał sterujący,

– kiedy sygnał kontrolujący klucz

jest aktywny klucz jest zamknięty i

bramka działa jak normalna

bramka logiczna.

– kiedy sygnał kontrolujący jest

nieaktywny klucz jest otwarty i

bramka jest odłączona od wyjścia.

•Wyjścia bramek trójstanowych mogą być

łączone razem pod warunkiem, że

zapewnimy, że dwie różne bramki tak

połączone nie będą aktywne

równocześnie.

Document Outline

Wyszukiwarka

Podobne podstrony:

demulti i multi

LG MULTI V

Multiplekser demultiplekser

ALAN42 MULTI component side

Multi PIN AEGON Firma 2008

Karta katalogowa Klimatyzator typu Multi Split V

Castles & Crusades Multi Classing

NDT 52517 a novel 5 category multi modal t1 and t2wi mri based strati 031914

Multi X english

CHIGO MULTI

multi 6, AGH

porozumienie 2010, Mechatronika AGH IMIR, semestr 6, Elementy wyk. robotów 2, ARTAS.SAM.v6.0.45.Mult

Cwiczenia 3 Multi wyniki

Karta katalogowa Klimatyzator typu Multi Split V (2)

racismz int (2) , Racism has become one of the many burdens amongst multi-cultural worlds like Canad

Informatyka, INFORMa, Bloki kombinacyjne średniego stopnia scalenia: multiplekser, demultiplekser(de

multiplekserPP, Polibuda, IV semestr, SEM IV, Elektronika i Energoelektronika. Laboratorium, 10. Ukł

Obrona na multi

więcej podobnych podstron