Architektura komputerów - ´cwiczenia - lista 4

Dysponuj ˛

ac procesorem o nast˛epuj ˛

acej architekturze:

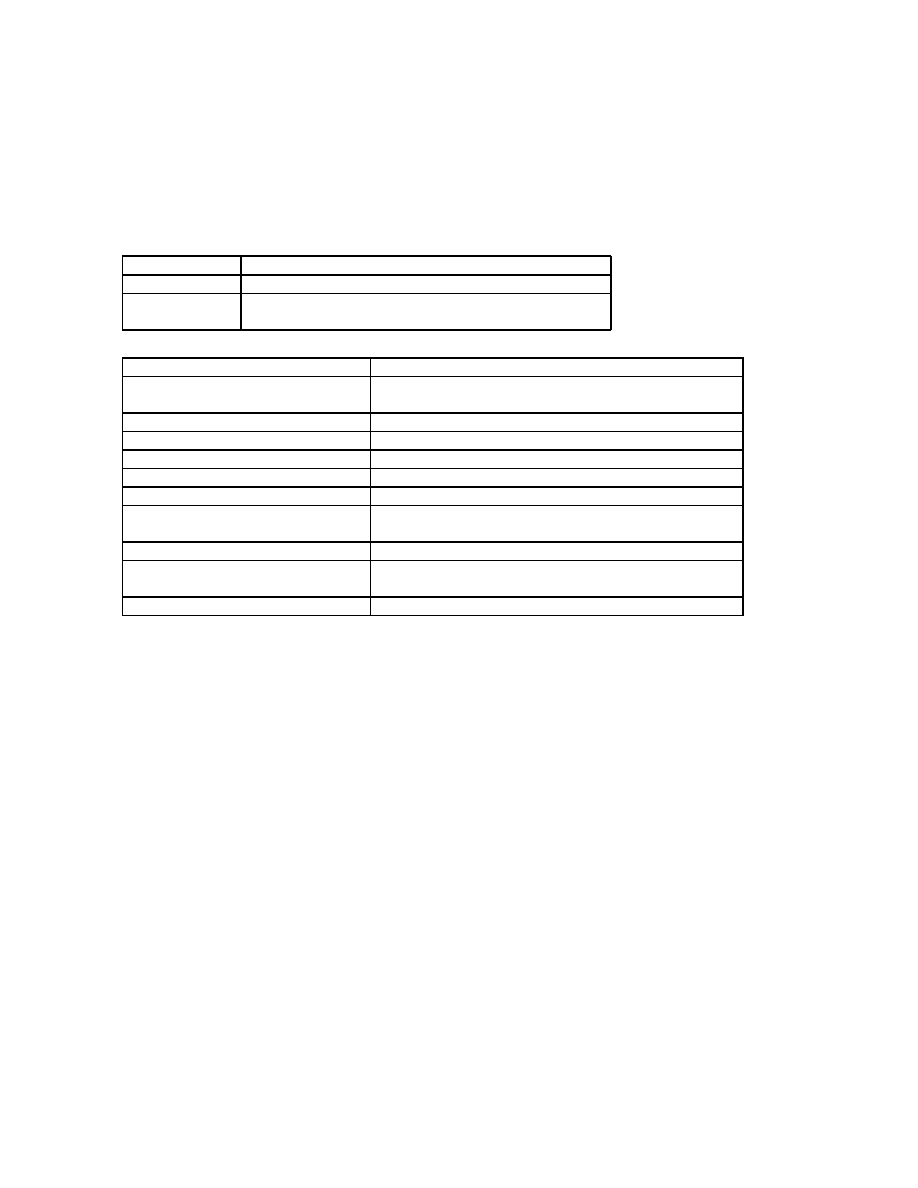

Rejestry (32 bity)

r0 . . . r31

rejestry ogólnego przeznaczenia

lr

rejestr adresu powrotu z podprogramu

psw

rejestr flag zawieraj ˛

acy status ostatnio wykonanej operacji:

bity nadmiaru OV, przeniesienia C oraz zero Z

Instrukcje

lr

r

, stała

ładuj do rejestru r

stał ˛

a

rrr

r

,r

,r

do r

zapisz wynik rotacji w prawo rejestru r

o liczb˛e bitów zawart ˛

a w r

add

r

,r

,r

do r

zapisz wynik sumy w kodzie U2 liczb z r

i r

and

r

,r

,r

do r

zapisz wynik iloczynu logicznego rejestrów r

i r

mul

r

,r

,r

do r

zapisz wynik iloczynu liczb z r

i r

bc / bnc

adres

skocz je´sli bit C jest 1/0

bv / bnv i bz / bnz

adres

jak wy˙zej dla bitów OV i Z

bl

adres

skok ze ´sladem pod adres (wywołanie podprogramu).

W rejestrze LR zapisywany jest adres powrotu.

blr

skok pod adres z rejestru LR (powrót z podprogramu).

stwu

przes(r

), r

zapisz pod adres z r

przes liczb˛e z rejestru r

.

Do rejestru r

zapisz nowy adres — r

przes (push).

lfm

r

, r

zapisz do rejestru r

liczb˛e spod adresu z r

.

napisz kod:

1. zwracaj ˛

acy w rejetrze r4 ilo´s´c "1" zawartych w słowie z r1,

2. obliczaj ˛

acy

-t ˛

a liczb˛e Fibonacciego według algorytmu iteracyjnego:

i n t f , f 1 = 0 , f 2 = 1 ;

f o r ( i n t

i = 2 ; i < ( n + 1 ) ; i + + )

{

f = f 1 + f 2 ;

f 1 = f 2 ;

f 2 = f ;

} ,

3. obliczaj ˛

acy silni˛e liczby

według algorytmu iteracyjnego:

i n t

s i l n i a = 1 ;

w h i l e ( n > 1 ) do {

s i l n i a

= n ;

n

;

} .

4. Zakładaj ˛

ac, ˙ze rejestr r1 jest wska´znikiem stosu napisz rekurencyjn ˛

a wersj˛e funkcji obliczaj ˛

acej silni˛e:

i n t

s i l n i a ( i n t n )

{

i f ( n < = 1 ) r e t u r n 1 ;

e l s e r e t u r n n

s i l n i a ( n

1 ) ;

}

Poka˙z rozmieszczenie danych na stosie.

Wyszukiwarka

Podobne podstrony:

Architektura Komputerow lista 3

Architektura Komputerow lista 2

Architektura Komputerow lista 5

Architektura Komputerow lista 3

Lista rozkazow 8051, architektura komputerow, architektura komputerow

ARCHITEKTURA KOMPUTEROW1A

architektury komputerow v1 1

Architektura Komputera, Informatyka, Płyta Główna

Architektury Komputerów zagadnienia

Architektura komputerów I 16 12 2008

gulczas 2001 opracowanie, Politechnika Wrocławska - Materiały, architektura komputerow 2, egzamin, o

Architektura komputerów I 09 12 2008

Architektura komputerów i systemy operacyjne

Architektura Komputerów wiedza ogólna

ak projekt, Studia, PWR, 4 semestr, Architektura komputerów 2, projekt

Tematy cwiczen, Architektóra komputerów

ako pytania zadania cz2 2010, Studia - informatyka, materialy, Architektura komputerów

więcej podobnych podstron