A

A

B

B

C

C

D

D

E

E

4

4

3

3

2

2

1

1

A/-B = L, COM = B

A/-B = H, COM = A

1 - 2 for modem pins

2 -3 for I/O

1 - 2 to config for I2C

2 -3 to config for SPI

1 - 2 ==> 750/760 TRANSMIT WITHOUT-RTS INVERT

2 - 3 ==> 750/760 TRANSMIT WITH -RTS INVERT

SPI_CS

SPI_MOSI

-RI

-RI

-CD

-CD

-DTR

-DSR

-DSR

-DTR

I2C_SDA

I2C_SCL

I2C_SCL

I2C_SDA

-RESET

-RESET

I2C_SCL

I2C/-SPI

X2

-DTR_IO

-DTR_IO

-CTS

I2C_SDA

-RI_IO

IO3

SPI_MISO

-RTS

-IRQ

-RI_IO

CS/-A0

-DSR_IO

TXD

IO0

SCL/SCLK

-CD_IO

X2

X1

-CD_IO

SPI_MISO

SI/A1

I2C_SDA

-RESET

RXD

-CTS

I2C/-SPI

IO2

-RTS

X1

IO3

OSCIL_CLK

SCL/SCLK

IO1

SPI_MISO

CS/-A0

IO1

-DSR_IO

SI/A1

IO2

I2C_SDA

IO0

-RTS

-CTS

SPI_SCLK

-RTS

-RTS

RXD

TXD

RXD

RXD

TXD

TXD

TXD

-IRQ

-IRQ

-IRQ

SPI_CS

SPI_MISO

SPI_MOSI

I2C_SDA

I2C_SCL

-IRQ

-RESET

OSCIL_CLK

SPI_SCLK

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

JP3

HEADER 4X2

1

2

3

4

5

6

7

8

JP7

HEADER 5

1

2

3

4

5

P1

CONNECTOR DB9

5

9

4

8

3

7

2

6

1

Y 1

14.7465MHz

R9

47

D5

LED

JP5

HEADER 3

1

2

3

C7

0.1uF

C5

0.1uF

C6

0.33uF

J1

TestPoint

1

C8

0.1uF

+

C9

10uF

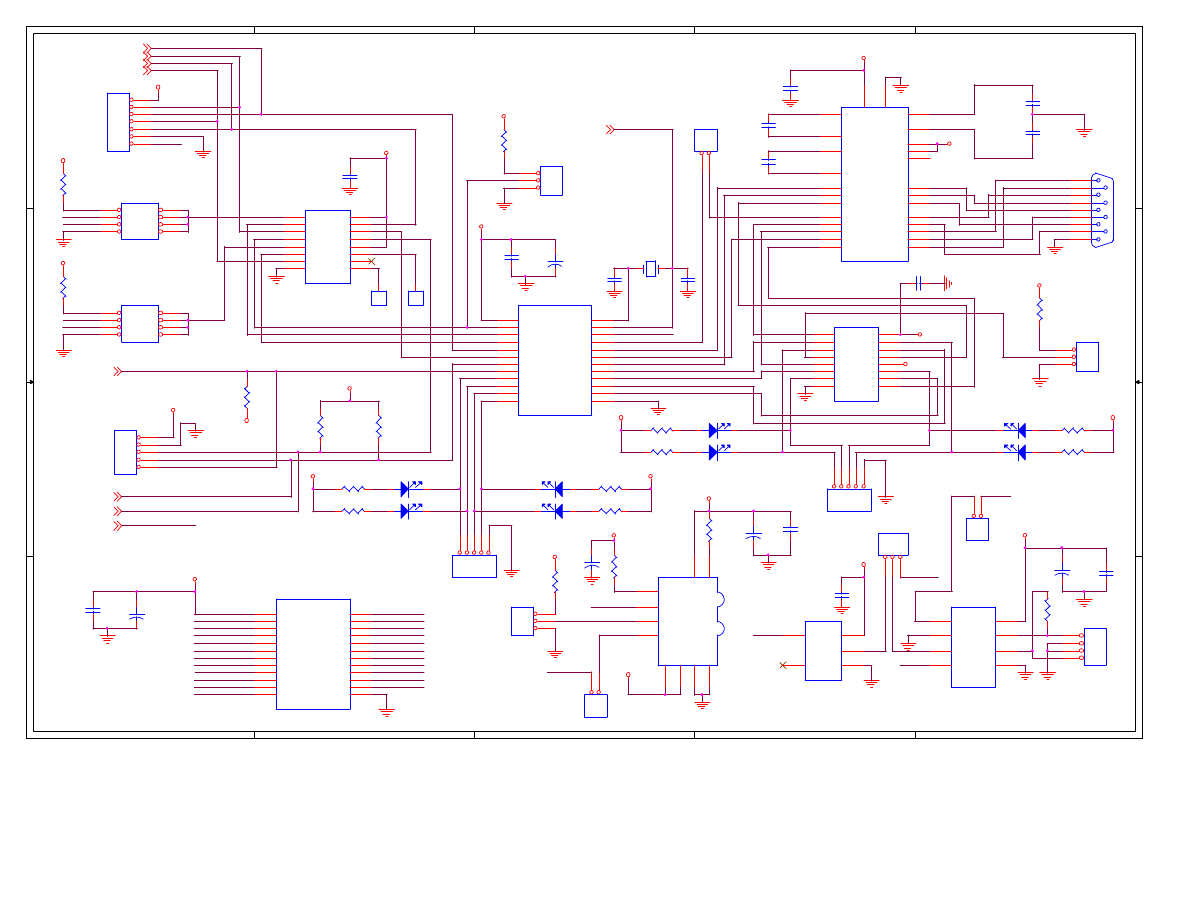

U2

SP3243E

C1+

28

C1-

24

C2+

1

C2-

2

T1IN

14

T2IN

13

T3IN

12

R1OUT

19

R2OUT

18

R3OUT

17

R4OUT

16

R5OUT

15

R1IN

4

R2IN

5

R3IN

6

R4IN

7

R5IN

8

T1OUT

9

T2OUT

10

T3OUT

11

V+

27

V-

3

-SHUTDOWN

22

-ONLINE

23

-STATUS

21

VCC

26

GND

25

C3

0.1uF

J2

TestPoint

1

JP4

HEADER 4X2

1

2

3

4

5

6

7

8

R11

47

R10

47

R12

47

D7

LED

D6

LED

D8

LED

R5

47

R7

47

D1

LED

D3

LED

D2

LED

D4

LED

R6

47

R8

47

JP2

HEADER 3

1

2

3

JP8

HEADER 5

1

2

3

4

5

U3

MAX4702

A1

1

COM1

2

B1

3

A/-B

4

A2

5

COM2

6

B2

7

GND

8

VCC

16

B4

15

COM4

14

A4

13

VL

12

B3

11

COM3

10

A3

09

C25

0.1uF

R15

10K

R16

10K

+

C2

10uF

C11

22pF

C1

0.1uF

JP15

HEADER 3

1

2

3

+

C26

10uF

C27

0.33uF

JP14

RJ11

1

2

3

4

U11

SN65HVD11D

R

1

-RE

2

DE

3

D

4

VCC

8

B

7

A

6

GND

5

+

C28

10uF

C29

0.33uF

U12

74HC1G04

VCC

5

GND

3

A

2

Y

4

NC

1

JP13

HEADER 3

1

2

3

C31

0.33uF

C4

0.33uF

R3

10K

R2

10K

R1

10K

U5

MAX4702

A1

1

COM1

2

B1

3

A/-B

4

A2

5

COM2

6

B2

7

GND

8

VCC

16

B4

15

COM4

14

A4

13

VL

12

B3

11

COM3

10

A3

09

R17

4.7

R4

10K

R18

4.7

+

C30

10uF

C24

0.1uF

C10

22pF

R19

10K

U10

GP2W1001YP

LEDA

10

RXD

8

FSEL

3

TXD

9

VDDD

6

DGND

7

VACC

1

AGND

2

MD1

5

MD0

4

U4

16IS750/760-24TSSOP

VCC

7

I2C/-SPI

8

CS/-A0

9

SI/A1

10

SO

11

SCL/SCLK

12

SDA

13

-IRQ

14

GPIO0

15

GPIO1

16

GPIO2

17

GPIO3

18

XTAL2

6

XTAL1

5

-RESET

4

RXD

3

TXD

2

-CTS

1

-RTS

24

GPIO7/-RI

23

GPIO6/-CD

22

GPIO5/-DTR

21

GPIO4/-DSR

20

GND

19

R20

10K

JP6

HEADER 5

1

2

3

4

5

JP1

HEADER 7

1

2

3

4

5

6

7

JP20

HEADER 2

1

2

JP19

HEADER 2

1

2

R21

100

JP18

HEADER 2

1

2

U1

16IS750/760-24HVQFN

VCC

4

I2C/-SPI

5

CS/-A0

6

SI/A1

7

SO

8

SCL/SCLK

9

SDA

10

-IRQ

11

GPIO0

12

GPIO1

13

GPIO2

14

GPIO3

15

XTAL2

3

XTAL1

2

-RESET

1

RXD

24

TXD

23

-CTS

22

-RTS

21

GPIO7/-RI

20

GPIO6/-CD

19

GPIO5/-DTR

18

GPIO4/-DSR

17

GND

16

A

A

B

B

C

C

D

D

E

E

4

4

3

3

2

2

1

1

RX

TX

uC UART

PORT

N/C or VCC

to enable

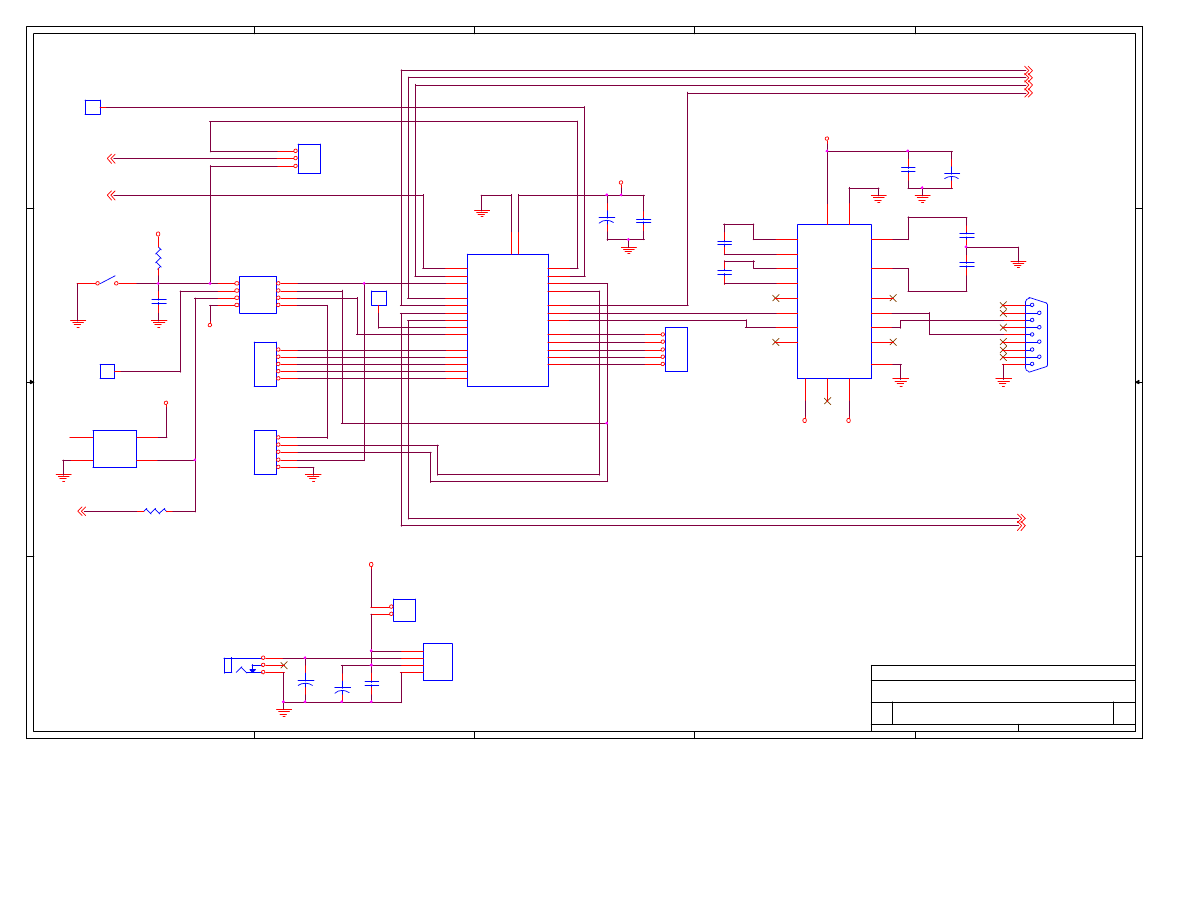

Revision 1.1

change U10 pin MD0 from 3 to 4

remove VCC from UP10 pin 1 and JP9 pin8

1-2 : uC reset

2-3 : hard reset

INSTALL FOR DC ADAPTER

REMOVE TO BE POWERED

FROM I2C or SPI BUS

DATE: 4-26-05 create ver 1.2

1. swap U3 all channel A to channel B

2 . redo pin map for U4 and U1 because ver 1.1 use old pin map

3. add pull-up resistor R20 on -IRQ signal

4. add JP16 to allow hardware reset and uC to SC16C750

5. move online pins of line drivers to VCC from GND

6. add -IRQ to JP6

7. add VCC pin JP1 pin 1

8. Change JP1 to 7 pin from 6, add -IRQ to pin 7

9 . Add jumper JP17 to isolate DC-DC converter when power

from I2C or SPI bus

10. Add JP18, JP19, JP20

11. Add R21

DATE: 5-8-05 create ver 1.3

1. Change pin-map of U1 to match datasheet

{Doc}

{RevCode}

{Title}

B

2

2

Wednesday, May 25, 2005

Title

Size

Document Number

Rev

Date:

Sheet

of

SPI_MISO

SPI_CS

SPI_MOSI

SPI_SCLK

I2C_SDA

I2C_SCL

-IRQ

SPI_MOSI

SPI_MISO

SPI_CS

SPI_SCLK

-RESET

-IRQ

I2C_SCL

I2C_SDA

OSCIL_CLK

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

JP10

HEADER 5

1

2

3

4

5

S1

SW SPST

C12

0.1uF

+

C13

10uF

C17

0.1uF

C15

0.1uF

U6

SP3223EY

C1+

2

C1-

4

C2+

5

T1IN

13

T2IN

12

R1OUT

15

R2OUT

10

V+

3

V-

7

T1OUT

17

T2OUT

8

R1IN

16

R2INI

9

GND

18

VCC

19

C2-

6

/SHDN+

20

/STATUS

11

/ONLINE

14

EN-

1

C20

0.1uF

J5

DC Power Jack

2

3

1

U9

LT1086CM

GND

1

VOUT

2

VIN

3

BODY

4

J3

TestPoint

1

C18

0.1uF

R13

10K

J4

TestPoint

1

U8

14.7456MHz

OE

1

GND

2

OUT

3

VCC

4

C16

0.33uF

P2

CONNECTOR DB9

5

9

4

8

3

7

2

6

1

+

C21

10uF

C14

0.33uF

+

C22

10uF

C23

0.1uF

R14

0

+

C19

10uF

JP9

HEADER 4X2

1

2

3

4

5

6

7

8

JP12

HEADER 5

1

2

3

4

5

JP11

HEADER 5

1

2

3

4

5

U7

LPC936

P2.0

1

P2.1

2

P0.0

3

P1.7

4

P1.6

5

P1.5/-RESET

6

VSS

7

P3.1/XTAL1

8

P2.5/SCLK

16

P2.4/-SS

15

P2.3/MISO

14

P2.2/MOSI

13

P1.2/SCL

12

P1.3/SDA

11

P1.4/-INT1

10

P3.0/XTAL2

9

P2.7

28

P2.6

27

P0.1

26

P0.2

25

P0.3

24

P0.4/PDA

23

P0.5/PCL

22

VDD

21

P0.6

20

P0.7

19

P1.0/TXD

18

P1.1/RXD

17

J6

TestPoint

1

JP16

HEADER 3

1

2

3

JP17

HEADER 2

1

2

Wyszukiwarka

Podobne podstrony:

ALi M3602 Demo Board

RAZR V3x D2A Daughter board Schematic and Overlays

06 pamięć proceduralna schematy, skrypty, ramyid 6150 ppt

7 aglebra schematow bloczkowych

wZ 2 Budowa wiedzy społecznej teoria schematów

3 ogolny schemat replikacji i onkogeza DNA wirusowa

Schematy animacji

wykład 5 schematy, przywileje, role

schemat mechanika

schemacik prezentacji

5 Algorytmy i schematy blokowe

Marsz Polonia demo

cad demo 1

Cutting Board 1

Propozycja przygotowania schema Nieznany

ABC praw konsumenta demo

f Obraz 6 plan 1 schemat

więcej podobnych podstron