12

Pamięci

Podstawowe parametry:

1) pojemność – ilość informacji cyfrowej jak może być zgromadzona

2) długość (szerokość) pamiętanego słowa. Organizacja struktury

pamiętającej inf. – ilość bitów możliwych do obsłużenia naraz w

procesie zapisu/odczytu. Ilość tych słów wyznacza pojemność

3) czas dostępu - czas od rozpoczęcia operacji do zakończenia (od

odczytu pamięci do zapisania danych na magistrali danych).

Dodatkowe linie:

RAS

(Row Address Select) – pomagają wybierać wiersz

CAS

(Column Address Select) – pomagają wybierać kolumnę

Klasyfikacja pamięci:

ROM – Read Only Memory (tylko do odczytu)

RAM – Random Access Memory – dostęp swobodny (zapis/odczyt)

ROM:

1) Mask ROM

2) PROM

3) EPROM

4) EEPROM

5) EAPROM

1) Mask ROM – tylko do odczytu, w niej jest inf. o procesie produkcji,

dostęp do inf. zaraz po włączeniu. Dane nie ulegają utracie po

wyłączeniu zasilania, duża szybkość, niewielka pojemność

2) PROM – programowalna – sprzedawana jako czysta, programowanie

tylko raz poza układem cyfrowym, w którym ma pracować, działa jak

MaskROM, bardzo szybkie, niewielka pojemność

3) EPROM – Erasable Programmable ROM – możliwy zapis i kasowanie

wielokrotne, zmiana struktury poza systemem, na drodze elektrycznej.

Tranzystory z pływającą bramką, w stanie czystym same jedynki.

Kasowanie – naświetlanie UV – zjawisko fotoelektryczne zewnętrzne w

tranzystorach, kasowanie całości. Programowanie – setki/tysiące razy.

Mogą mieć duże pojemności, nie są zbyt szybkie

4) EEPROM – elektrycznie kasowalne EPROMy, własności jak wyżej

5) EAPROM – możliwość wybiórczego kasowania i programowania,

kasowanie elektryczne

13

RAM:

1) DRAM

2) SRAM

1) DRAM – elementy pamiętające – wartość ładunku na kondensatorach.

Samo zasilanie nie wystarczy, kondensatory tracą ładunek – jest

konieczne odświeżanie informacji, inaczej na kondensatorach mogą

odłożyć się dowolne ładunki

2) SRAM – przerzutnik – element pamiętający – musi być utrzymana

wartość logiczna

konieczne zasilanie

Odczyt i zapis

Odczyt z ROM (lub SRAM):

1) ustawienie adresu (odwołanie się do pamięci) – linie adresowe (np. A0 ...

A14), ile linii – zależy od tego ile pamięci jest w systemie. Na podstawie

adresu zostaną zaktywowane linie MREQ lub im odpowiadające

2) CE/ (Chip Enable) – linie wyboru określonego układu pamiętającego,

aktywne stanem niskim

3) OE/ albo RD/ - Output Enable/Read – linie odczytu – ustawia akcję

odczytu

4) to wszystko wysyłane do układu pamiętającego na linię adresową (np.

D0 ... D7)

Zapis do SRAM

Wybór adresu i układu jak poprzednio, zmiana linii WRITE – dane z pamięci

muszą być ustawione przed ustawieniem linii WRITE w stan aktywny (przez

procesor lub układ DMA). Procesor lub DMA musi utrzymać dane przez czas

wymagany dla pamięci, ale bez zwrotu informacji o tym, że zapis się udał czy

nie.

Odczyt z DRAM:

Pojawiają się linie RAS i CAS

1) na magistrali adresowej jest podawany adres wiersza – jak się adres

ustawi, to

2) linia RAS przechodzi w stan aktywny (poziom niski) – potwierdzenie, że

na magistrali jest adres wiersza

3) na magistrali adresowej przełączanie adresu (stan niestabilny) – żeby

pojawił się adres kolumny – linia CAS przechodzi w stan aktywny

(poziomem niskim)

Po zakończeniu adresacji – wskazanie linii MREQ.

14

Gdy RAS i CAS są w stanie aktywnym, linia READ przechodzi w stan aktywny –

zaczynamy realizować odczyt.

Na magistrali danych dane są odczytywane (pobierane).

Czas dostępu – od momentu rozpoczęcia adresacji do odczytu danych (t

ACC

) –

maksymalny. Można też wymyślać inne, ale po co . Koniec odczytu – linie

RAS i CAS przechodzą w stan nieaktywny.

Zapis

Zmiany:

1) adres wiersza, aktywna linia RAS (do końca procesu zapisu)

2) adres kolumny, aktywna linia CAS (do końca procesu zapisu)

Ukształtowanie danych na magistrali danych, linia WR uaktywnia się.

Odświeżanie DRAM

1) w trybie skupionym. Dla każdego elementu odczyt i zapis. Tryb prosty,

ale: fragment pamięci zawsze nieaktywny, mocne obciążenie dla

systemu – ruch na magistrali, lepsze jest odświeżanie wyrywkowe

(pojedynczych komórek), typy:

2) odświeżanie sygnałem RAS/ (RAS only refresh): - nie jest podawany

adres kolumny, tylko adres wiersza. Jest specjalny licznik, który wybiera

kolumny – i z tego licznika jest pobierana ta wartość (po upływie

timeout-u) i ta komórkę odświeżamy (i tylko tą). Małe obciążenie dla

procesora – adres wiersza i odświeżenie tylko jednej kolumny. Procesor

musi sensownie wybierać adresy wiersza

3) odświeżanie ukryte. Odczyt/zapis kończy się kiedy linia RAS jest

nieaktywna, ale CAS jest aktywna – mamy adres kolumny, potem RAS

znowu aktywna, itd. Zaleta: odświeżanie wyrywkowe, przy okazji

odczytu/zapisu, procesor raz podał adresy i sprawa załatwiona, adres

sam się wygeneruje. Zawsze zdążymy z odświeżeniem, nic nie będzie

pominięte

4) CAS/ przed RAS/ - najpierw w stan aktywny linia CAS, potem RAS,

magistrala adresowa nie transportuje adresu, adresy wybierane z

liczników. Na końcu odświeżania przechodzimy do normalnego

zapisu/odczytu. Odświeżanie wybiórcze, minimalnie angażuje procesor

(musi uaktywnić RAS i CAS, nic poza tym)

5) Odświeżanie automatyczne – układ pamięci odświeża się sam, procesor

nie jest angażowany

Specjalne tryby pracy układów DRAM (kiedy chcemy zminimalizować czasy

dostępu)

15

1) odczyt – modyfikacja – zapis. Zapis jest w to samo miejsce, co odczyt –

jedna operacja, oszczędzamy na adresacji. Wstrzymanie pracy magistrali

– np. DMA nie może pracować

2) tryb stronicowy – ograniczenie ilości adresowania. Adres wiersza jest

stały, kolumny odczytywane z jednego wiersza (adres kolumny się

zmienia)

3) tryb półbajtowy, RAS aktywna, CAS się zmienia (następne kolumny z

tego samego wiersza)

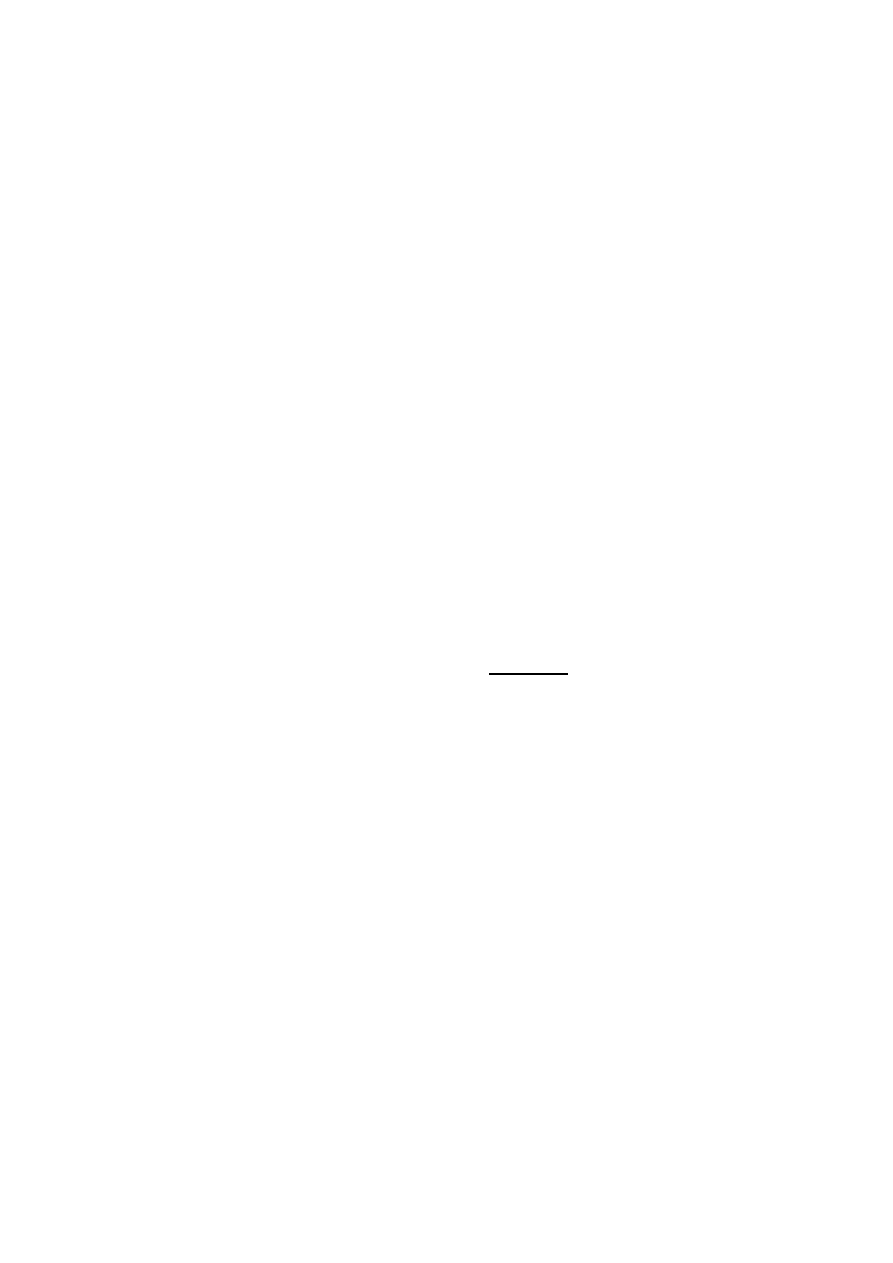

Tworzenie bloków pamięciowych

2 akcje:

- zwiększanie szerokości pamiętanego słowa (k-bloków o organizacji 2

m

słów*n, chcemy zrobić szerokość słowa n*k)

wszystkie układy jednocześnie włączone, chcemy odczyt/zapis w każdym z

układów

- zwiększanie ilości pamiętanych słów. Linie danych – do każdego z układów

pamiętających; linia adresowa – też, ale wyodrębnione (o adresach A

n

... A

n+1 –

najstarsza część adresu

) do dekodera. W danej chwili wybranie 1 układu

pamiętającego odczyt/zapis też tylko w tym układzie; wiele układów

odczyt/zapis taki jak w pojedynczym układzie

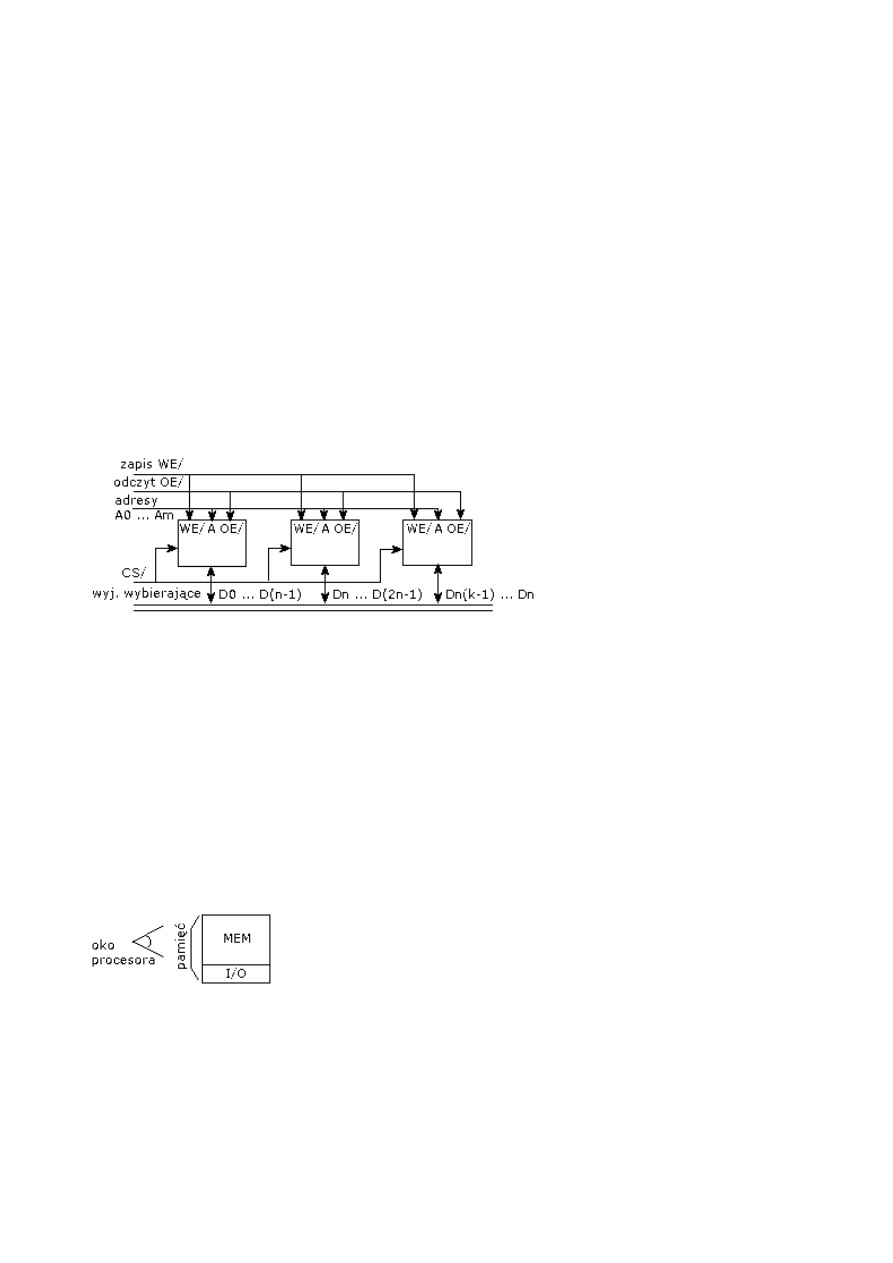

Współadresowanie i adresowanie izolowane pamięci i układów WE/WY

1) współadresowanie – z punktu widzenia procesora, pamięć + I/O to jeden

blok – pamięć;

zalety:

- w liście programów danego procesora jest więcej

instrukcji odnoszących się do pamięci niż do I/O

wygodna obsługa I/O

- zanika I/OREQ, MEMRQ – do zaadresowania wystarczą linie adresujące

wady:

- nie możemy użyć max. pamięci operacyjnej – ograniczona przestrzeń

związana z pamięcią

- mała szansa reorganizacji

16

- wolniejszy dostęp (potencjalnie) do układów I/O

podsumowanie:

- układy dedykowane do obsługi określonego zadania (np. w silniku)

- dla komputera ogólnego przeznaczenia to nie ma sensu

2) adresowanie izolowane – 2 odrębne zasoby, bloki się nie nakładają, ale

te same adresy odpowiadają MEM i I/O dla pewnego zakresu

wady:

- muszą być linie MEMRQ i I/ORQ – żeby

rozgraniczyć

- dostęp do I/O jest nie zawsze wygodny

zalety:

- brak ograniczeń na ilość pamięci i adresów I/O

- brak problemów z rozbudową

podsumowanie:

- sprawdza się w komputerach ogólnego przeznaczenia, tak są zbudowane

PC-ty

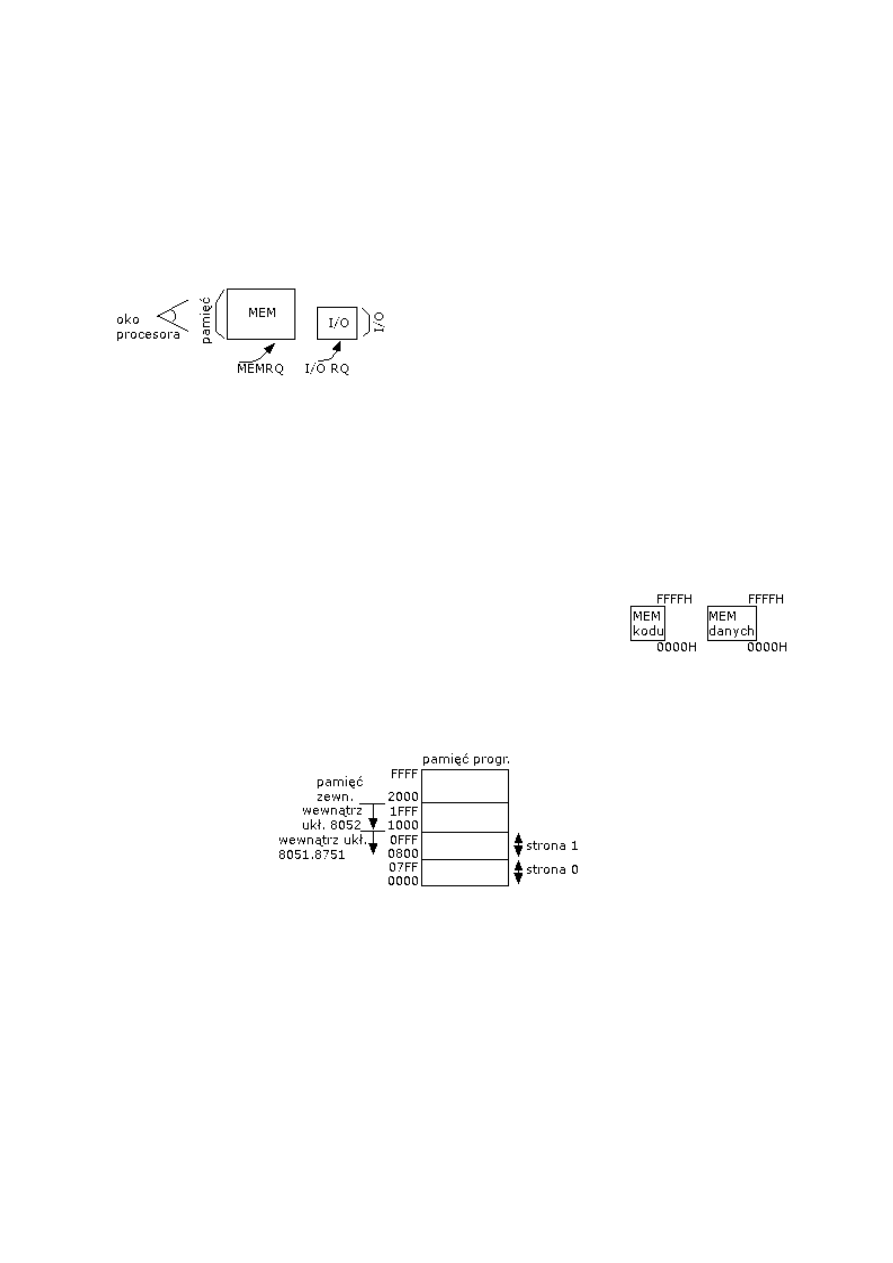

Konstrukcja pamięci w 8051

- architektura harwardzka – odseparowanie pamięci

programu od pamięci danych:

1) MEM kodu – max. 64 kilobajty pamięci

+ pamięć zewnętrzna

+ pamięć wewnętrzna

Strony – po 2 kilobajty; odwoływanie do pamięci – PC. Pamięć kodu –

adresowanie w sposób rejestrowy pośredni, rejestr pośredni – PC. MOVC –

kontakt z pamięcią, zaczerpnięcie danych.

PC 16 bitowy, bity 11-15 (najstarsze) – wskazują stronę (blok 2-kilowy), bity

0-10 – adres.

Pamięć danych

- max. 64 kb

+ wewnętrzna – max. FF (245 bajtów) albo 128 bajtów

+ zewnętrzna – reszta

17

- odwołania

+R0 i R1 – odwołanie do pamięci danych – adresowanie rejestrowe

pośrednie

MOV A,@R0 – pobranie do A z wewn. pamięci danych, zawartość R0 jest

adresem wskazującym na wewn. pamięć danych

MOVX A,@R0 – pobranie do A z zewn. pamięci danych, tu 8 bitów nie

wystarczy – potrzebny jest rejestr DPTR

DPTR – rejestr. pośrednie przez DPTR, np. MOVX A,@DPTR

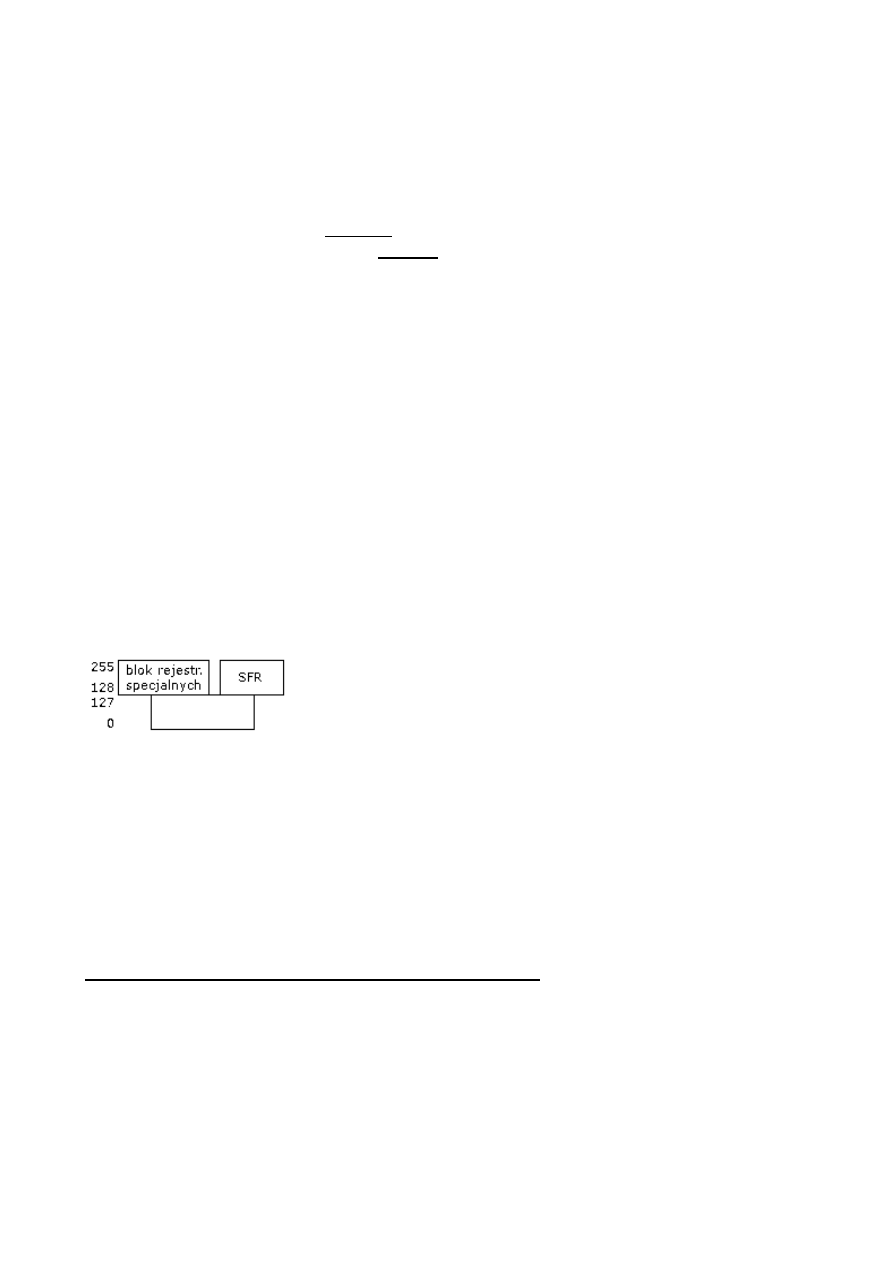

- pamięć wewnętrzna:

+ adresy 0 do 31 – zestawy rejestrów od R0 do R7

+ od 32 do 47 – obszar adresowany bitowo

+ od 48 do 127 (7FH)

+ 80H (128) – 255 (FFH) – rejestry specjalnego przeznaczenia – blok

SFR

Cała pamięć wewnętrzna może być adresowana w trybie bezpośrednim.

Stos znajduje się pod adresem 07 (po restarcie).

Podsumowanie: obszar pamięci użytkowej: od 0 do 127, rejestry specjalne: od

128 do 255

Dla procesorów 8052 – modyfikacja

SFR – rejestry specjalne, tryb adresowania

bezpośredniego

Blok rejestrów specjalnych – pośredni tryb

adresowania

Przyłączanie zewnętrznych pamięci

8 linii adresowych, 8 linii danych. Magistrala danych – linie portu od P00 do

P07, linie te pełnią też rolę młodszej części magistrali adresowej

(multipleksowana (przełączana) linią ALE).

Port 7: P3.7 – read, P3.6 – write. Wykorzystanie starszej części adresu. P2 –

starsza część magistrali adresującej.

Przyłączanie zewnętrznej pamięci programu.

Linia PSEN (budowa – bramka AND razem z READ) – sygnalizuje dostęp do

zew. pamięci programu. Można połączyć pamięć programu i danych

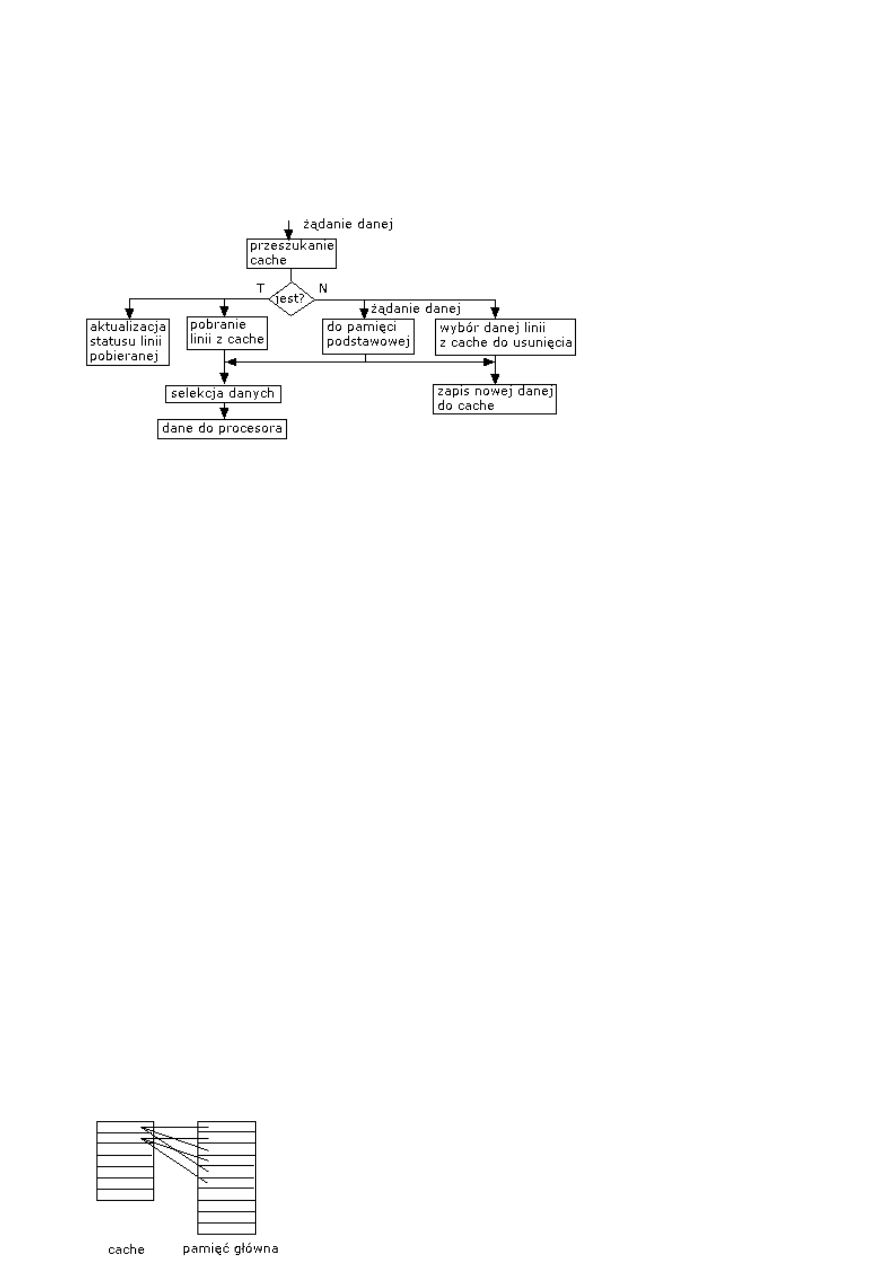

Pamięć podręczna – CACHE

Ma lepsze parametry niż zwykła pamięć, niewielka, zawarte są w niej

instrukcje często potrzebne procesorowi.

18

Cechy:

+ współczynnik trafienia (hit ratio) – prawdopodobieństwo, że dana potrzebna

procesorowi jest w pamięci cache

+ miss ratio – danej nie ma w cache

Które dane usunąć z cache? Algorytmy usuwania danych:

+ uwzględnianie informacji statusowej

- LRU (+)

- MIN (-)

+ bez uwzględniania informacji statusowej

- FIFO (+) (first in first out) – usunięta ta, która jest najdłużej pod

względem czasu trwania

- RANDOM (+)

LRU – usuwa się daną, która najdłużej nie była w użyciu

MIN – usuwa tę, która najdłużej w przyszłości nie będzie potrzebna (bardzo

fajnie, ale jak to zrobić?)

Oprócz tych 4 mechanizmów, są jeszcze mechanizmy uaktualniania pamięci

podstawowej:

+ każdy zapis do cache automatycznie do pamięci podstawowej – na wypadek

awarii cache, ale spada prędkość działania cache => rzadko stosowane

+ dane do pamięci podstawowej – tylko wtedy, gdy mają być skasowane z

cache – wydajniejszy sposób

+ kopiowanie danych przed usunięciem i jeszcze dodatkowo badani czy dane

uległy zmianom

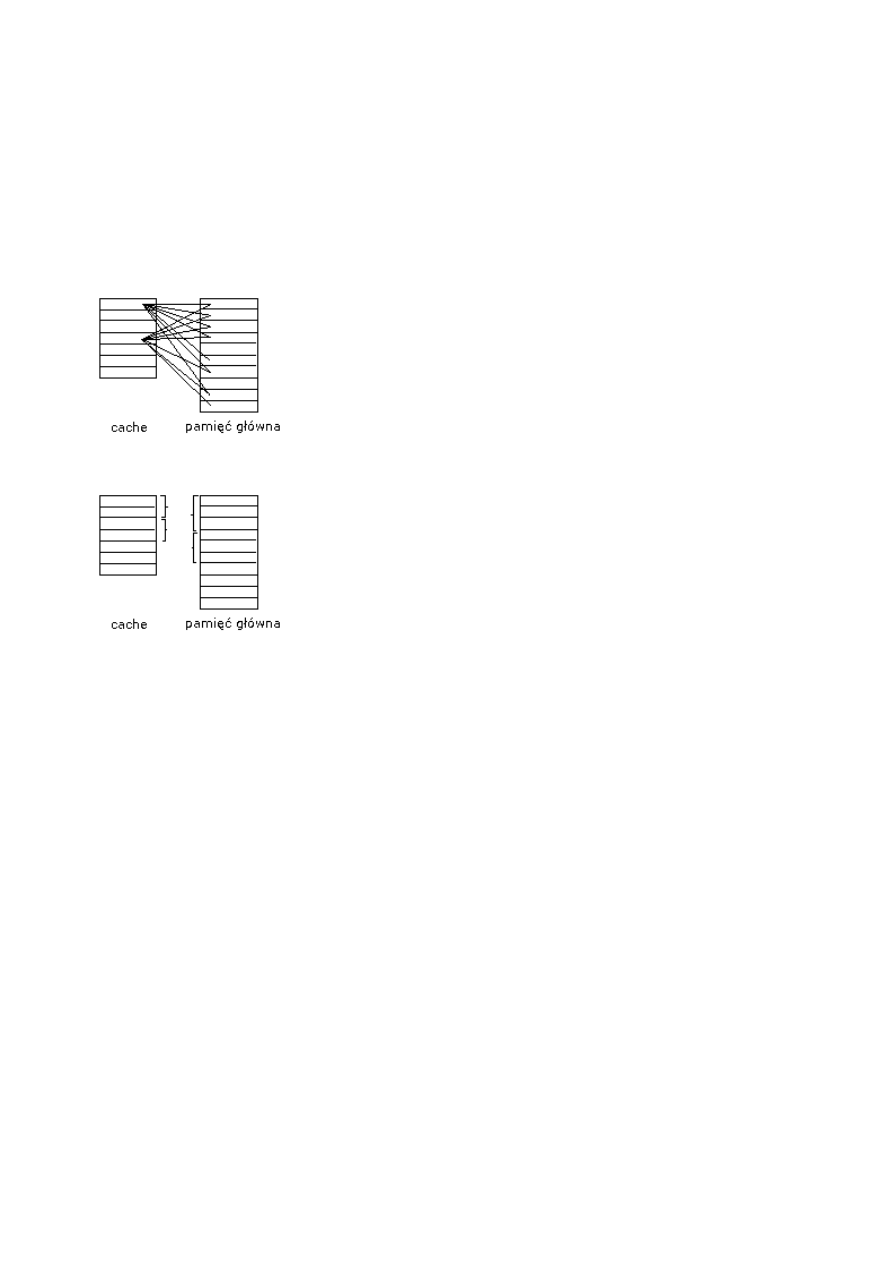

Organizacja pamięci cache

+ cache o bezpośrednim mapowaniu (direct mapping) – dane z pamięci

głównej brane są z pewnym krokiem

19

ZALETA: oszczędność w czasie przeszukiwania pamięci cache

WADA: zapotrzebowanie procesora może być takie, że będzie potrzebował

dużo danych z pamięci głównej, a cache jest mała => cache mało przyspiesza

działanie procesora

+ cache w pełni asocjacyjna – w danej komórce cache może być dana z

dowolnego obszaru pamięci głównej, dane z każdej komórki pamięci

podstawowej

ZALETA: unikamy poprzedniej wady, można

odwzorować duży fragment pamięci głównej w cache

WADA: trudno znaleźć daną w pamięci głównej

+ pamięć cache zbiorowo – asocjacyjna

Cache dzielone na mniejsze bloki, które są

odpowiedzialne za bloki pamięci głównej. Obszary

pamięci są ze sobą powiązane.

ZALETY:

- wstępne uporządkowanie

- dość duża elastyczność

Każde z tych 3 rozwiązań możemy spotkać – nie ma „lidera”

Zarządzanie pamięcią operacyjną

Pamięć główna:

- podrzędna – często tworzona też z innych urządzeń, np. fragmentów

dysku

- nadrzędna – zawsze pozostaje pamięcią półprzewodnikową

Pamięć podrzędna – nie powinna być pamięcią, do której system często się

odwołuje, raczej do składowania informacji

Pamięć nadrzędna jest dzielona na mniejsze struktury:

- stronicowanie – podział na bloki o jednakowej wielkości. Blok –

najmniejsza jednostka jaka może być przydzielona np. programowi.

Stronicowanie – wygodniejsze z punktu widzenia sterowania pamięcią,

po zakończeniu np. programu nowa strona może zastąpić stare

„cegiełki”. Wada – często zadanie nie potrzebuje całego bloku (np. tylko

parę bitów)

20

- segmentacja – zmiana wielkości bloku. Po zakończeniu programu

mogą zostać luki po przydzieleniu bloku innemu procesowi

Cechy pamięci:

+ protekcja (zabezpieczenie)

+ udostępnianie (współdzielenie)

Mechanizmy alokacji/relokacji stron (segmentów):

+ sposób statyczny – przydzielenie zasobów w momencie uruchomienia

programu, później bez zmian aż do końca

+ dynamiczny – uruchomienie nowego programu powoduje przydzielenie

zasobów, natomiast zakończenie programu powoduje analizę rozdzielenia

stron/segmentów

Dla mechanizmu dynamicznego:

- lokalność danych:

+ czasowa – warto rozmieścić dane w pobliżu, ale działania na tych

danych będą ustawiane w określonym porządku (np. dla pętli

niekoniecznie po kolei w komórkach)

+ przestrzenna – warto, żeby dane znalazły się w kolejnych

strukturach/komórkach pamięci, np. tablica

Zbiór pracujący – lokalność i czasowa i przestrzenna

Wyszukiwarka

Podobne podstrony:

mazurkiewicz,Technika Cyfrowa, lista rozkazów procesora

mazurkiewicz,Technika Cyfrowa, organizacjie komputerów

mazurkiewicz,Technika Cyfrowa, system przerwań procesora

mazurkiewicz,technika cyfrowa,cyfrowe układy scalone

mazurkiewicz,technika cyfrowa,Modemy i kodery multimedialne

mazurkiewicz,Technika Cyfrowa, koprocesor arytmetyczny

Technika Cyfrowa (mazurkiewicz) -wyklady, edu, el, pwr, Technika Cyfrowa (mazurkiewicz) -wyklady

mazurkiewicz,Podstawy techniki cyfrowej i mikroprocesorowej I, opracowanie zagadnień

Technika cyfrowa opracowanie (Mazurkiewicz)

NOTAKI Z TECHNIKI CYFROWEJ

Laboratorium 4, Politechnika Koszalińska, III semestr, Laboratorium techniki cyfrowej

Przekazniki i styczniki, Nauki Ścisłe Politechnika, Elektronika Teoria, Technika Cyfrowa, Technika C

Lab0, ZUT, Technika Cyfrowa, Technika Cyfrowa, sprawozdaniaTC

4 Podstawy techniki cyfrowej, Podstawy techniki cyfrowej

Lab4, ZUT, Technika Cyfrowa, Technika Cyfrowa, sprawozdaniaTC

więcej podobnych podstron