A

RCHITEKTURA KOMPUTERÓW

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

ARCH–1

Architektura i organizacja komputera

A

RCHITEKTURA

K

OMPUTERA

specyfikacja funkcjonalnych cech

komputera opisanych list rozkazów

i wskazaniem obiektu ich oddziaływania

(architektura listy rozkazów – ISA)

O

RGANIZACJA

K

OMPUTERA

(

STRUKTURA LOGICZNA

)

odwzorowuj ca cechy funkcjonalne

i nadaj ca kształt operacyjny

(architektura układów – HSA)

W

YKONANIE

(

TECHNOLOGIA

)

A

RCHITEKTURA KOMPUTERÓW

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

ARCH–2

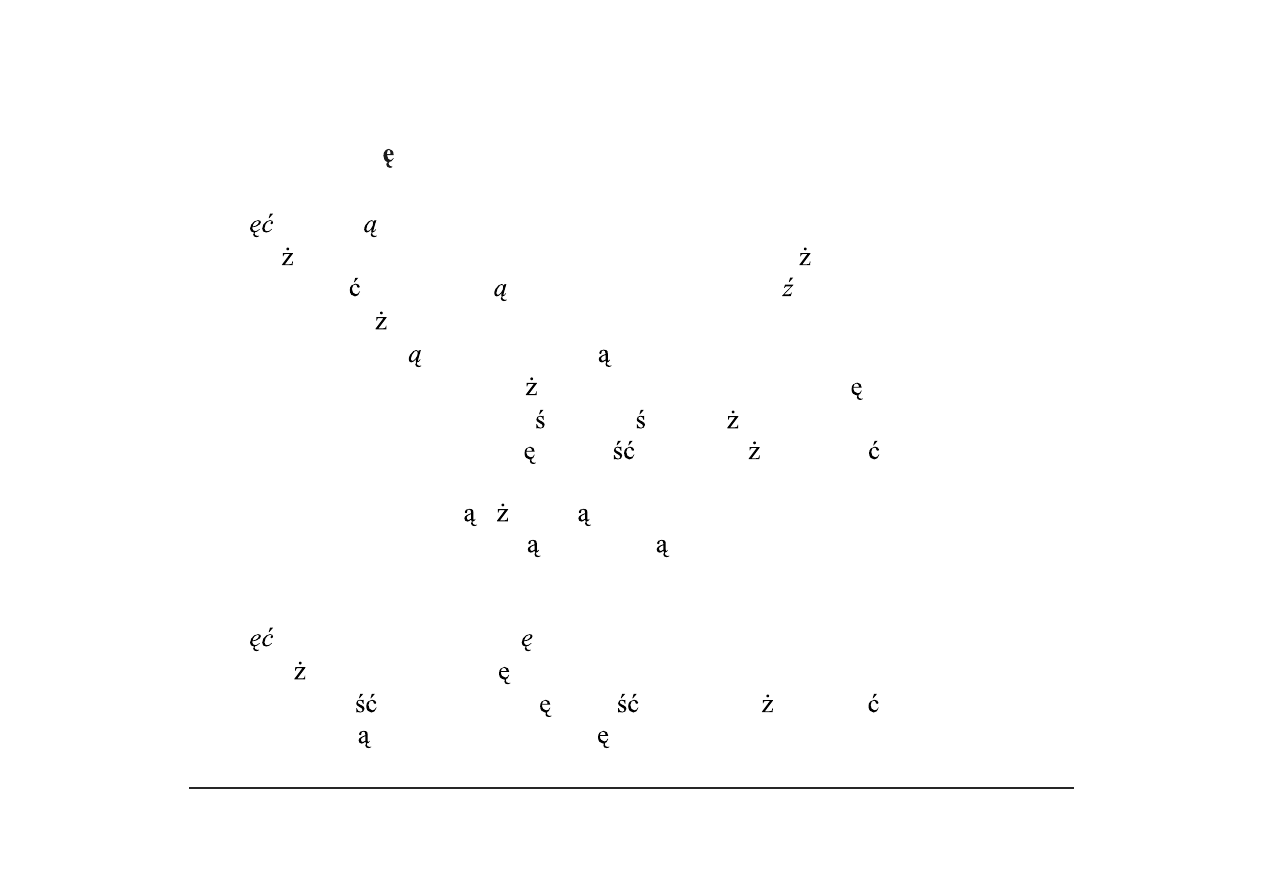

Komputer z programem przechowywanym (pami tanym)

program-stored computer

(J.von Neumann, 1945)

CU

M

adres

jednostka

wykonawcza

ALU

słowo

słowo

słowo N

…

WY

WE

dane

teoria informacji

(Claude Shannon, 1936)

koncepcja jednolitego przetwarzania

(Alan Turing, 1937)

?

jak działa komputer?

…⇒ (CU: słowo: M

→ALU) ⇒

(interpretacja CU: polecenie)

⇒ (CU: słowo: M→ALU) ⇒

(interpretacja CU: argument) …

⇒ (wykonanie ALU: wynik→AC)

(interpretacja CU: słowo AC

→M)

⇒ (CU: słowo: M→ALU) ...

(AC – rejestr akumulatora)

? – gdzie jest kolejne słowo?

• wskazanie explicite – adres

• domniemanie – nast pne

→ licznik programu (PC)

A

RCHITEKTURA KOMPUTERÓW

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

ARCH–3

Koncepcja pami ci

Abstrakcja

Pami

– uporz dkowany zbiór słów (informacji)

• ka de słowo ma ustalone miejsce w zbiorze – mo na mu jednoznacznie

przypisa numer porz dkowy – unikatowy wska nik lokacji (adres)

• rozmiar ka dego słowa jest taki sam

• słowa nie maj etykiet wskazuj cych ich znaczenie

• znaczenie słowa nie zale y od jego lokalizacji w pami ci

• interpretacja słowa (okre lenie tre ci) zale y od stanu procesora podczas

pobierania słowa z pami ci – tre słowa mo e oznacza :

kod rozkazu

(polecenia), ang. op-code,

argument

(dan u ytkow ), ang. user data,

parametr stanu

(dan systemow ), ang. system data

Realizacja

Pami

– zbiór komórek pami ci – główny magazyn informacji

• ka da komórka pami ci (

ang.

memory cell) zawiera jedno słowo

• zawarto komórki pami ci (tre słowa) mo e zmieni tylko procesor,

dokonuj c przesłania do pami ci wyniku wykonania rozkazu.

A

RCHITEKTURA KOMPUTERÓW

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

ARCH–4

Nawigacja – gdzie s potrzebne słowa?

tryb control flow – polecenie (rozkaz) czeka na dane

• najpierw musi by pobrane słowo polecenia

o

musi by ustalona lokacja pierwszego pobieranego słowa

• z interpretacji słowa wynika zapotrzebowanie na argumenty

• kolejne słowo polecenia musi by wskazane:

o

w tre ci polecenia bie cego

o

automatycznie

→ licznik rozkazów (program counter)

typowe realizacje procesorów

tryb data flow – dane czekaj na polecenie

• osobne strumienie danych i polece

• zestawy polece tworz sekwencj opisan przez algorytm

o

mo liwe przetwarzanie współbie ne

• zestawy danych s (cz ciowo) uporz dkowane

o

mo liwe jednoczesne przetwarzanie danych przez kilka rozkazów

!

brak komercyjnych realizacji procesorów dla trybu dataflow

powszechne realizacje jednostek wykonawczych

A

RCHITEKTURA KOMPUTERÓW

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

ARCH–5

Sterowanie wykonaniem programu – udany kompromis

Adres (lokacja) kolejnego słowa polecenia

• wskazany automatycznie (licznik rozkazów) – powi zanie sekwencyjne

o

zaleta

: w kodzie słowa nie jest potrzebny adres kolejnego polecenia

o

wada

: wykluczone sterowanie – kolejne polecenie nie zale y od

wyniku polece wcze niejszych

• wskazany w tre ci polecenia bie cego – powi zanie ła cuchowe

o

zaleta

: rozwi zanie elastyczne, sterowanie dowolne

o

wada

: konieczna rozbudowa kodu o adres kolejnego polecenia

Kompromis

• zasada – powi zanie sekwencyjne → licznik rozkazów

• wyj tek – powi zanie ła cuchowe → mo liwo sterowania

o

specjalne rozkazy skoku (jump) / rozgał zienia (branch)

→ wymuszanie stanu licznika rozkazów

A

RCHITEKTURA KOMPUTERÓW

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

ARCH–6

Polecenia (ISA) i układy (HSA)

Architektura listy rozkazów (ISA) – opis dost pnych polece (instrukcji)

1. Identyfikacja i organizacja danych – adresowanie pami ci

a. struktury danych

b. rozpoznawanie typu danej

2. Działania na danych (CPU)

a. kategorie działa i schematy wykonania działa

b. algorytmy działa elementarnych

3. Program i sterowanie jego przebiegiem

a. domniemana i wymuszana kolejno działa

b. przekazywanie sterowania

4. Wspomaganie ochrony danych

Architektura sprz tu (HSA) – organizacja komputera

1. Struktura bloków funkcjonalnych

2. Organizacja pami ci

3. Buforowanie danych

4. Układ sterowania

5. Przetwarzanie współbie ne

A

RCHITEKTURA KOMPUTERÓW

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

ARCH–7

Obszary architektury komputerów

Sfera kompilatora (struktury danych i algorytmy)

• typy danych – umowy i standardy (ASCII, NB, U2, IEEE 754)

• struktury danych i adresowanie → tryby adresowania

• działania i ich cechy

• sterowanie, procedury i funkcje

Sfera wykonania (organizacja i struktury wykonawcze)

• układy arytmetyczne

• organizacja pami ci i buforowanie danych (pami podr czna, kolejki)

• przetwarzanie potokowe i współbie no w trybie data flow

• transmisja danych

Sfera zarz dzania (system operacyjny)

• zarz dzanie procesami i ochrona danych

• pami wirtualna i zarz dzanie pami ci

• przerwania i obsługa zdarze

o

obsługa wyj tków

o

obsługa wej cia i wyj cia

A

RCHITEKTURA KOMPUTERÓW

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

ARCH–8

Dane

kody polece + parametry stanu +

argumenty (dane u ytkownika)

Typy skalarne:

• jako ciowe (enumeration) – cechy obiektu (attribute), kody informacji,

• logiczne (boolean), znakowe (character), opisowe (descriptive);

• nieci głe (discrete), w szczególno ci:

• całkowite (integer) i porz dkowe / naturalne (cardinals / natural),

• pseudo-ci głe (non-discrete), w szczególno ci:

•

zmiennoprzecinkowe (floating-point) – standard IEEE754.

Typy strukturalne – zbiory danych skalarnych lub strukturalnych i obejmuj :

• wektory (vectors) i tablice (arrays) – uporz dkowane zbiory danych,

• ła cuchy (strings) – uporz dkowane ci gi (wektory) znaków,

• rekordy (records), – regularne struktury danych dowolnych typów.

• zestawy (sets) – nieuporz dkowane zbiory danych,

Typy wska nikowe (access) – identyfikuj lokalizacj (adres) obiektu

D

ANE

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

DANE-1

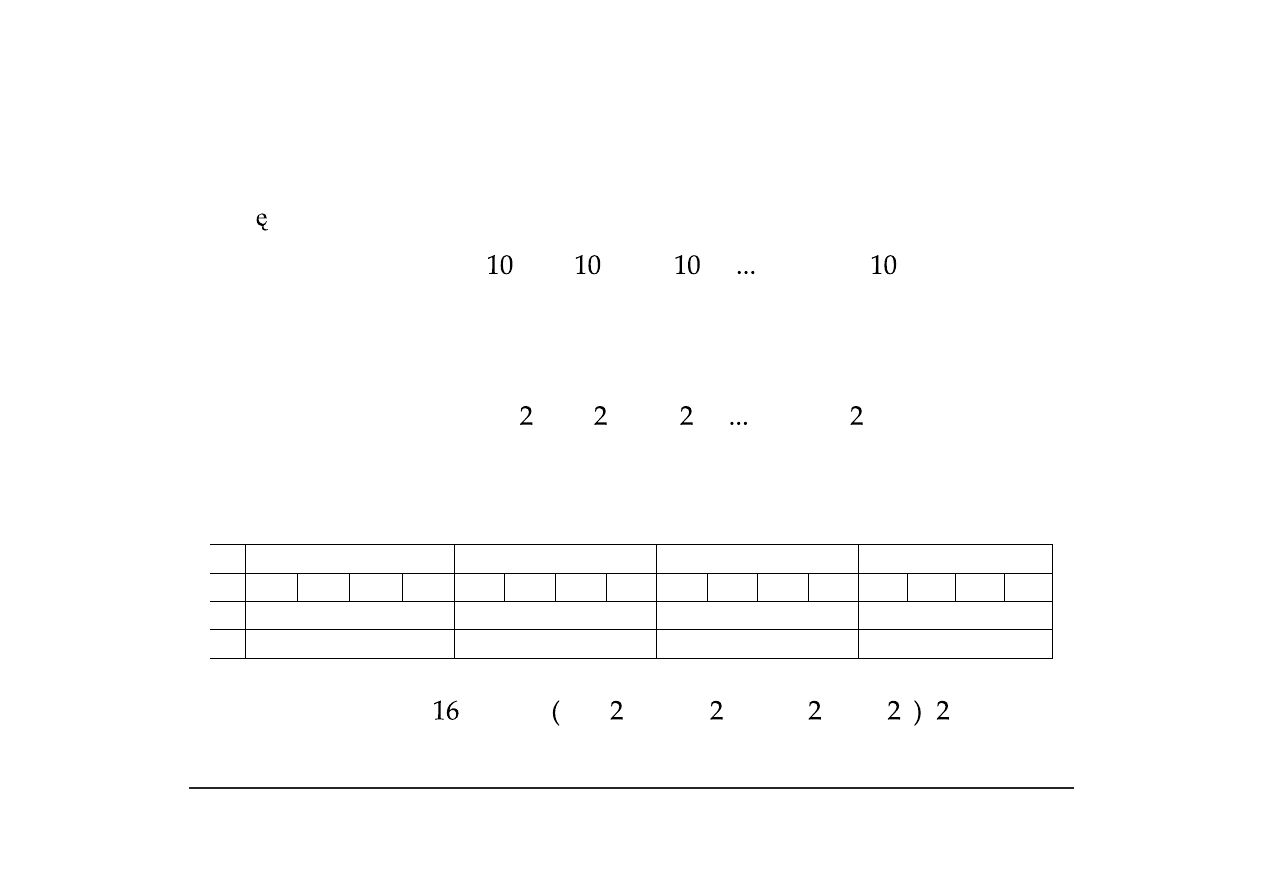

Reprezentacja pozycyjna liczb naturalnych

dziesi tna: 3765

10

= 3

⋅10

3

+7

⋅10

2

+6

⋅10

1

+5

⋅10

0

∑

=

⋅

=

+

⋅

+

⋅

+

⋅

+

=

n

i

i

i

d

d

d

d

d

X

dwójkowa: 101001

2

= 1

⋅2

5

+0

⋅2

4

+1

⋅2

3

+0

⋅2

2

+0

⋅2

1

+1

⋅2

0

∑

=

=

+

⋅

+

⋅

+

⋅

+

=

N

i

i

i

b

b

b

b

b

X

szesnastkowa: DAF5

16

=

13

⋅16

3

+

10

⋅16

2

+

15

⋅16

1

+

5

⋅16

0

=

1101 1010 1111 0101

2

1

1

0

1

1

0

1

0

1

1

1

1

0

1

0

1

…

b

4i+3

b

4i+2

b

4i+1

b

4i+0

b

8+3

b

8+2

b

8+1

b

8+0

b

4+3

b

4+2

b

4+1

b

4+0

b

3

b

2

b

1

b

0

…

h

i

h

2

h

1

h

0

D

A

F

5

∑

∑

=

+

+

+

=

⋅

+

+

+

=

⋅

=

p

i

i

i

i

i

i

p

i

i

i

b

b

b

b

h

X

D

ANE

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

DANE-2

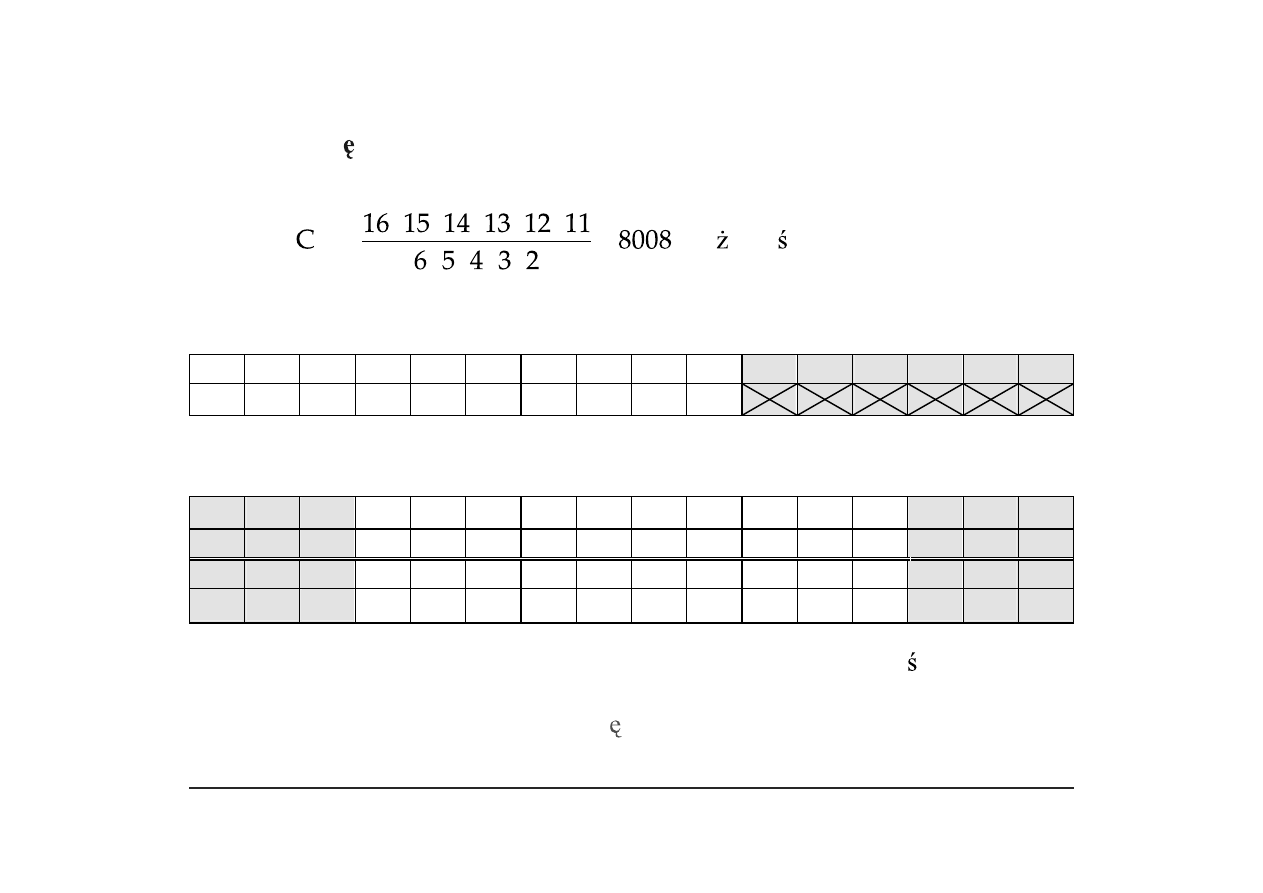

Liczby dziesi tne kodowane dwójkowo

• do binarnego zakodowania jednej z

β

cyfr potrzeba log

2

β

bitów

• jest

=

⋅

⋅

⋅

⋅

⋅

⋅

⋅

⋅

⋅

=

mo liwo ci kodowania cyfr 0…9

Kod BCD (Binary Coded Decimal)

0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111

0

1

2

3

4

5

6

7

8

9

Kod BCD+3 (Excess-3, XS-3) i jego dopełnienie (~1930)

–

–

–

0

1

2

3

4

5

6

7

8

9 –

–

–

0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111

1111 1110 1101 1100 1011 1010 1001 1000 0111 0110 0101 0100 0011 0010 0001 0000

–

–

– 9−0 9−1 9−2 9−3 9−4 9−5 9−6 9−7 9−8 9−9 –

–

–

• samodopełnianie – negacja bitów cyfry → dopełnienie warto ci cyfry

W

NIOSEK

:

W komputerze zapis dziesi tny jest nieefektywny!

D

ANE

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

DANE-3

Reprezentacje liczb całkowitych (ujemnych i dodatnich)

naturalne reprezentacje liczb dodatnich

•

zapis znak-moduł

– osobny symbol znaku – np. „–3427”

o

intuicyjny

zapis, ale

podwójne zero

o

zagmatwane dodawanie, odejmowanie, skalowanie

•

zapis obci

ony

– reprezentacja warto ci X+N

≥ 0 (zakres od –N do …)

o

łatwe porównanie, dodawanie i odejmowanie,

o

trudne mno enie, bardzo trudne dzielenie

•

zapis uzupełnieniowy

– reprezentacja Z=X–Y taka, e Z+Y=X,

o

zachowanie reguł odejmowania/dodawania pozycyjnego

o

reprezentacja systematyczna, łatwo rozszerzalna

•

inne mo liwo ci zapisu

o

cyfry ze znakiem

(ang. signed digit, SD) – przydatny,

łatwa transformacja na zapis uzupełnieniowy

o

ujemna podstawa

–

du a asymetria, trudna arytmetyka

o

zapis dopełnieniowy

–

podwójne zero, skomplikowana arytmetyka

(binarny dopełnieniowy identyczny z binarnym kodem znak-moduł)

D

ANE

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

DANE-4

Reprezentacja uzupełnieniowa

Pozycyjne dodawanie wykonuje si tak:

2735

…000

2735

99…99

…000

99…99

+7329

+

…000

7329

+1

+

…000 00…0

1

=

1

0064

=

…00

1

0064

=

1

00…00

=

…00

1

00…00

– 7329

–

…000

7329

– 1

–

…000 00…0

1

=

0

2735

=

…000

2735

=

0

99…99

=

…000

99…99

W ten sam sposób wykonamy odejmowanie – symbol

1

oznacza „minus jeden”:

0064

=

…000

0064

…

(0)

0064

00..00

=

(0)

00…00

– 7329

–

…000

7329 … –

(0)

7329

– 1

–

(0)00…0

1

=

1

2735

=

…999

2735 … =

(9)

2735

=

1

99..99

=

(9)

99…99

+7329

+

…000

7329 … +

(0)

7329

+1

+

(0)00…0

1

0

0064

…000

2735 … =

(0)

2735

0

99..99

(0)

00…00

Wnioski:

• reprezentacja

liczby przeciwnej

–

wynik odejmowania liczby od zera

• dodawanie i odejmowanie jak w naturalnym systemie pozycyjnym

• zapis liczby mo na rozszerzy lewostronnie na dowoln liczb pozycji

• po dana

symetria

zakresu (wykonalno 0 – X)

D

ANE

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

DANE-5

Liczby wymierne o ustalonej podstawie

Reprezentacja stałoprzecinkowa – liczby wymierne z małego zakresu

• ułamki wła ciwe, np

∑

∑

=

−

−

−

=

=

m

j

j

m

j

m

m

i

i

i

x

x

β

β

β

• skalowane liczby całkowite, np.

∑

∑

−

+

=

+

−

=

=

s

k

s

i

s

i

i

k

i

i

i

s

x

x

β

β

β

– umowny, domy lny współczynnik skalowania s

Reprezentacja zmiennoprzecinkowa – liczby wymierne z du ego zakresu

• zmienna warto współczynnika skali – notacja in ynierska/naukowa, np

3,14159

⋅10

3

, 6,02214179

⋅10

23

, 1,3806505(24)

⋅10

–23

,

– mo liwe pokrycie bardzo du ego zakresu

• wiele reprezentacji tej samej liczby

3,14159

⋅10

0

, 0,314159

⋅10

1

, 314,159

⋅10

–2

• po dana

normalizacja

– np. p cyfr w cz ci całkowitej mno nika

,

E

M

F

β

±

=

warunek normalizacji:

p

p

M

β

β

<

|

|

1

≤

−

D

ANE

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

DANE-6

Binarne formaty zmiennoprzecinkowe

liczba znormalizowana

(p=1 ⇒ wiod cym bitem mno nika M jest zawsze 1)

1

0

),

1

(

2

)

1

(

<

≤

+

−

=

f

f

F

E

s

brak reprezentacji zera !!

naturaln reprezentacj zera jest kod postaci s 00...00 00...00

liczba zdenormalizowana

(ukryty bit „0”) – kod wykładnika E

0

: 00…0

1

0

),

0

(

2

)

1

(

0

<

≤

+

−

=

f

f

F

E

s

wskazana równomierno pokrycia przedziału w pobli u

0

)

001

...

00

.

0

1

(

2

)

1

...

111

,

0

0

(

2

)

0

1

(

2

min

0

min

+

≤

+

−

+

E

E

E

Kody specjalne

–

kod wykładnika: 11…1

• (f = 0) niesko czono ci ±∞,

• (f ≠ 0) nie-liczby, NaN – wyniki, które nie s liczbami

D

ANE

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

DANE-7

Format zmiennoprzecinkowy IEEE 754/854

bit ukryty

s

e e e ... e e e e b b b b ... b b b b b b b b b b b b b

znak E – wykładnik (+N)

f

– cz

ułamkowa modułu znacznika |M|

1 bit

k

bitów

m

bitów

SINGLE (32b) – [s

31

|| E

30:23

|| f

22:0

]

DOUBLE (64b) – [s

63

|| E

62:52

|| f

51:0

]

k = 8, m = 23

k = 11, m = 52

–2

7

+ 2 = – 126

≤ E ≤ 127 = 2

7

– 1

–

2

10

+ 2 = – 1022

≤ E ≤ 1023 = 2

10

– 1

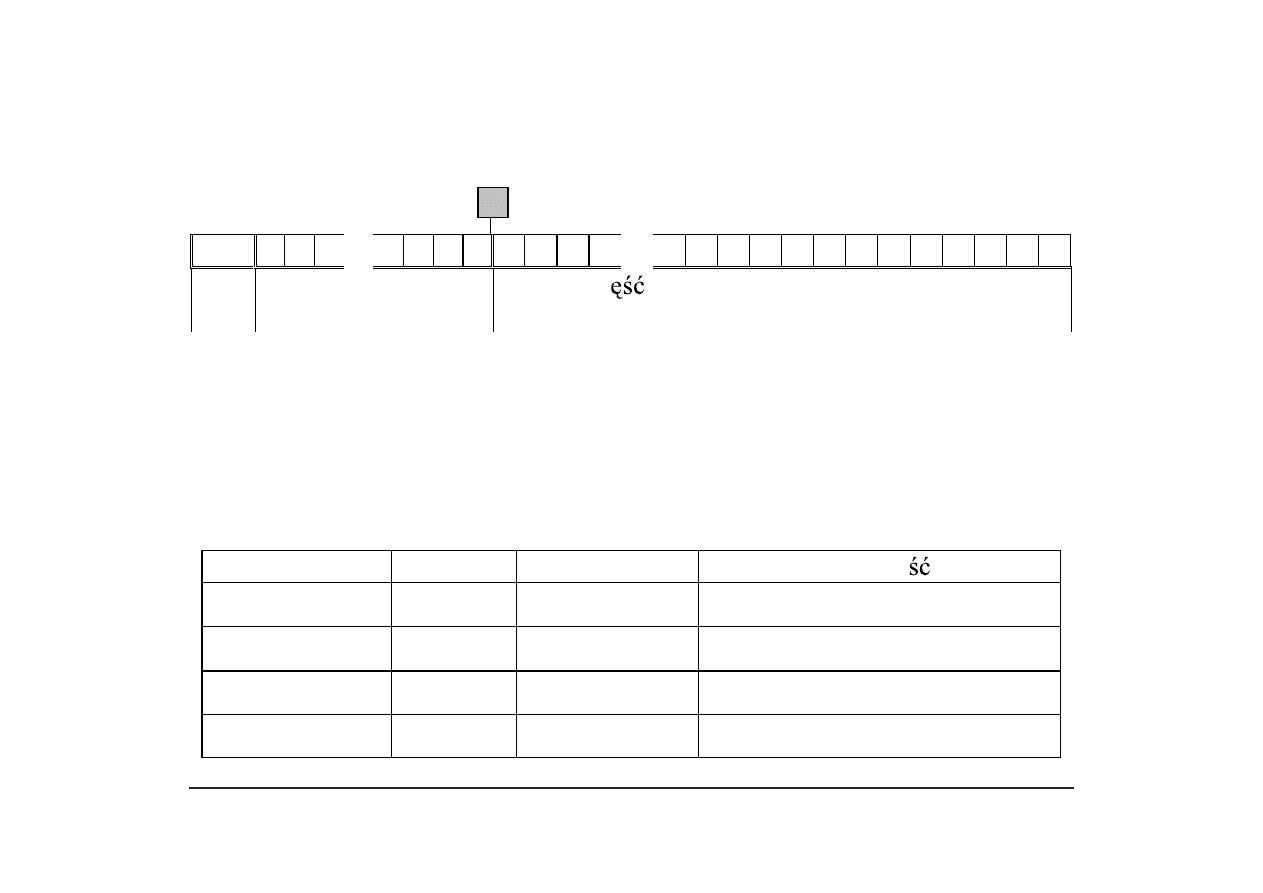

Wzorce kodów obiektów standardu IEEE 754

Wykładnik

Ułamek

Kod binarny

Wielko

E

0

=

0...00

f

s

0...00 b...bb

0

2

)

0

(

)

1

(

E

s

f

F

+

−

=

E

min

≤ E ≤ E

max

f

s e...ee b...bb

E

s

f

F

2

)

1

(

)

1

(

+

−

=

E=

1...11

f

= 0

s

1...11 0...00

± ∞

E=

1...11

f

≠ 0

s

1...11 b..bb

NaN

D

ANE

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

DANE-8

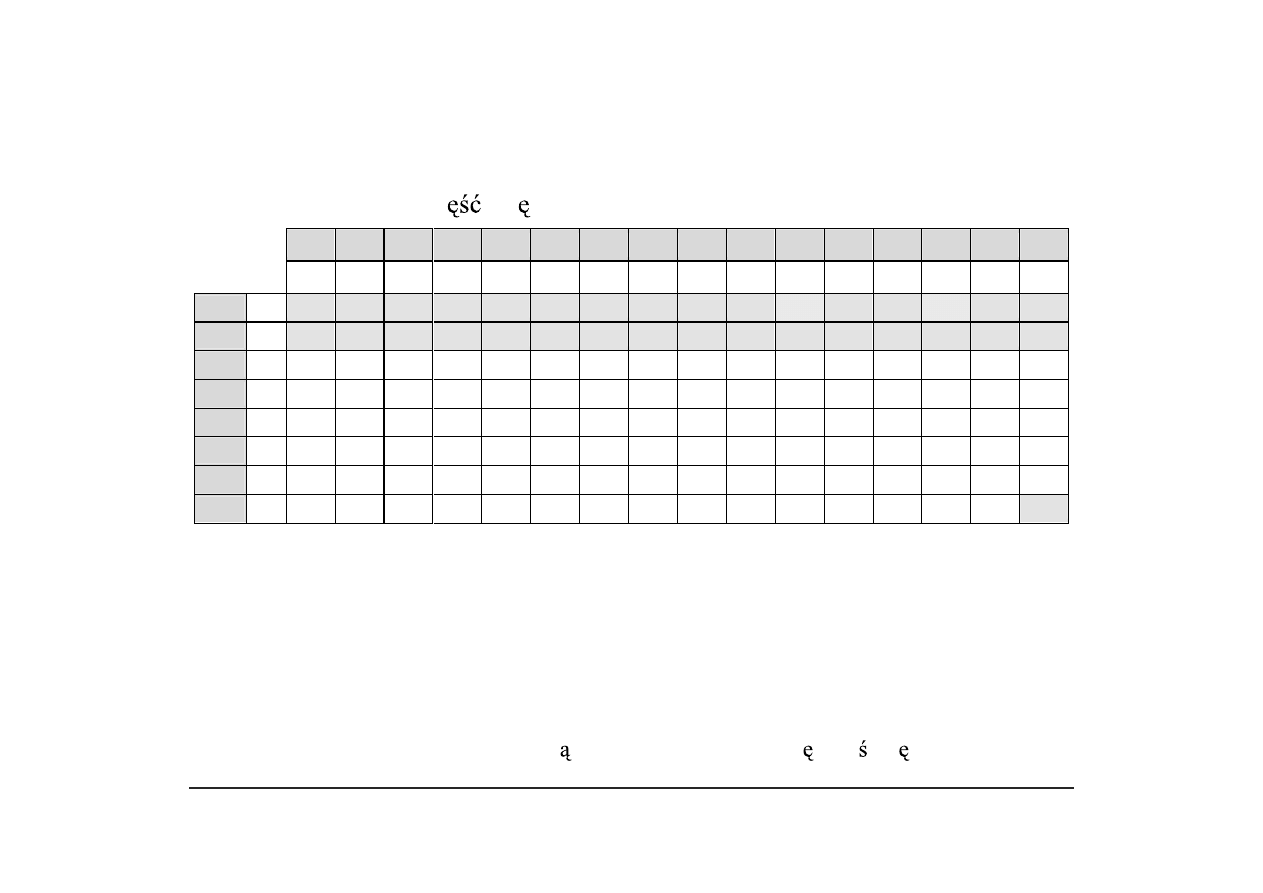

Kod ASCII (American Standard Code for Information Interchange)

Kod ASCII (cz

mi dzynarodowa) = 0 | | ISO-7 (CCITT No 5)

llll

0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111

hhhh

H

L

0

1

2

3

4

5

6

7

8

9

A B

C D E

F

0000

0

NUL SOH STX ETX EOT ENQ ACK BEL BS HT LF

VT FF

CR SO SI

0001

1

DLE DC1 DC2 DC3 DC4 NAK SYN ETB CAN EM SUB ESC FS

GS RS US

0010

2 SP !

”

#

$

%

&

‘

(

)

*

+

,

–

.

/

0011

3 0

1

2

3

4

5

6

7

8

9

:

;

<

=

>

?

0100

4 @ A B

C

D

E

F

G

H

I

J

K

L

M N

O

0101

5 P

Q

R

S

T

U

V

W X

Y

Z

[

\

]

^

—

0110

6 `

A

b

c

d

e

f

g

h

i

j

k

l

m

n

o

0111

7 p

q

r

s

t

u

v

w

x

y

z

{

|

}

~

DEL

NUL nullify

SOH – start of header

STX – start of text

ETX – end of text

EOT – end of transfer

ENQ – enquire

ACK – acknowledge

BEL – bell

BS – backspace

HT – horizontal tab

LF – line feed

VT – vertical tab

FF – form feed

CR – carriage return

SO / SI – shift out i in

DLE – data link ESC

DC# – data control

NAK – negative ACK

SYN – synchronize

ETB – end of text block

CAN – cancel

EM – end of medium

SUB – substitute

ESC – escape

FS – file separator

GS – group separator

RS – record separator

US – unit separator

UNICODE – kod 16-bitowy, obejmuj cy znaki diaktryczne wi kszo ci j zyków

D

ANE

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

DANE-9

Kod ASCII – regularno ci

Konwencje asemblera:

‘

’

– kod ASCII znaku/litery

(1bajt)

”tekst” – kod ASCII kolejnych znaków tekstu

(ci g bajtów w konwencji BE)

Kody cyfr dziesi tnych i liter alfabetu łaci skiego s systematyczne:

kody cyfr dziesi tnych: (

@

10

= bbbb

2

=

@

16

– warto cyfry):

0011 bbbb

2

=

3

@

16

– (‘7’ = 37

16

= 0011 0011

2

)

3

@

0 0 1 1 … … … …

kody liter (bbbbb – 5-bitowy nr litery w porz dku alfabetu łaci skiego):

du ych: 010 bbbbb (‘A’ = 010 00001 = 41

16

),

małych: 011 bbbbb (‘z’

=

011 11010 = 7A

16

)

0 1 c … … … … …

D

ZIAŁANIA PROCESORA

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

DZIAŁANIA-1

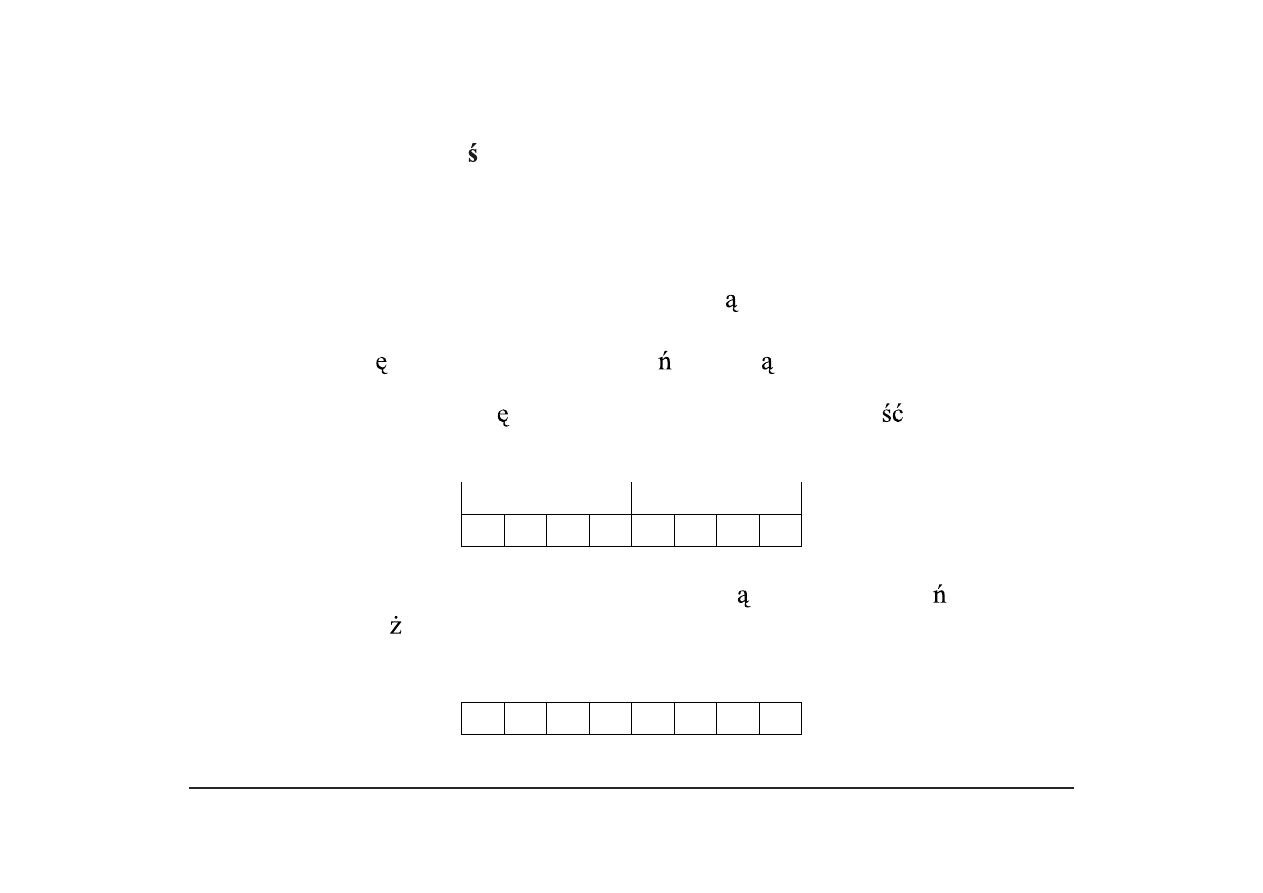

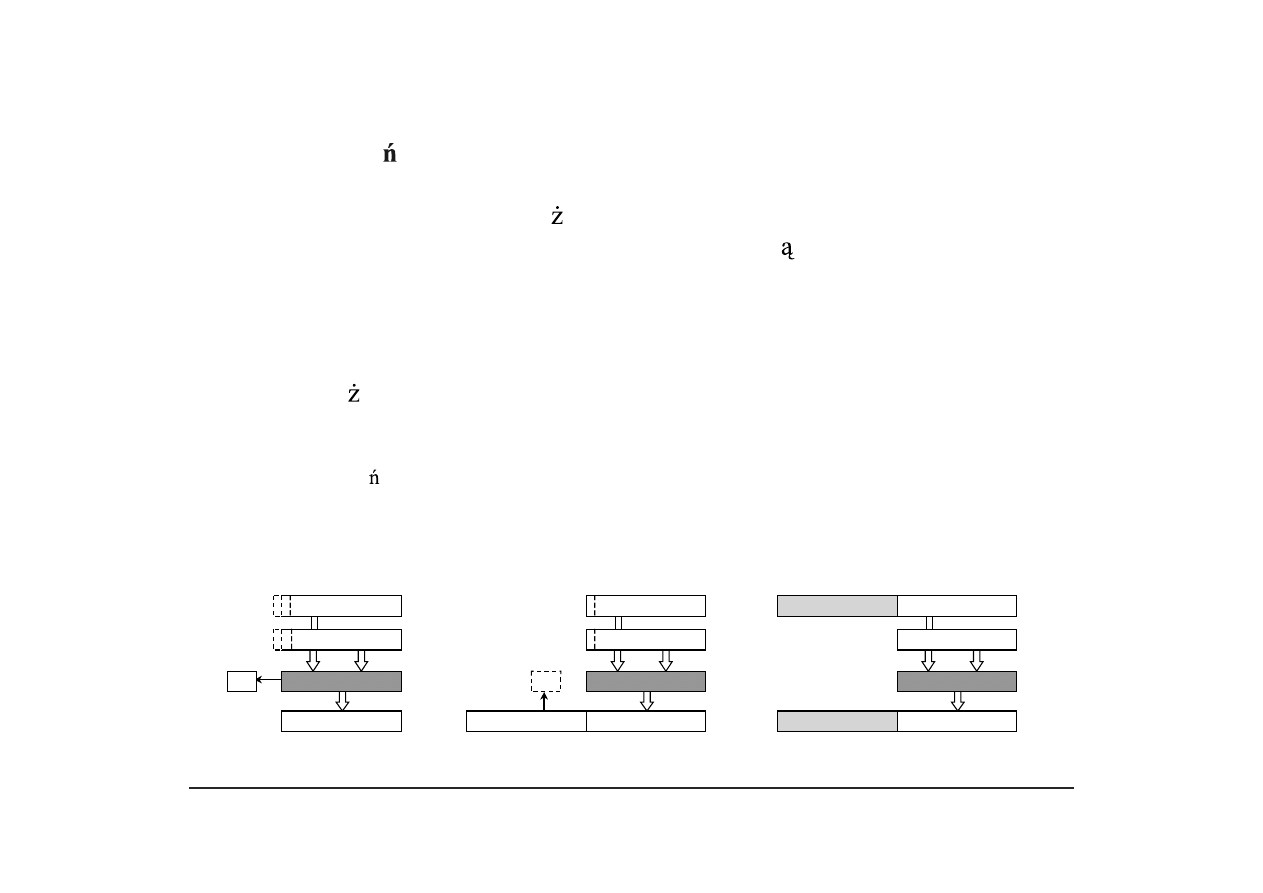

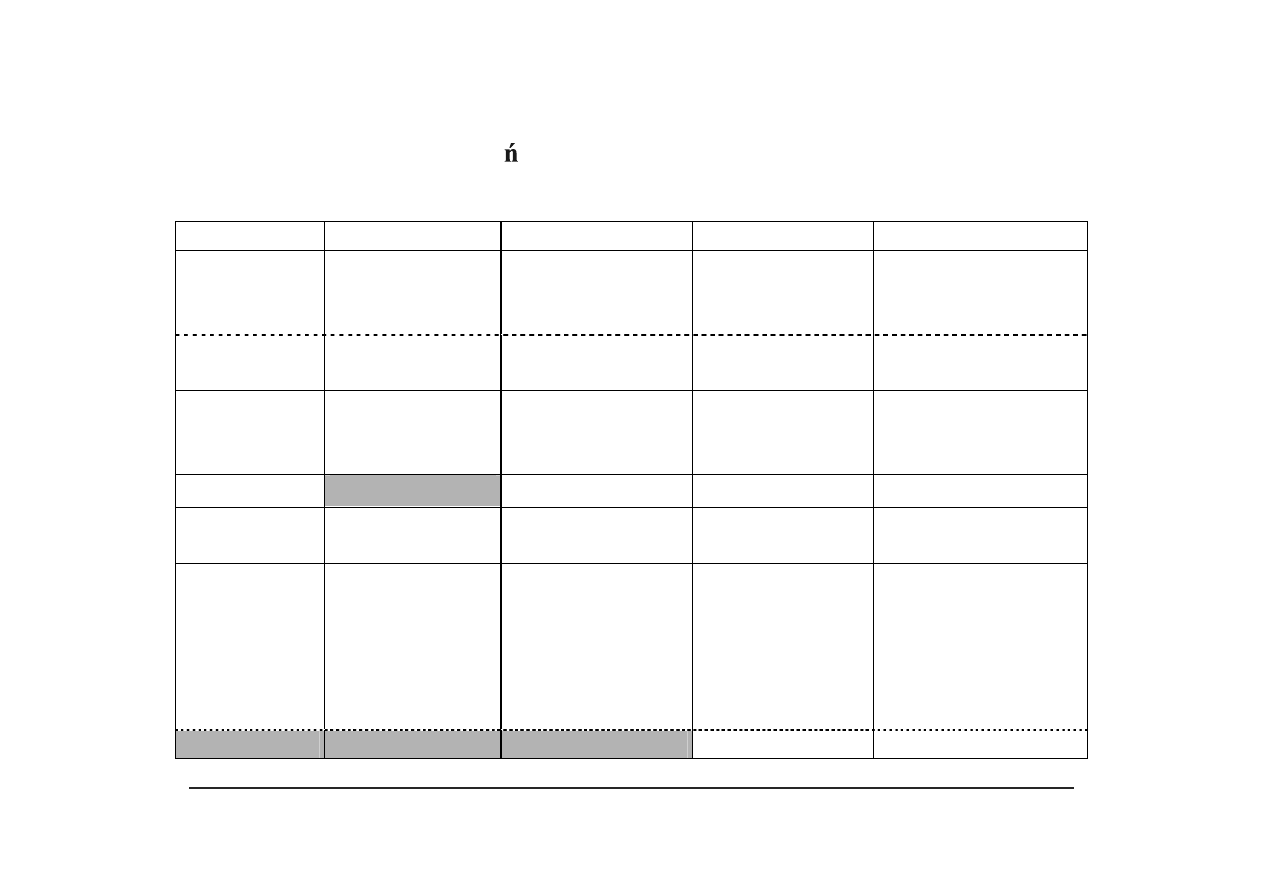

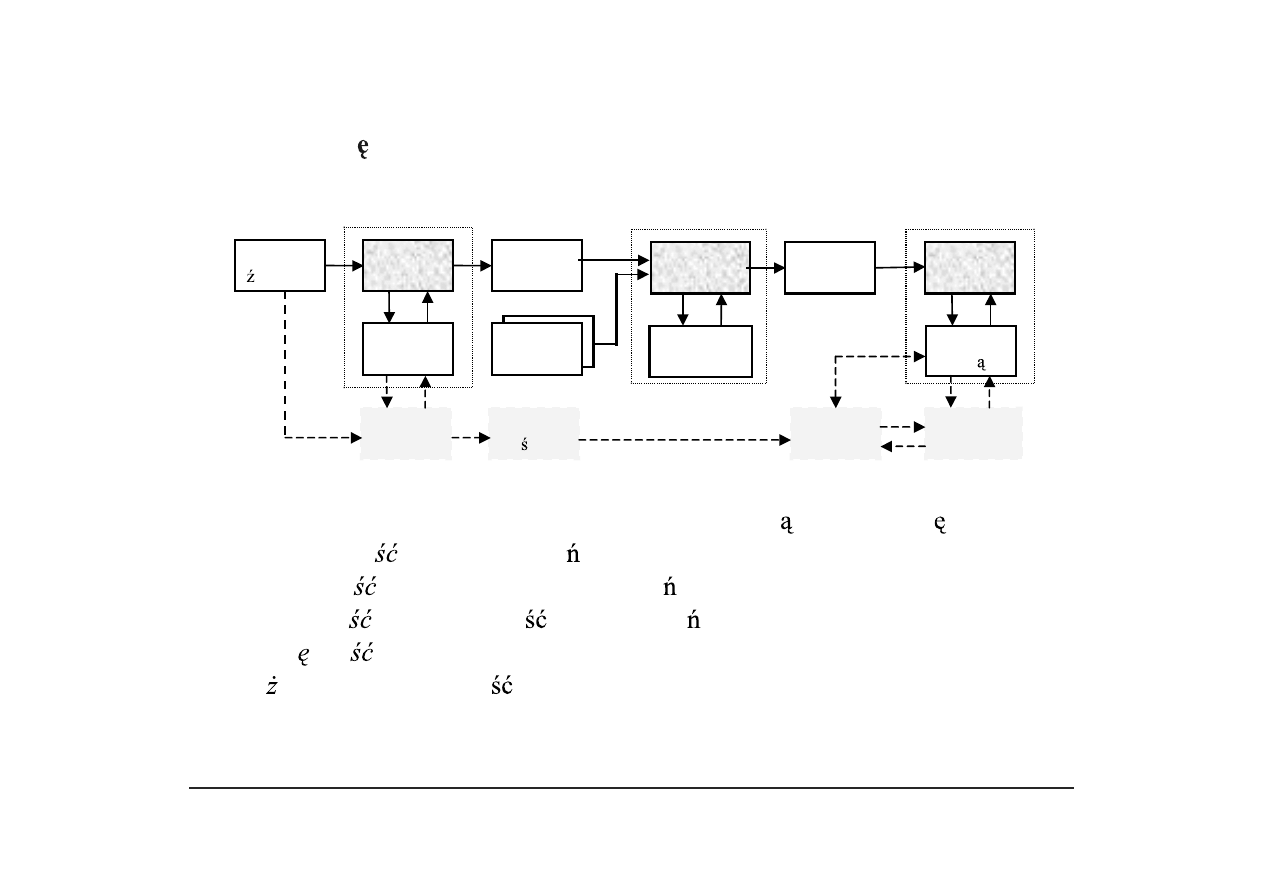

Elementarne działania na danych (1)

zakres

pobranie

rozpakowanie

dekodowanie

argument(y)

wynik

kod

upakowanie

przechowanie

formowanie

Klasyfikacja działa i fazy ich wykonania (format = struktura)

D

ZIAŁANIA PROCESORA

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

DZIAŁANIA-2

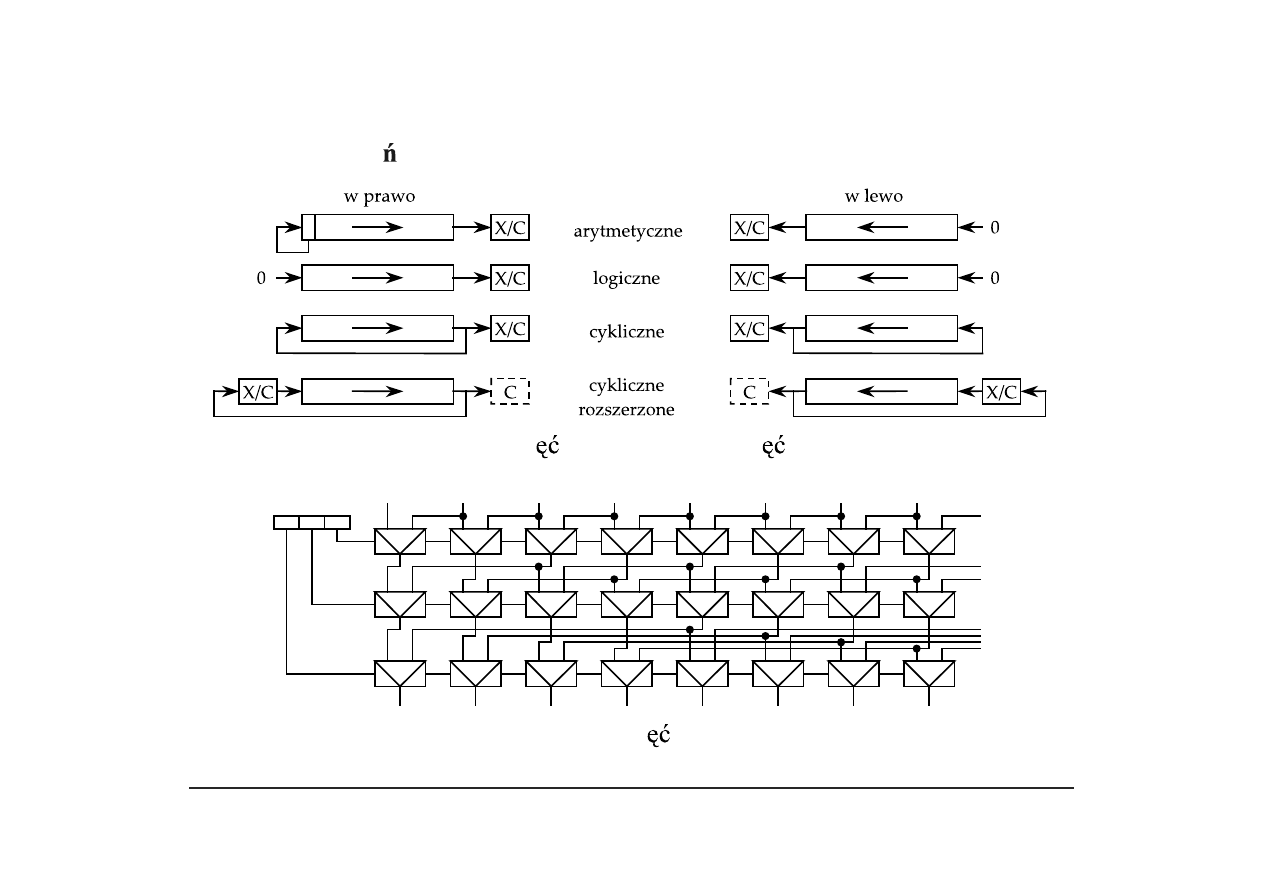

Elementarne działania na danych (2)

kopiowanie

• niszcz ce, nieodwracalne

• kopiowanie bloków – ryzyko zniszczenia ródła (kolejno przesła )

• wymiana (exchange) (tak e przestawianie (swap)) – odwracalne

zmiana formatu

– przestawianie i powielanie bitów słowa

• systematyczne przemieszczenie bitów

o

zwykłe – przesuni cie arytmetyczne lub logiczne

o

cykliczne – rotacja prosta i rozszerzona

• rozszerzanie (wydłu anie) kodu liczby

• konwersje formatów zmiennoprzecinkowych

• przemieszczenie pól (rekordów) – przestawienie (swap)

• przeplot rekordów

zmiana kodu

– przekodowanie słowa bez wykonania działa ALU

• konwersje zapisu liczb (zmiennoprzecinkowy ↔ stałoprzecinkowy)

• … (przekodowanie przez tablic przekodowa )

• … (upakowanie i rozpakowanie kodu BCD)

D

ZIAŁANIA PROCESORA

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

DZIAŁANIA-3

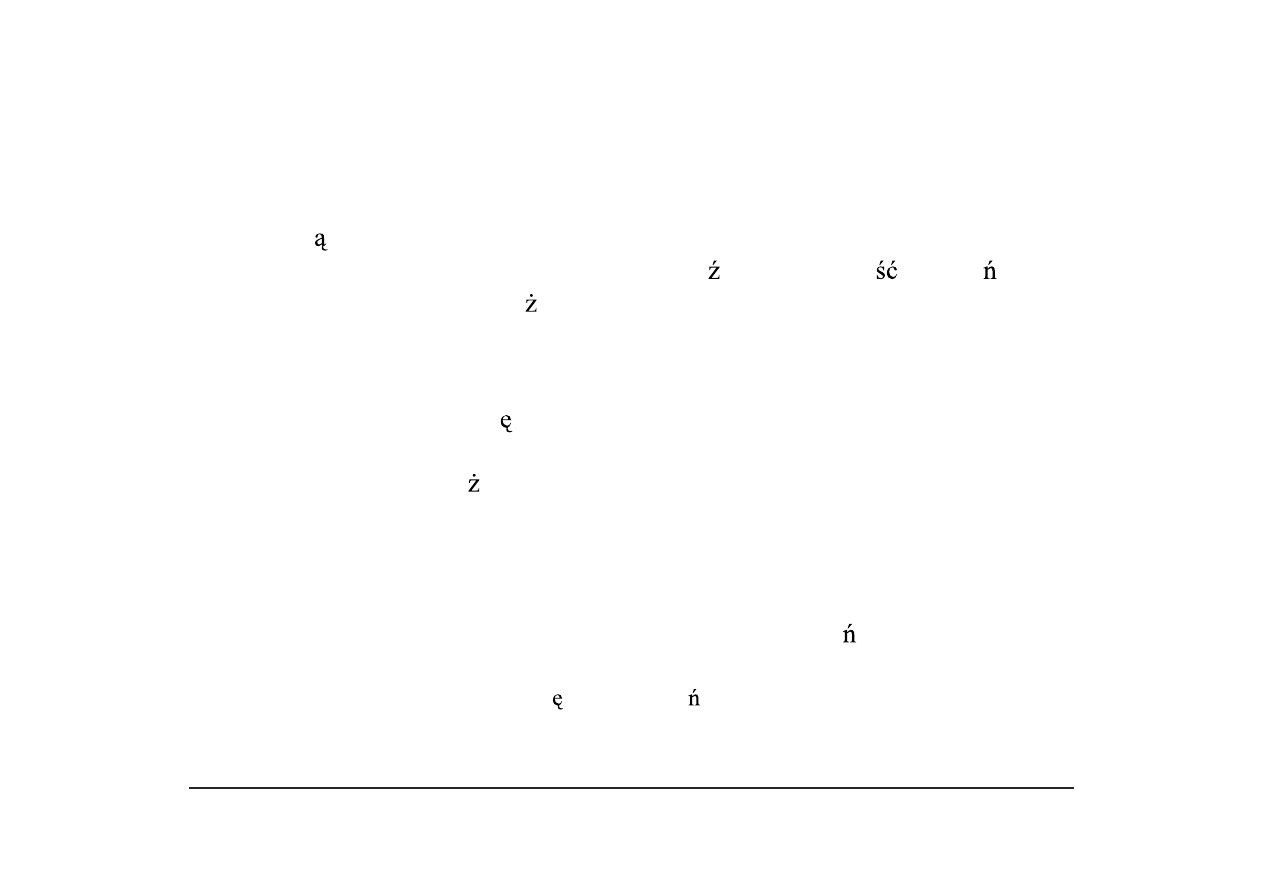

Schematy działa – kopiowanie

source

destination

Kopiowanie zwykłe (mov %eax, %edx)

Wymiana danych (xchg %ebx, lok)

(src)

(src)

(src)

(dst)

(dst)

(dst)

Schemat transferu bloku słów (movs src, dst)

D

ZIAŁANIA PROCESORA

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

DZIAŁANIA-4

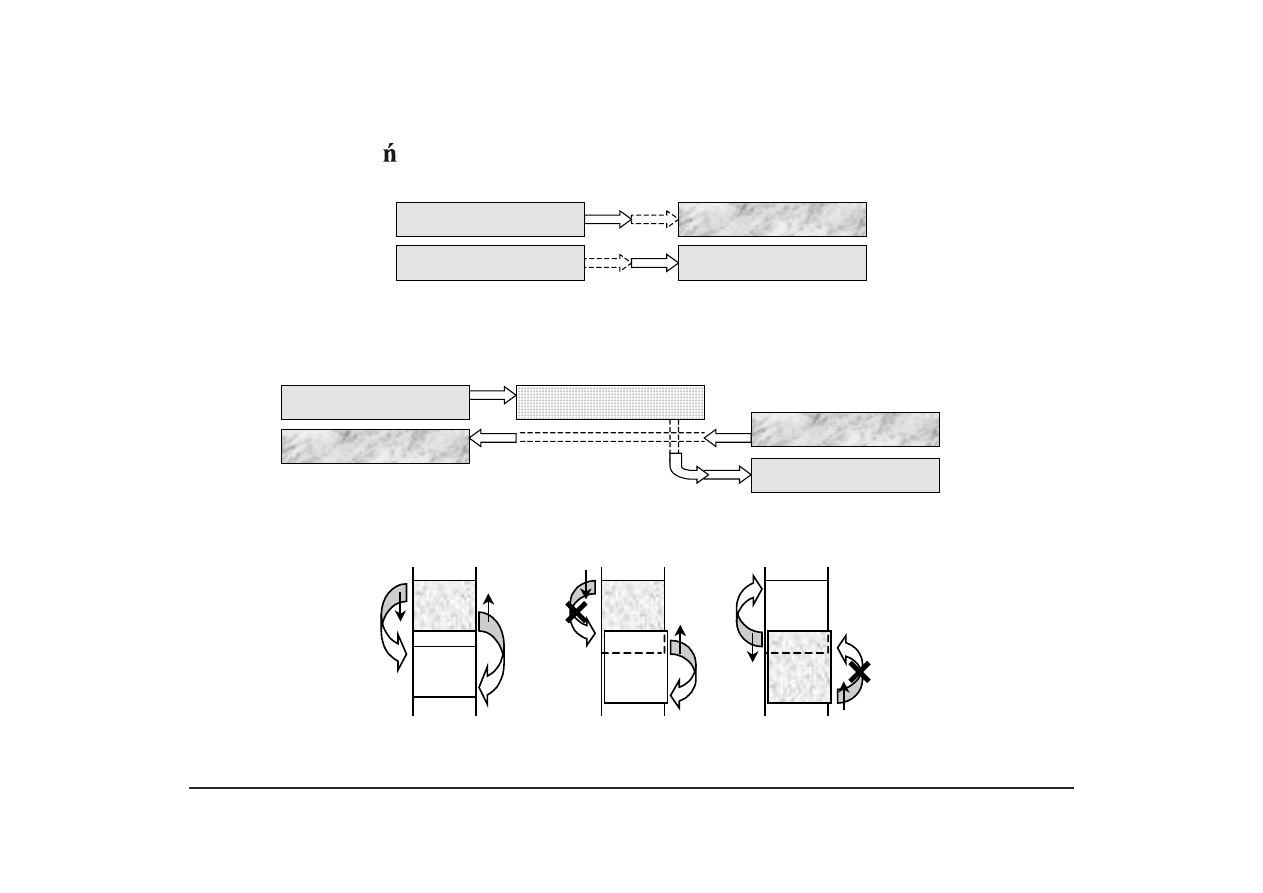

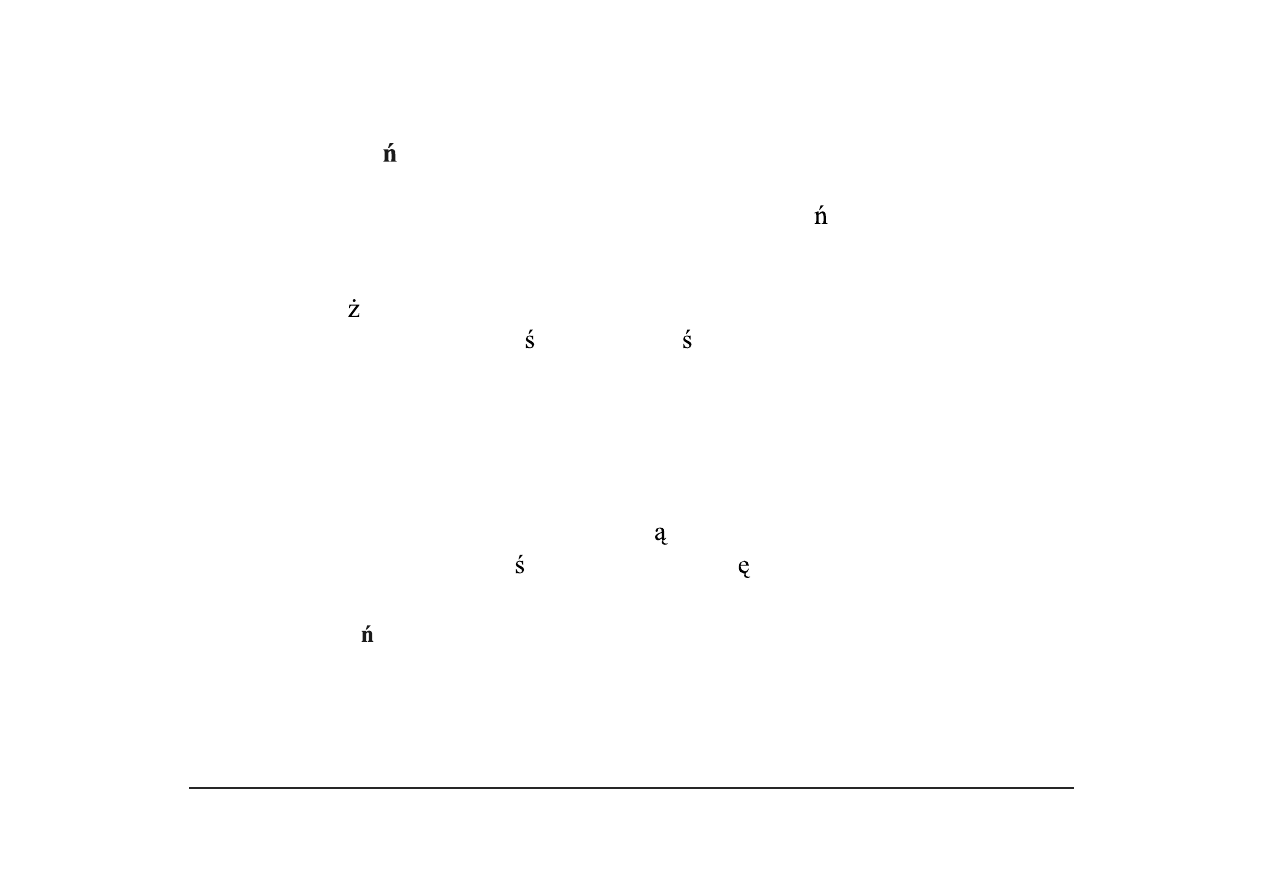

Schematy działa – zmiana formatu (1)

Schematy przesuni i rotacji (przesuni cyklicznych)

n

Kombinacyjny układ przesuni (w lewo) (barrel shifter)

D

ZIAŁANIA PROCESORA

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

DZIAŁANIA-5

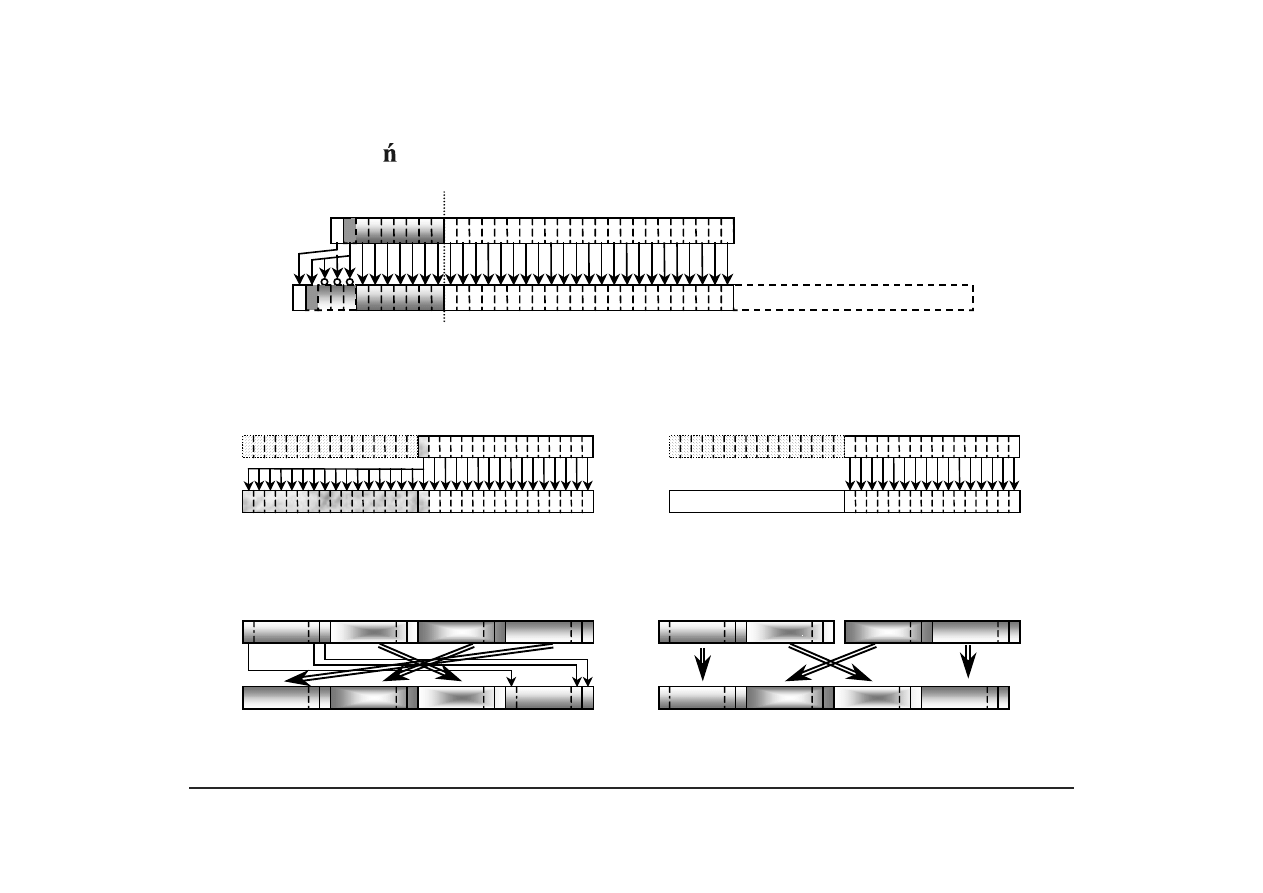

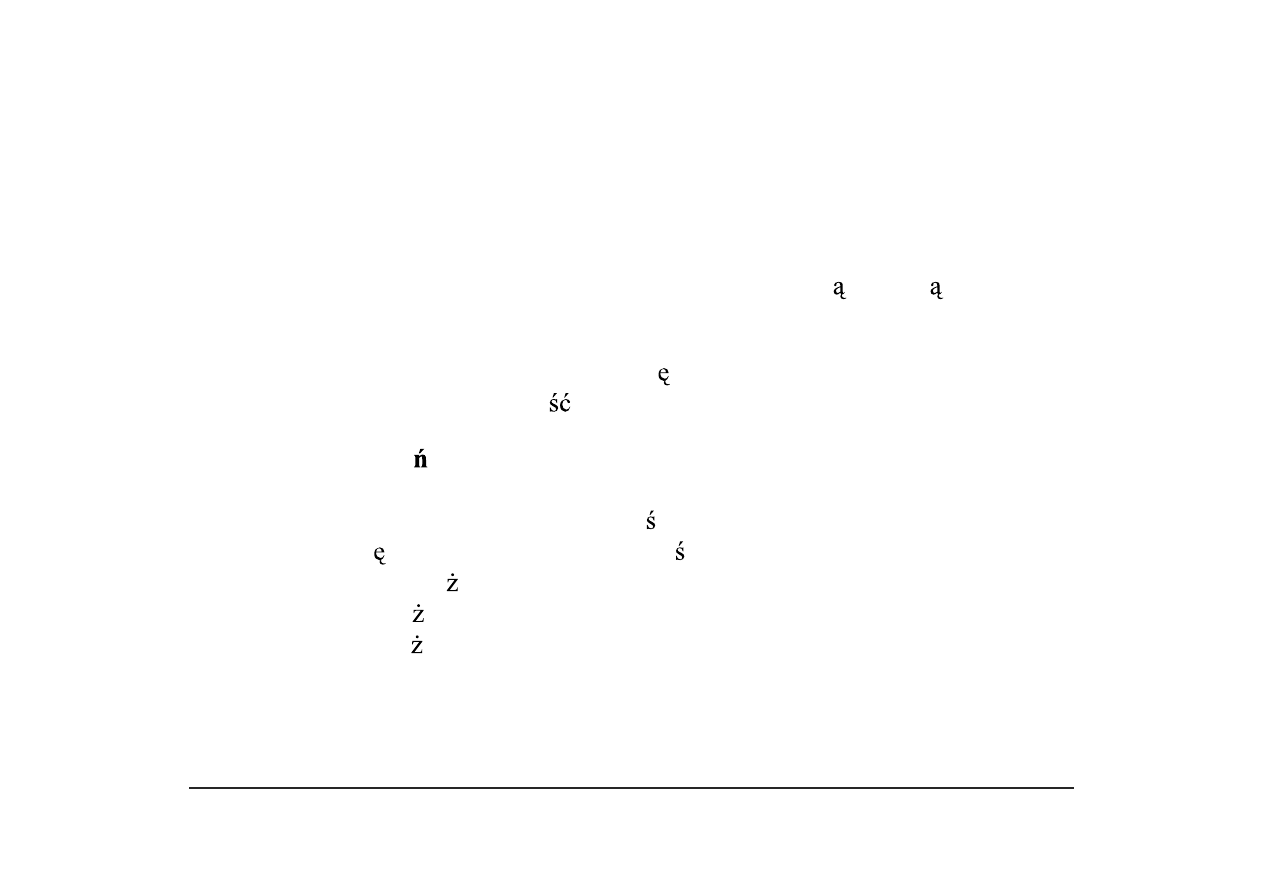

Schematy działa – zmiana formatu (2)

s

e

f

0 0 0 … … … … … … … . 0 0 0

Konwersja formatu zmiennoprzecinkowego (

o

– negowanie bitu)

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

movsx …

movzx

…

Znakowe (movsx …) i zerowe (movzx …) rozszerzenie kodu

Przestawienie i przeplot rekordów

D

ZIAŁANIA PROCESORA

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

DZIAŁANIA-6

Arytmetyka

Teoria liczb – wła ciwo ci liczb naturalnych

Sposoby obliczania wyniku podstawowych działa arytmetycznych

•

odejmowanie

i dodawanie (... mo na wykona przez odejmowanie)

• mno enie – sekwencyjne lub równoległe

o

skalowanie – mno enie przez całkowit pot g podstawy (bazy)

• dzielenie – sekwencyjne lub mno enie przez odwrotno dzielnika

• wyci ganie pierwiastka kwadratowego – sekwencyjne

Arytmetyka klasyczna

– dowolny rozmiar liczb (rozszerzenia niesko czone)

✧

problem – jak to zrobi ? -

algorytm

zapewniaj cy

F

wykonalno

oblicze

Arytmetyka komputerowa

– ograniczony zakres argumentów

✧

problem –

algorytm

zapewniaj cy

F

dokładno

wyniku – utrzymanie dokładno ci

F

poprawno

- kontrola zakresu

F

szybko

wykonania – zrównoleglenie działa

D

ZIAŁANIA PROCESORA

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

DZIAŁANIA-7

Dokładno i szybko oblicze

Dodawanie, odejmowanie, mno enie

• argumenty dokładne – wynik tak e dokładny

• argumenty przybli one ze znan dokładno ci :

– łatwa kontrola dokładno ci wyniku,

– ryzyko kumulacji bł dów przybli e

Dzielenie, obliczanie pierwiastka kwadratowego

• wynik zwykle niedokładny (nawet gdy argumenty s dokładne)

• konieczna kontrola dokładno ci wyniku

W

NIOSEK

:

Nale y najpierw wykona działania dokładne.

Obliczenia: dost pne działania składowe + algorytm (przepis)

Ze wzgl du na szybko

zło one działania

składowe warto realizowa układowo a nie programowo

D

ZIAŁANIA PROCESORA

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

DZIAŁANIA-8

Schematy działa – jednostka stałoprzecinkowa (IU)

• działania logiczne – niezale ne na poszczególnych bitach słowa

o

iloczyn (

AND

), suma (

OR

) i suma wykluczaj ca (

XOR

)

o

iloczyn z argumentem zanegowanym (

ANDN

) – zamiast (

NOT

)

• arytmetyka stałoprzecinkowa – realizacja arytmetyki pozycyjnej

o

dodawanie, odejmowanie, porównanie

o

mno enie

o

dzielenie i obliczanie pierwiastka kwadratowego

• ła cuch bitów odzwierciedla zapis pozycyjny lub uzupełnieniowy

• interpretacja kodu warunkowego (CC):

– post-factum, wg potrzeby (Pentium),

– wskazana w kodzie rozkazu (PowerPC)

rozszerzenie?

argument 1

argument 2

+/–/?

suma / ró nica

CC

mno na

mno nik

*

iloczyn dolny

CC

iloczyn górny

dzielna – l

dzielnik

/

iloraz

dzielna – h

reszta

D

ZIAŁANIA PROCESORA

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

DZIAŁANIA-9

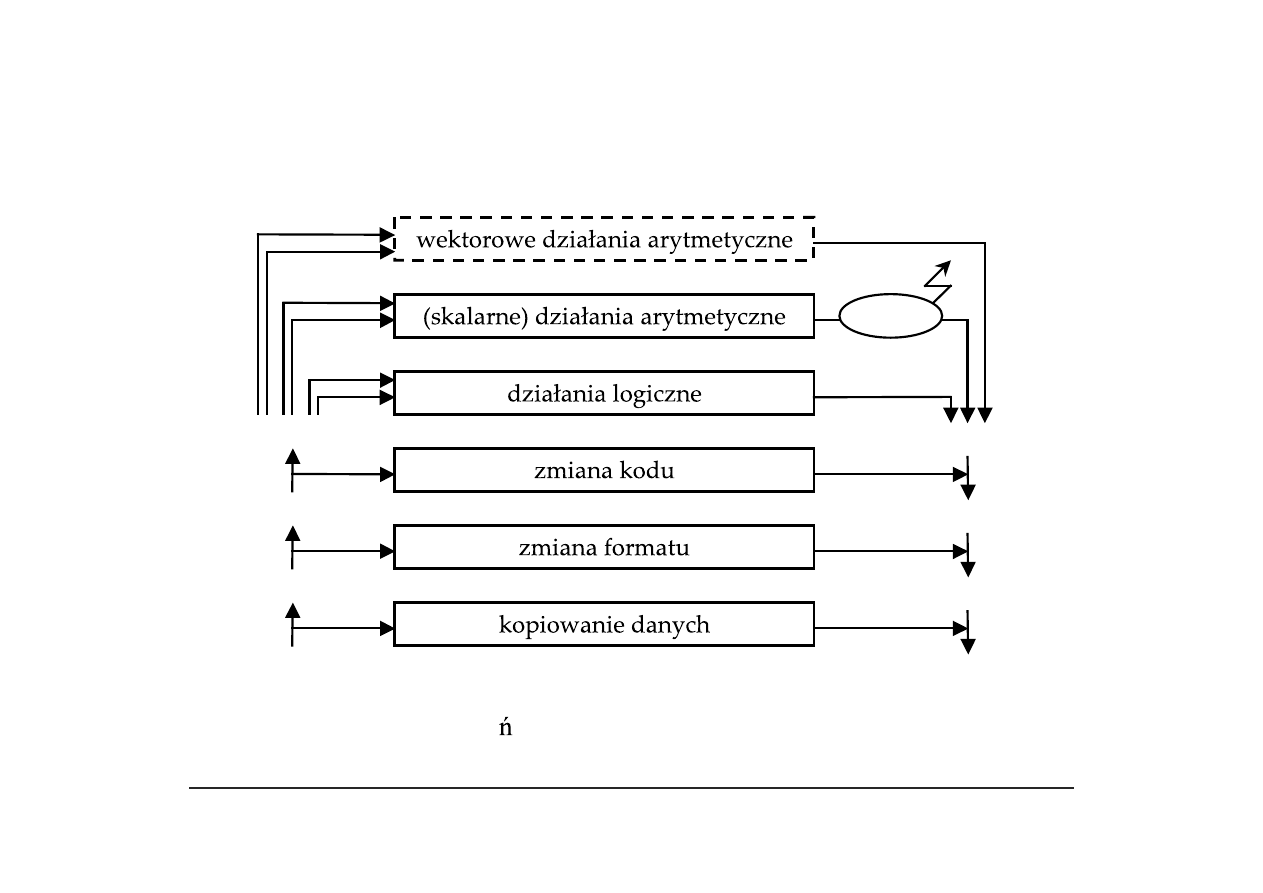

Schematy działa – jednostka zmiennoprzecinkowa (FPU)

• arytmetyka zmiennoprzecinkowa – kategorie działa :

o

porównanie

o

dodawanie i odejmowanie,

o

mno enie i dzielenie

o

obliczanie odwrotno ci i odwrotno ci pierwiastka kwadratowego

o

obliczanie funkcji elementarnych

etapy działania:

• uformowanie argumentów

• wykonanie działania na wykładnikach i ułamkach

• normalizacja – uformowanie i zokr glenie wyniku

• weryfikacja poprawno ci – sygnalizacja bł dów

Schematy działa – arytmetyka nasyceniowa

• arytmetyka nasyceniowa – wektorowe działania arytmetyczne

o

jednakowe działania na wszystkich polach (rekordach) danych

o

dyskryminacja (nasycanie) wyniku w ustalonych granicach

D

ZIAŁANIA PROCESORA

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

DZIAŁANIA-10

Model programowy procesora

wykaz rejestrów i ich cechy

§

rejestry ogólnego przeznaczenia GPR (general purpose registers)

§

zmiennoprzecinkowe – FPR (na przykład fr0, fr1, …)

§

rejestry specyficzne – sterowanie, zliczanie, powi zania w tków

tryby adresowania

§

sposoby tworzenia adresu w pami ci (głównej)

§

ograniczenia (niespójno architektury)

specyfikacja działa

§

sposób tworzenia wyniku i jego syndromów

o zasady (postulat ortogonalno ci)

o odst pstwa od zasad (niespójno ci architektury)

§

ograniczenia u ycia argumentów

o nakaz u ycia (wg specyfikacji lub przez domniemanie)

o zakaz u ycia (wg specyfikacji)

§

interpretacja argumentów

o interpretacja kodów 0-1 jako liczb

o sposób tworzenia i przekształcania stałych (rozszerzenia kodu)

D

ZIAŁANIA PROCESORA

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

DZIAŁANIA-11

Konwencje opisu działa

składnia

j zyki symboliczne:

wynik

= argument-a

DZIAŁANIE

argument-b

DZIAŁANIE

…

albo

wynik

=

FUNKCJA

(argument-a, argument-b,…)

asembler (poziom maszyny rzeczywistej):

mnemonik argument-a, argument-b,…,

wskazywanie argumentów

j zyki symboliczne: zmienne, stałe (obiekty)

asembler: słowa w pami ci, rejestry procesora, stałe

rejestry

:

RISC – rejestry numerowane (R

0

, R

1

, ..., R

16/32...64

/ FPR

0

,..., FPR

7/15

)

CISC – rejestry nazywane:

MC68x00 – dane: d0,…, d7– 8/16/32-bitowe (#.b/ #.w/ #.d)

– adresy a0,…,a7 – 16/32-bitowe

IA-32

– eax, ebx, ecx, edx, esi, ebp, esp, esi, edi

D

ZIAŁANIA PROCESORA

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

DZIAŁANIA-12

Mnemoniczny zapis działa na poziomie architektury listy rozkazów (ISA)

(jednostka stałoprzecinkowa)

Działanie

x86/Pentium

Intel

MC680x0

Motorola

R2000

MIPS

PowerPC 6xx

Kopiowanie

mov, (cmovcc)

xchg,

bswap

move, clr,

exg,

swap

move, mf, mto,

lbu, lhu, lwu, la

sb, sh, sw

lwz, lfs,…

stw, stfs,…

skoki

* jmp, call,

jmp, jsr, bra,

j, b,

b, ba,

jcc, loop

bcc, dbcc

bcc

bc, bclr, bcctr

Zmiana

formatu

shl, shr, sar,

rol, ror, rcl, rcr

movsx, movzx

lsl, lsr, asl, asr,

rol, ror, roxr, roxl,

sext, zext

sll, sra, srl,

rol, ror,

lb, lh, lw

sle, slw, sre, srw,

rlmi, rrib,

extsb, extsh, lbz, lhz

Zmiana kodu xlat, aad, aam

Działania

logiczne

and, or, xor, not,

test, setcc

and, or, eor, not,

tas, scc

and, or, xor, nor,

not, scc

and, nand, or, nor,

xor, eqv, cmpl

Działania

arytmetyczne

add, adc,

sub, sbb,

mul, imul,

div, idiv,

neg,

cmp

add, adc,

sub, sbb,

muls, mulu,

divs, divu,

neg, negx,

cmp

add, addu,

sub, subu,

mul, mulo, mult,

div, divu, rem,

neg, negu

add, addc, adde,

sub, subc, sube,

mul, mullwu,

div, divw,

neg, abs, nabs,

cmp

(arytm. dzies) daa, das

abcd, sbcd, nbcd

D

ZIAŁANIA PROCESORA

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

DZIAŁANIA-13

Model programowy 80x86/Pentium

model programowy – rejestry

(danych) a, b, c, d w wersjach:

• 8-bitowych #h, #l (al, ah, bl, bh, cl, ch, dl, dh)

• 16-bitowych #x (ax, bx, cx, dx)

• 32-bitowych e#x (eax, ebx, ecx, edx)

• 64-bitowych r#x, #l (rax, rcx, rdx, rbx / r0, r1, r2, r3, r8,…,r15)

(blokowe – mm0,…,mm7, xmm0,…xmm7)

(adresowe) w wersjach:

• 16-bitowych (si, di, bp, sp)

• 32- bitowych (esi, edi, ebp, esp)

• 64-bitowych (rsp, rbp, rsi, rdi / r4, r5, r6, r7)

segmentowe (adres bloku)

• 16-bitowe (cs, ds, es, fs, gs, ss)

specyficzne – flagi (kody warunkowe), sterowanie

D

ZIAŁANIA PROCESORA

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

DZIAŁANIA-14

Adresowanie 80x86/Pentium

rejestry

– przez wskazanie (specyfikacj )

konwencja domniemywania

:

• rejestr akumulatora (al, ax, eax, rax, dx:ax, edx:eax) – mul /div

• zliczanie (cx, ecx, rcx) – loop, movs, cmps

adresowanie pami ci

tryb adresowania

– składowe adresu i sposób obliczania

80x86/Pentium – segment:[ tryb adr.],

podstawowy 8086 – dozwolone tylko zestawienia:

seg:[bx|bp+si|di+przemieszczenie], np. es:[bx+si+dest]

seg = cs, ds, es, ss

rozszerzony 80386 – jedno ograniczenie (baza

≠ esp):

seg:[baza+indeks+przemieszczenie], np. ds:[eax+4*ebx+dest]

seg = cs, ds, es, fs, gs, ss

baza|indeks = eax, ebx, ecx, edx, esi, edi, ebp, esp

D

ZIAŁANIA PROCESORA

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

DZIAŁANIA-15

Asembler 80x86/Pentium

TASM, MASM – segmentowy model pami ci, składnia Intel (...C++)

as /gcc

– liniowy model pami ci, składnia AT&T (Linux/UNIX)

Instrukcje procesora

Działania podstawowe

– arytmetyczne i logiczne

– przeformatowanie

– kopiowanie danych

– sterowanie – rozgał zienia i skoki

Instrukcje pomocnicze:

– identyfikacja procesora (CPUID) i specyfikacja wersji

– odczyt licznika cykli (RDTSC)

Dyrektywy

(pseudoinstrukcje)

Dyrektywy organizacyjne (dla kompilatora i linkera)

Definicje stałych

Deklaracje zmiennych

Rezerwacja bloków (buforów) pami ci

Makrooperacje

D

ZIAŁANIA PROCESORA

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

DZIAŁANIA-16

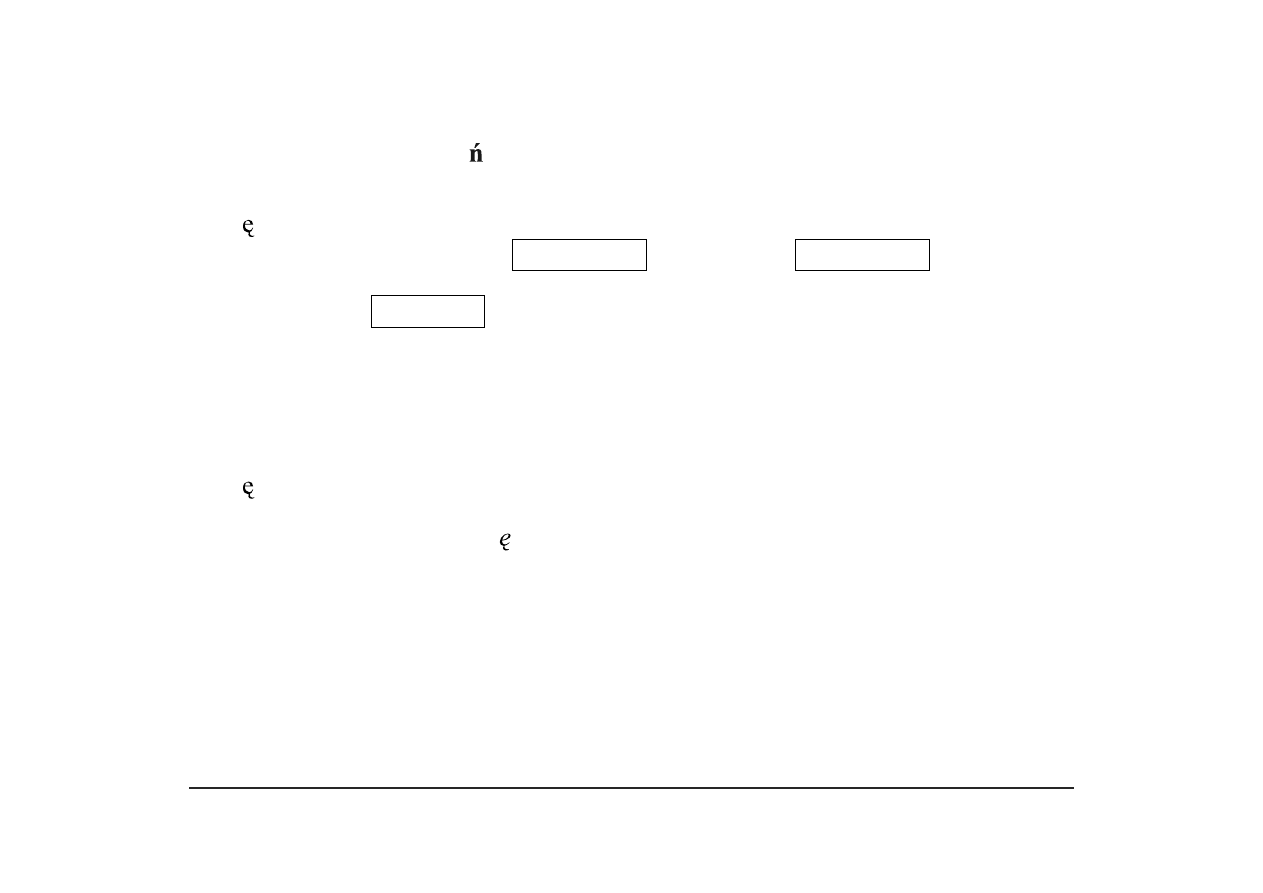

Odwzorowanie programu w przestrzeni logicznej

Edycja – plik ródłowy (*.asm, *.txt, *.c, itp.)

§

opis struktur danych (zmienne)

§

opis algorytmu w j zyku programowania (+ zwrot sterowania (restart))

Kompilacja – plik wynikowy (*.obj)

§

przekodowanie opisu na posta półskompilowan (kod + powi zania)

§

powi zania (

ang.

binding

) statyczne (

ang.

early) i dynamiczne (

ang.

late

)

Konsolidacja – ł czenie modułów (

ang.

linking):

§

powi zania (

ang.

binding)

o wczesne (

ang.

early), statyczne – zmienne deklarowane

o pó ne (

ang.

late), dynamiczne – zmienne implikowane (stos)

§

tworzenie nagłówka pliku wykonalnego ( *.exe, *.dll, **, itp.)

o nazwa i struktura pliku, zapotrzebowanie na pami operacyjn

D

ZIAŁANIA PROCESORA

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

DZIAŁANIA-17

Odwzorowanie programu w przestrzeni fizycznej

Przydział (

ang.

allocation) pami ci operacyjnej (RAM)

§

dla struktur danych programu

§

dla kodu programu

§

dla stosu obliczeniowego

§

bufor dynamiczny (dla zmiennych roboczych

Załadowanie kodu do pami ci alokowanej (

ang.

loading)

§

przydział bloku (partycji)

§

kopiowanie kodu

§

przekazanie sterowania do pierwszej instrukcji programu

D

ZIAŁANIA PROCESORA

©

J

ANUSZ

B

IERNAT

, AK1-1-09- A

RCHITEKTURA

.

DOC

, 23

WRZE NIA

2009

DZIAŁANIA-18

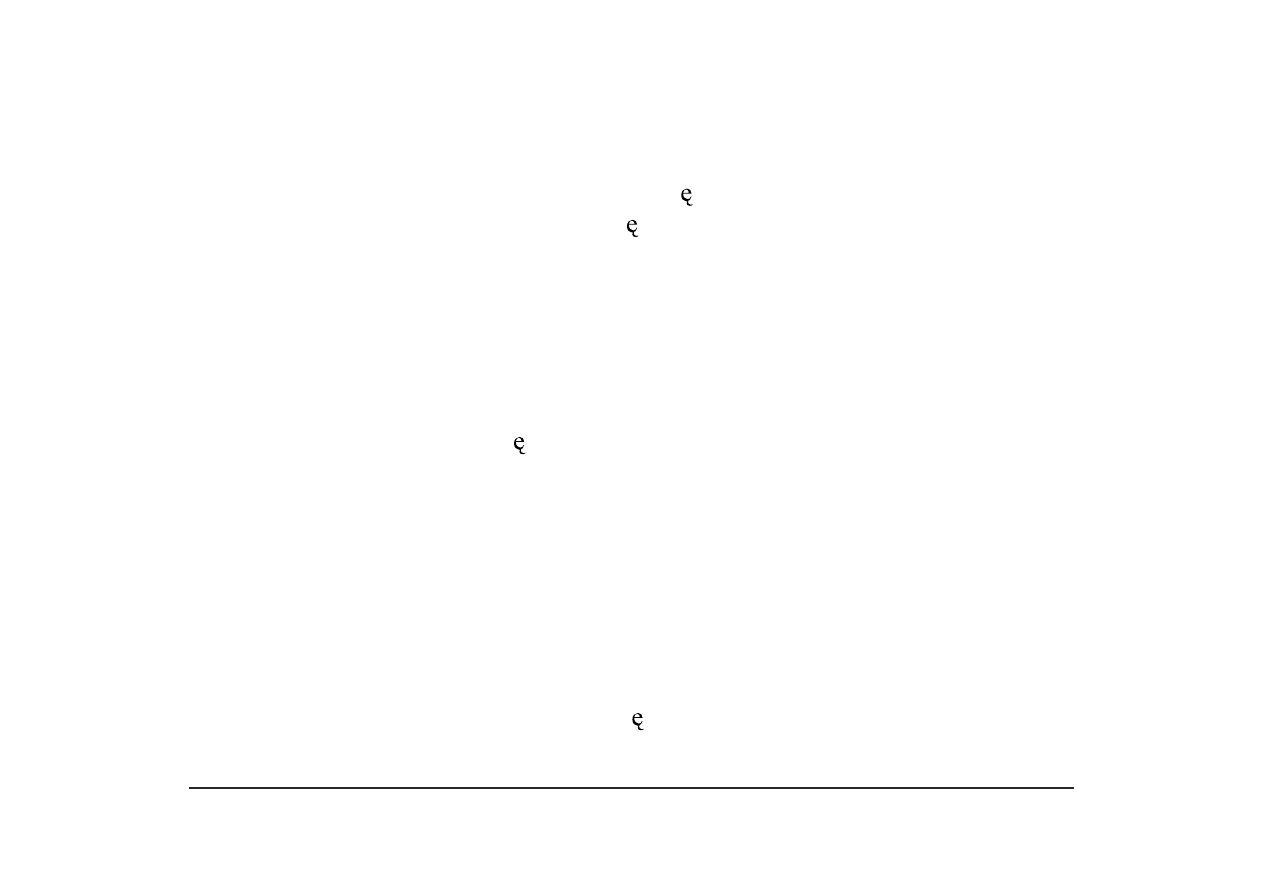

Konwersja mi dzypoziomowa - kompilacja i interpretacja

program

ródłowy

procesor

program

wynikowy

inne

moduły

procesor

program

wykonalny

y

kompilator

procesor

(.obj)

(.txt)

(.exe)

konsolidator

program

ładuj cy

kod

po redni

pseudo-

kompilator

interpreter

kod

maszynowy

Cechy architektury listy rozkazów procesora ułatwiaj ce kompilacj

• ortogonalno zestawu działa i sposobów adresowania argumentów

• kompletno – szeroki repertuar działa

• regularno – jednorodno opisu działa

• oszcz dno – niewiele prostych rozkazów i sposobów adresowania

• du o rejestrów – łatwo odwzorowania zmiennych roboczych

→ cechy dobrej (przejrzystej) architektury

Wyszukiwarka

Podobne podstrony:

Allplan 2009 Architektura NOWSCI spis treści

Logo - trendy 2009, Architektura i budownictwo, Architektura, wizerunek firmy i kreowanie marki

Semestr VI - harmonogram 2008 2009, architektura

Dziennik Ustaw z 2009 r ZMIANA WARUNKÓW TECHNICZNYCH OD 08-07-2009 R, Projektowanie Budownictwo Arch

Porządki architektoniczne cz 3 2008 2009

2009.11.04 - SIEDZIBA VITRY - ARCHITEKTONICZNA MEKKA, Z bryla.gazetadom.pl

Historia architektury i sztuki (10 10 2009)

Historia architektury i sztuki (14 11 2009)

Historia architektury i sztuki (24 10 2009)

Wprowadzenie do historii sztuki (Techniki i terminologia architektury) bibliografia 2009

2009 01 01 ARCHITEKTURA i BIZNES nowosci dedietrich

architektura i biznes wrzesien 2009

Wykład 6 2009 Użytkowanie obiektu

ARCHITEKTURA KOMPUTEROW1A

Przygotowanie PRODUKCJI 2009 w1

więcej podobnych podstron