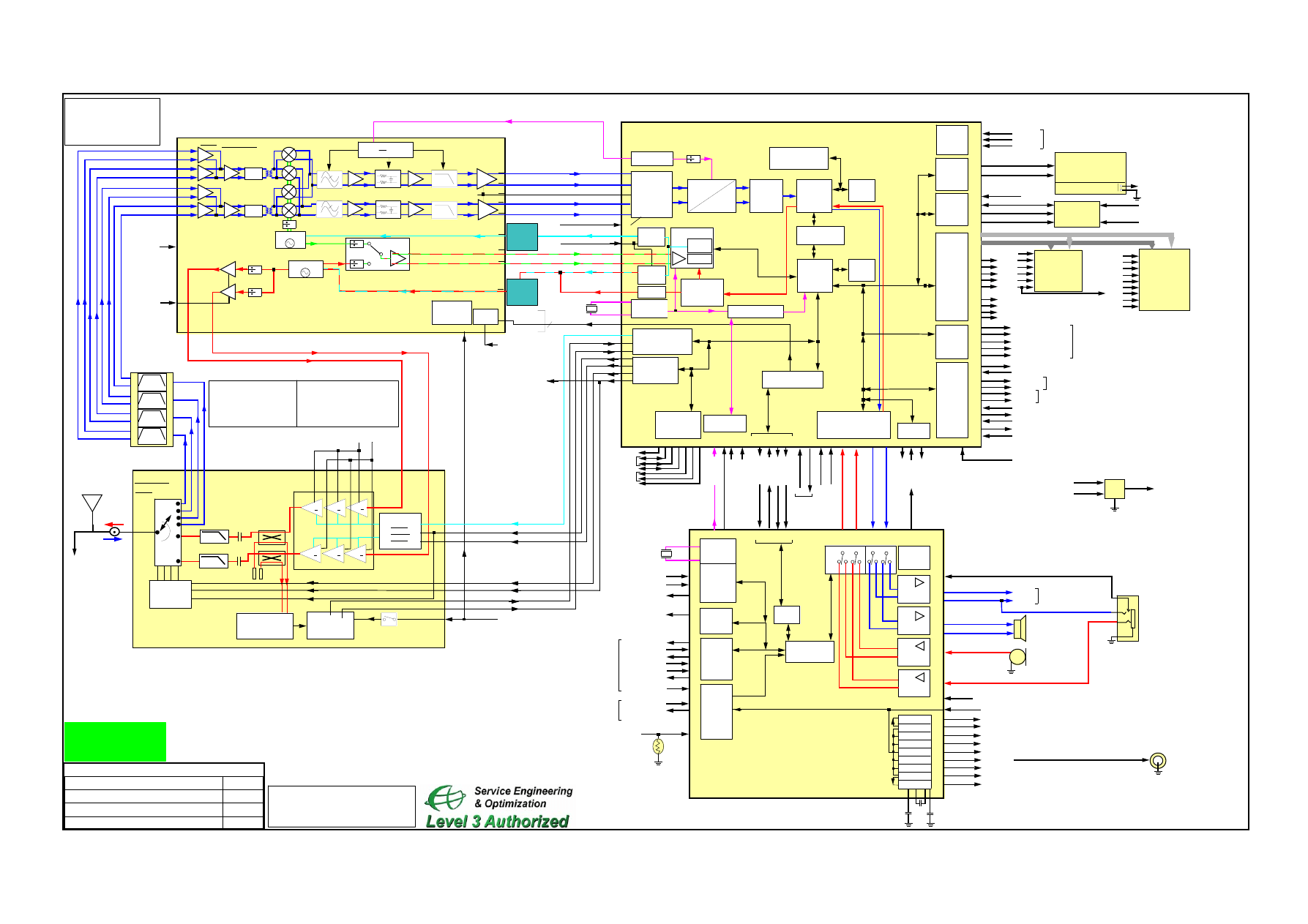

Internal

Antenna

J1

AOC_DRIVE

Antenna

Switch

FL100

Quard Saw Filter

4

3

25

47

Synth F/B

TX_IN_HB

TX_IN_LB

38

39

41

42

44

CM IN

RF_REG

7, 8, 10, 11, 15, 18, 21, 37, 43, 48

Power Detector

PACII IC

VCC

2

6

4

17

LOWB_HIGH

TX_EN

8,16

Switch

Control

Circuit

EXC_EN

EUROB_US

PA_REF

PA_DET

19

18

14

15

13

Matching and

Combiner Network

LP

LP

Low Band

High Band

3

3

2

2

1

1

Super Filter

Generator

2,45V

5

4

720 - 915 MHz

1710 - 1785 MHz

880 - 915 MHz

TX

Loop

ALGAE

U150

TRK CLK

EXC EN

Lo

w Ba

nd 850

M

H

z

EGSM: 880 - 915MHz

DCS: 1710 - 1785MHz

TX VCO FRQ. RANGE

850: 824 - 850Mhz

PCS: 1850 - 1910MHz

EGSM: CH 37 - 897,4Mhz

DCS: CH 700 - 1747,8MHz

TX VCO MID CHANNELS

GSM: CH 62 - 902,4MHz

PCS: CH 661 - 1880 MHz

850: CH 190 - 836,6

GSM : 890 - 915 MHz

36

2

4

TX VCO

3.4 - 3.7 GHz

(VCC)

RX

Loop

AGC

RF Det.

AGC

RF Det.

RX VCO

3.6 - 3.9 GHz

n

LNA

LNA

LNA

LNA

23

27

29

Low Band

850MHz

Low Band

900MHz

High Band

1800MHz

High Band

1900MHz

21

6

1

and Matching

Low

Band

9

00 M

H

z

H

igh Ba

nd 18

00 MH

z

14

15

12

13

8

9

10

11

Hig

h

Ban

d

190

0

M

H

z

19

20

22

23

16

17

13

14

EAGLE

U100

CMOS

PA Bias

Circuit

33

32

10

34

11

12

BATT_B+

BATT_B+

RX EN

9

b

Service Engineering & Optimization

2004.05.12

LEVEL 3 Block Diagram

Rev. 1.1

Quad Band V180

Alexander Buehler, Michael Hansen

Page 1of 2

RX_CP

TX_CP

D5

RX

Loop

Filter

SYNTH_FD_P

SYNTH_FB_N

C9

BB_I

BB_IX

BB_Q

BB_QX

A8

B8

A9

B9

B6

Tracking Osc.

RF

_RE

G

RF_REG

RX

Charge

TX

CP

C4

D9

IO_2,65V

RF_CS

RF_DATA

RF_CLK

3

W9, U8, V7

GMSK Mod &

Mod DAC

(TX)

PA Control

(PAC)

Y800

3

1

A4

T6

U6

W7

N9

VM_REG

D12

A10

Digital Channal

Filters

26 MHz

Y900

4

1

B1

A1

32,768 kHz

Timer

C

L

K

_32

K

AD2 Mux

SPI

Control

Logic

DMA

1Mbit RAM

Pump

D4

A6

Synthesizer

Prescaler

Phase

Detect

Dual ADC

DSP

DSP

UltraLite

104 MHz

DSP Peripherals

accelerator, encryption

Timer, Interupts

Shared Memory

MCU

52 MHz

ARM7

MCU

26 MHz

Oscillator

B4

SPI

Memory

Memory

KBC0, KBC1

Keypad

Port

KBR0 - KBR7

6

5

4

SIM

Interface

SIM_DIO

SIM_RST

SIM_CLK

J4

L1

K3

1

SIM_VCC

2

GND

3

NC

MQSPI

Display

M4

L3,L2, ...

LCD_DATA (0-5)

Connector

J300

SIM

SIM_EN

GPIO

F4

D14

M1

C8

SIM_EN

External

Interface

Memory

Reset

V13 U13

(decoupling analog GND)

HP-Filter

D8

TX

Loop

Filter

Clock Generator

Audio

Codec

ADC

_N

AD

C_P

DA

C_N

DA

C_P

Amplifier

Microphone

G9

D3

E4

C3

G3

H4

F4

F5

Amplifier

Microphone

A2

Speaker

Amplifier

Aux.

Mux.

VM_REG

C907

C908

C934

A4

A8

4,7V- 5mA

IO_2.65V

2,75V- 200mA

(to Syn. Chargep.,

Switch control

)

(to VM, NeptuneI/O, Ser- Flash, Displ.)

DIG_1.875_EN

1,875V- 200mA

(to U930)

RF_REG

2,75V- 200mA

AUD_2.65V

2,75V- 150mA

(Synthes., SF reg., RF& AL funct.of Algae)

(Aud. analog funct. of Neptune & Seaweed)

1,575V- 100uA

COINCELL

(RTC)

1,85/ 2,85V- 20mA

SIM_VCC

(SIM Card)

VIB_OUT

1,3V- 200mA

A5 A6

I/O Regulator

A3

V. Multiplier

A8

Digital Reg.

A9

Reference Reg.

RF Regulator

D9

Audio Reg.

B7

SIM Regulator

B9

J7

Vibrator Reg.

G8

B+

D8, E8, F8

AD / DA

R

E

S

ETB

E3

L1 Timer

WDOGB

B2

GPIO

NEPTUNE

SEAWEED

U800

U900

VAG Regulator

1,325 - 100uA

VAG_CODEC

V

A

G_

CO

DEC

D1

ST

ANDBY_T

O

DAI

T

i

m

e

r

PWR_SW

F2

XTAL

EXTAL

LOW_BATT_B

LOW_BATT_B

A2

F1

EXT_PWR_ON

Charger

Interface

CHRG_DETB

CHRG_STATE

D1

E1

G1

CHRG_SW

E6

CHRG_TYP

D6

(TEMP)

PC12

PC12

E2

DISABLE

Interface

USB

Interface

USB_TXENB

USB_VPIN

USB_VMIN

USB_XRXD

USB_VPOUT

USB_VMOUT

USB_SUSPEND

D15

A17

C16

B16

C15

A16

B17

USB_DET

C13

B5

( 26MHz for RC tuning)

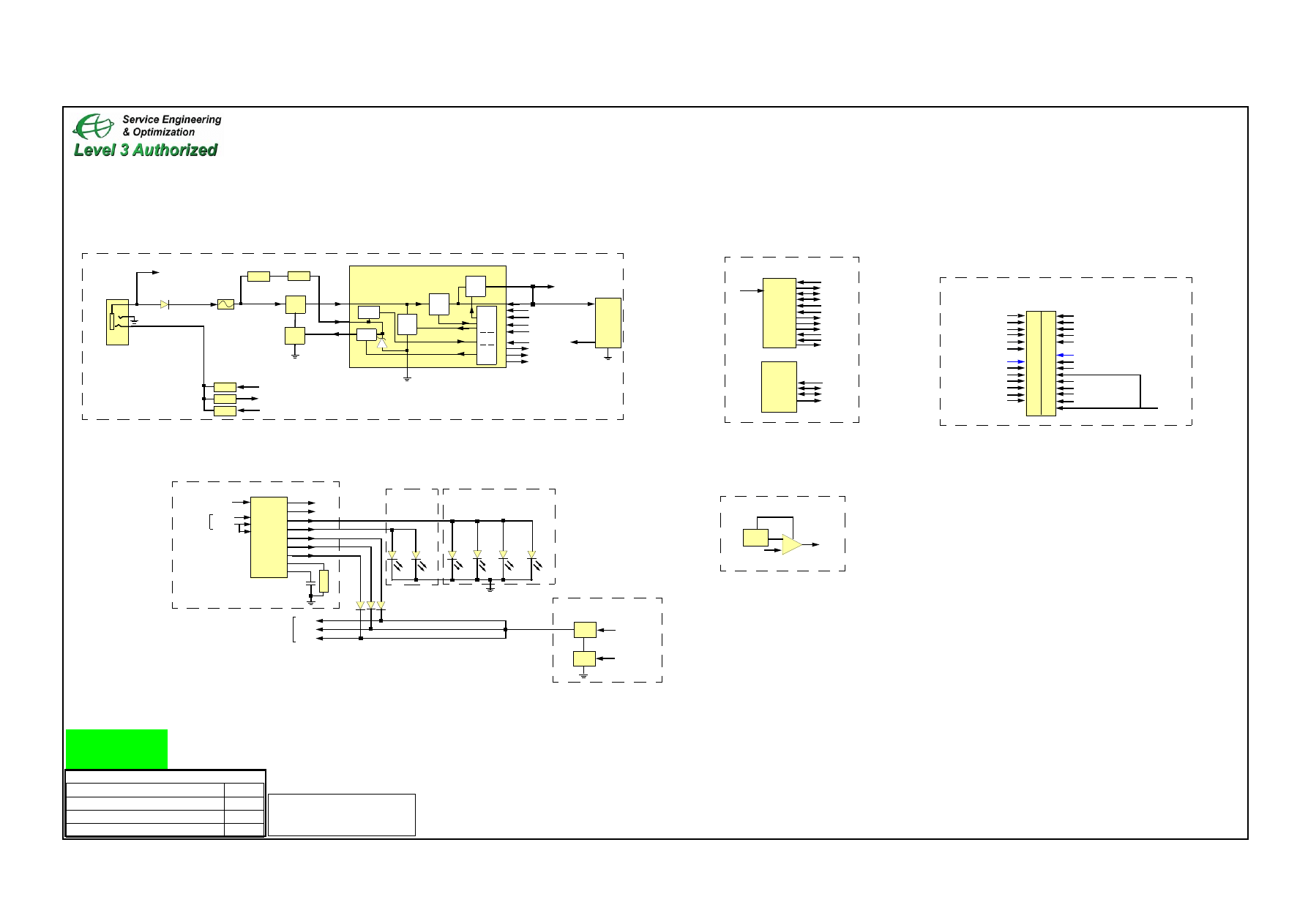

V180

G6

G8

A

U

D

_2.

65V

D7

IR

Q

B14

Reset

C1

B15

SOFTCON

B+ Sense

EGSM: CH 37 -- 942,4Mhz

DCS: CH 700 -- 1842,8MHz

RX MID CHANNELS

GSM: CH 62 -- 947,4 MHz

Direct

Memory

Access

Controller

Analog / Digital

Converter

N

and LO

Digital

If Mixer

Keypad

Matrix

C5

NC

(BL_SINK)

Revision Overview

Rev. 1.0: initial Block Diagram

Rev. 1.1: Change Alert - Speaker Amp. in Seaweed, Add

Navigation Keys

PA_REF

PA_DET

LOWB HIGH

TX_EN

EXC_EN

EURO_US

EXC_EN

(to Algae)

(VCC)

SPI

32

33

34

31

25

27

28

29

30

LP Filter

Tracking

Control

PMA

AAF

(Post Mixer Amplifier)

BB

Out

BB

Out

IF Amp.

2 Pole Filter

L & H

Band

100kHz

100kHz

35

A1

Alert

Amplifier

J19

T16

V17

T19

K16

L16

V18

G17

N18

W5

RE

SET

_

O

U

T

A13

ENT_MUTE

J950

Coincell

E3

D2

D3

D4

T11

V11

V12

W12

K2

SIM_VCC

ADC_DATA

E5

F6

ADC_SYNC

A

DC_

DA

T

A

E1

AD

C_

S

Y

N

C

W13

B10

0-9,*,#,Send,

PWR/End,Menu,

Soft Left+Right

PWR/END

PWR_SW

RT900

D5

32kHz RTC

Osc.

C3

MQSPI

SPI

_

CL

K

MIS

O

A

MO

SIA

SPI

_

CS

3

WD

OG

B

P16

A14

PE12

T7

TOUT9

G12

SC0A

LSC_CLK_DATA

LCD_SDATA_DATA

P1

LCD_CS

LCD_RS

N3

P2

(from / to U900)

(from / to U800)

(from / to U920)

(t

o

U

7

01)

(from U900)

(to U900)

(to U900)

(from U900)

(to U600)

(to U500)

(to U900,U920)

(from J600)

(from Lightsensor)

J513

Power

IO_2.65V

RF_REG

DIG_1.875

(VCC)

U701

DIG_1,875

A4,G4,A5

BURSTCLK

E1,G6

B4

R_WB

C5

CS0B

OEB

F8

E7

LBAB

ECBB

B5

C4

RESET_OUT

D3

U705

DIG_1.875

A6,E1,D6

EB1_B

EB0_B

A2

A1

B5

OEB

R_WB

A2

G5

CS1B

Software

EE Prom

SRAM

32 Mbit

BURSTCLK

LBAB

ECBB

128 Mbit

Flash

DATA BUS

D0-15

ADDRESS BUS

A1-24

DIG_1,875

CS0B

J8

J9

SPKP

SPKN

ALTP

ALTN

MIC

J4

J4

F9

E9

HED_MIC

J400

HEAD_INT

C4

U930

B+

DIG_1.875_EN

DIG_1.875

V6

RX_EN

( to U150)

(to J800 Display Con.)

(To J800)

(To J800)

ANT_DET

ANT_DET

U12

IO

_2

.6

5V

E1

IRQ

C2

J930

MIC

J410

Alert

HEAD_SPK

P_S

(tfrom J800 Display Con.)

G11

Navigation Keys

U500

BATT_B+

NC

NC

LED3

LED4

LED5

LED6

LED7

ISET

R

501

VPOUT

C505

LED

Driver

C1

D6

E5

D4

E3

C5

C3

B4

C7

A3

B6

E7

(from Neptune)

D500

Q902

Q903

E

B

G

IO_2.65V

SOL_EXT_B+

C

S

D

Sign of live Circuit

SOL

3

1

2

1

2

3

DS530

Light

Sense

5

4

U530

IO_2.65V

PE12

3

1

IO_2.65V

1

2

D511

Keypad Backlight

Driver

DIAMONDHEAD 3

U920

M4

G

S

D

M5

G

S

D

M3

S

D

G

9-12

B

E

C

Q900

VDETECT

VIN

6,7,15,16

Sense

13

Current

(Charge and Protection)

Safety

Pass Transistor

B

E

C

Q901

Fuse

EXT_B+

R900

IO_2.65V

CHRG_TYP

CHRG_SW

R907

R908

F900

CNTRL

CHRG_STATE

CHRG_DETB

B+

B+

24-26

DISABLE

PC12

(CHEMISTRY)

NC

GND

5

18

17

22

28

3

4

20+21

8

Logic

I / O

Charge

Control

P900

Battery

Conn.

1

2

PNP

NPN

(Charge)

(Drive)

Charge

Control

Shunt

Sense

Under-

voltage

&Short

Circuit

Protect.

19

BATT_DETB

3

CHRG_C

R901

R902

(from U900)

(Bias)

(from U900 - If high current is set to 400mA limit. If low current is set to 900mA imit.)

(to U900 - Charger Type indication from pull down resisor in Charger)

EXT_PWR_ON

1,2

USB_TXENB

USB_VPIN

USB_VMIN

USB_XRXD

USB_VPOUT

USB_VMOUT

USB_SUSPEND

U600

USB

Interface

IC

Accesory

J600

Connector

USB_DNEG

USB_DPOS

USB_DET

USB_DNEG

USB_DPOS

USB_VCC

USB_VCC

IO_2.65V

SOFTCON

16

14

9

10

8

3

4

2

11

12

5

1

7

1

2

3

4

5-9

GND

ENT_MUTE

SC0A

TOUT9

USB

b

Service Engineering & Optimization

2004.05.12

LEVEL 3 Block Diagram

Rev. 1.1

Quad Band V180

Alexander Buehler, Michael Hansen

Page 2of 2

V180

Charger Detection Port (Pin2)

Light Sensor

(to Neptune)

D510

D509

D508

J900

Charger

Jack

2

3

1,4

Charger

Menu Backlight

J800

1

GND

3

2

LCD_SDATA

4

Flex Connector

5

7

9

11

13

15

17

19

21

23

25

27

29

6

8

10

12

14

16

18

20

22

24

26

28

30

LED3

LED1

LED2

LCD_DATA_0

LCD_DATA_2

LCD_DATA_4

LCD_DATA_1

LCD_DATA_3

LCD_DATA_5

SPKN

SPKP

LCD_CLK

RESETB

P_S

IO_2.65V

IO_2.65V

VIB_OUT

GND

GND

GND

GND

LCD_RS

LCD_CS

GND

NC

NC

D502

D501

LED1

LED2

LED3

D505

D506

Keypad Backlight

(to J800)

D512

SOL_EXT_B+

A7

Revision Overview

Rev. 1.0: initial Block Diagram

Rev. 1.1: Change Alert - Speaker Amp. in Seaweed, Add

Navigation Keys

Wyszukiwarka

Podobne podstrony:

BD C650 A3 C L3 V1[1] 1

BD W220 A3 C L3 V1 1

SF V180 A3 C L3 V1

BD W206 W213 A3 C L3 V1

TS V180 A4 L3 V1[1] 2

Signal Flow V220 A3 C L3 V1

SF C650 A3 C L3 V1

BL 84D86261P05 JADE A3 C L3 V1 0

BD V3i A3 C L3 1 0

BL 8403574B1 P01 C550 A3 C L3 V1

SF C380 A3 C L3 V1

sf v66i 8489894k04c a3 c l3 v1

C370 C450 PCB & Signal A3 C L3 V1

BD V177 A3 C L3 2 0

BD V557 A3 C L3 1 4

SCH K1 A3 C L3 V1

V220 Block diagram A3 C L3 V1[1] 1

Block Diagram V220 A3 C L3 V1[1] 1

więcej podobnych podstron