12

1

2

3

SIM

Connector

1.8 or 3V

SIM Card

6

5

6

Att 3dB

R718

Att 3dB

R719

E20 E21 E19 F18

6

U200

FLASH

128Mbit

&

PSRAM

32Mbit

K5

V_RAM

Address Bus ADD[1:23]

V_FLASH

D

a

ta

B

u

s

D

A

TA

[0

:1

5

]

J8,K7,

L3

G2 K7 K8 K3

F3

C2

D6

K1

T

D

I

T

C

K

T

D

O

T

M

S

(from / to JTag Test Points - not in use)

W5 M4

G11,

C21 R19 V7 AA4 C7

M3

K

E

Y

L

IG

H

T

_

E

N

(t

o

ke

yp

a

d

)

H

S

_

D

E

T

E

C

T

(f

ro

m

H

e

a

d

se

t)

H

W

_

ID

(d

e

te

ct

V

1

7

5

/V

1

7

6

o

r

V

1

7

7

)

L

C

D

_

ID

(f

ro

m

L

C

M

)

H

S

_

E

N

(t

o

H

e

a

d

se

t)

A

U

D

A

M

P

_

S

D

(t

o

S

p

e

a

ke

r)

F

O

L

D

_

D

E

T

(f

ro

m

ke

yp

a

d

)

L

C

D

_

n

R

E

S

E

T

(t

o

L

C

M

)

D16 B19 A20 C18 D17

R

T

S

_

M

O

D

E

M

1

D

S

R

_

M

O

D

E

M

1

T

X

_

M

O

D

E

M

1

R

X

_

M

O

D

E

M

1

C

T

S

_

M

O

D

E

M

1

(f

ro

m

/

to

M

u

lip

le

xe

r

a

t

h

e

a

d

se

t

co

n

n

e

ct

o

r)

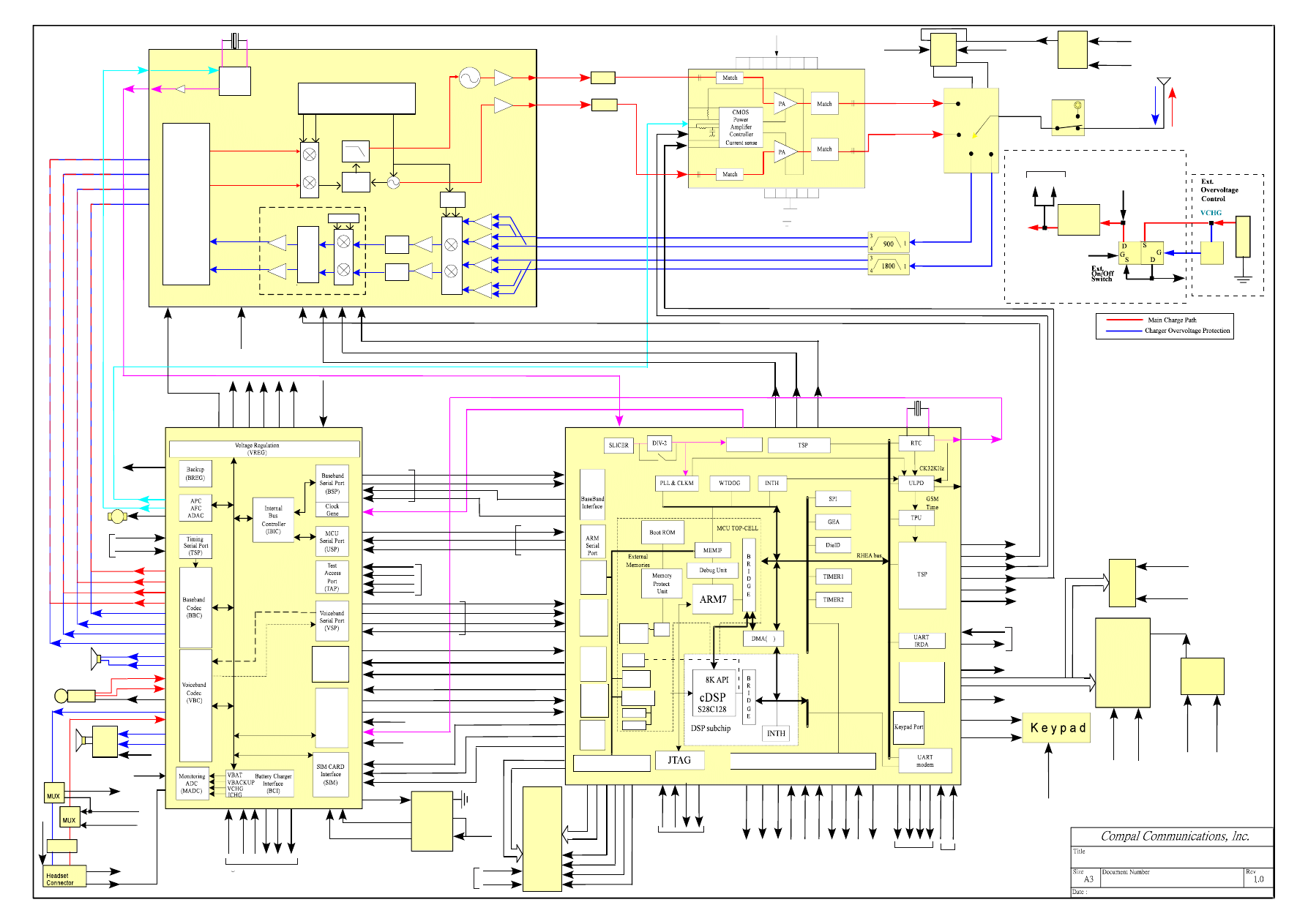

V175/V176 EU Band Block Diagram

23. June. 2005

A19

D

T

R

_

M

O

D

E

M

1

(from / to Modem

Test Points - not in use)

K

E

Y

L

IG

H

T

_

E

N

(f

ro

m

G

+

)

ROW0 - ROW4

COL0 - COL4

R18,V21,U19,

W21,T18

Y21,V19,U18,

W19,V18

LCD_D[7:0]

L

C

D

_

n

R

E

S

E

T

(f

ro

m

G

+

)

not use

Sub-

Display

C17

A18

RX_irDA

TX_irDA

LED(Back Light_5V)

Y4

B

A

C

K

L

IG

H

T

_

E

N

(t

o

U

2

0

1

)

Charge Pump

U201

1

3

B

A

C

K

L

IG

H

T

_

E

N

(f

ro

m

G

+

)

5

V

B

A

T

V12

V10

P12

R12

V15

V11

SW_LO_TX

PDN

PA_EN

BS

TSPEN0

SW_HI_TX

(to T700)

1

2

3

4

5

6

Dual-

BJT

LDO

3

1

4

RF2V8

TCXOEN

(from G+)

VBAT

ANT Switch

2

10

VC1_DCSTX

VC1_GSMTX

SW_HI_TX

SW_LO_TX

T700

(to T700)

(from G+)

(from G+)

U701

X100

H20

J20

H21

LNA850

LNA1800

19

U703 SI4210

XTAL

26MHz

LNA900

LNA1900

PGA

PGA

Q

ADC

I

ADC

PGA

PGA

VCO+FREQUENCY SYNTHESIZER

DET

90/0

LOW-IF

DCXO

11

A

N

A

L

O

G

IN

T

E

R

F

A

C

E

AFC

R

F

_

C

L

K

(2

6

M

H

z)

4

5

7

6

9

D

IG

IT

A

L

F

IL

T

E

R

I N

I P

Q P

Q N

8

27

31

30

3

1

2

SKY77328

U700

20

21

22

EGSMRX

DCSRX

BF700

BF701

3

5

11

1

8

G

S

M

R

X

D

C

S

R

X

SW700

15

11

GSM_TX

DCS_TX

4

20

18

1

3

(to Syren)

AA17

V14

W16

Battery

APC

XTAL

32.768KHz

TSPDO

TSPCLK

TSPEN2

12,13,25,28,29

R

F

2

V

8

(f

ro

m

U

7

0

1

)

16

15

LBTXOUT

HBTXOUT

26MHz

CLK13M

AA18

J21

U100 G+

AA12

Y13

Y12

W14

BFSR

BDR

BFSX

BDX

(Base Band

Intercommunication)

W6

V8

Y5

MCUDI

MCUDO

MCUEN0

W10

W12

W11

R11

(ARM - Syren

Intercommunication)

UDX

UDR

UEN

VCLKRX

VFSRX

VDR

VDX

VCK

VFS

VDR

VDX

from JTag Test

Points - not in use

TMS

TCK

SYREN_TDO

TDO

(Voice Band

Intercommunication)

I2S Audio

Series Port

W18

Y18

Y19

CDO

CSCLK

CSYNC

Memory IF

SIM

I2S

64b key

128b key

CRYPTO

Processors

48Kbytes

ROM/Boot

0.5Mbit

SRAM

5Mbit

SRAM

Write

Buffer

Voice

Band

Interface

NAND

Flash IF

LCD IF

ARMIO (GPIO)

13MHz

D9

C8

H9

SIM-IO3

SIM-CLK3

SIM-RST3

V_SIM

SIM_CLK

SIM_I/O

SIM_RST

Voltage

Reference

Power

Control

(VRPC)

J1

CLK32K

E11

PWON

H3

IT-WAKEUP

E10

RPWON

J3

J2

ONnOFF

nRESPWRON

RTC/

RESET

G19

J15

H18

(from keypad)

(from TP11 on Test point )

(Keypad ON indication from keypad interface processor)

(Weak up interrupt from RTC)

(Chip reset)

CLK32K

U101 SYREN

M3

L2,M1

V

_

S

IM

V

_

IO

H1

V

_

R

T

C

V

_

R

A

M

F1

V

_

F

L

A

S

H

V

_

D

B

B

V

B

A

T

D1

A3 D11,A2,L1,K1,D2,

E2,C7,C6,M7

F3

VBACKUP

C11

C12

D9

AFC

Vibration

K2

J4

TSPEN0

TSPDO

(from G+)

G10

H11

H12

H10

F12

F11

G11

G12

TXQN

TXQP

TXIP

TXIN

RXQN

RXQP

RXIP

RXIN

A8

B8

B12

A12

C9

MIC

Receiver

EARP

EARN

MICIP

MICIN

MICBIAS

A10

A11

D18

H

S

_

M

IC

(t

o

h

e

a

d

se

t

fo

r

p

o

w

e

r

su

p

p

ly

)

4

H

S

_

M

IC

(f

ro

m

G

+

)

ESD

3

5

1

3

4

5

4

4

U300

U302

HSOR

SHMICP

TX_MODEM1

(to G+)

HS_EN

(Headset / Data select from G+)

RX_MODEM1

(from G+)

3

6

1

3

1

F302

J300

HS_DETECT

(to G+)

U301

Audio

AMP.

3

4

8

5

1

SPKN

SPKP

AUDAMP_SD

A7,B7

A6,B6

Speaker

J12

J10

BATTEMP

(from Battery)

HS_MODE

K8 M8 K9 M9 L8

L7

V

B

A

T

S

V

C

H

G

V

C

C

S

IC

T

L

P

C

H

G

L

E

D

C

from / to Charger

L4

K4

L5

M5

K5

E3

A4

C4

D4

B2

B3

B4

K6

H2

M6

L6

M2

L3

K3

CLK13M

E1

C2

D3

C1

C3

(from Syren)

(from Syren)

J700

Charger

J601

4

1-3

A

D

A

P

T

E

R

C

O

N

N

E

C

T

O

R

U500

4, 5

1

3

2

U501

4

5

VCHG

(to Syren)

6

(Charge Current Control)

ICTL

(from Syren)

PCHG

(from Syren)

(sense charge current)

U502

Charger IC

1

10

VBAT

ICTL VBATS

(to Syren)

(from G+)

LCD_nRESET

CLI

(f

ro

m

G

+

)

(from G+)

LCD_nCS0

LCD_nCS1

L

C

D

_

n

C

S

0

LCD_nCS1

N14

R20

n

C

S

5

n

C

S

4

n

B

L

E

n

B

H

E

to

2

.8

V

to

2

.8

5

/1

.8

V

to

1

.5

V

to

1

.8

V

to

2

.8

V

to

1

.5

V

Wyszukiwarka

Podobne podstrony:

BD C650 A3 C L3 V1[1] 1

BD W220 A3 C L3 V1 1

BD V3i A3 C L3 1 0

Sch V177 A3 C L3 2 0

BD V557 A3 C L3 1 4

BD V180 A3 C L3 V1[1] 1

BD BlDi V235 L3 C A3 V1[1] 1

BD W206 W213 A3 C L3 V1

BD BlDi E365 A3 C L3 1[1] 2 030611100711

bd bldi v66i refresh a3 c l3 1

V171 PCB A3 C L3 1 0

SF CD920930 A3 C L3 V12

BL F3 Motofone Keypad A3 C L3 A

BL BoLaKeP4 V80 A3 C L3 1 0

Signal Flow V220 A3 C L3 V1

BL BoLaMaPCP4 V80 A3 C L3 1 0

Sch V171 A3 C L3 1 1

SF C139 A3 C L3 1 0

więcej podobnych podstron