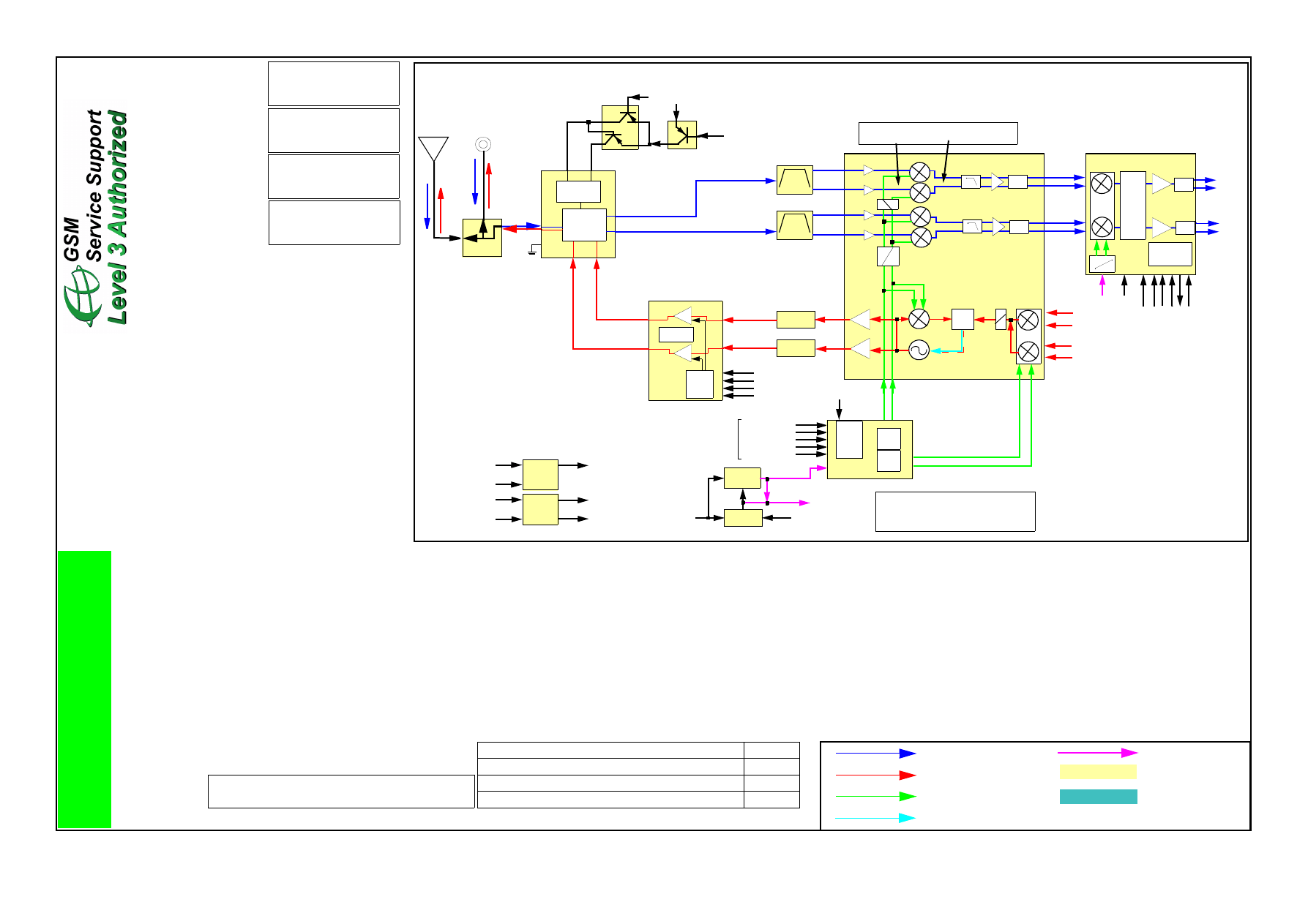

RX SIGNAL PATH

TX SIGNAL PATH

MAIN VCO SIGNAL PATH

TUNING VOLTAGES

REFERENCE CLOCK

Orderable Part

Non - Orderable Part

GSM SERVICE SUPPORT GROUP

2003.05.19

LEVEL 3 RF Block Diagram

Rev. 1.2

Dual Band - E365

Michael Hansen

Page 1 of 2

D

u

a

l

B

a

n

d

E

3

6

5

PA

GSMPA

DCSPA

22

21

20

13

U302

AFC

U503

1

4

3

4

2

13Mhz_BB

CMOS

1

7

9

11

EGSM RX

Low Channel - 975 = 925.2Mhz

Mid Channel - 37 = 942.4Mhz

High Channel - 124 = 959.8Mhz

EGSM TX

Low Channel - 975 = 880.2Mhz

Mid Channel - 37 = 897.4Mhz

High Channel - 124 = 914.8Mhz

GSM 1800 RX

Low Channel - 512 = 1805.2Mhz

Mid Channel - 700 = 1842.8Mhz

High Channel - 885 = 1879.8Mhz

GSM 1800 TX

Low Channel - 512 = 1710.2Mhz

Mid Channel - 700 = 1747.8Mhz

High Channel - 885 = 1784.8Mhz

19

12

R

F

L

O

P

VTCXO

13Mhz

RF_CLK

RF_DAT

RF_LE

VSYN

U105

1

3

5

VCC4

VTCXO

5

TXIN

TXIP

TXQN

TXQP

6

5

8

7

CH 62 RX Mode

RFLO=

947.3Mhz

RX

IF = 100kHz

(Tuning/Bias)

JP1

1805-1880MHz

925-960MHz

AP2

CALIBRATION

RF PORT

GSM_RX

DCS_RX

TX / RX Switch

1

T/R Switch

Control

1

4

6

3

2

RF ANTENNA

VRF

TRENA

U103

U102

3

1

GSM_TXEN

2

F101

2

4

6

F102

2

4

6

R

F

L

O

N

4

5

3

2

RXIN

RXIP

RXQN

RXQP

IFLOP

IFLON

VRF

14, 23,

26, 32

(VCC)

SDO_RF

PDNB

(Data in)

(Clock in)

(Latch)

(Data out)

1

N

13Mhz

100kHz

7

ION

IOP

CKN

CKP

C

h

a

n

n

el

F

il

te

r

PGA

PGA

ADC

ADC

U201

U203

6, 20

R

F

_

C

L

K

R

F

_

D

A

T

R

F

_

L

E

IF

SPI

1

2

3

4

12

11

9

10

18 17 16

(D

at

a

in

)

(C

lo

ck

i

n

)

(L

at

ch

)

S

D

O

_

R

F

5

(D

at

a

o

u

t)

P

D

N

B

14

T

C

X

O

E

N

13

(E

n

a

b

le

)

o

0

90 o

9 10

Exc.

Exc.

25

24

GSM

DCS

PHASE

DET.

IF/100kHz

R402

1

2

R403

1

2

GSM_TX

DCS_TX

Control

APC

(Power Control)

6

PAENA

(Enable)

3

GSM_TXEN

(Band Select)

2

VBAT

(VCC)

4

U401

8

2

U101

11

3

5

10

1

6, 12

TCXOEN

U104

7

3, 5

8

VBAT

VSYN

SXENA

6

VRF

(VCC)

(VCC)

(Enable)

(Enable)

RX /CH 62

1894.6 MHz

TX/ CH 62

902,4 MHz

CH 62

947,4 MHz

CH 62

798 MHz

1

2

TX /CH 62

1301.4 MHz

CH 62 TX Mode

RFLO=

1301,4Mhz

IFLO=

798MHz

TX VCO =

902,4 MHz

23

IF

VCO

RF

VCO

SPI

U301

24

26

27

13

IF

12

11

10

9

5, 25, 28

7

399MHz

399MHz

ADC

ADC

(Enable)

(from/to U15)

(E

n

ab

le

)

(Tx /Rx selection)

(VCC)

(Tx Enable)

1

2

Revision Overview

Rev. 1.0: initial Block Diagram

Rev. 1.1: updated SDO_RF signal direction, updated U303 to U503

Rev. 1.2: updated F1 as EMI filter, RF VCO frequency, U201 internal divider, U503 output, TR Switch

Duplexer

Control

Function

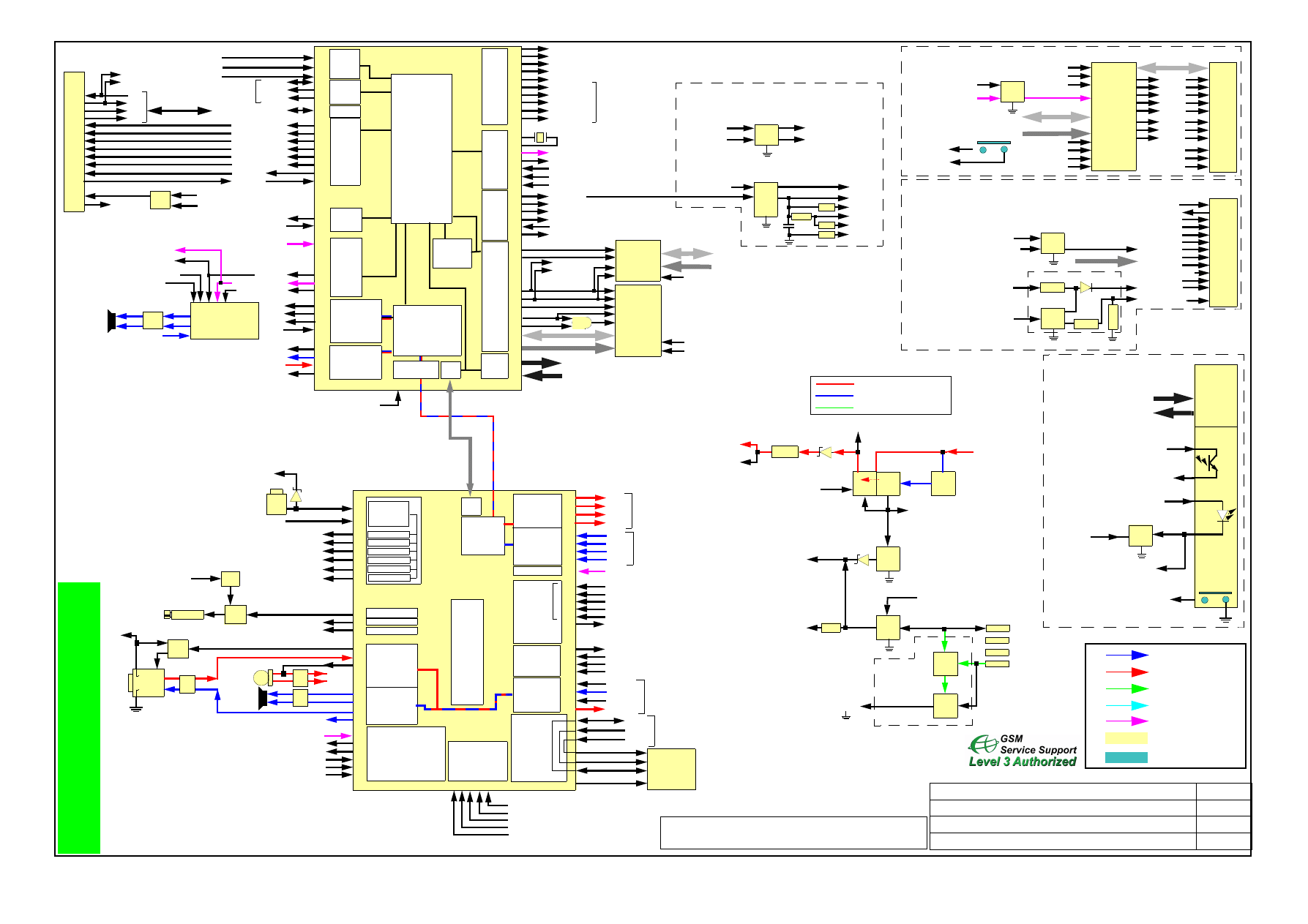

RX SIGNAL PATH

TX SIGNAL PATH

MAIN VCO SIGNAL PATH

TUNING VOLTAGES

REFERENCE CLOCK

Orderable Part

Non - Orderable Part

RXIP

RXIN

RXQP

RXQN

LS2

SPKR

TXIP

TXIN

TXQP

TXQN

Kepad

PWON

nFOE

nCS0

RNW

Backlights

VIBRATOR

BQ1

D

u

a

l

B

a

n

d

E

3

6

5

GSM SERVICE SUPPORT GROUP

2003.05.19

LEVEL 3 AL Block Diagram

Rev. 1.2

Dual Band-E365

Michael Hansen

Page 2 of 2

J5

RTC

U14

GPIO

MEM

I/FACE

ARM 7

2M RAM

RTC - 1.5V

BACKUP

Hercules U15

OMEGA U1

BASEBAND

PORT

SPI

Battery

VOICE

VOICE

3V / 5V

LEVEL

SHIFTERS

TSP

BASEBAND

UPLINK

BASEBAND

DOWNLINK

AFC

APC

AFC

APC

MIC1

EF2

J4

Audio

Jack

VCLKRX

VDX

VFSRX

VDR

SIM I/Face

SIM CON.

CON1

SCLK5

SRST5

SIO5

VR_1.8/2.9VSIM

SCLK3

SRST3

S_IO

(to/ from Hercules)

VCC4

RTC BATTERY

BT1

VRABB_2.8V

VRIO_2.8V

VRRAM_2.8V

VRMEM_2.8V

VRRTC_1.5V

BDR

/

BFSR

1

2

3

4

BATTEMP

BATTERY

CONNECTOR

J3

PWON

Main Charge Path

1

Charger Overvoltage Protection

Battery Over Voltage Protection

(to RF Side)

CLK32K_OUT

1,2

3

4,5

TFTConnector

LCD_ID

NC

GND

nRESET

VBAT

M1

FDP

DATA BUS

ADD BUS

FLASH

MEMORY

VRMEM_2.8V

U6

DATA BUS

ADD BUS

nBLE

nBHE

ROW 0 - ROW 4

COL 0 - COL 4

ROW 4 - ROW 1

COL 0 - COL 4

CLK13M_OUT

B13

A14

E4

F5

E2

C2

F4

C5

(Write Enable)

F8

E7

B5

E1,G6, D6, B4

D1

J4

K4

J7

J8

J9

J10

B6C7A6

E2

B4

D4

C4

F4

B3

G4

A5

A4

C5

F9

F10

E10

E9

D9

D10

C10

C9

1

3

2

5

UPLINK

DOWNLINK

Charger

VCHG1

U2

D2

D2, D3

Light

VBAT

SIM

VOICEBAND

Interface

DAI

SRST3

SIO3

SCLK3

to/ from Omega

13MHZ_BB

VCLKRX

VDX

VDR

VFSRX

G13

G10

F13

E13

N12

P14

N13

M13

Digtal Audio

TIMER

Radio

Int.

H10

N2

N11

L7

Analog / Baseband

Revision Overview

Rev. 1.0: initial Block Diagram

Rev. 1.1: updated SDO_RF signal direction, updated U303 to U503

Rev. 1.2: updated F1 as EMI filter, RF VCO frequency, U201 internal divider, U503 output, TR Switch

nCS3

CE

U20

D3

(Output Enable)

(Reset)

B2

A22

F_1.8

A5, A4, G4

VRRAM_2.8V

U7

SRAM

A1

B2

G5

A2

D6, E1, A6

S19

DSP

SDO

nSCS0

SCLK

SDI

U10

Melody IC

(from U303)

29

30

31

32

Interface

K8

L9

P9

M9

nIRQ_Melody

3

4

CLK13M_OUT

1

F12

E5

(to/ from Hercules)

E1

VBACKUP

ZD1

VRAM_2.8V

IBIC

BUS

CNTL

IO

DAC

H4

C12

CLK32K_OUT

RTC_ALARM

B14

ADC

Analog/Digital

Converter

VRPC

Volt. Reg. and

Power up Ctnl.

SWITCHONOFF

F10

SWITCHONOFF

RESPWRONZ

D12

ON/

OFF

CNTL

RESPWRONZ

D3

E3

F8

RTC_ALARM

D2

VRRTC

D14

VRDBB1,5V

F11

POWER

VRDBB1.5V

VRIO_2.8V

A11,L14,N3,N1,N5

A5,B12,F11,M1,N14,P7

VRMEM_2.8V

A4,B6,D1,G1

AUXO

12,13,14

K9

AUXOP

17

18

BL1

1

2

3

4

LS1

SPKR

VRIO_2.8V

7

15

VBAT

1

3

F1

2

1

2

A1,A2,G2,G9,K1

(from U4/ D3)

MEMORY - 2.8V

VRDBB_1.5V

G1

RAM - 2.8V

F1

IN/ OUTPUT- 2.8V

B1

BASEBAND - 2.8V

H10

BASEBAND - 1.5V

J1

EMI Filter

MICIP

MICIN

H7

MICBIAS

EARP

EARN

BL2

BQ4

1

EF1

1

5

5

Auxi2

HSO

HSMICIP

K7

H9

4

3

3

4

3

2

HSMICBIAS

(to U10)

B

C

E

E

A

R

_

D

E

T

E

C

T

EAR_DETECT

K8

CTS_MODEM

RX_MODEM

TX_MODEM

RTS_MODEM

DSR_MODEM

DTR_MODEM

J1

7

8

9

10

11

12

C9

A9

B9

E8

D9

N3

USP

H5

G5

F5

K3

Micro Proc.

Ser. Port

(to U201)

(fromU203)

TMS

JTAG

JTAG

SERIAL

SPI

BDX

/

BFSX

Key

board

Int.

BS_TDO

TDI

TCK

E7

D7

E8

D8

TMS

TDO

TDI

TCK

5

3

15

14

TDO, TDI, TMS, TCK

DLPWR

VACCID

VBAT-VCHG

13

Rx_IrDA

Tx_IrDA

6

4

VCHG

1

(from ext. charger)

U9

1

1

5

4

VBAT

IO_PWR_EN

E4

D8

C8

NC

VBAT

BATTEMP

VBAT

BATTGND

VACCID

DLPWR

F7

(from U15)

(to U15)

(to U15)

(from Keyboard)

(from U15)

(Ext./ on from J1)

J1/ J2

1-5

15-12, 7

6

8

11

18

16

nCS2

6

LCDA0

7

RNW

8

LCD_RD

9

D0-D12

10-22

D13-D15

28-26

VDDS-MIF_2.8V

23,24

nRESET

25

LED_Cathode

LED_Anode

29

30

LEDLCM_EN

D6

VBAT

Boost Power

FL1

R36

U11

2

4

1

R

R

1

U19

3

5

4

VDDS-MIF_2.8V

nCS2

(enable)

(VCC)

(VCC)

(enable)

D6, D7

D8, D9

LEDKEYN

Sensor

VDDS-MIF_2.8V

LIGHTSENSER_EN

BQ3

1

2

3

KeyLed_En

LEDB

Q1

LCD_ID

L8

nCS2

C1

LCDA0

M4

RNW

DATA BUS

nRESET

(to Display)

LEDLCM_EN

L4

C6

LIGHTSENSER_EN

LEDB

A10

KeyLed_En

M

C

U

D

I

M

C

U

D

O

M

C

U

E

N

0

N7, M7, M8

J5, K5, K6

U12

B9

DATA BUS

ADD BUS

D0-7

A1-3

Connector

4

10

8

20

9

2

3

5

6

7

DATA BUS DD 0-7

(to/ from Hercules)

RNW

B10

nFOE

nFOE

B10

nCS4

nCS4

C11

CLK13M_OUT

CLK13M_DSC

U18

3

2

4

5

CLK13M_OUT

D33V

PWDN

F1

SCK

SDA

SDO

SCLK

H4

E9

D9

E10

SHS

SVS

SPCLK

K3

J4

F10

S25V

DD25V

1

GND

DISITAL CAMERA

J6

IC

CAMERA

Connector

COMS_EN

M10

U13

6

2,3

9

1

VBAT

(VCC)

D33V

DD25V

S25V

L8

RR26

D25V

L6

AVDDP

L7

AVSSP

AVDDP

AVSSP

D25V

D33V

ROW4

S22

6

COL4

CAMERA

Switch

U8

2,3

1

9

VCC4

VRRAM_2.8V

(enable)

(VCC)

Regulator

VDDS-MIF_2.8V

F_1.8

(to Flash)

(to U19, Q1, J2)

Regulator

10

G1, ......

L2, ......

B4

A4

UART

RX/TX

CNTL

GSM_TXEN

TRENA

PAENA

SXENA

TCXOEN

RF_CLK

RF_LE

SDO_RF

PDNB

RF_DAT

A13

A12

H11

J14

H14

VCHG

(from J1)

U3

4, 5

1

Ext.

Control

Overvoltage

5

6

2

ICTL

S

S

B

3

G

D

D

nCHG

G

(to U1, U5)

(Charge Current Control)

(bulk)

PCHG

VCCS

R1

VBAT

VBATS

U5

1

2

D3

VCC4

Regulator

(to U1 as

U4

1

2

(VCC)

(ON/OFF)

Batterie

Switch

VCHG1

Main Soure

for Regulators)

VBATD

(Sense)

R16

(Sense)

(Sense)

(to Batterie)

Charger

Ext.

Switch

On/Off

VBATS

VBATD

VCHG1

VCCS

D5

ICTL

PCHG

D6

B5

U16

2

3

U17

5,6

7, 8

GND

B

A

T

T

G

N

D

2

5

Batterie

Over Voltage

Protection

Switch

1

Sense

M14

K13

K14

L12

I/O

eventuell verbunden auf RF!! U203, U301

(Charge Current Control)

Sense

Interface

(to RF Side)

Camera

TFT Display

Keyboard

Regulator

Wyszukiwarka

Podobne podstrony:

BD W206 W213 A3 C L3 V1

DeGu E365 A4 C L3 1[1] 0 030611093814

BD BlDi V235 L3 C A3 V1[1] 1

bd bldi v66i refresh a3 c l3 1

BD C650 A3 C L3 V1[1] 1

BD W220 A3 C L3 V1 1

BD V3i A3 C L3 1 0

BD V177 A3 C L3 2 0

BD V557 A3 C L3 1 4

BD V180 A3 C L3 V1[1] 1

V171 PCB A3 C L3 1 0

SF CD920930 A3 C L3 V12

BL F3 Motofone Keypad A3 C L3 A

BL BoLaKeP4 V80 A3 C L3 1 0

Signal Flow V220 A3 C L3 V1

BL BoLaMaPCP4 V80 A3 C L3 1 0

Sch V171 A3 C L3 1 1

SF C139 A3 C L3 1 0

więcej podobnych podstron