Servive, Engineering & Optimization

2005.05.23

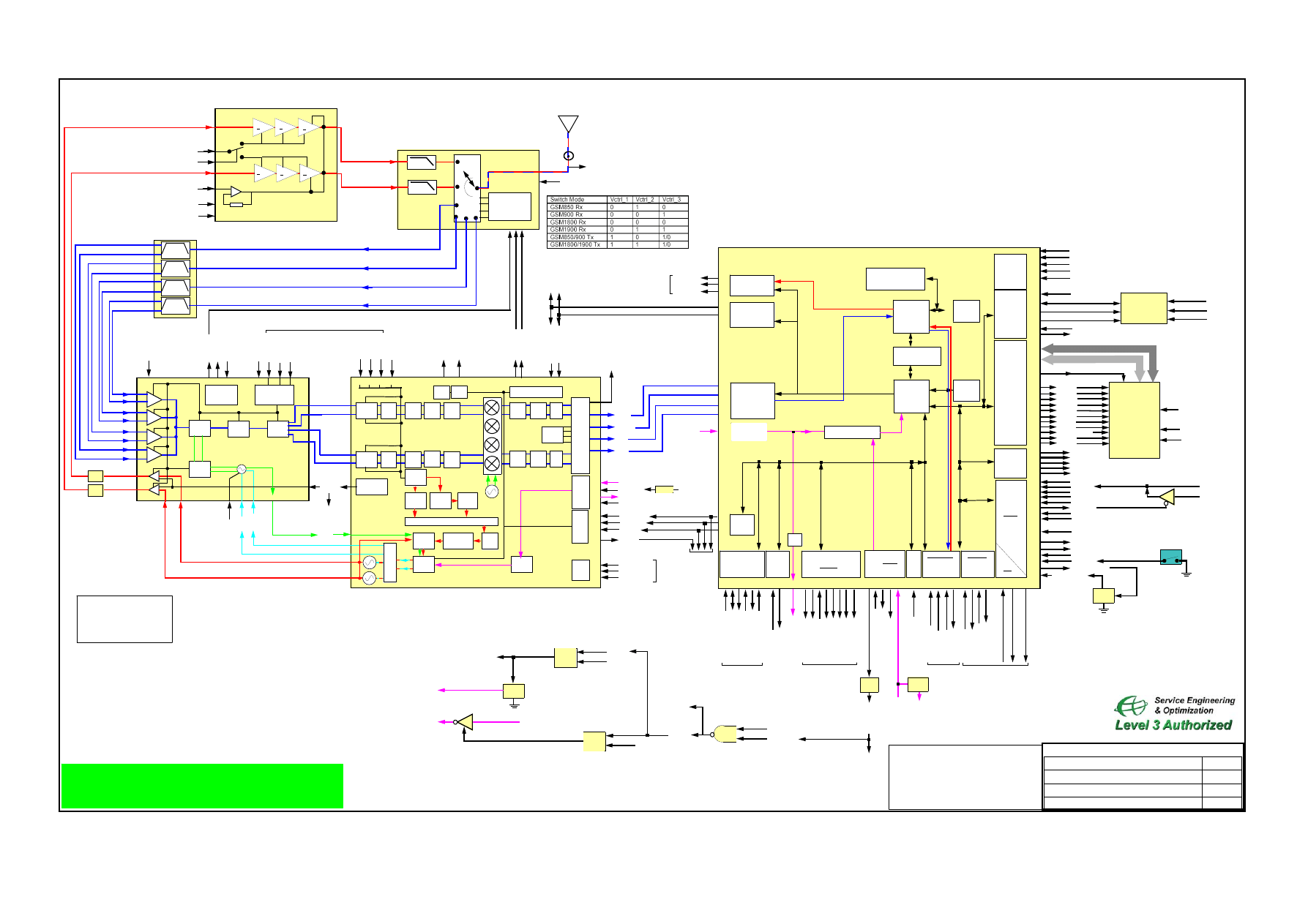

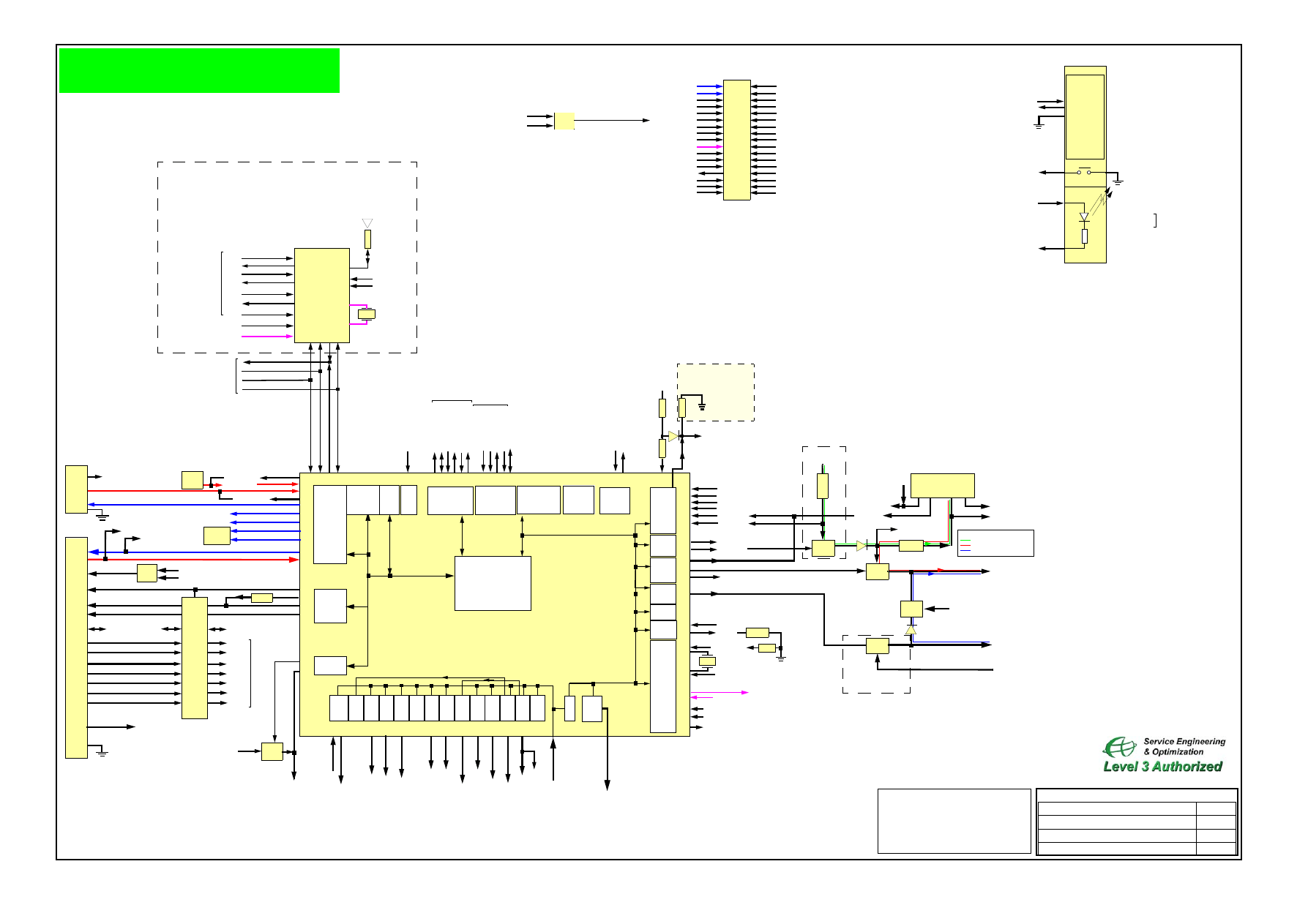

LEVEL 3 AL Block Diagram

Rev. 1.4

V540, V551, V557, V330 San2ini Series

Alexander Buehler, Michael Mauderer

Page 1of 2

V540/V551/V557/V330

TCXO

Switch

Control

Circuit

U80

3

3

2

2

1

1

TX_EN

PA_BAND_SELECT

LNA

LNA

LNA

LNA

Quadrature

Polyphase

Quadrature

Mixer

Filter

Generator

FL100

Quard Saw Filter

4

3

High Band

1900MHz

6

1

and Matching

14

15

12

13

8

9

10

11

LP

LP

2

3

4

5

6

7

8

1

Low Band

900MHz

Low Band

850MHz

12

13

18

17

VRAMP

GSM850/GSM900 IN

DCS/PCS IN

DCS/PCS OUT

GSM850/

VRANGE

BPLUS

7

3

2

4

5

6

1

9

11

GSM900 OUT

DC

Correct

22

21

20

19

27

25

26

14

15

16

GMSK/ EDGE Select

L

oop

Filter

RX/TX

Switch

ADC

13 bit

Sync

Filter

Anti

Drop

Anti

Alias

RX/TX

Switch

ADC

13 bit

Sync

Filter

Anti

Drop

Anti

Alias

Chanel

Filter

DAC

12 bit

LPF

Chanel

Filter

DAC

12 bit

LPF

Serial

Interface

Ser

ial

In

te

rface

GMSK

Modulator

EDGE

Modulator

EDGE

FIR

Filter

Anti

Alias

Pre-Distortion

Filter

Devider

PA Control

36

35

34

33

32

1

2

3

4

16

17

19

20

23

22

9

7

10

12

High Band

1800MHz

U50

PA

Antenna Switch

4

1

20

15

16

17

LD

T

O

RF

_

C

L

K

RF

_DA

T

A

R

F

_C

S

CT

RL

_

2

R

X_A

NT

_E

N

P

A

_

B

A

N

D_

SE

L

RF

_R

EG

9,10,24,32

31

30

29

28

VC

O

_

R

E

G

VTC

FIN

11

VT

U150

RF IC

ENR

CLKR

FSR

DRI

VRANGE

IIN

IBIN

QBIN

QIN

41

40

39

38

LDTO

TX

I

MS

MD

I

MC

LK

45

44

43

42

DA

C2

VR

AM

P

TX_EN

VCO2 (TX_HB)

VCO1 (TX_LB)

U200

RX/TX IC

from Neptune

22

ANTSW_1

Y806

26MHz

4

1,2

3

1800 MHz

1900 MHZ

850 MHz

900 MHz

900 MHz

850 MHz

1900 MHZ

1800 MHz

(from U200)

(to U50)

(PA Disable function)

(PA Disable function)

(from U200)

(t

o U1

10)

(P

A P

o

wer

Contr

o

l)

J1

Mechanical

Antenna Switch

Output M

ixer

Digital TX

Interface

Reference

Devider

U51

U52

Internal

Antenna

M3

Control

Serial Data

Interface

23

RX_

AN

T_E

N

C

N

TR

L_

1

C

N

TR

L_

3

TX_

S

T

A

R

T

11

OSCA

OSCO

OSCM

OSCOM

48

31

30

O

sci

la

to

r and

C

loc

k G

en

er

at

o

r

(N

C)

5

2

(T

ra

ns

m

itt E

n

able)

MS

MDI

MCLK

RF_CLK

RF_DATA

RF_CS

(NC

)

( VCO Feedback )

(from U200)

(to U50)

( VCO Fine Tuning)

( VCO Coarse Tuning)

(100KHz)

( Lock Detect Out)

14

15

DAC1

DAC2

(to U150)

(f

ro

m U200)

(to U200)

37

6

7

5

GPIO

CP

Phase Det.

(Main IC Control)

( Frontend Control

and Digital Modulation)

ADC

Voltage

Reg.

VCO_REG

IO_REG

RF_REG

24

47

9,18

VCC’s from PCap

A4

1Mbit RAM

DSP

DSP

UltraLite

104 MHz

DSP Peripherals

accelerator, encryption

Timer, Interupts

Shared Memory

MCU

52 MHz

ARM7

MCU

26 MHz

Oscillator

Memory

Memory

SIM

Interface

External

Interface

Memory

W7

Clock Generator

SPI

Power

NEPTUNE LTE

U800

G12

A13

N10

VoiceBand

L1 Timer

V8

U6

U8

V7

W9

SPI

U8

V7

W9

(t

o U150)

(from U150)

(t

o U50)

UART / USB

Interface

Keypad

Interface

On

Off

5

4

3

SIM DIO

SIM RST

SIM CLK

BATT_DETB

(SIM_PD)

6

VSIM

1

GND

Connector

J1350

SIM

1.8 or 3V

SIM Card

VSIM_EN

VBUCK

RF_REG

(VCC + 2.775V)

(VCC + 1,875V)

(from PCAP )

VSIM

(to Pcap)

VMEM_IO

(VCC + 1,575V)

J4

L1

K3

R1

M1

K2

(from PCAP )

(from PCAP )

2

NC

BB_IO_REG

(VCC + 1875V)

( to PC

ap )

R

X

_

ANT

_E

N

TX

_S

T

A

R

T

(f

ro

m U

8

0

0

)

(100KHz)

EGSM: CH 37 -- 942,4Mhz

DCS: CH 700 -- 1842,8MHz

PCS: CH 661 -- 1960MHz

RX MID CHANNELS

GSM: CH 62 -- 947,4 MHz

850: CH190 -- 881,6

MQSPI

Display

T6

V14

W8

OPT1

OPT2

T7

SW B+ EN

U700

EB1B

EB0B

OEB

R WB

CS1B

ADDRESS BUS

DATA BUS

K16

J19

G17

T16

BURSTCLK

LBAB

CS2B

ECBB

V17

T19

L16

W19

N18

A1-24

D0-15

32 MB Flash

RESET OUT

F3

C2

D6

E5

F5,D5

J2,H1,H8

G7

C6

G8

PMODE

K8

F4

K1

ADDR.(24:1)

LOGIC SENSE

T13

P2

LCD RS

P1

LCD SDATA DATA(7)

M4

LCD CLK DATA(6)

N3

LCD CS

L3...

LCD DATA (0 - 5)

A14

DSL0

G11

DSL2

G10

DSL1

U11

HKSW

MUTE*

T8

HS INT

C14

S550

(Flip Open/ Close

Detect)

J8..

ADC DATA

E1

Q801

LT_SNS_CTL

1

5

2

Light Sensor

8MB SRam

(from Neptune)

FLASH

VBUCK

L4..

VMEM_IO

U13

BB

S

A

P

T

X

BB

S

A

P

R

X

B

B

SA

P FS

BB

S

A

P

C

L

K

B13

B12

A12

D13

(fra

m

es

ync)

(c

lo

ck)

CLK

13 MH

z

W13

C15

C16

D15

A16

BB

S

P

I

CL

K

BB

SPI

M

O

S

I

BB

S

P

I

MI

S

O

PC

AP C

S

Neptune PCap

Communication

T11

V12

V11

W12

ST

AN

DB

Y

_

1

_

5

V

G8

U806

ST

AN

DBY

Buffer

CL

K 32

KH

Z

E3

B14

PC

AP IN

T

RE

SE

TB

V13

(13 M

H

z)

(W

atchdog)

WD

OG

OW

B

W11

O

n

e W

ire d

at

a from

B

at

ter

y

U801

Buffer

(t

o J

130

0)

US

B VP

IN

US

B XR

XD R

T

S

US

B VP

OUT

TXD

US

B VM

IN RX

D

US

B TX

ENB

US

B SE

0

B16

A17

Neptune PCap

USB/ RS232

Communication

(f

ro

m P

C

a

p

)

RE

SE

T OU

T

W5

(t

o U700

)

CL

K 32K

HZ

B

(from/ to Neptune

Serial Audio for Ringtone

and Voice Audio)

BL

UE

_R

X

B

L

U

E

_T

X

B

L

U

E

_R

TS

B

B

L

U

E

_C

TS

B

N17

N13

V16

D16

(from/ to U301 BT, J1300

Neptune - BT - Neptune

Communication and Wakeup)

BLU

E_

W

A

KE

B

B

L

UE

_H

OS

T_W

A

K

E

B

D19

B15

KB

R0

-7

KB

C

0

-1

E3....

G3....

GA

_S

PI_C

S

D18

Neptune Display Diver

T12

FU

N_

S

P

I_

CS

Timer

GPIO

Interface

BaseBand

Port Interface

Serial Audio

(tx)

(rx)

MQSPI

One

Bus

Wire

UART2

Universal

Asynchron.

Rx /Tx

BT

ANT_DET

(VCC)

IO_REG

R204

OSCA

TCXO

BPLUS

5

3

1

U221

U220

OSCM

RF_REG

2,3

5

4,6

Q200

ANTSW_1

(VCC to U80)

OSCO

B

L

UE

_C

LK

_EN

B

B17

CS1B

CS0B

D6

V17

T18

DAI_EN

C18

MUTE*

BB_SAP_FS

ANT_DET

T12

V6

STANDBY_GATEB

T10

GA

_

INT

STANDBY_GATEB

STANDBY

OSCM

U804

1

2

4

OSCM

(t

o P

C

A

P

)

(VCC + 2.775V)

POWER_CUTS_VCC

R12

Revision Overview

Rev.1.0: Initial Block Diagram

Rev.1.1:Updated following Part Designator: U800, J1350,

CR950, L950 DNP

Rev.1.2: Remove signal between OSCA & OSCO, removed note

at BT IC

Rev.1.3: add product names

Rev.1.4: add product name V540

Servive, Engineering & Optimization

2005.05.23

LEVEL 3 AL Block Diagram

Rev. 1.4

V540, V551, V557, V330 San2ini Series

Alexander Buehler, Michael Mauderer

Page 2of 2

(clock)

CLK 13 MHZ

C2

CLK_32KHZ

T7

TIMER

WDOG

H12

CNTL.

PRI SPI

LOGIC

Logic

F3

,E

1

3

....

...

.

S

w

itcher 1

B

+

Sens

e

B

B

-S

PI_

C

L

K

BB

_

S

P

I_M

OS

I

BB

_S

P

I_

M

IS

O

P

CAP

C

S

CODEC

PHONE

K9

R7

P8

M8

H8

H7

F6

F5

9

5

6

4

INTERF.

USB

D+

D-

USB PWR

Y900

U8

T11

RTC_BATT

U10

BP

LU

S

to V

ibr

a

2

13

14

RAW_OPT1

RAW_OPT2

HAND SPKR-

HAND SPKR+

HJACK_MIC

J4

K2

H2

J2

F1

H1

ON

2

PW

R SW

AUDIO_OUT

15

F2

ON2

T6

J1

2

16

1

17-20

RAW_BATT_FDBK

RAW_EXT_B+

3

SWB+

U980

BPLUS

SWB+_EN

B3

A5

B4

7

U900

PCAP3

MEMORY

HOLD

BACKl.

CONTR.

ON

LOGIC

M1700

OWB

THERM

U5

THERM

2

3

RAW_EXT_B+

ISENSE

BATT+

R17

M13

T15

1

4

GND

BATT+

Q950

CHRGC

R15

R9

50

EXT_BPLUS

S

G

D

CHARGE

CHARGER

BATT CONN.

AUDIO_IN

K7

CNTL.

LED

BATT FDBK

L9

IO

R

E

G

R6

This resistor is IN the

Charger accessory and

is used for identification

L12

VI

B

DR

IV

E

BATTERY

B

B

SA

P FS

BB SA

P CL

K

BB

S

A

P

TX

BB

SAP

R

X

(tx) (rx)

CR

95

1

Neptune PCap

CODEC

16 BIT

STEREO

(tx) (rx)

Communication

ALERT-

ALERT+

STANDBY

M9

(to Neptune and U301 BT)

PC

AP IN

T

L1

0

RESETB

(from Neptune)

CNTL.

SEC SPI

LOGIC

Neptune PCap

Communication

EXT_OUT

USB PU

R940

C4

Q952

S

G

D

BPLUS

N15

MAIN_FET

VOLT.

OVER

CNTL.

Battery to BPLUS

Switch

Q954

S

G

D

(Overvoltage Protection)

OV GATE

RAW EXT B+ to EXT B+

RAW EXT B+

R96

2

( from/ to PCap)

8

( toPCap + Q954)

LOGIC_SENSE

N13

IO

N8

THERMBIAS

AD

6

US

B VP

IN

US

B XR

XD

R

T

S

US

B VP

OU

T

TX

D

US

B VM

IN

R

X

D

US

B TX

EN

B

US

B SE

0

USB/RS232

(communication)

G7

C6

C5

G8

E5

F7

13 BIT

FAIL DET.

POWER

INT_MIC+

MIC BIAS 1

G2

L2

HJACK_SPKR

J1240

4

2

3

HJACK_DET

1

Headset

DE

T

.

ST

ERE

O

B

u

ck M

o

de

A12

( 1

,87

5V

)

VB

UCK

S

w

itcher 2

B

u

ck M

o

de

G21

S

w

itcher 3

B

oos

t M

o

d

e

B1

1

( 5,

6

V

)

VBO

O

S

T

H17

( 2

,775

V

)

IO

R

E

G

U1

( 2,

77

5V

)

AU

D_

R

E

G

K19

( 1

,27

5

)

G

A

VCC

H15

M15

N19

G17

( 2

,77

5V

)

RF

_R

EG

V1

V2

V3

V4

V5

V6

V7

PO

W

E

R CU

TS

V

C

C

A7

A6

( 1,

57

5V

)

RE

F_

REG

N20

V8

V9

V10

E2

B7

( 1,

8

/ 3V

)

VS

IM

VS

IM

V

S

IM

_EN

H1

4

AUDIO

AMPL.

EXT BPLUS

BATT_FDBK

13

12

D+

D-

24

22

1

3

J1701

GND

CONTR.

BATT DETB

K13

NC

NC

D4

B3

(to

SIM PD

)

BATT.

AD

EXT BPLUS

T16

R9

65

IO

R

E

G

(B

ia

s)

(One Wire Bus

to Neptune)

VR951

S

G

D

MIDRATE

Q953

EXT BPLU to BPLUS

Switch

SWITCH

(Key Source

for PCap IC)

(from Acesory Connector)

(to PCap AD Converter

(to PCap AD Converter)

and internal Charger)

Main Charge Path

B+ support without Ext Charger

B+ support with Ext Charger

Color definition only for this section !

CR950

NC

BB SAP TX

BB SAP RX

BB SAP FS

BB SAP CLK

(framesync)

NC

NC

Bluetooth

U301

32

30

28

27

BLUE_WAKEB

11

BLUE_HOST_WAKEB

9

BLUE_TX

5

BLUE_CTSB

BLUE_RTSB

31

BLUE_RX

33

29

RESET_OUT

22

(from Neptune/ PCap)

(from/ to Neptune

Serial Audio for Ringtone

and Voice Audio)

IO_REG

10

BTRF_REG

21

BT_ANTENNA

25

Strip Line

Antenna

(on PCB)

R30

1

Y300

15

16

12

( 1,

8V

)

BT

RF

_

R

E

G

NC

NC

VV

IB

( t

o

V

ib

ra

to

r in

F

lip

)

(from Neptune)

( 1,

8V

)

Neptune PCap

NC

NC

NC

NC

NC

NC

NC

NC

Neptune PCap

USB/ RS232

Communication

23

K17

K15

BL FB

BL SINK

R1459

1

2

M11

(Over Volt. Sense)

(Battery Sense)

(External B+ Sense)

R16

MIDRATE

K2

MIC BIAS 2

IO

HJ

ACK

_D

ET

K7

CONV.

D/A

CLK 32KHZ

(from PCap)

(to Neptune)

(to PCap)

(to PCap IO)

J1200

A, B

Jack

J1400

CE

Conn.

J1260

1

2

OPT1

OPT2

5

6

20

19

10

11

RAW_DSEL2

RAW_DSEL1

DSEL2

DSEL1

9

8

16

17

12

RAW_DSEL0

DSEL0

7

18

( to Neptune)

RAW_HKSW

RAW_MUTE*

14

15

HKSW

MUTE*

11

10

J1300

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

HAND SPKR+

HAND SPKR-

GND

LCD DATA(0)

RESET OUT B

GA INT

LCD RS

CLK 32KHZ B

GND

GND

GND

GND

GA SPI CS

GND

LCD DATA(1)

LCD DATA(2)

LCD DATA(3)

LCD DATA(4)

LCD DATA(5)

LCD CLK DATA(6)

LCD SDATA DATA(7)

LCD CS

VBUCK

BPLUS

GND

GA_VCC

GND

FUN SPI CS

IO REG

GND

VVIB

KEYPAD

MATRIX

L1

7

(from PCap)

(from PCap 1,3V from Vibrator Regulator)

( 1,3

V

)

VBOOST

R1450- R1457

D1450- D1457

BL SINK

KBC0 -1

KBR1 -7

PWR SW

POWER/END

S513

0-9,*,#,

Center,

Soft L+R,

Menu, Send,

Volume U-D

Smart, VA,

GND

(from/ to U301 BT,

Neptune - BT - Neptune

Communication and Wakeup)

CONNECTOR

BACKLIGHT

LED´s

FL1400

ESD Protection

Internal

MIC

Alert

Speaker

Revision Overview

Rev.1.0: Initial Block Diagram

Rev.1.1:Updated following Part Designator: U800, J1350,

CR950, L950 DNP

Rev.1.2: Remove signal between OSCA & OSCO, removed note

at BT IC

Rev.1.3: add product names

Rev.1.4: add product name V540

V30x, V400, V50x, V600

(only us

ed in P

C

ap)

BB SPI CLK

BB SPI MOSI

BB SPI MISO

(from Neptune)

(from Neptune)

(from Neptune)

(from Neptune)

(from Neptune)

(to Neptune)

RESET OUT

U1300

VBUCK

5

2

4

Navigation

(up,down,

left,right)

BLUE_CLK_ENB

R924

BATT_I

BATT_I

TX_START

P15

(from Neptune)

( 2

,775

)

BB

_IO

_

RE

G

( 2

,775

)

VC

O_R

E

G

NC

Q901

REF_REG

VHO

L

D

_

E

X

T_

EN

3

1

2

U13

( 1

,87

5V

)

VM

EM

_IO

V540V551/V557/V330

Wyszukiwarka

Podobne podstrony:

BD C650 A3 C L3 V1[1] 1

BD W220 A3 C L3 V1 1

BD V3i A3 C L3 1 0

BD V177 A3 C L3 2 0

BL V557 A3 C L3 1 1

BD V180 A3 C L3 V1[1] 1

BD BlDi V235 L3 C A3 V1[1] 1

BD W206 W213 A3 C L3 V1

BD BlDi E365 A3 C L3 1[1] 2 030611100711

bd bldi v66i refresh a3 c l3 1

V171 PCB A3 C L3 1 0

SF CD920930 A3 C L3 V12

BL F3 Motofone Keypad A3 C L3 A

BL BoLaKeP4 V80 A3 C L3 1 0

Signal Flow V220 A3 C L3 V1

BL BoLaMaPCP4 V80 A3 C L3 1 0

Sch V171 A3 C L3 1 1

SF C139 A3 C L3 1 0

więcej podobnych podstron