Politechnika Śląska

Wydział AEiI

Laboratorium

z Elektroniki

Bramki logiczne

Grupa 4 sekcja 9

Dariusz Rozwadowski

Grzegorz Witek

Marcin Pocztowski

1. Bramka TTL

charakterystyka statyczna

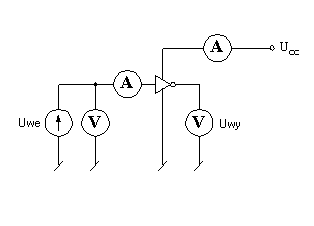

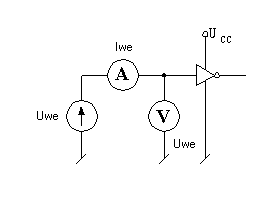

Pomiary przeprowadziliśmy dla bramek bez obciążenia ale także z dwoma, pięcioma bramkami obciążającymi. Do celów ćwiczenia wykorzystaliśmy poniższy układ pomiarowy:

Dla braku obciążenia otrzymaliśmy następujące wyniki :

Uwe [V] |

Uwy [V] |

Icc [mA] |

0,02 |

3,89 |

17,9 |

0,17 |

3,89 |

18 |

0,41 |

3,89 |

18,2 |

0,67 |

3,79 |

18,3 |

0,88 |

3,5 |

18,5 |

0,91 |

3,32 |

18,5 |

1,02 |

3,05 |

18,5 |

1,18 |

2,33 |

18,7 |

1,23 |

1,62 |

18,7 |

1,3 |

1,03 |

21,9 |

1,43 |

0,60 |

23,6 |

1,5 |

0,04 |

20,9 |

1,56 |

0,04 |

20,9 |

1,6 |

0,04 |

20,9 |

1,63 |

0,04 |

20,9 |

1,74 |

0,04 |

20,9 |

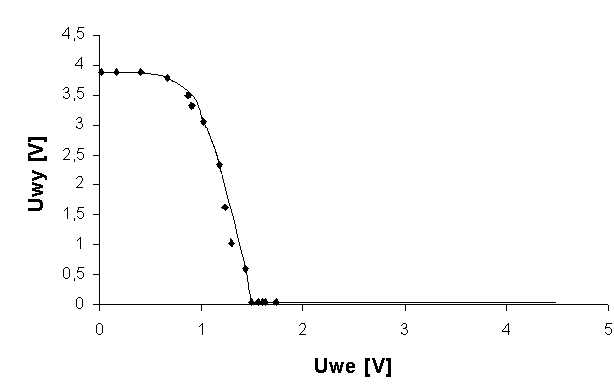

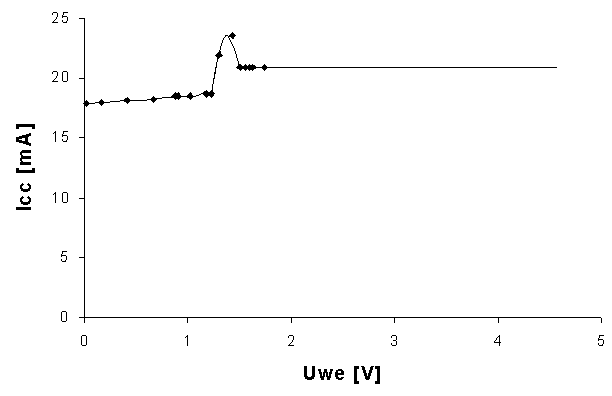

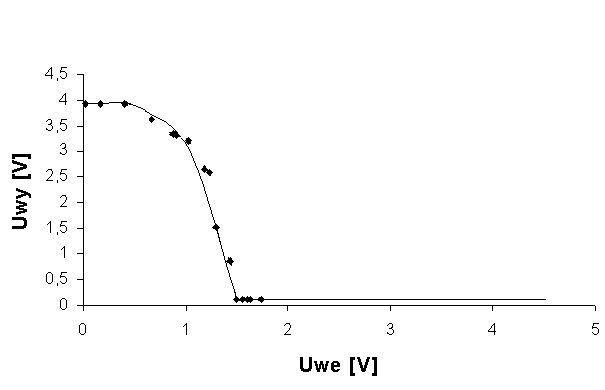

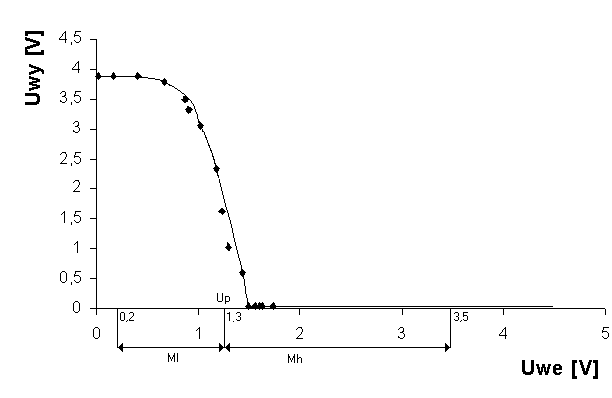

Na podstawie wyników otrzymaliśmy następujące charakterystyki dla braku obciążenia :

Dla obciążenia dwóch bramek otrzymaliśmy następujące pomiary :

Uwe [V] |

Uwy [V] |

Icc [mA] |

0,02 |

3,93 |

18,7 |

0,17 |

3,93 |

18,7 |

0,41 |

3,93 |

18,7 |

0,67 |

3,61 |

18,7 |

0,88 |

3,45 |

18,7 |

0,91 |

3,38 |

18,7 |

1,02 |

3,28 |

18,8 |

1,18 |

2,66 |

18,9 |

1,23 |

2,64 |

18,9 |

1,3 |

1,66 |

27,1 |

1,43 |

0,69 |

26,7 |

1,5 |

0,59 |

26,4 |

1,56 |

0,2 |

21,3 |

1,6 |

0,09 |

21,2 |

1,63 |

0,08 |

21,1 |

1,74 |

0,08 |

21,1 |

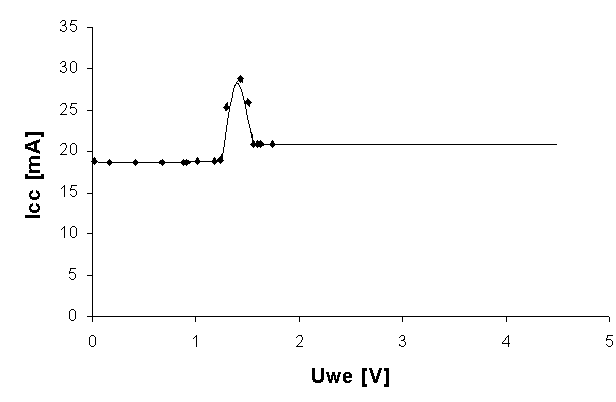

Otrzymaliśmy następujące charakterystyki dla obciążenia dwóch bramek :

Dla obciążenia pięciu bramek otrzymaliśmy następujące wyniki :

Uwe [V] |

Uwy [V] |

Icc [mA] |

0,02 |

3,93 |

18,8 |

0,17 |

3,93 |

18,7 |

0,41 |

3,93 |

18,6 |

0,67 |

3,63 |

18,6 |

0,88 |

3,33 |

18,7 |

0,91 |

3,31 |

18,7 |

1,02 |

3,2 |

18,75 |

1,18 |

2,65 |

18,85 |

1,23 |

2,6 |

18,9 |

1,3 |

1,52 |

25,4 |

1,43 |

0,85 |

28,8 |

1,5 |

0,1 |

25,9 |

1,56 |

0,1 |

20,8 |

1,6 |

0,1 |

20,8 |

1,63 |

0,1 |

20,8 |

1,74 |

0,1 |

20,8 |

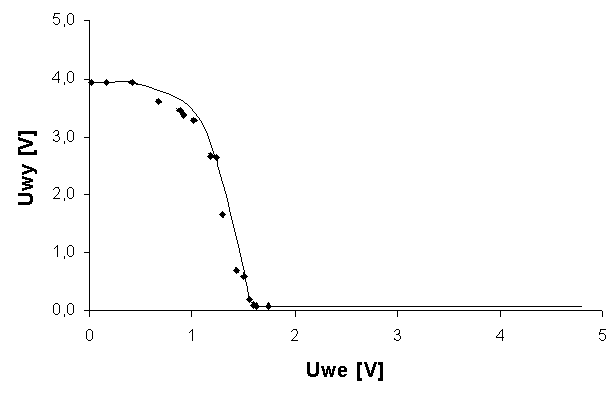

Otrzymaliśmy następujące charakterystyki dla obciążenia pięciu bramek :

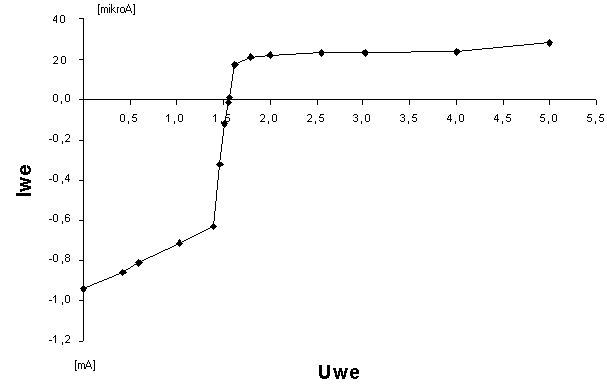

charakterystyka wejściowa

Pomiary przeprowadziliśmy w oparciu o poniższy schemat obwodu

Uzyskaliśmy następujące wyniki :

U we [V] |

I we [mA] |

0,00 |

-0,940 |

0,42 |

-0,860 |

0,59 |

-0,810 |

1,03 |

-0,710 |

1,40 |

-0,630 |

1,46 |

-0,320 |

1,51 |

-0,120 |

1,55 |

-0,010 |

1,57 |

0,01μ |

1,62 |

0,17μ |

1,80 |

0,21μ |

2,00 |

0,22μ |

2,55 |

0,23μ |

3,02 |

0,23μ |

4,00 |

0,24μ |

|

0,28μ |

Charakterystyka wejściowa dla bramki TTL :

c) charakterystyki wyjściowe

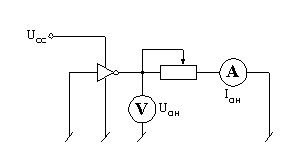

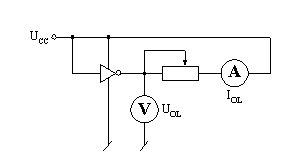

Charakterystyki wyjściowe wyznaczaliśmy dla stanu niskiego i wysokiego. Posłużyliśmy się w tym celu następującymi schematami pomiarowymi.

Bramka w stanie wysokim :

Bramka w stanie niskim :

Uzyskaliśmy następujące wyniki :

Stan niski Stan wysoki

U ol [V] |

I ol [mA] |

|

|

U oh [V] |

I oh [mA] |

0,114 |

5,00 |

|

|

3,4 |

2 |

0,122 |

6,20 |

|

|

3,42 |

3 |

0,131 |

6,80 |

|

|

3,39 |

3 |

0,155 |

9,65 |

|

|

3,14 |

5 |

0,194 |

15,93 |

|

|

2,36 |

11 |

0,240 |

23,60 |

|

|

1,65 |

15 |

0,411 |

50,11 |

|

|

1,02 |

19 |

0,460 |

55,72 |

|

|

0,5 |

22,5 |

0,575 |

71,83 |

|

|

0,25 |

24 |

0,700 |

83,45 |

|

|

0,1 |

25 |

1,864 |

102,50 |

|

|

0,03 |

27 |

2,750 |

109,00 |

||||

4,320 |

121,30 |

||||

4,940 |

126,45 |

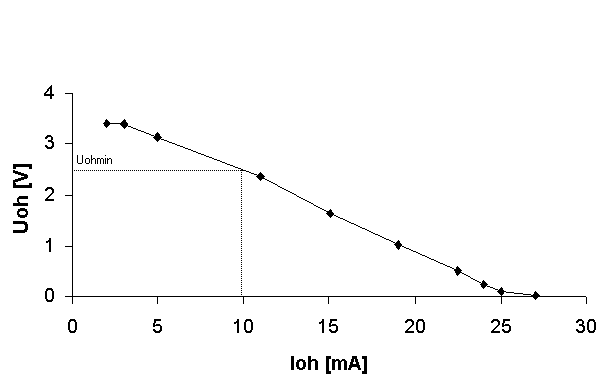

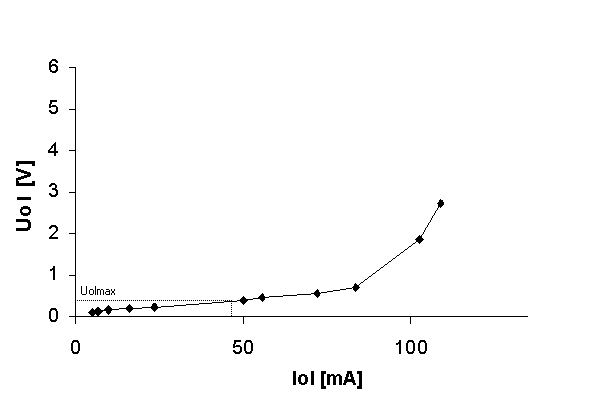

Na podstawie powyższych danych otrzymaliśmy następujące charakterystyki wyjściowe

Stan wysoki :

Stan niski :

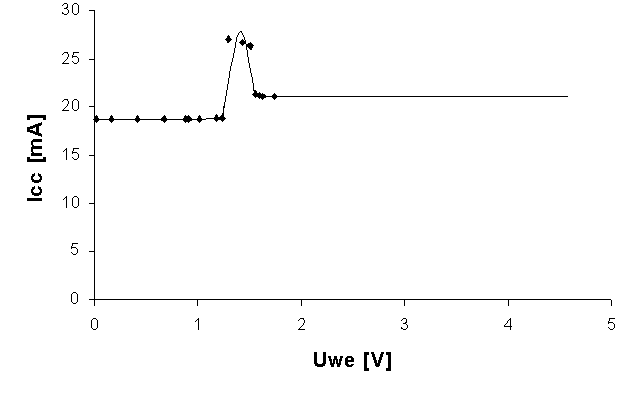

d) marginesy zakłóceń

Korzystając z wyznaczonej wartości napięcia przełączenia, wynoszącej Up=1,3 i wyznaczonej charakterystyki przejściowej bramki wyznaczyliśmy marginesy zakłóceń statycznych według wzorów:

ML = UP - UOL typ

MH = UOH typ - UP

Podstawiając do wzoru otrzymaną wartość napięcia przełączenia oraz typowe wartości napięć dla układów TTL otrzymujemy:

ML = 1,3 V - 0,2 V = 1,1 V

MH = 3,5 V - 1,3 V = 2,2 V

Wyniki w przybliżeniu odpowiadają oczekiwanym wartościom ( ML = 1,2 V i MH = 2,3 V).

Wartości te zaznaczone są na poniższym wykresie (charakterystyka przejściowa bez obciążenia):

2. Bramka CMOS

charakterystyka przejściowa

Dla braku obciążenia otrzymaliśmy następujące wyniki :

Uwe |

Uwy |

0,01 |

4,98 |

0,1 |

4,99 |

0,56 |

4,99 |

0,6 |

4,98 |

0,7 |

4,49 |

0,83 |

4,93 |

1,73 |

4,14 |

2,68 |

4,98 |

2,76 |

0,52 |

2,77 |

1,18 |

2,78 |

0,52 |

2,81 |

0,01 |

3,2 |

0,01 |

|

|

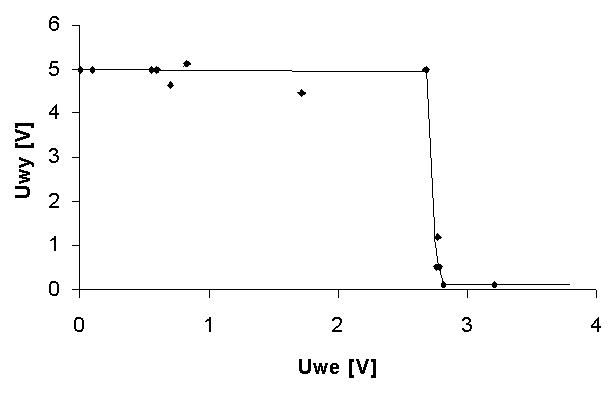

Uzyskaliśmy następującą charakterystykę dla braku obciążenia :

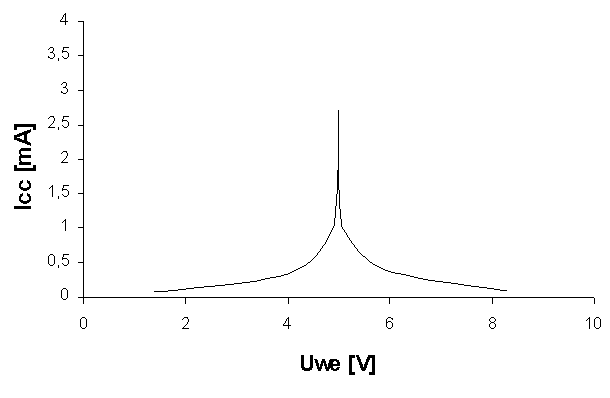

Poniżej przedstawiona jest charakterystyka dla prądu obserwowana no oscyloskopie :

3. Wnioski

Wszystkie wyznaczone charakterystyki pokrywają się z teoretycznymi, nie odbiegają kształtem od oczekiwanych. Marginesy zakłóceń w przybliżeniu odpowiadają typowym wartościom. W wyniku początkowych problemów z połączeniem układu dla bramki logicznej TTL i krótkiego czasy trwania laboratorium, nie zdążyliśmy wyznaczyć wszystkich charakterystyk bramki CMOS, które obserwowaliśmy na ekranie oscyloskopu w trakcie wprowadzenia do ćwiczenia laboratoryjnego.

Uwy [V]

Icc [5 mA]

Uwe [V]

Uwe [V]

[V]

Wyszukiwarka

Podobne podstrony:

Koordynacja ze strzałem na dwie bramki cz 3

Bramki Logiczne

Bramki i funkcje specjalne użyte przy budowie układu

bramki

bramki 2

bramki char

EEKsem3 bramki logiczne w7

bramki logiczne, Szkoła, Systemy Operacyjnie i sieci komputerowe, utk, semestr I

Bramki logiczne

Bramki TTL

BRAMKI

o fashizme v rossii i demokraticheskom lozunge net krasno

krestnyj put rossii

istorija rossii s drevnejshih vremen kniga viii 1703 nachalo

paradoksy i prichudy filosemitizma i antisemitizma v rossii

istorija skautinga v rossii

istorija rossii s drevnejshih vremen kniga iv 1584 1613

więcej podobnych podstron