Temat i plan wykładu

Tranzystor jako element cyfrowy

1. Wprowadzenie

2. Tranzystor jako łącznik

3. Inwerter tranzystorowy

4. Charakterystyka przejściowa

5. Odporność na zakłócenia

6. Definicja czasów przełączania

7. Czas propagacji bramki

Wprowadzenie

Technika cyfrowa jest obszarem wiedzy o całkowicie

interdyscyplinarnym obliczu. Jej zagadnienia kształtowane z

jednej strony przez języki opisu sprzętu, a z drugiej przez

programowalne moduły logiczne, śmiało mogą być zaliczone

zarówno do Informatyki, Elektroniki jak i Telekomunikacji.

Techniki projektowania układów cyfrowych polegają już nie tylko

na składaniu układu z dostępnych komponentów, a raczej na

procesie formalnej, abstrakcyjnej specyfikacji projektu w

odpowiednim języku opisu sprzętu (HDL – Hardware Description

Language) oraz na transformacji tej specyfikacji przy użyciu

różnorodnych narzędzi komputerowego wspomagania projektowania

CAD (Computer Aided Design). Technika cyfrowa ma wielki wpływ

na wszystkie obszary ludzkiej aktywności; między innymi

radykalnie przeobraziła metody i formy komunikacji społecznej

zarówno w ujęciu zbiorowym jak i indywidualnym, a układy

cyfrowe można dziś znaleźć niemal w każdym urządzeniu

technicznym.

Wprowadzenie

W zależności od technologii i techniki projektowania

specjalizowane układy scalone klasyfikujemy w następujących

kategoriach:

a) układy zamawiane przez użytkownika (Full Custom),

b) układy projektowane przez użytkownika (Semi Custom),

c) układy programowane przez użytkownika (FPLD – Field

Programmable Logic Devices).

Coraz większą rolę w technice cyfrowej odgrywają programowalne

moduły logiczne (FPLD – Field Programmable Logic Devices),

krótko zwane układami (strukturami) programowalnymi.

Układy programowalne to – z punktu widzenia struktury – układy

typu matrycowego lub komórkowego, jednak z możliwością

programowania połączeń na drodze elektrycznej. W ich przypadku

proces produkcyjny jest odmienny – producent dostarcza

„prefabrykaty” projektantowi, który może je zaprogramować u

siebie „na biurku”.

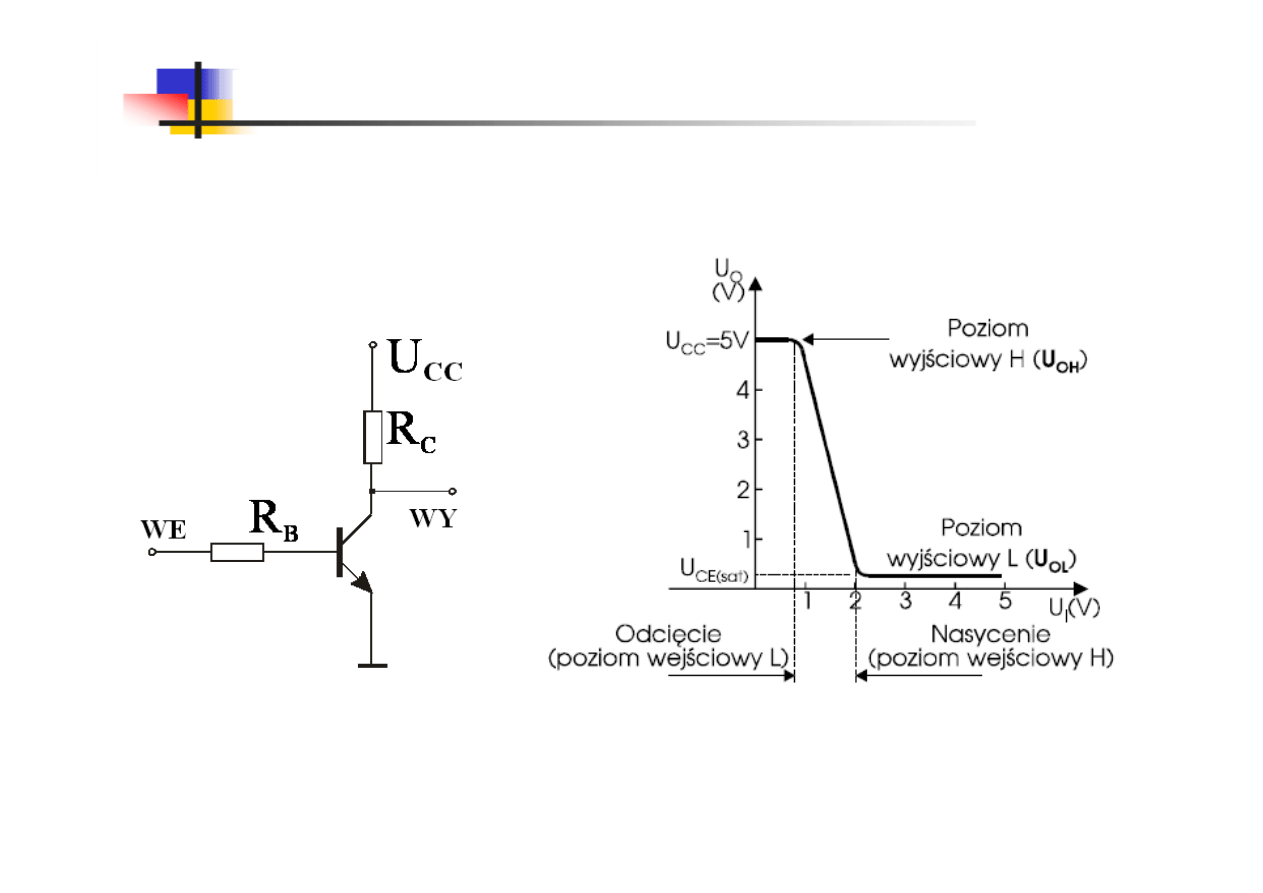

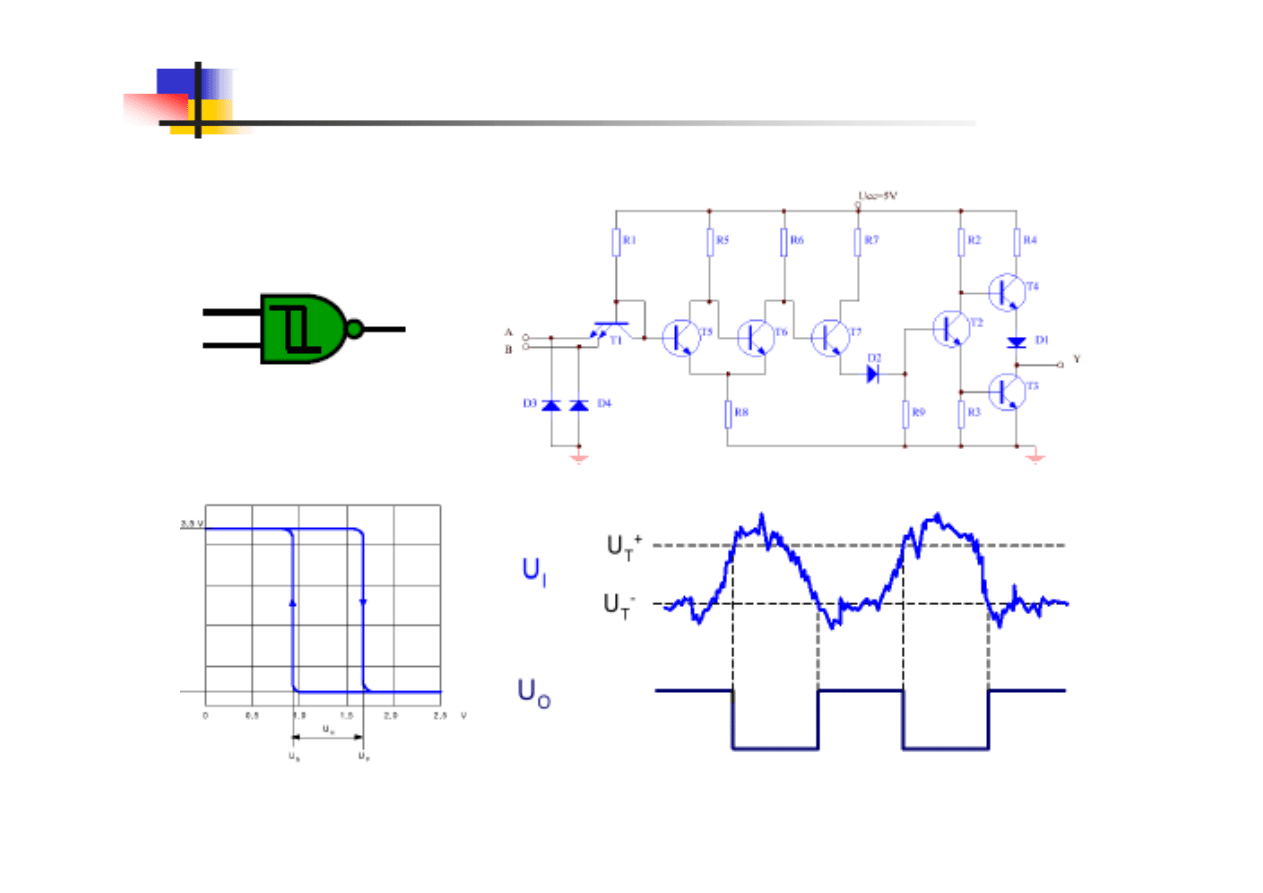

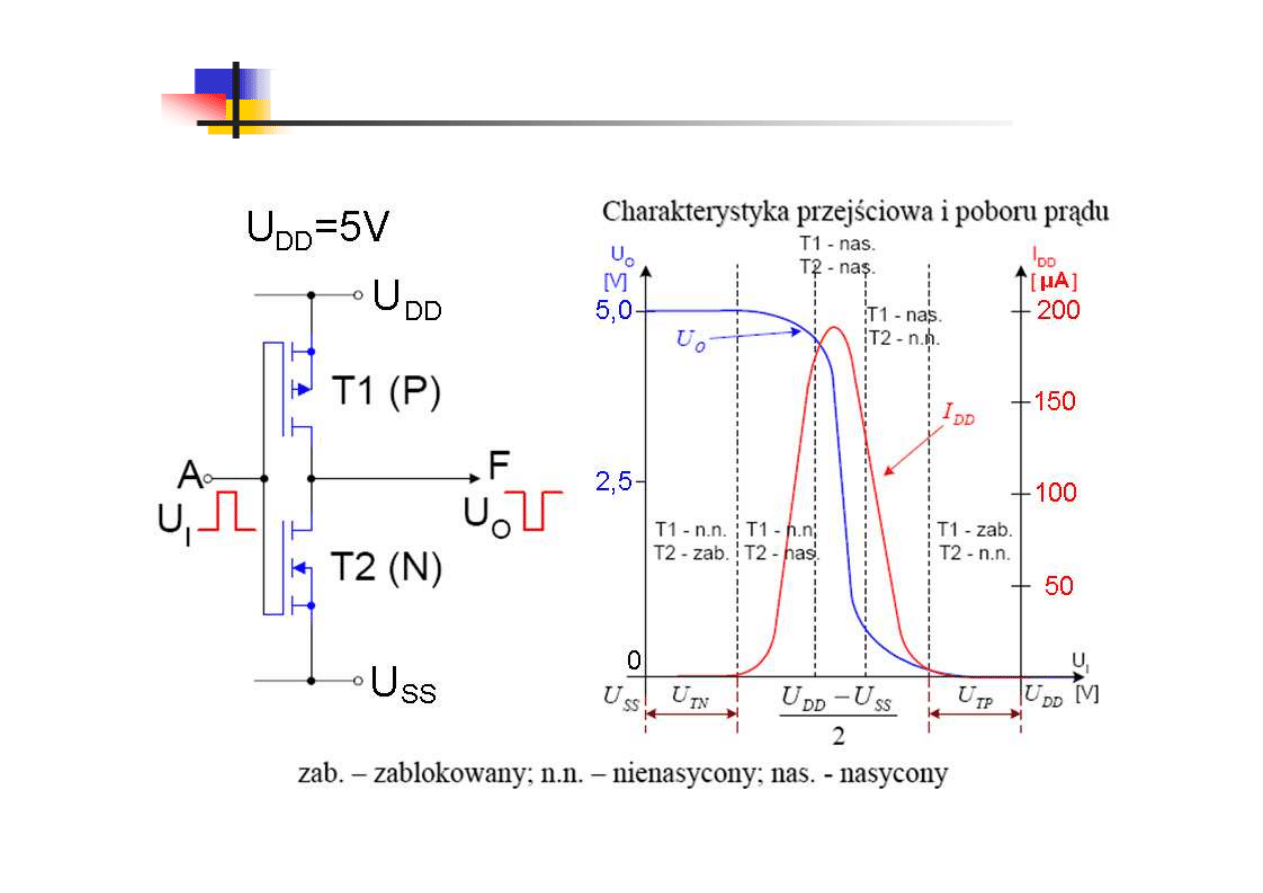

Charakterystyka przejściowa inwertera

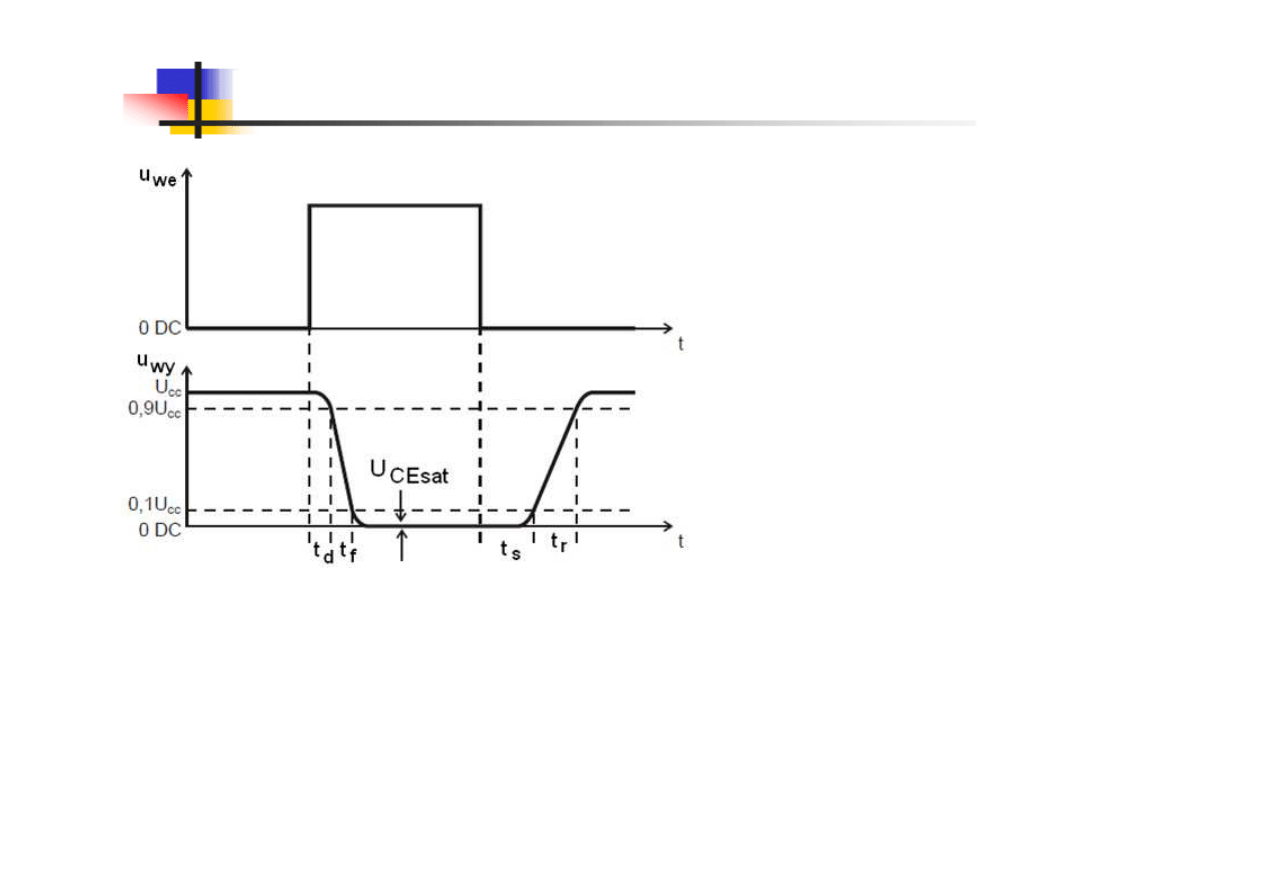

Definicja czasów przełączania

t

d

czas opó

ź

nienia (ang. delay time)

t

f

czas opadania (ang. fall time)

t

s

czas magazynowania (ang. storage time)

t

r

czas narastania (ang. rise time)

Czas magazynowania t

s

wyst

ę

puje przy zatykaniu

tranzystora, podczas

wychodzenia ze stanu

nasycenia (U

CE

=U

CEsat

).

Je

ż

eli U

CE

> U

CEsat

to t

s

=0.

Szybkie ł

ą

czniki – tranzystory

nienasycone.

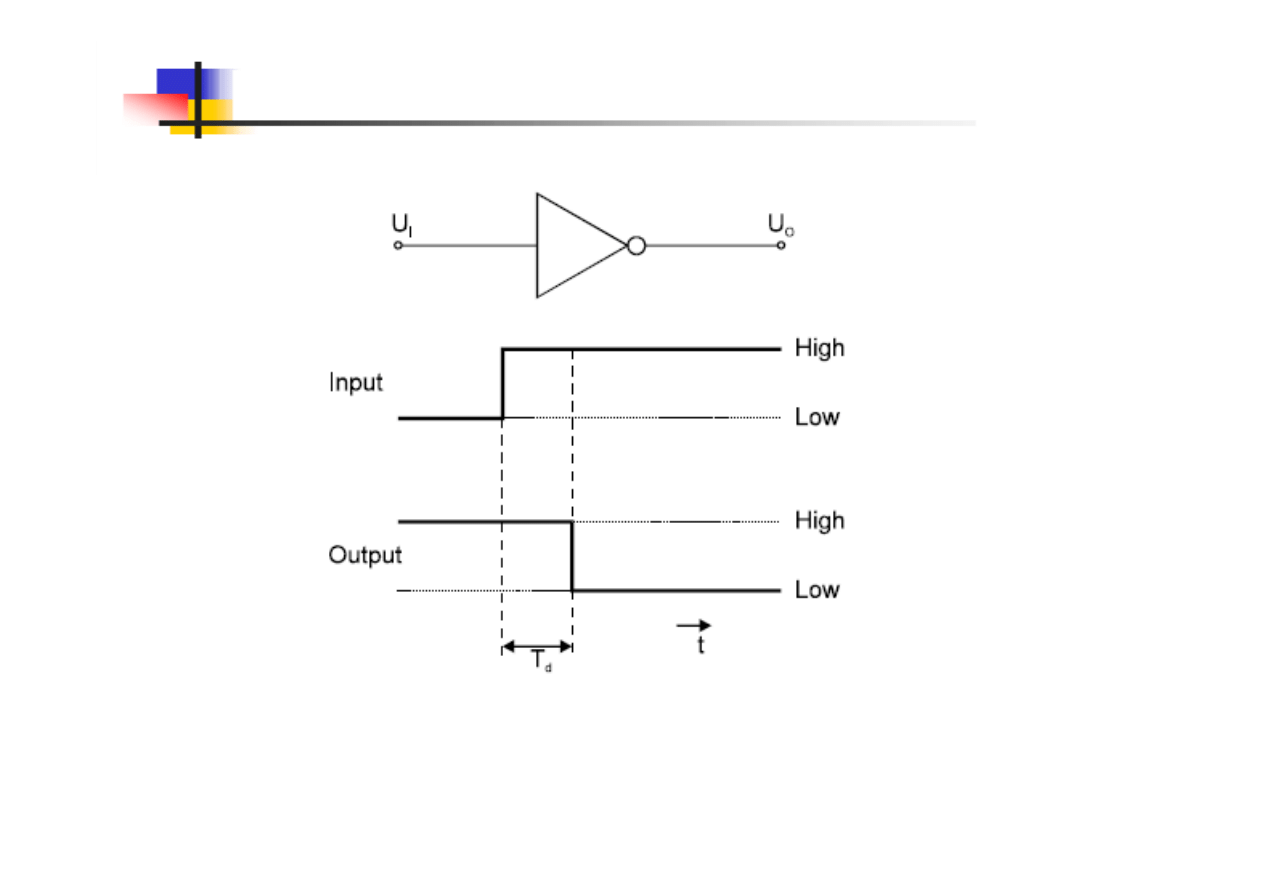

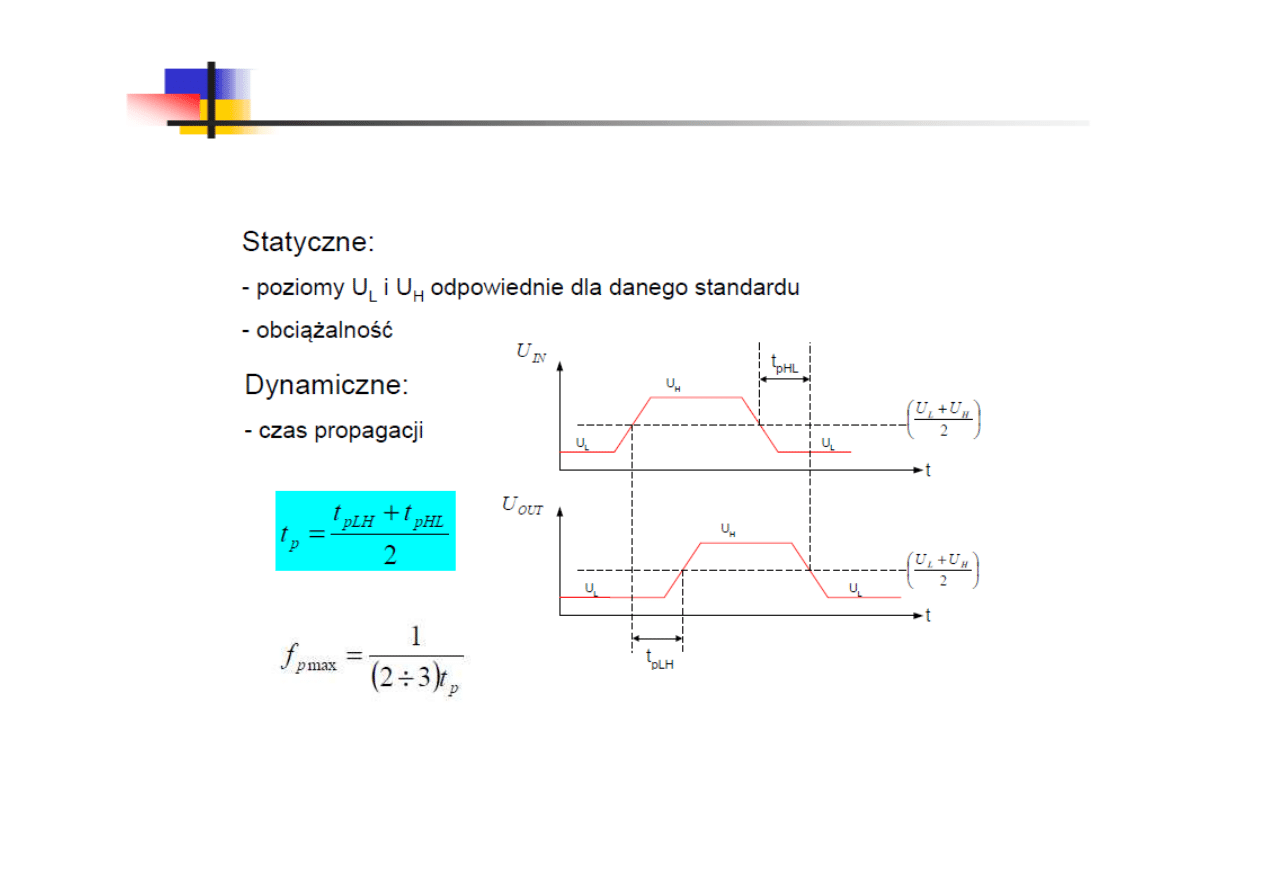

Czas propagacji inwertera

Czas propagacji (T

d

) - określa czas opóźnienia

odpowiedzi układu na sygnał sterujący i jest podstawową

miarą szybkości działania układu cyfrowego.

Temat i plan wykładu

Podstawowe bramki logiczne

1. Elementarne funkcje logiczne, symbole

2. Struktura bramek bipolarnych, CMOS i BiCMOS

3. Parametry bramek

4. Rodziny układów cyfrowych

5. Bramki transmisyjne

6. Elastyczność łączeniowa bramek

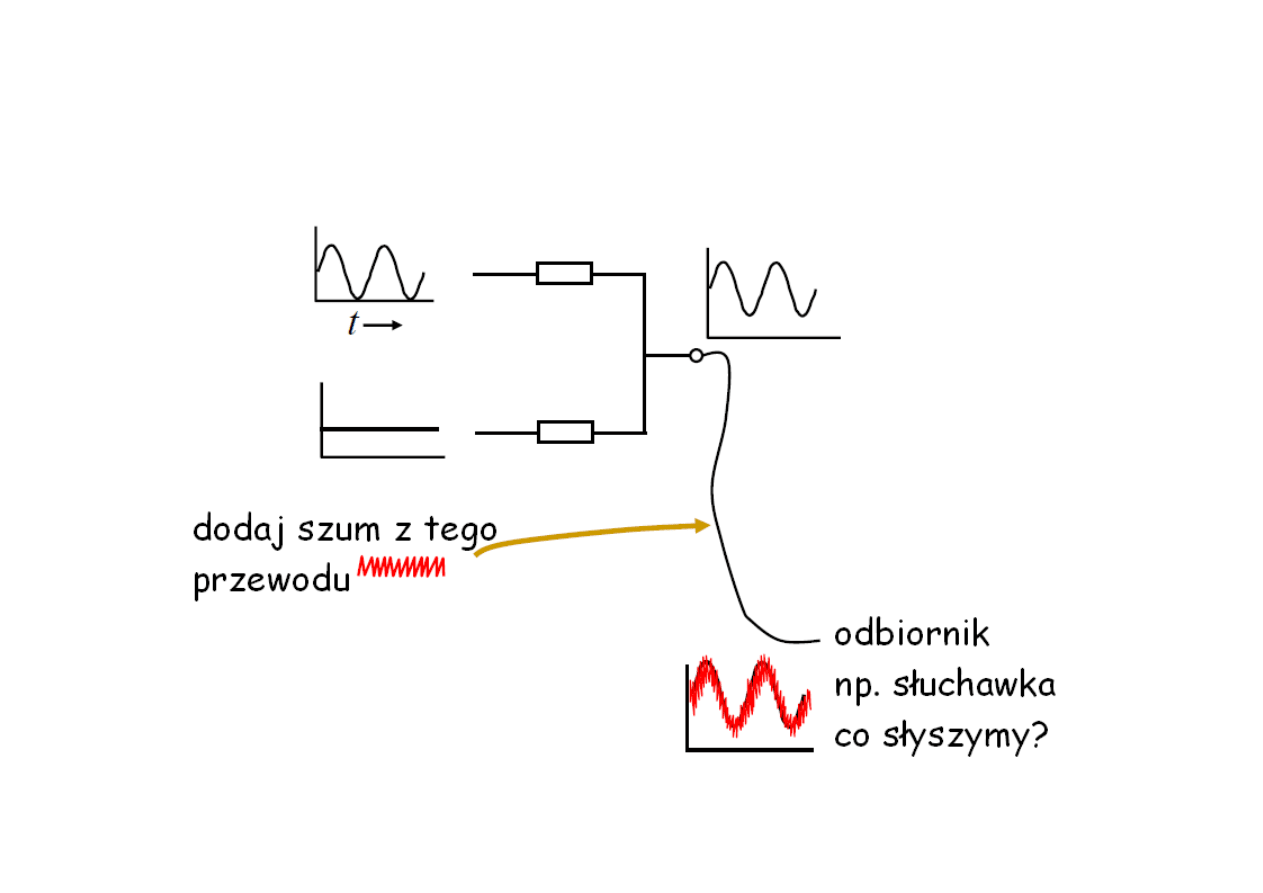

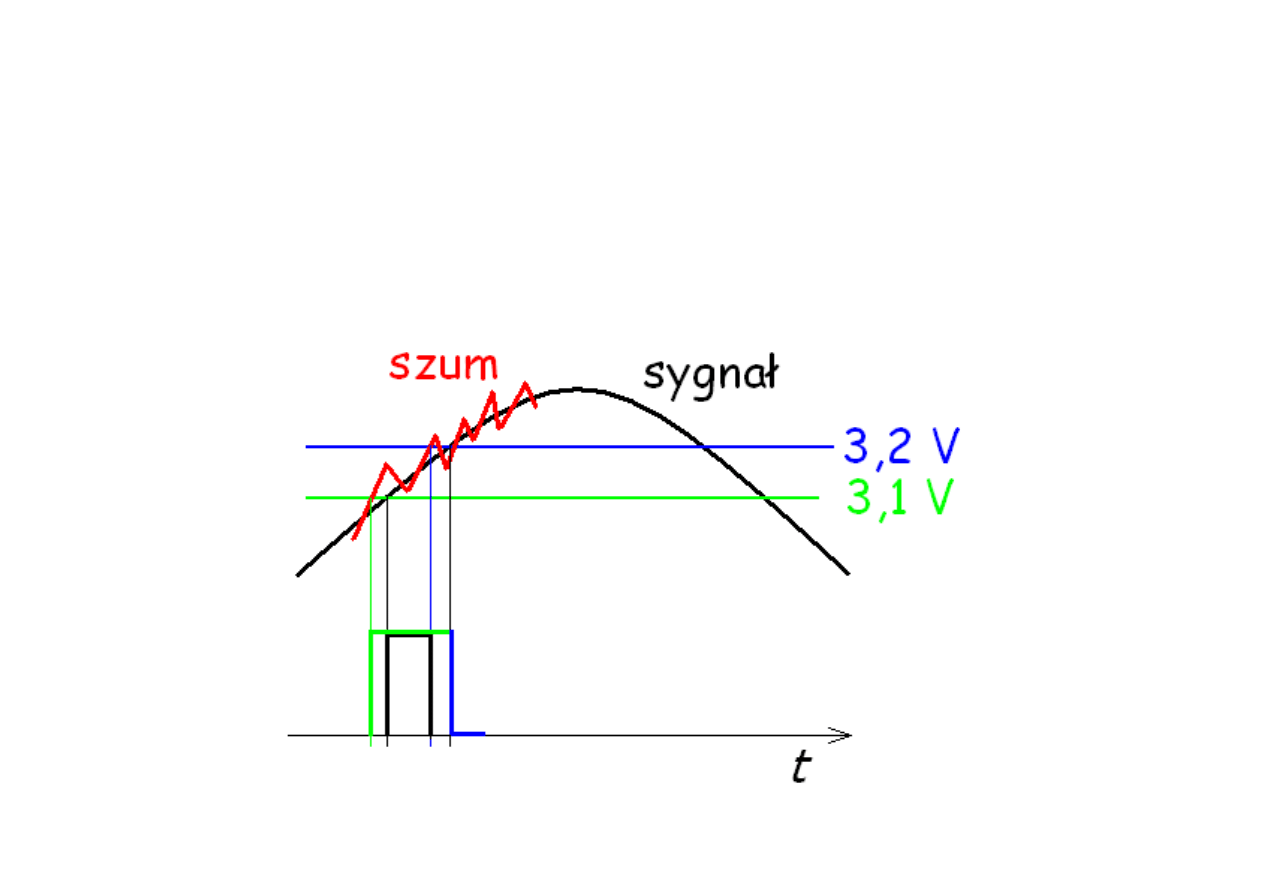

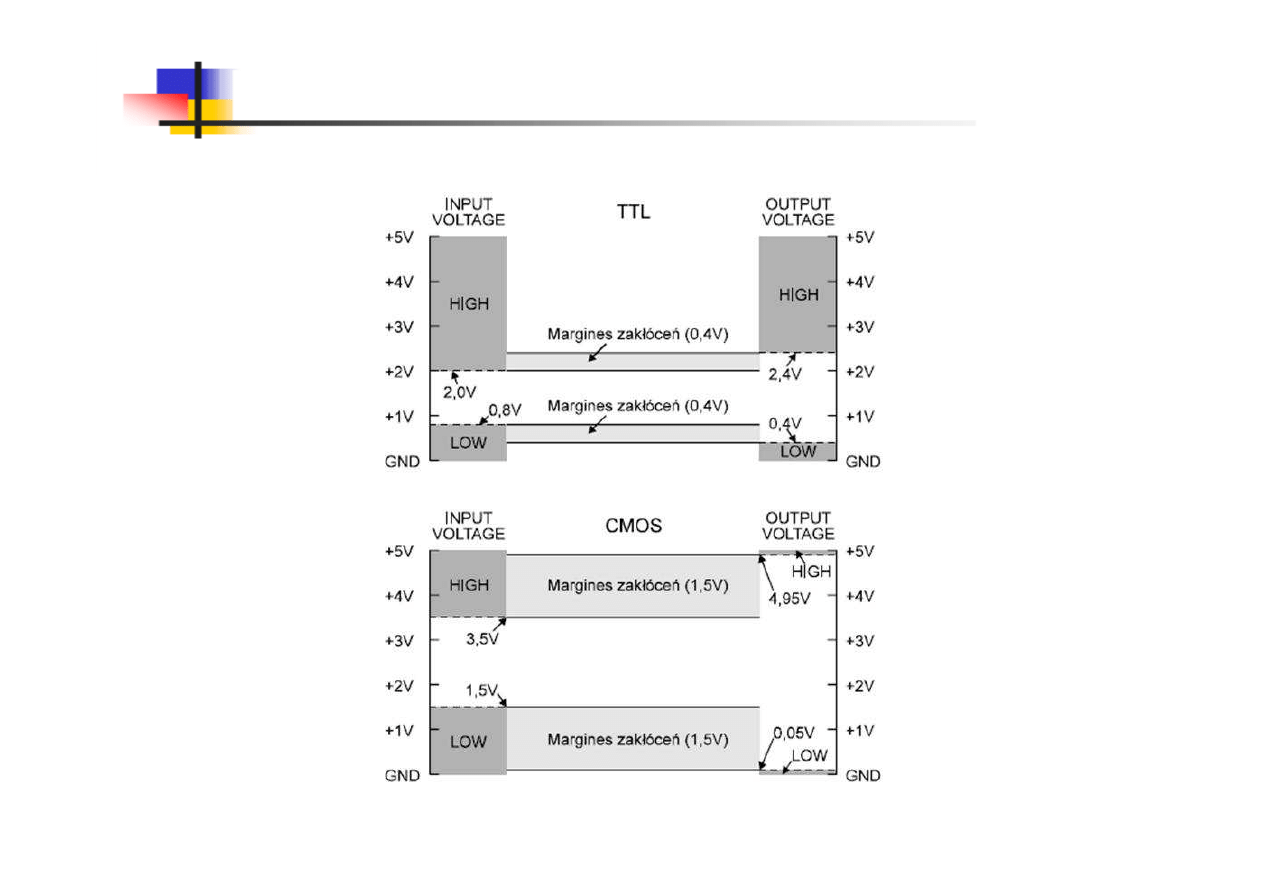

Problemy z zakłóceniami

zakłócenia w linii

transmisyjnej

… zakłócenie utrudnia (nie pozwala)

wychwycenie niewielkich różnic pomiędzy

sygnałami np. między 3,1 V a 3,2 V

Sygnał z szumem (zakłóceniami)

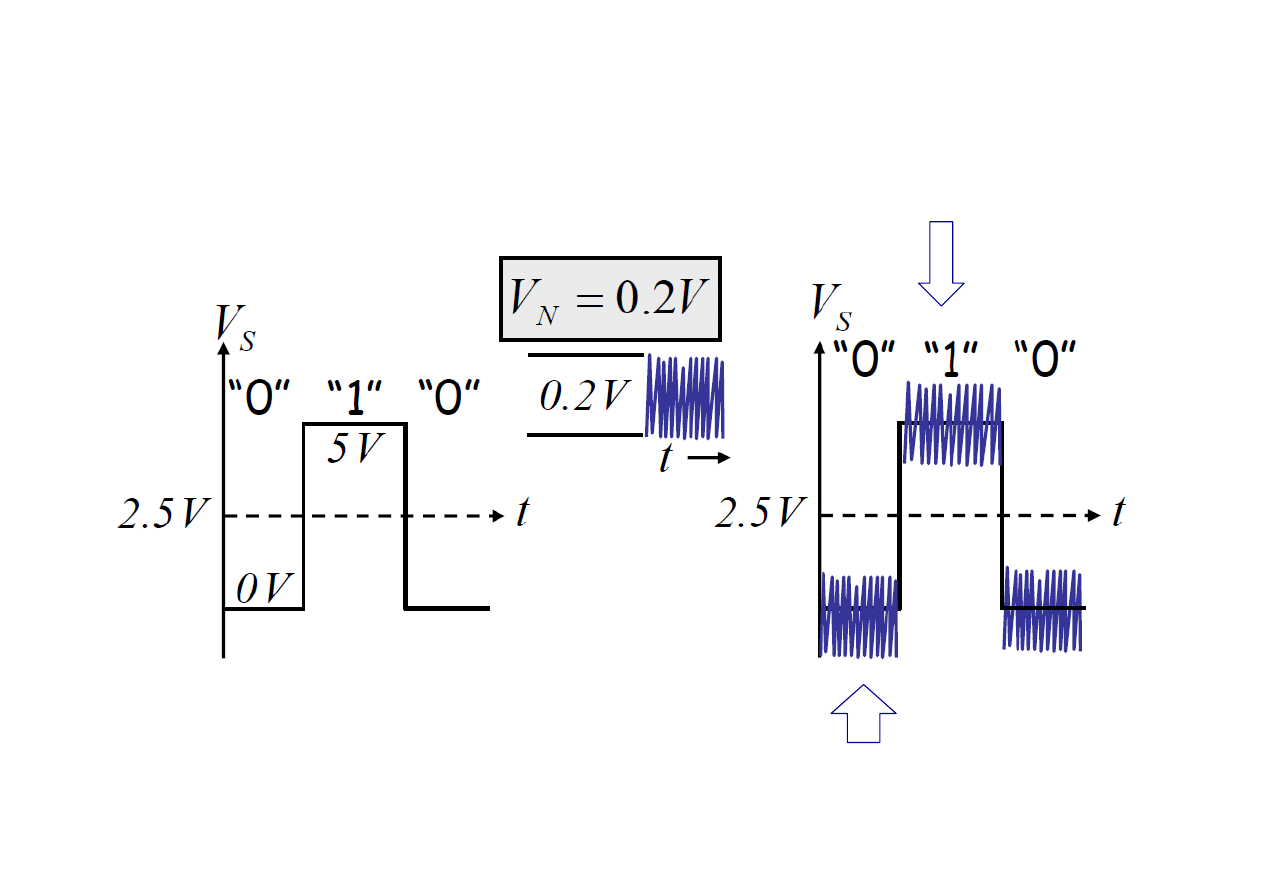

Zakłócenia napięcia zasilającego

Zakłócenia uziemieniowe

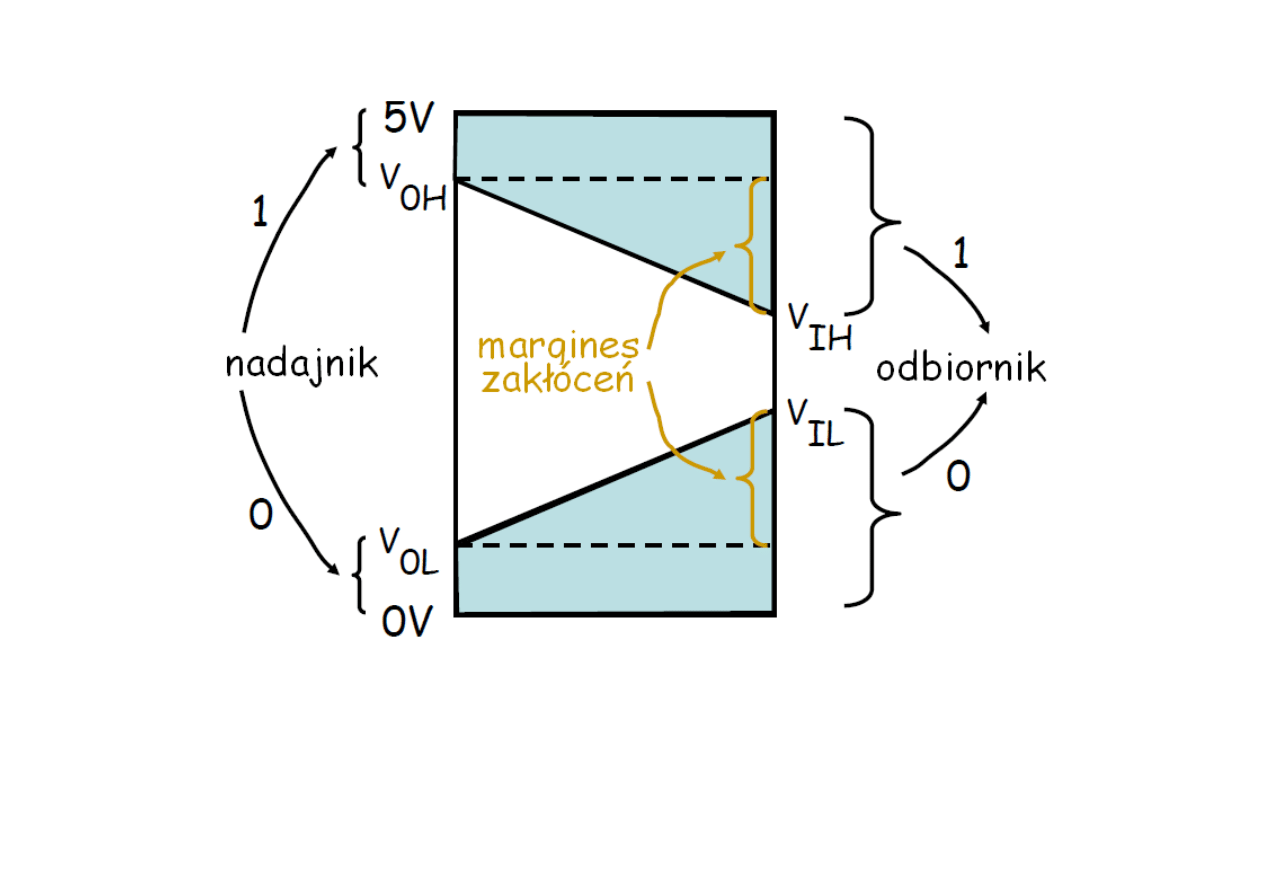

“1” margines zakłóceń: VIH - V0H

“0” margines zakłóceń: VIL - V0L

System cyfrowy

Lepsza odporność na zakłócenia.

Wielkość marginesu zakłóceń

decyduje o odporności na

zakłócenia.

Co się kryje

wewnątrz

bramki

cyfrowej?

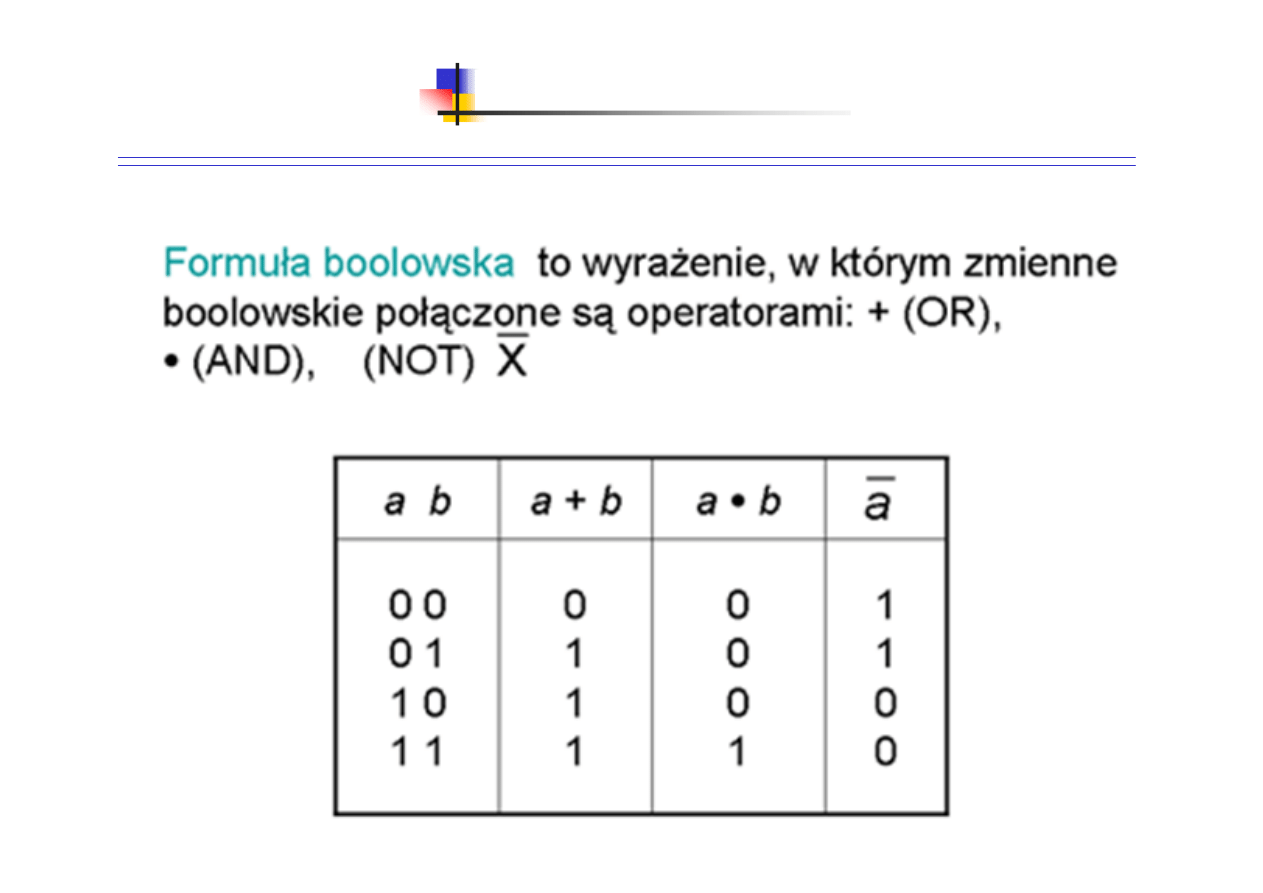

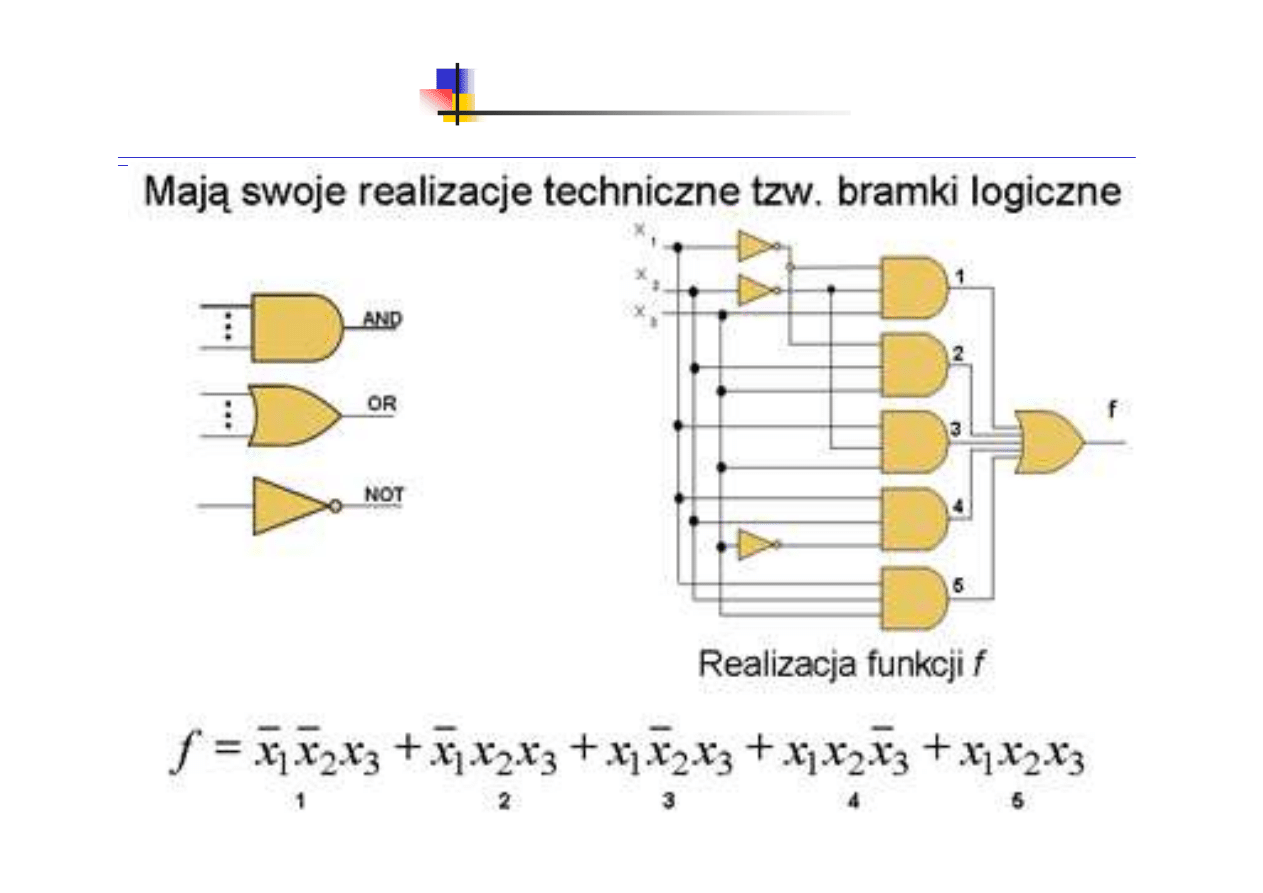

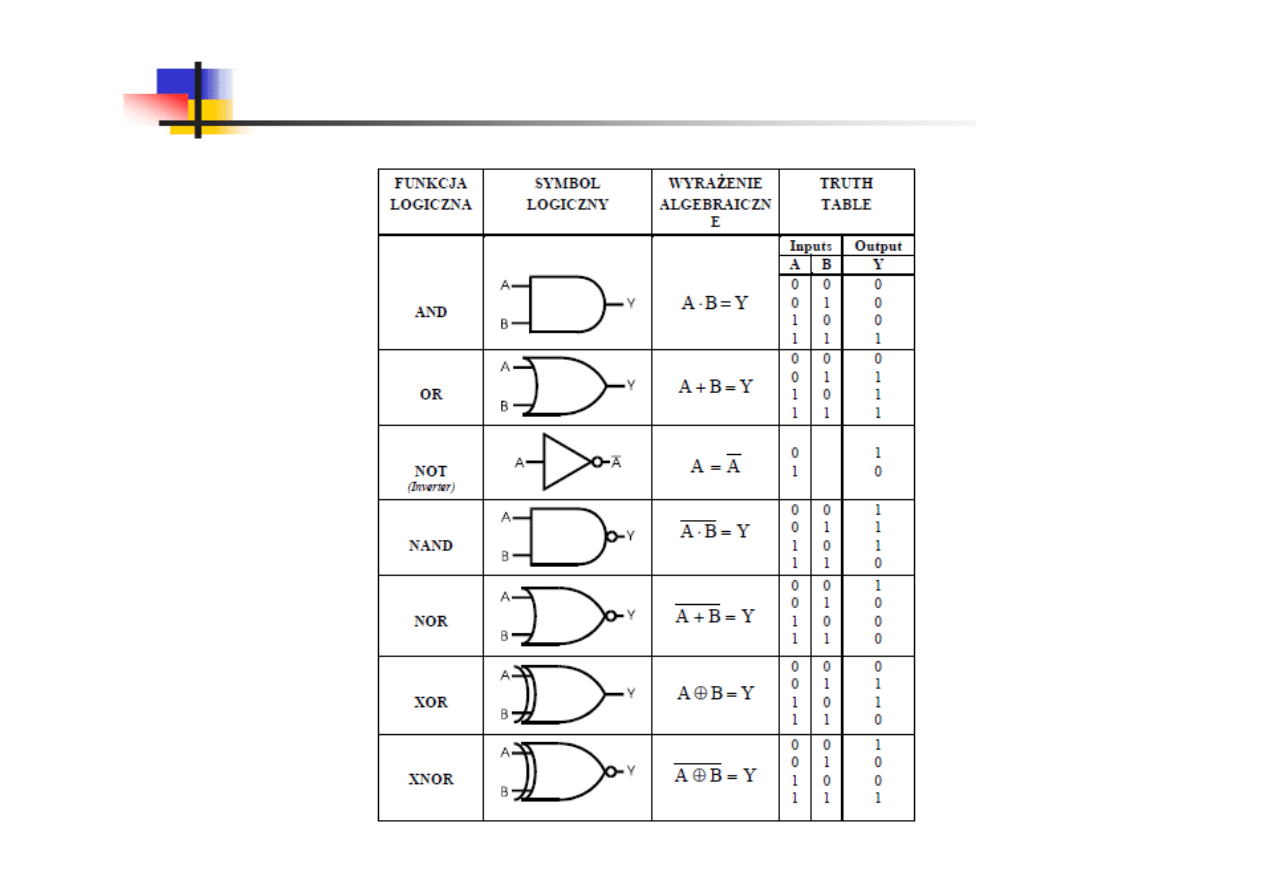

Definicja bramki logicznej

Bramki – scalone układy

elektroniczne realizujące

funkcje algebry Boole’a

.

Formuła boolowska

Operatory logiczne

Operatory logiczne

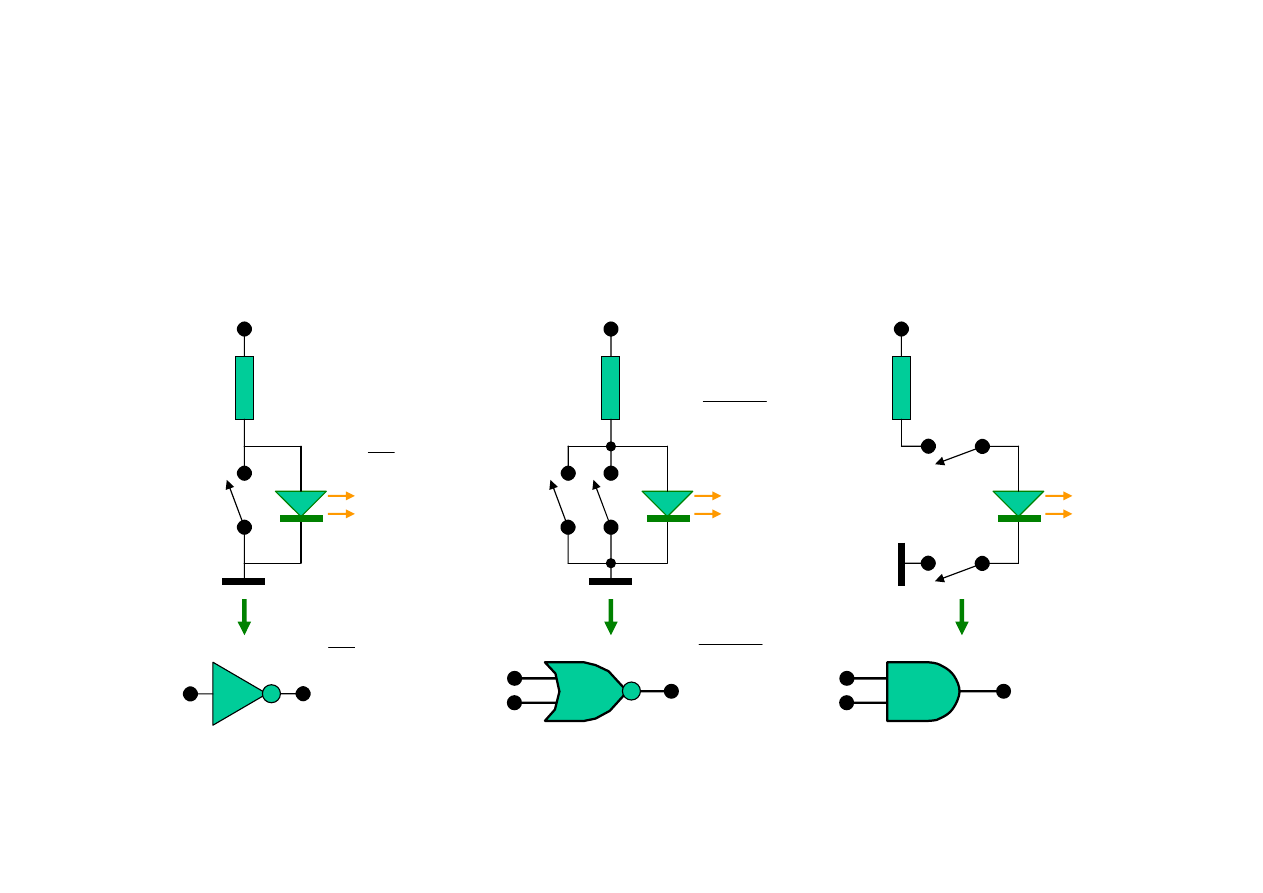

Modele prostych funktorów logicznych

A

A

Y

=

NOT

U

zaś

>+3V

A

A

Y

=

AND

U

zaś

>+3V

A

B

A

Y

∗

=

B

A

B

B

A

Y

∗

=

U

zaś

>+3V

A

B

A

Y

+

=

B

A

B

B

A

Y

+

=

NOR

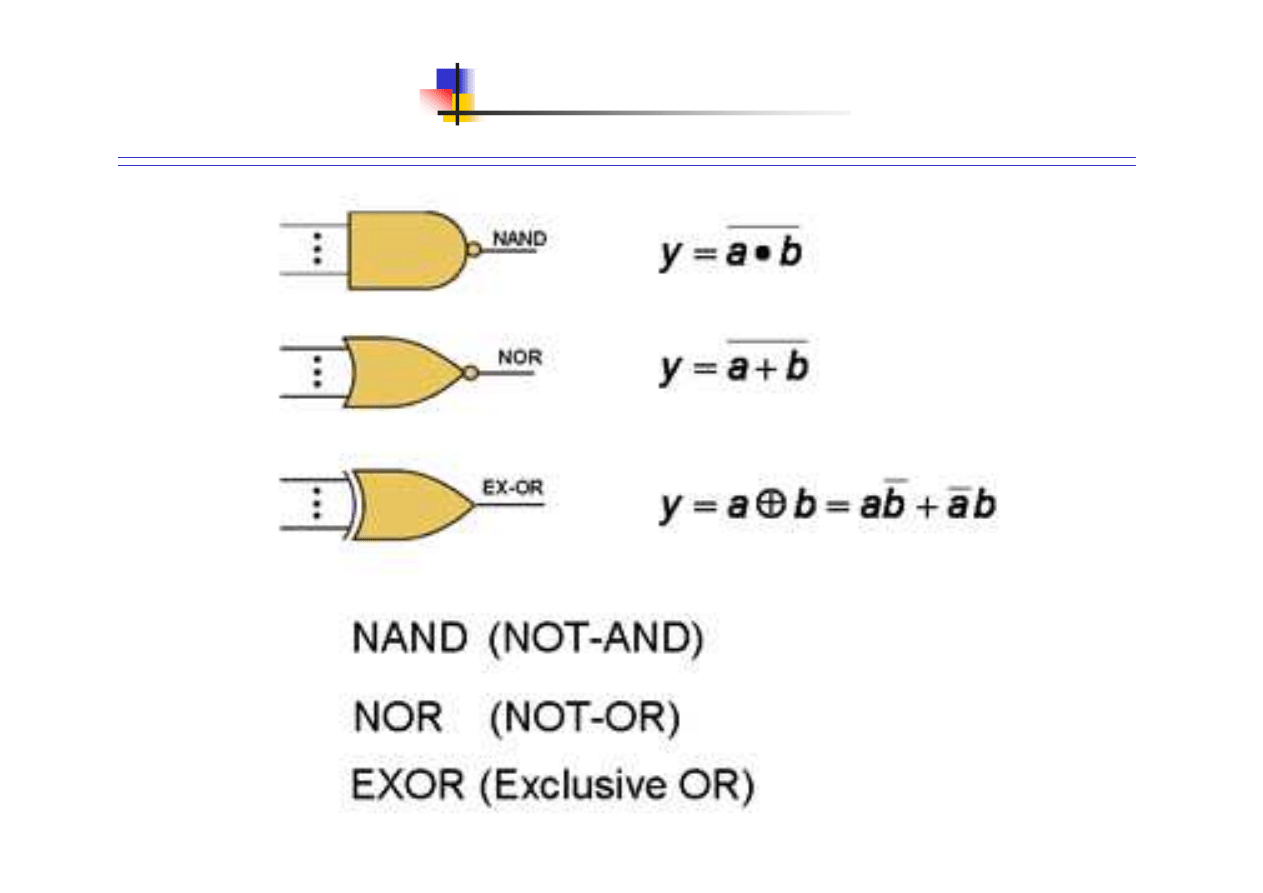

Funkcje i symbole

Klasy układów cyfrowych

TTL (Transistor – Transistor - Logic) – układy TTL,

ECL (Emiter – Coupled Logic) – układy o sprzężeniu emiterowym,

MOS (Metal – Oxide - Semiconductor) – układy MOS,

CMOS (Complementary MOS) – układy komplementarne MOS,

BiCMOS (Bipolar CMOS) – układy ,,mieszane”, bipolarne CMOS,

I

2

L (Integrated Injection Logic) – układy iniekcyjne,

CTD (Charge Transfer Device) – układy o sprzężeniu ładunkowym,

GaAs MESFET – układy GaAs.

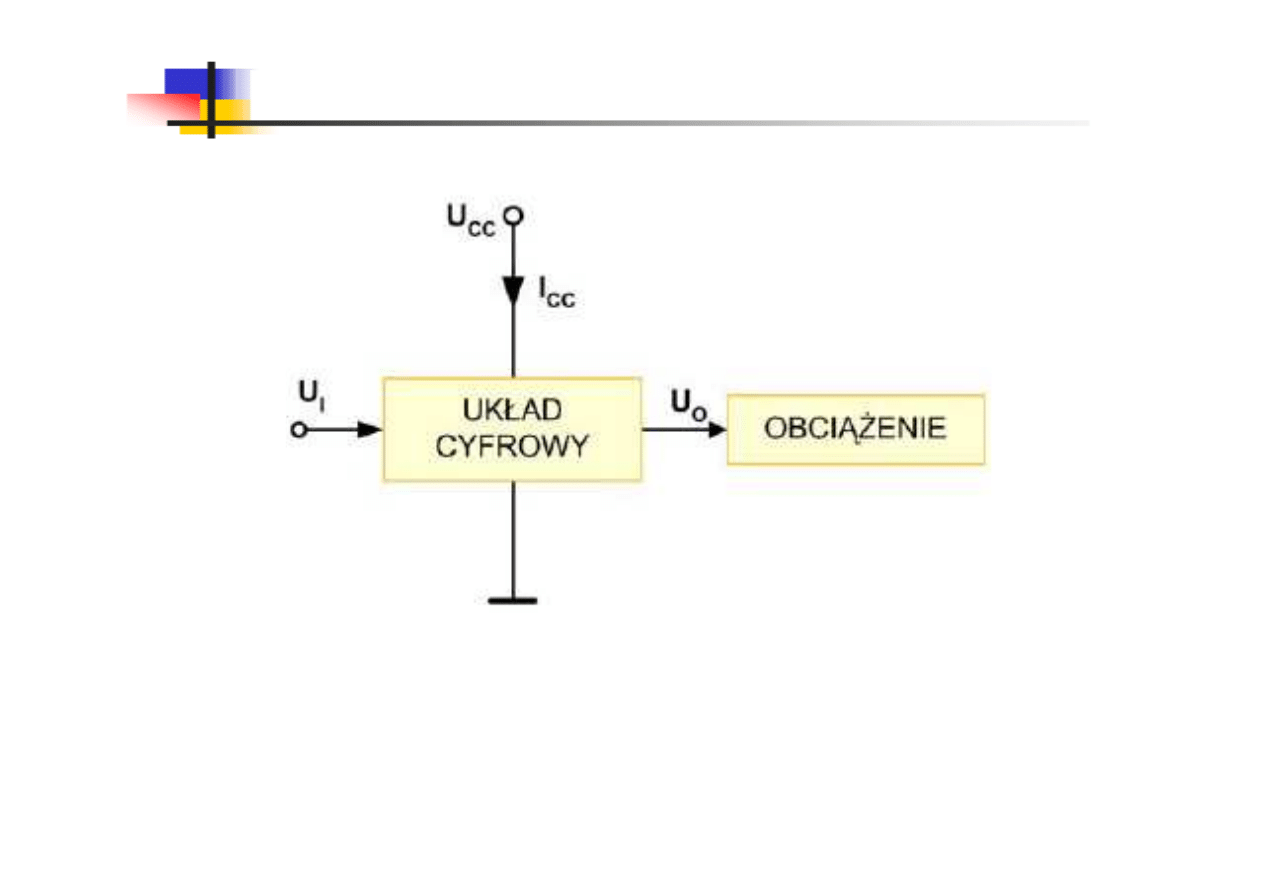

Oznaczenia napięć i prądów układu cyfrowego

U

CC

- napięcie zasilania, I

CC

– prąd zasilania, U

I

(U

O

) –

napięcie wejściowe (wyjściowe)

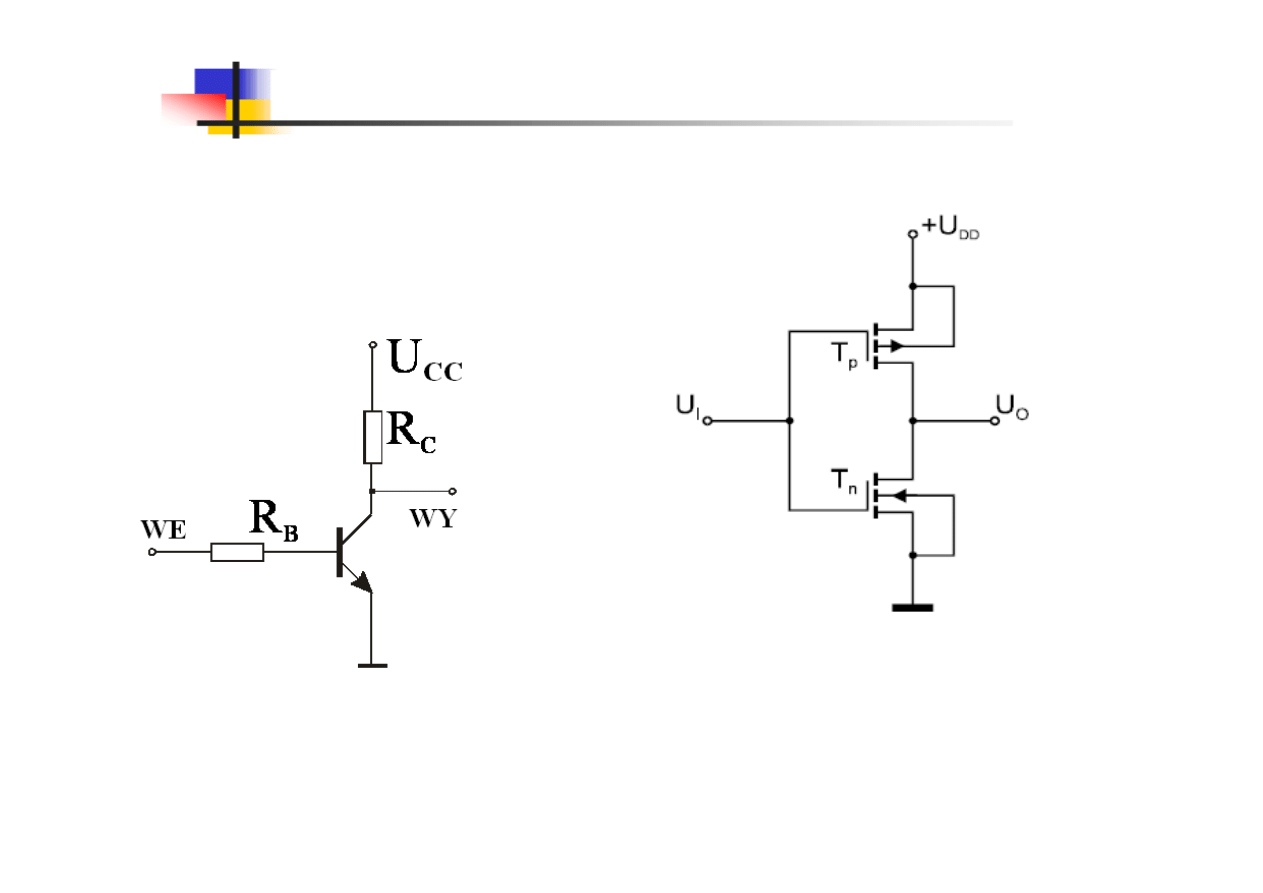

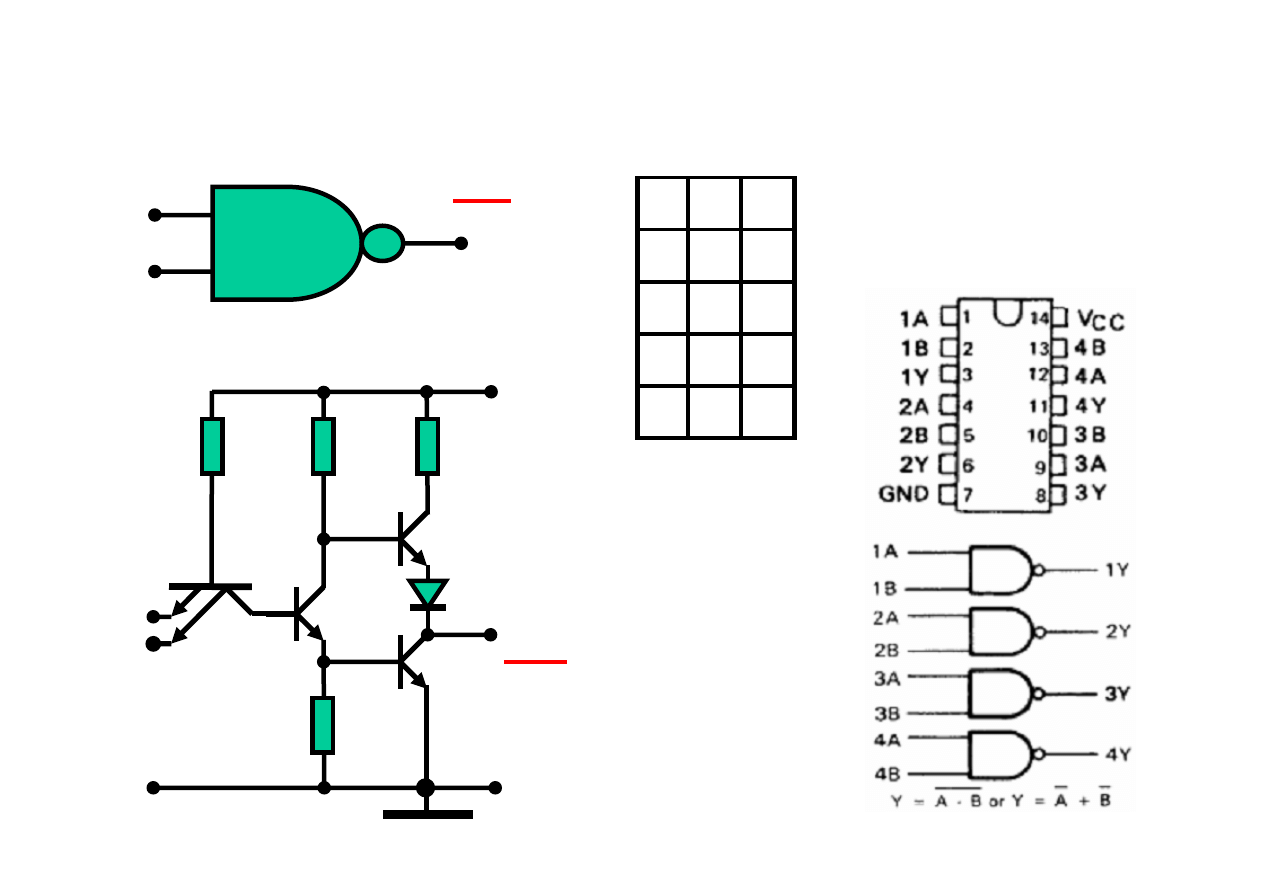

Budowa inwertera TTL i CMOS

a) inwerter TTL

b) inwerter CMOS

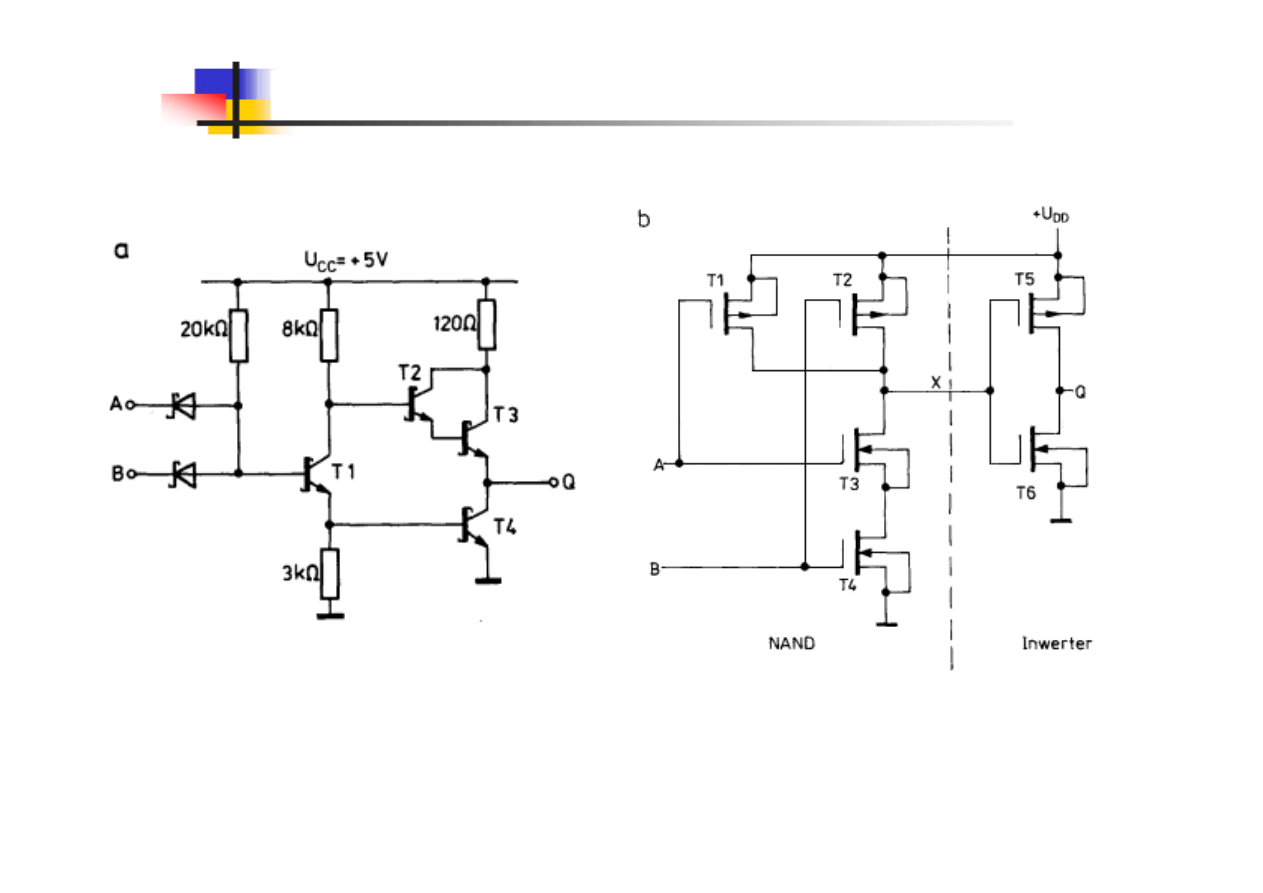

Budowa TTL i CMOS

a) Bramka NAND LS-TTL,

b) bramka AND CMOS

Parametry cyfrowych układów cyfrowych

Przy projektowaniu urządzeń z cyfrowymi

układami scalonymi istotne są następujące

parametry:

∗

∗

∗

∗ szybkość działania,

∗

∗

∗

∗ moc strat,

∗

∗

∗

∗ odporność na zakłócenia,

∗

∗

∗

∗ zgodność łączeniowa i obciążalność.

Przy konstrukcji systemów cyfrowych powinny

być znane właściwości obudów oraz

niezawodność cyfrowych układów scalonych.

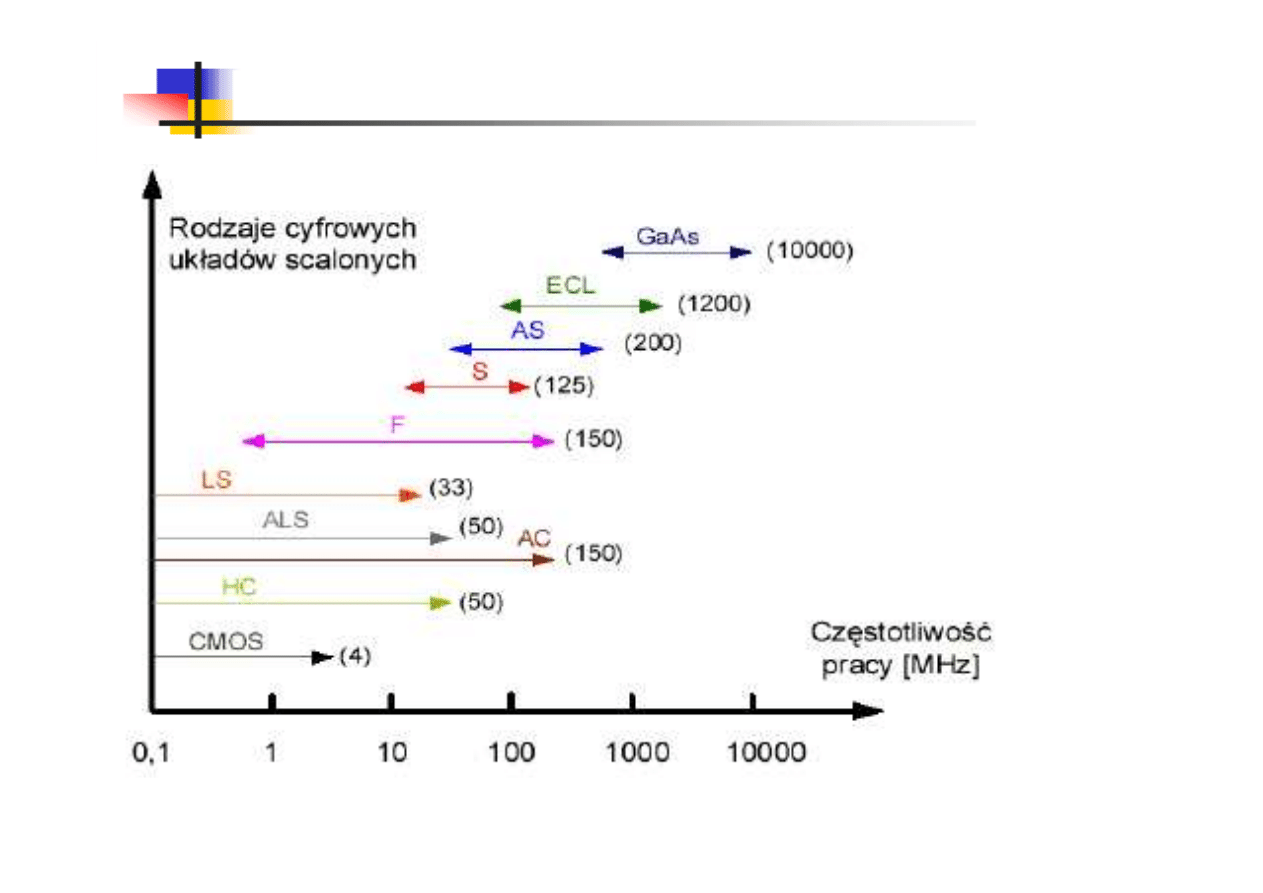

Szybkość działania – czas propagacji

TTL do 500MHz, GaAs do 20GHz,

ECL do 5GHz.

Częstotliwości graniczne układów cyfrowych

S

– bardzo szybka (Schottky)

LS

- małej mocy, bardzo szybka

(Low power Schottky)

F

– bardzo bardzo szybka (Fast)

AS

– ulepszona, bardzo szybka

(Advanced Schottky)

ALS

- ulepszona małej mocy,

bardzo szybka

(Advanced Low power Schottky)

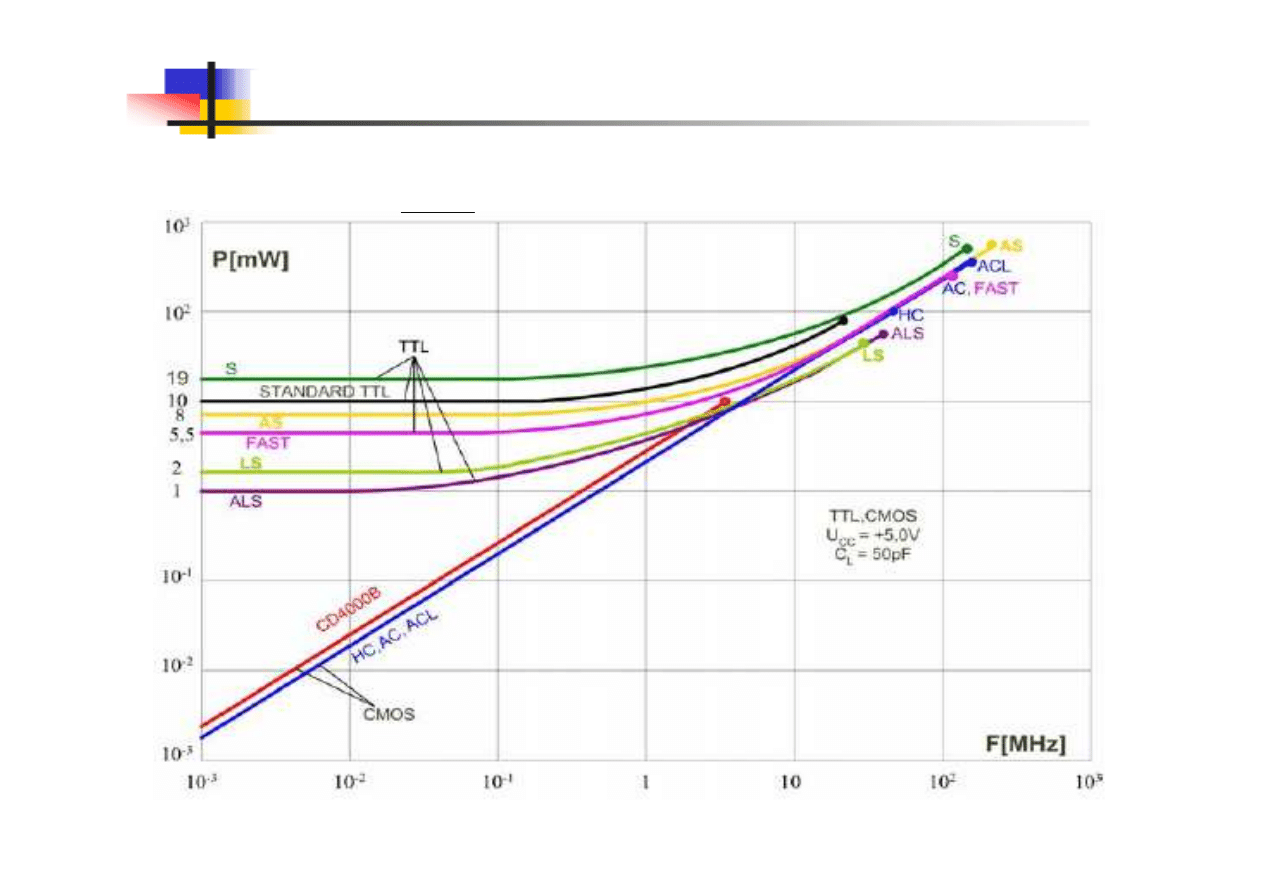

Straty mocy jako funkcja częstotliwości

( )

∫

=

=

T

CCavr

CC

CC

CC

I

U

dt

t

I

T

U

P

0

Źródła zakłóceń

• napięcia zasilającego,

• uziemieniowe,

• przesłuchowe w liniach transmisyjnych,

• odbiciowe w liniach transmisyjnych,

• zewnętrzne.

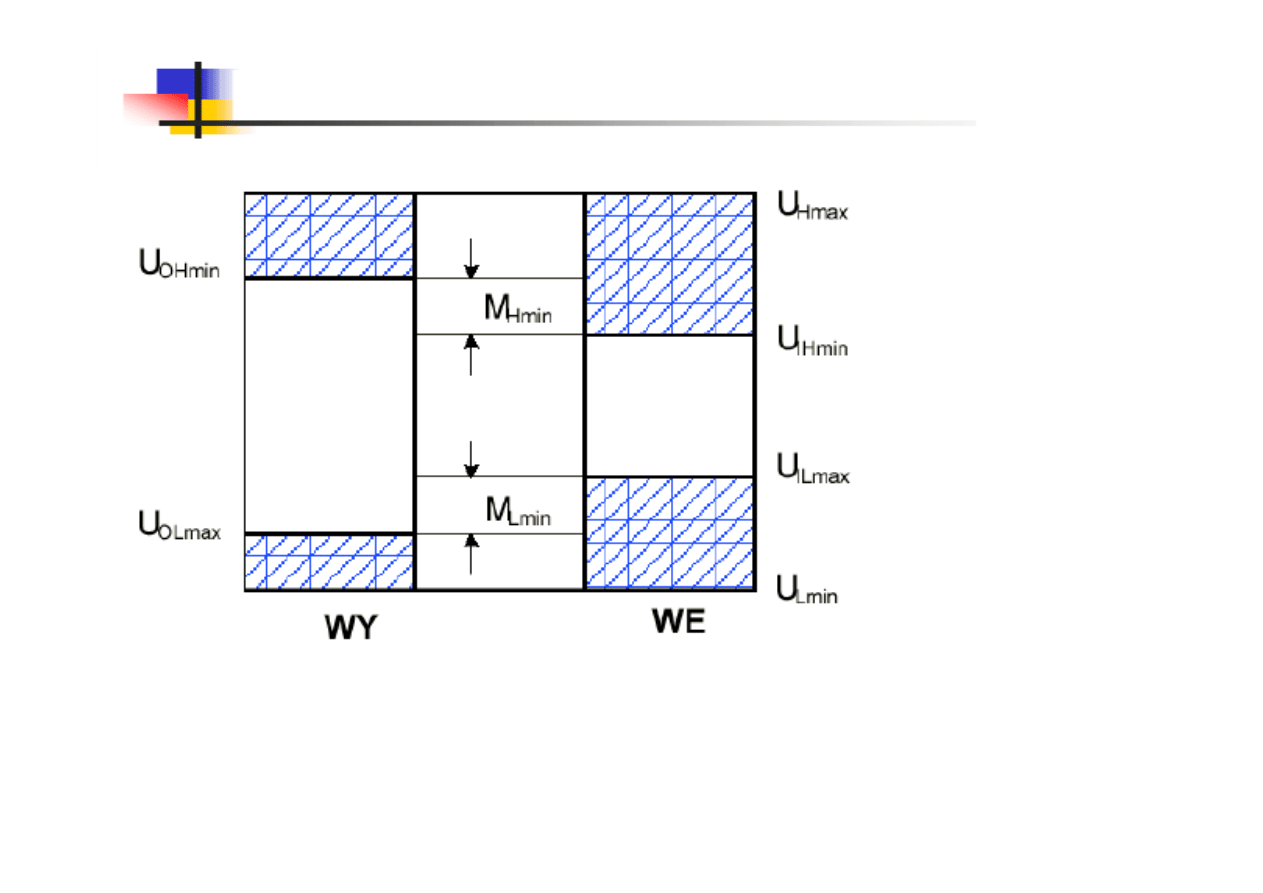

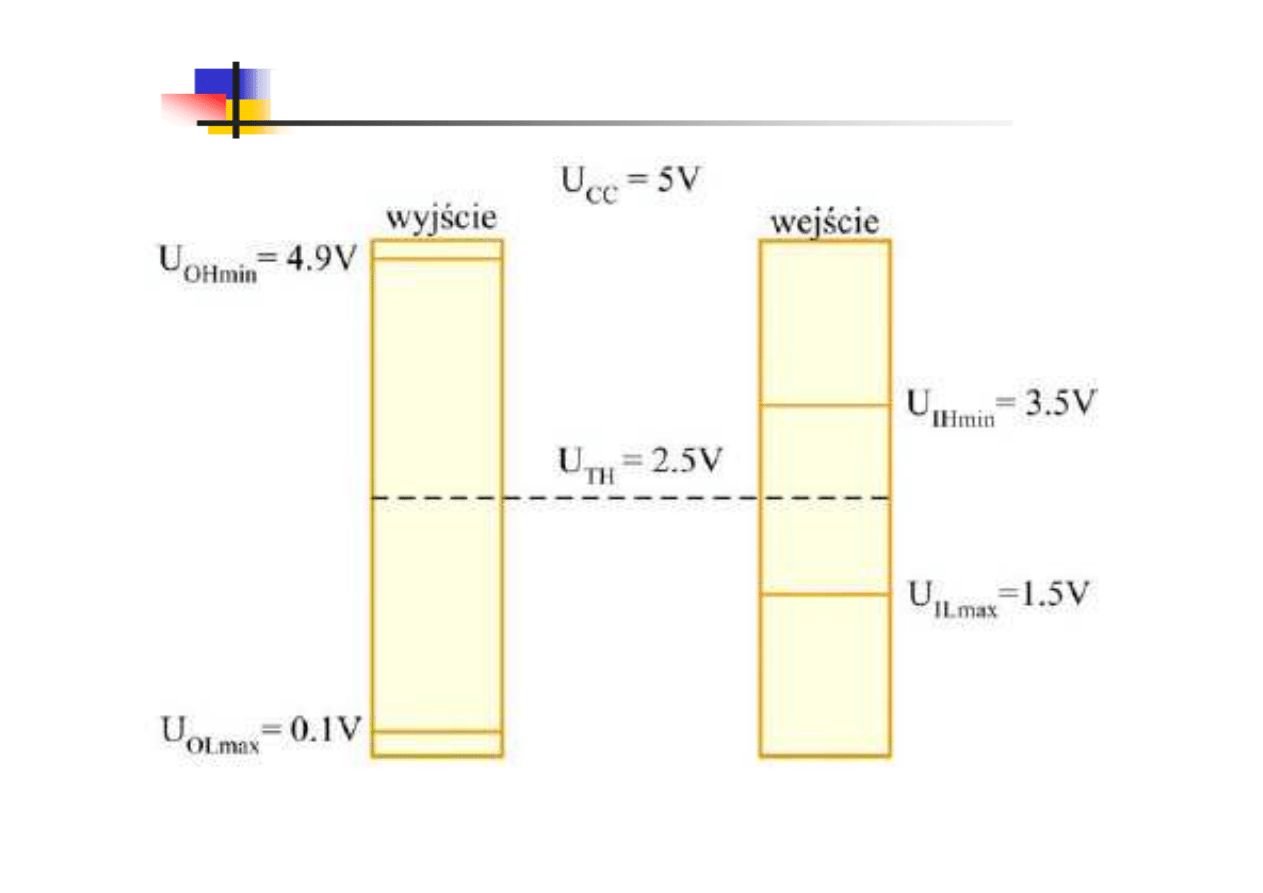

Napięcia progowe i odporność na zakłócenia

Marginesy

zakłóceń

wskazują, jaki

poziom zakłóceń

nie spowoduje

błędnego odczytu

sygnału

wejściowego w

najgorszym

przypadku.

U

LI max

-U

LO max

- margines zakłóceń stanu niskiego

U

HO min

-U

HI min

- margines zakłóceń stanu wysokiego

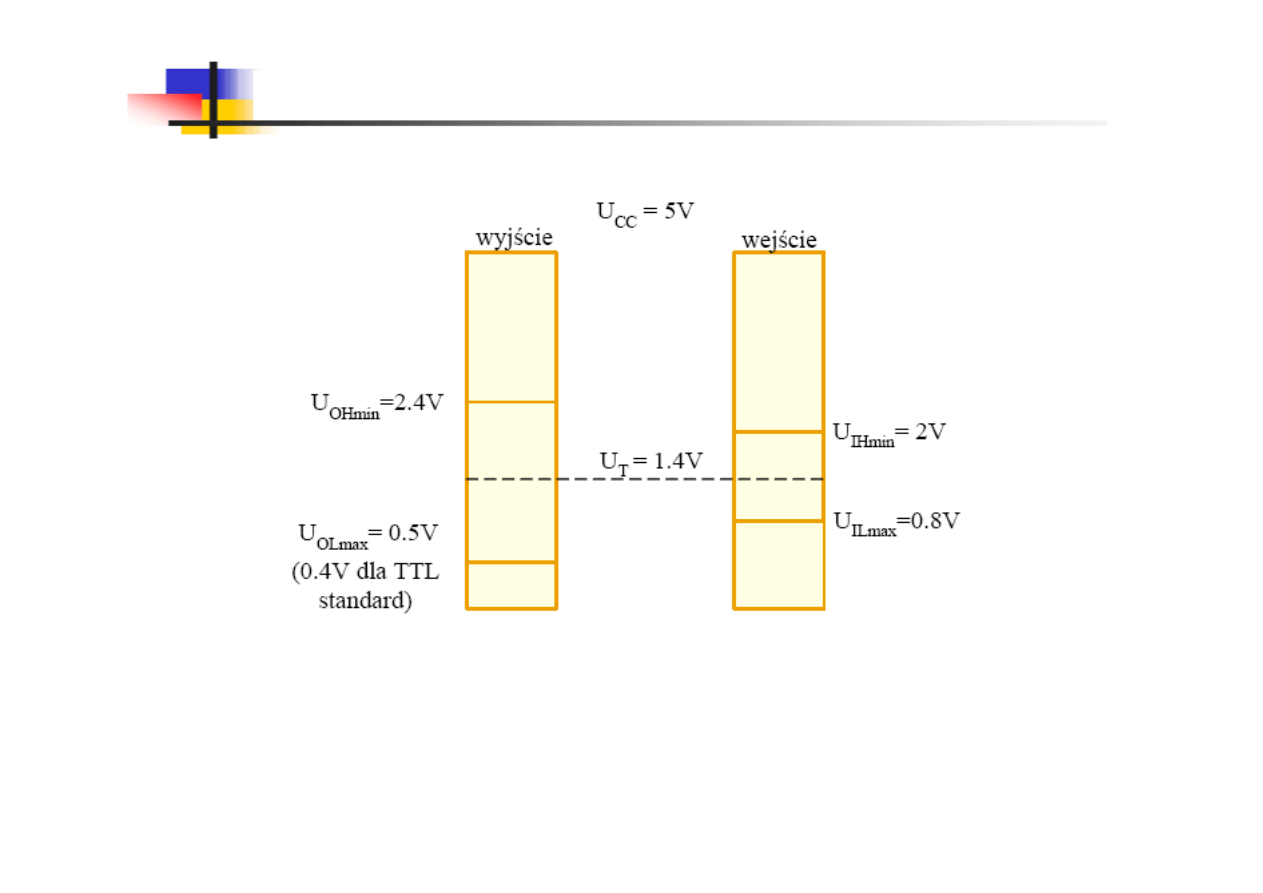

Napięcia progowe i odporność na zakłócenia

Poziomy napięć układów TTL

Wartości gwarantowane poziomów napięć logicznych na

wejściu i wyjściu układów TTL, U

T

– próg przełączania

bramki

W technice TTL są produkowane obecnie następujące serie:

TTL

– standard TTL – 74,

S

– bardzo szybka (Schottky) – 74S,

LS

- małej mocy, bardzo szybka (Low

Power Schottky) – 74LS,

F

– bardzo bardzo szybka (Fast) – 74F,

AS

– ulepszona, bardzo szybka (Advanced

Schottky) – 74AS,

ALS

- ulepszona małej mocy, bardzo szybka

(Advanced Low Power Schottky) - 74ALS.

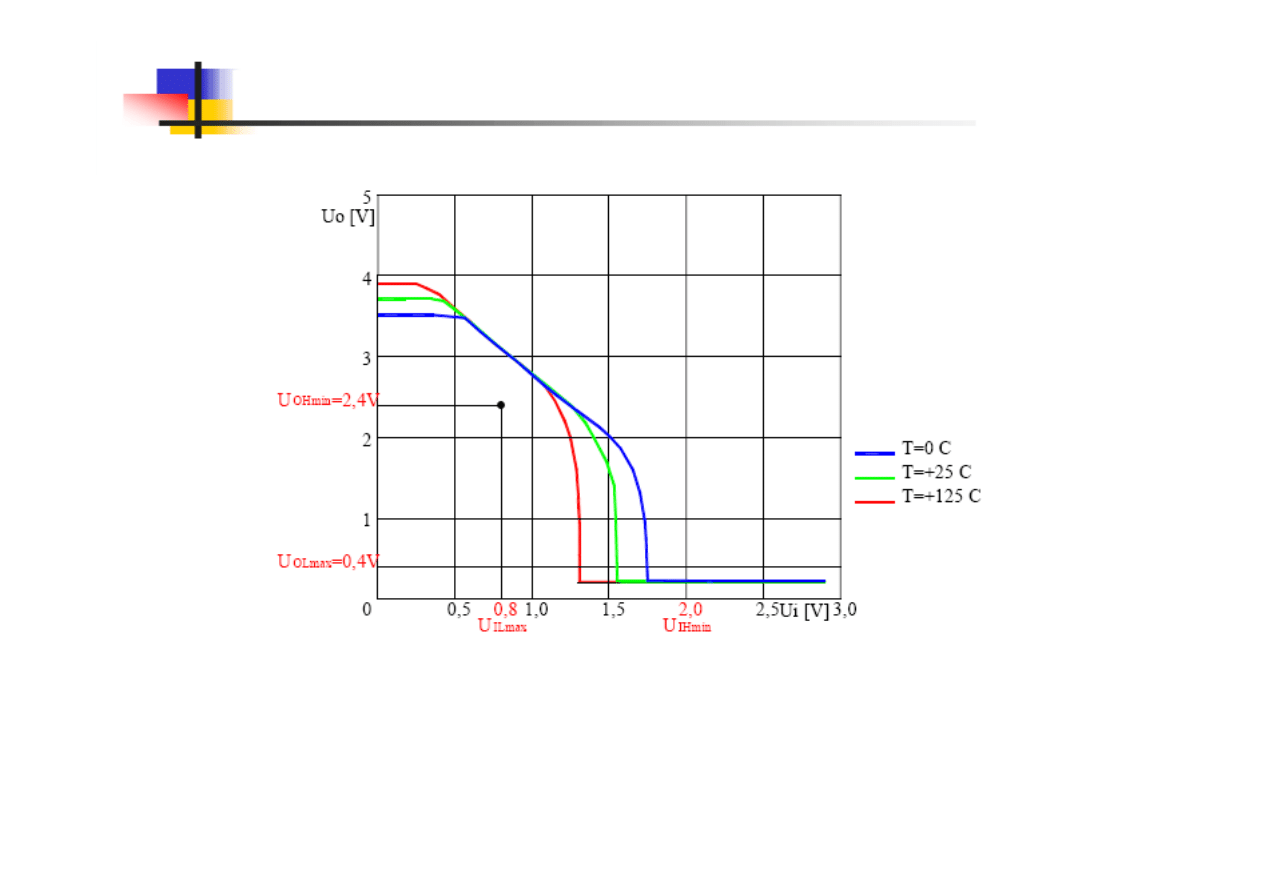

Rodziny bipolarnych układów cyfrowych TTL

• Napięcie zasilające +5V (+4,75V do +5,25V),

• sygnał wyjściowy: H > 2,4V L < 0,4V,

• sygnał wejściowy: H > 2,0V L < 0,8V,

• obciążalność 10 – 48,

• współczynnik dobroci: D=t

p

P; 5-100 [pJ],

•

maksymalna częstotliwość pracy:

• TTL (25 MHz),

• TTL-S (125 MHz) diody Schottky'ego 2x pobór mocy,

• TTL-LS (33 MHz) trochę mniejszy pobór mocy,

• TTL-F (150 MHz),

• TTL-AS (200 MHz) 10x mniejszy pobór mocy w

stosunku do TTL,

• TTL-ALS (50 MHz).

Podstawowe parametry układów TTL

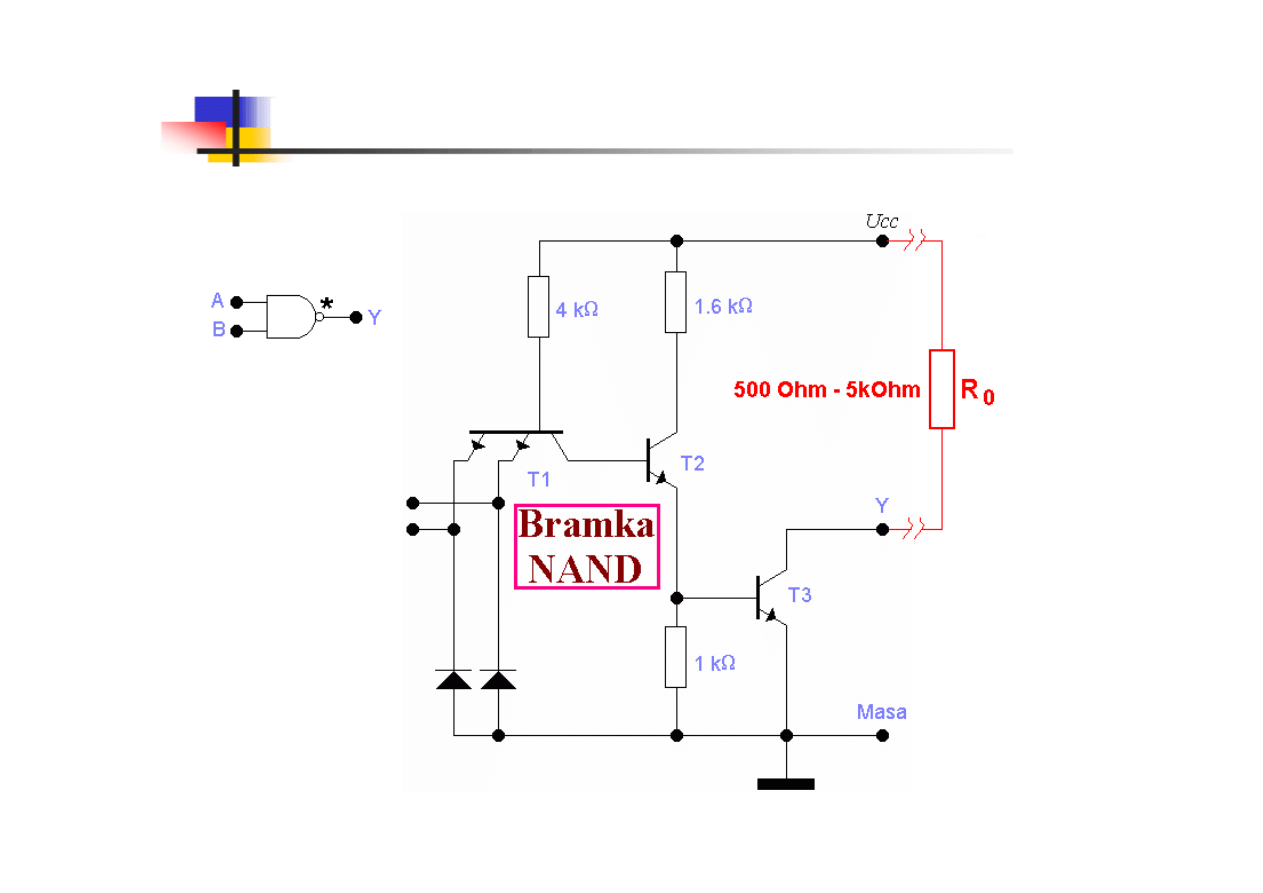

Bramka NAND z serii standardowej TTL (7400)

Y=A*B

4k

1,6k 130

1k

A

B

5V

Y=A*

B

A

B

A B Y

H H L

L H H

H L H

L L H

Charakterystyka przejściowa bramki NAND TTL

Charakterystyka przejściowa podstawowej bramki NAND

TTL serii standardowej, zależność charakterystyki

przejściowej od temperatury

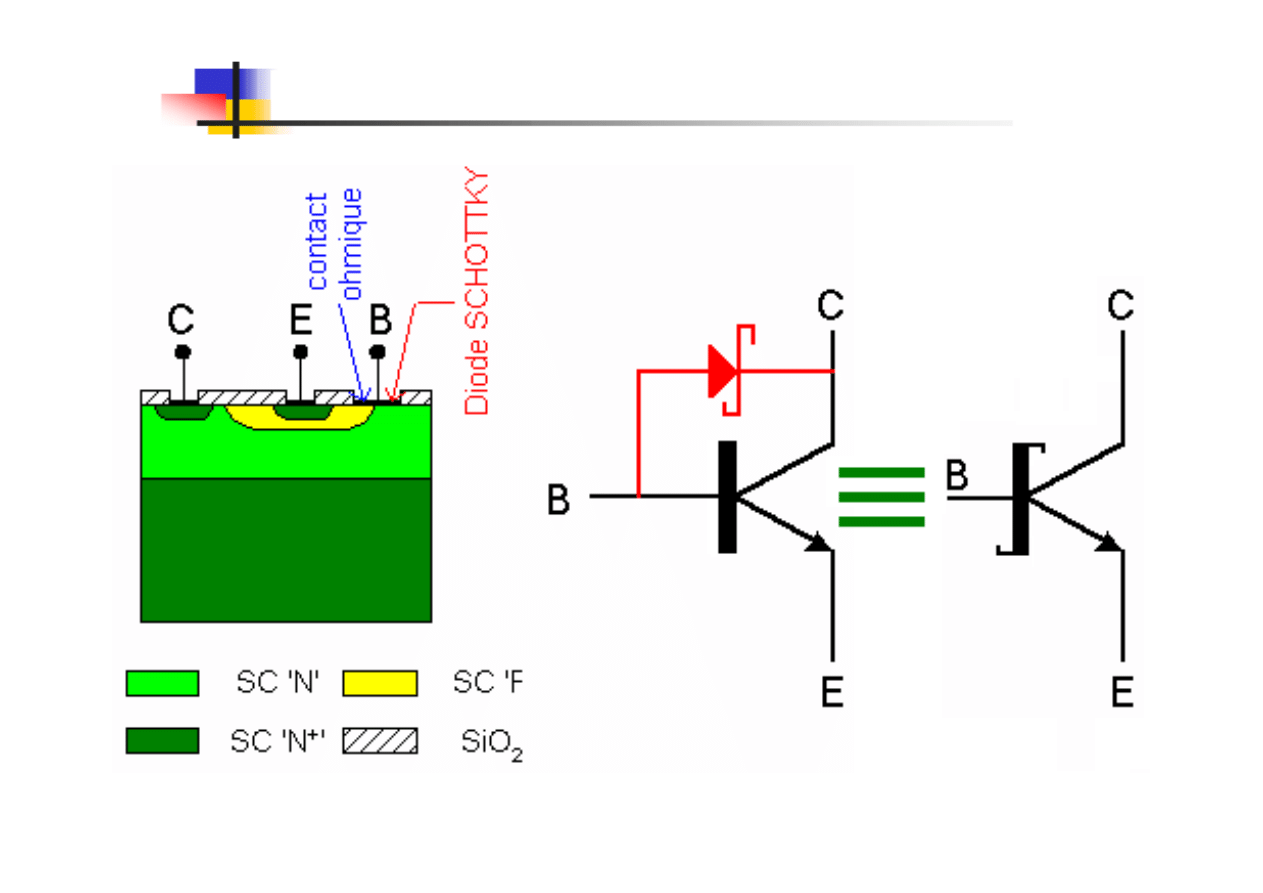

Tranzystor Schottky’ego

Własności:

•napięcia progowe oraz histereza,

• duża odporność na zakłócenia.

Zastosowania:

• przekształcanie wolnozmiennych sygnałów

na impulsy o szybkich zboczach,

• przemiana napięcia sinusoidalnego na

prostokątne,

• redukcja wpływu zakłóceń,

• proste układy multiwibratorów astabilnych.

Układy z wejściem Schmitta

Bramka z wejściem Schmitta

Bramka NAND 1/4 7401 z otwartym

kolektorem

OC

symbol

graficzny

Serie 74F38, 74ALS38B

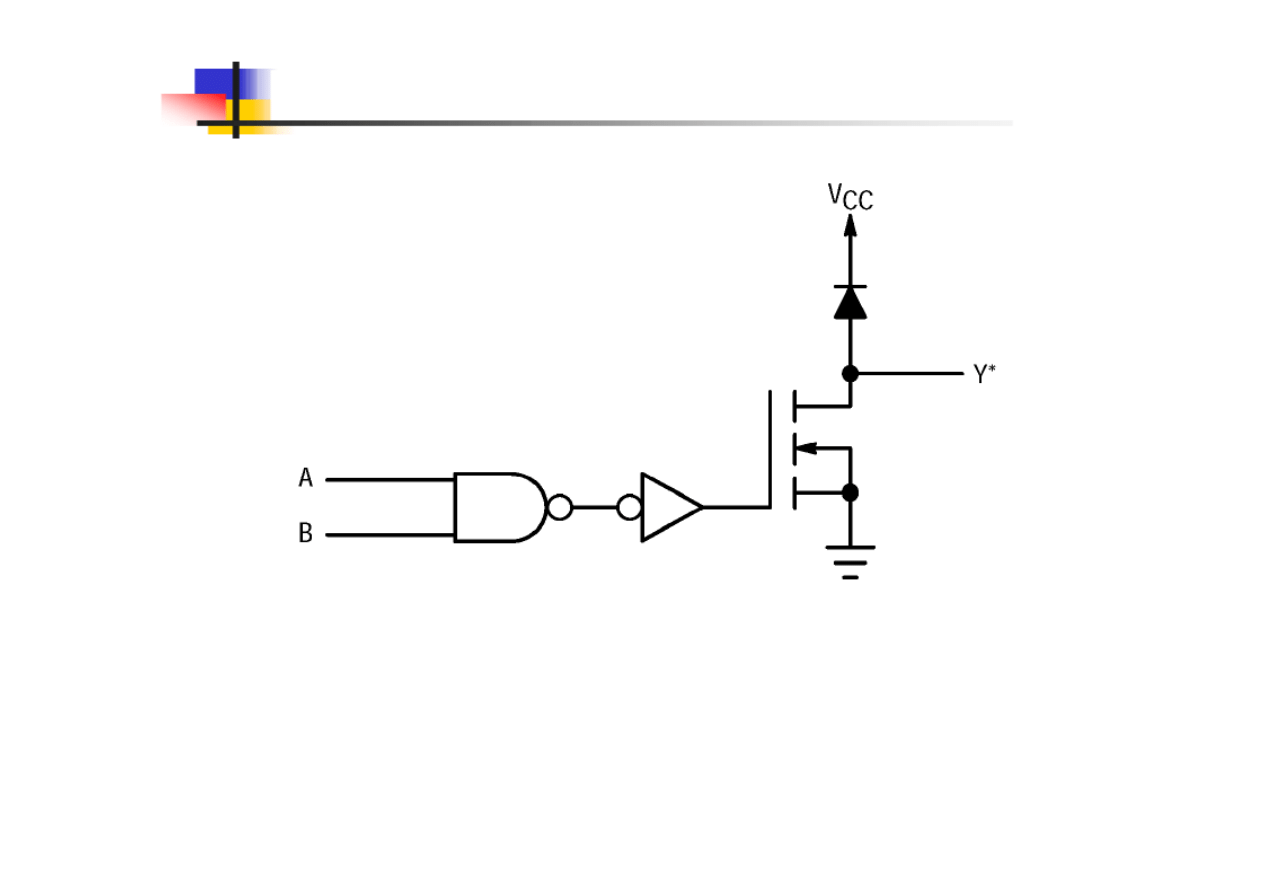

Bramka z otwartym drenem

OD

• Należy dołączyć zewnętrzny rezystor do V

CC

,

• bramka NAND (HC03).

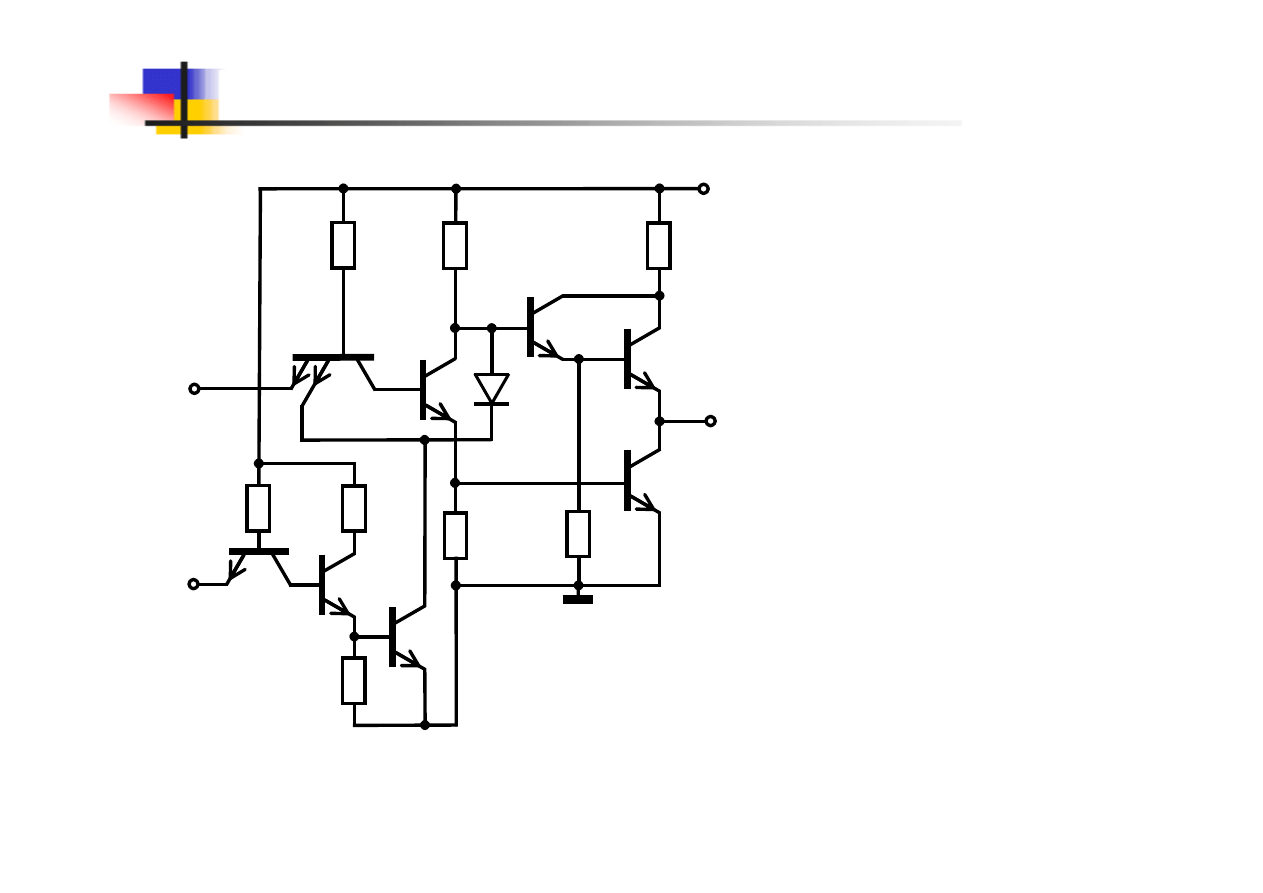

Bipolarna bramka trójstanowa (blokada wyjść)

R1

R2

R3

R4

U

CC

=5

V

T1

T2

T4

T5

A

Y

O

E

_

_

T3

R5

R6

R7

R8

T6

T7

T8

D

OE (Output Enable)

wejście zezwalające

OE=L T6=L, T7,T8=zatkane

OE=H T7,T8=L T2,T4,T5=zatkane

__

__

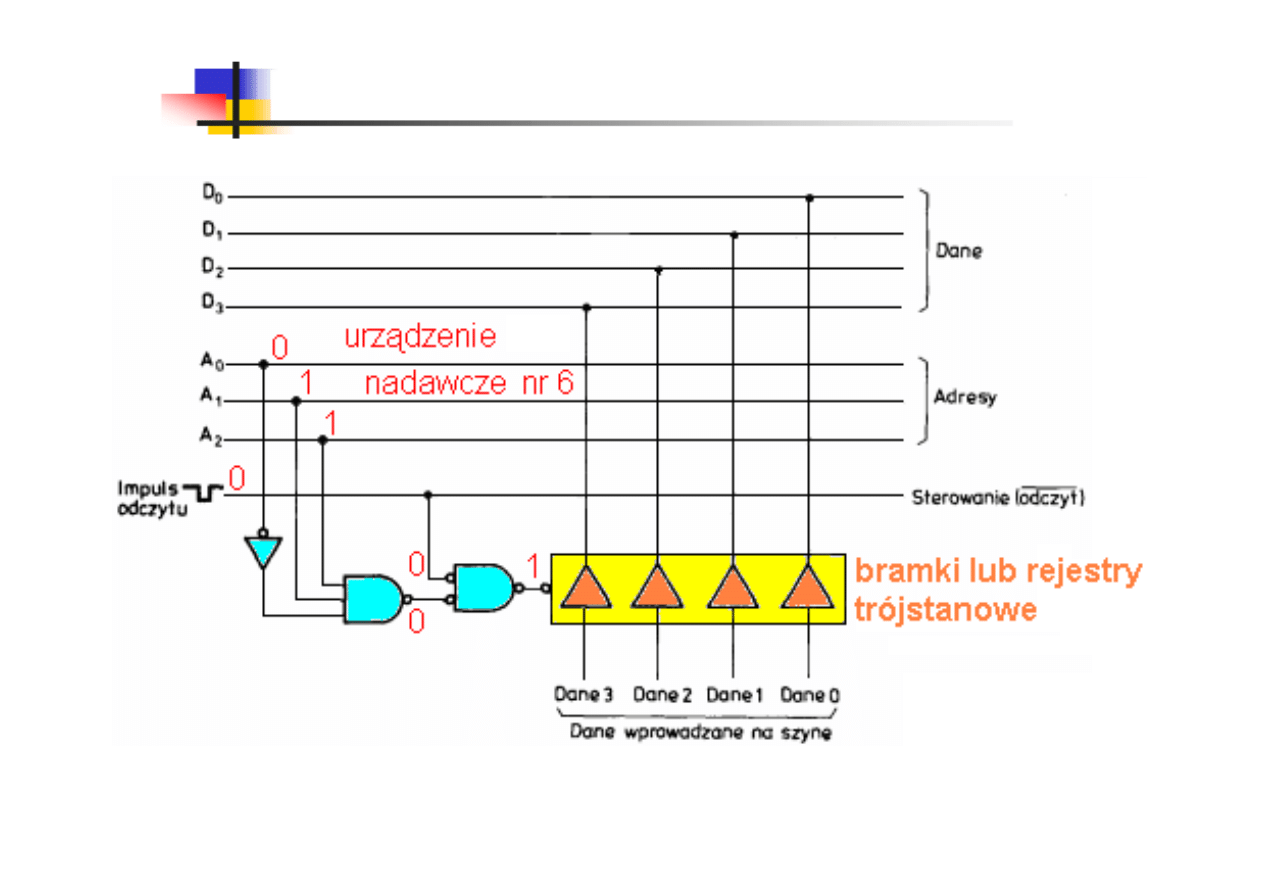

Sterowanie szyną danych

Konflikty na magistrali eliminuje specjalny układ.

Trójstanowe wzmacniacze logiczne (ang. driver) są układami szeroko

stosowanymi do sterowania komputerowymi szynami danych. Każde urządzenie

(pamięć, urządzenie zewnętrzne itp.), które chce przekazywać dane na wspólną

szynę jest dołączone do tej szyny poprzez bramki trójstanowe (lub poprzez

bardziej skomplikowane układy trójstanowe, takie jak rejestry). Obsługa

urządzeń dołączonych do wspólnej szyny jest rozwiązana tak sprytnie, że w

danej chwili wzmacniacze logiczne tylko jednego urządzenia są aktywne,

natomiast wzmacniacze pozostałych urządzeń znajdują się w trzecim stanie

(mają otwarte wyjścia). W typowej sytuacji wybrane urządzenie "dowiaduje

się", że musi dostarczyć dane na szynę, rozpoznając swój własny adres na

liniach adresowych i sterujących. W tym uproszczonym przypadku urządzeniu

nadano adres 6. Dekoduje ono adres pojawiający się na liniach A

0

-A

2

i kiedy

widzi na liniach adresowych swój adres (tzn. 6) i widzi impuls na linii żądania

odczytu (ang. read), umieszcza dane na szynie danych D

0

-D

3

. Taki protokół

szyny wystarcza w większości prostych systemów. Podobny układ jest

wykorzystywany w większości mikrokomputerów. Zwracamy uwagę, że musi

istnieć jakiś układ zewnętrzny, który zapewni takie sterowanie urządzeniami z

wyjściami trójstanowymi, dołączonymi do wspólnej szyny, aby nie zdarzyło się

równoczesne uaktywnienie kilku urządzeń (taki niepożądany przypadek nazywa

się formalnie "konfliktem na magistrali"). Wszystko jest w porządku tak długo,

jak długo każde urządzenie reaguje tylko na swój własny, różny od innych,

adres.

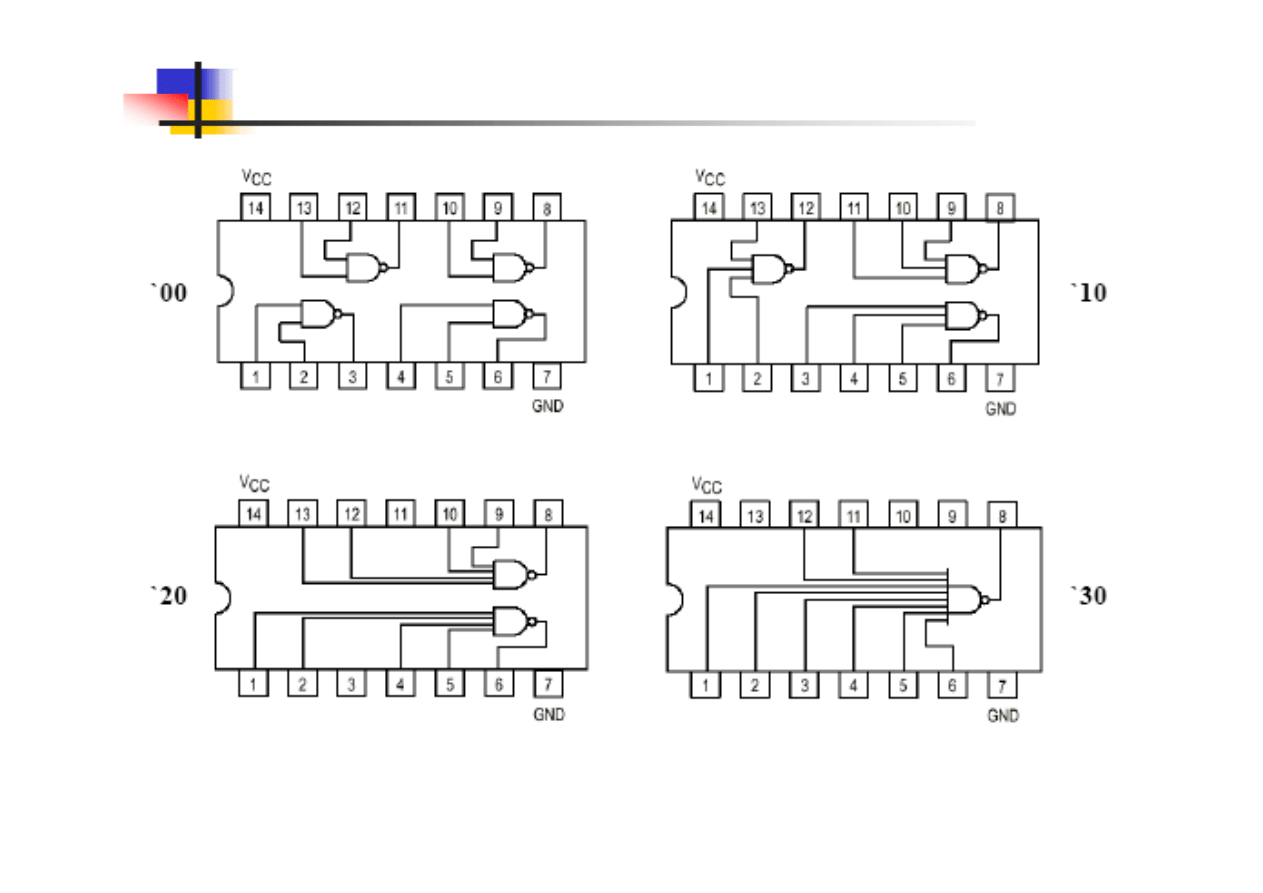

Przykłady obudów bramek TTL

Układy scalone rodziny CMOS

KRÓTKI OPIS RODZINY

• CMOS komplementarne tranzystory PMOS i NMOS bez rezystorów

• bardzo mała moc strat w stanie statycznym i przy małych

częstotliwościach

• praca przy obniżonym napięciu zasilania 3,3 V (± 0,3 V), 2,5 V (±0,2

V), 1.8V (±0.15V), a nawet 0.8V

• np. straty mocy P=U

2

/R przy 5V i 3,3 V

5

2

/ 3,3

2

≈ 2,3 raza

• większą szybkość działania niż układy pięciowoltowe

• znaczne zmniejszenie moc strat przy większych częstotliwościach

• niższy poziom generowanych zakłóceń

elektromagnetycznych i

elektrycznych

• wyższa niezawodność pracy.

Układy scalone rodziny CMOS

Układy CMOS można ogólnie podzielić na cztery

kategorie:

∗

∗

∗

∗

Układy do zastosowań masowych, o niewielkiej

szybkości

działania

(układy

zegarkowe,

nie

programowalne układy kalkulatorowe z napięciem

zasilania 0.8 V ÷ 1,5 V).

∗

∗

∗

∗ Układy programowalne (takie jak układy PLD i FPGA)

i specjalizowane (ASIC).

∗

∗

∗

∗ Uniwersalne układy cyfrowe LSI i VLSI, głównie

układy mikroprocesorowe i pamięciowe.

∗

∗

∗

∗ Uniwersalne układy cyfrowe SSI i MSI, stanowiące

funkcjonalne odpowiedniki układów TTL.

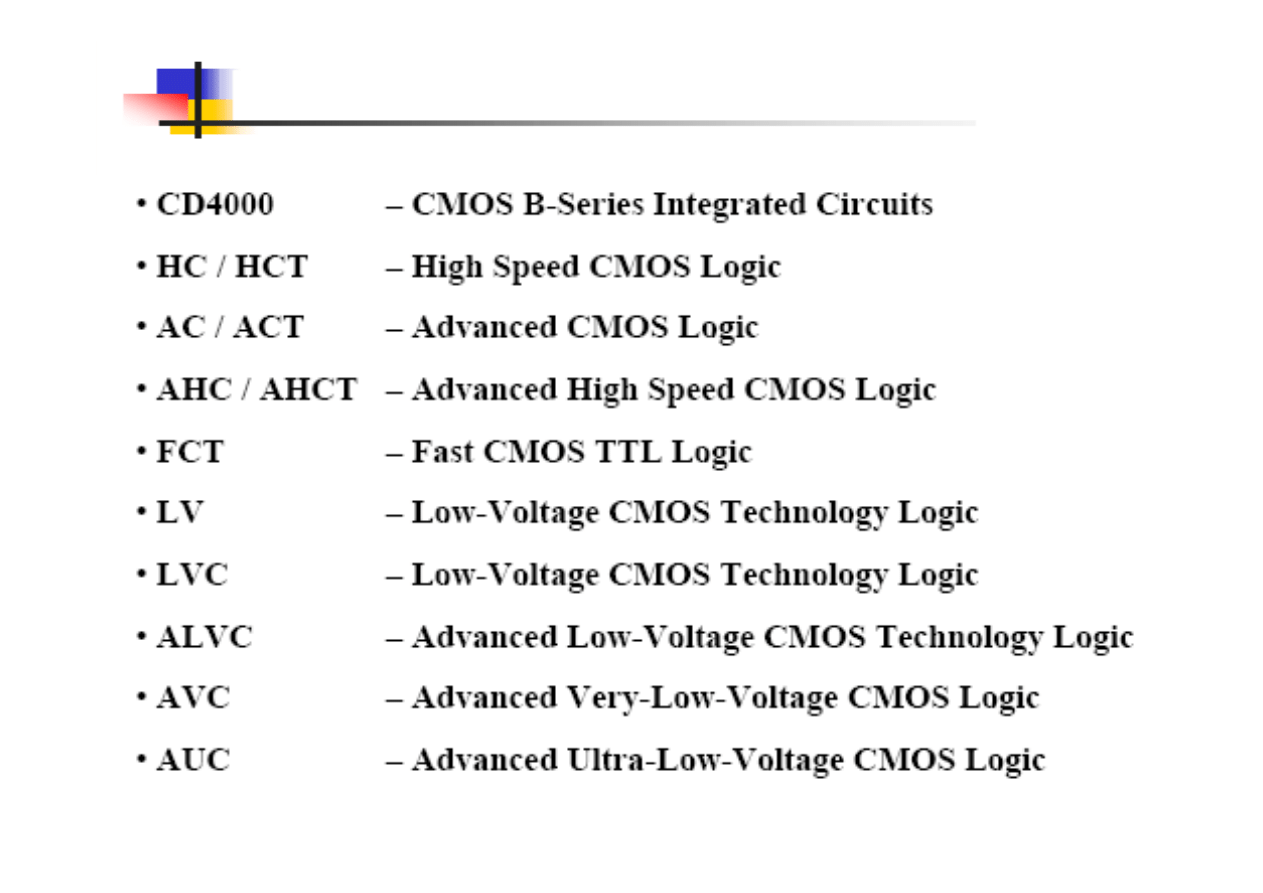

Rodziny układów cyfrowych CMOS

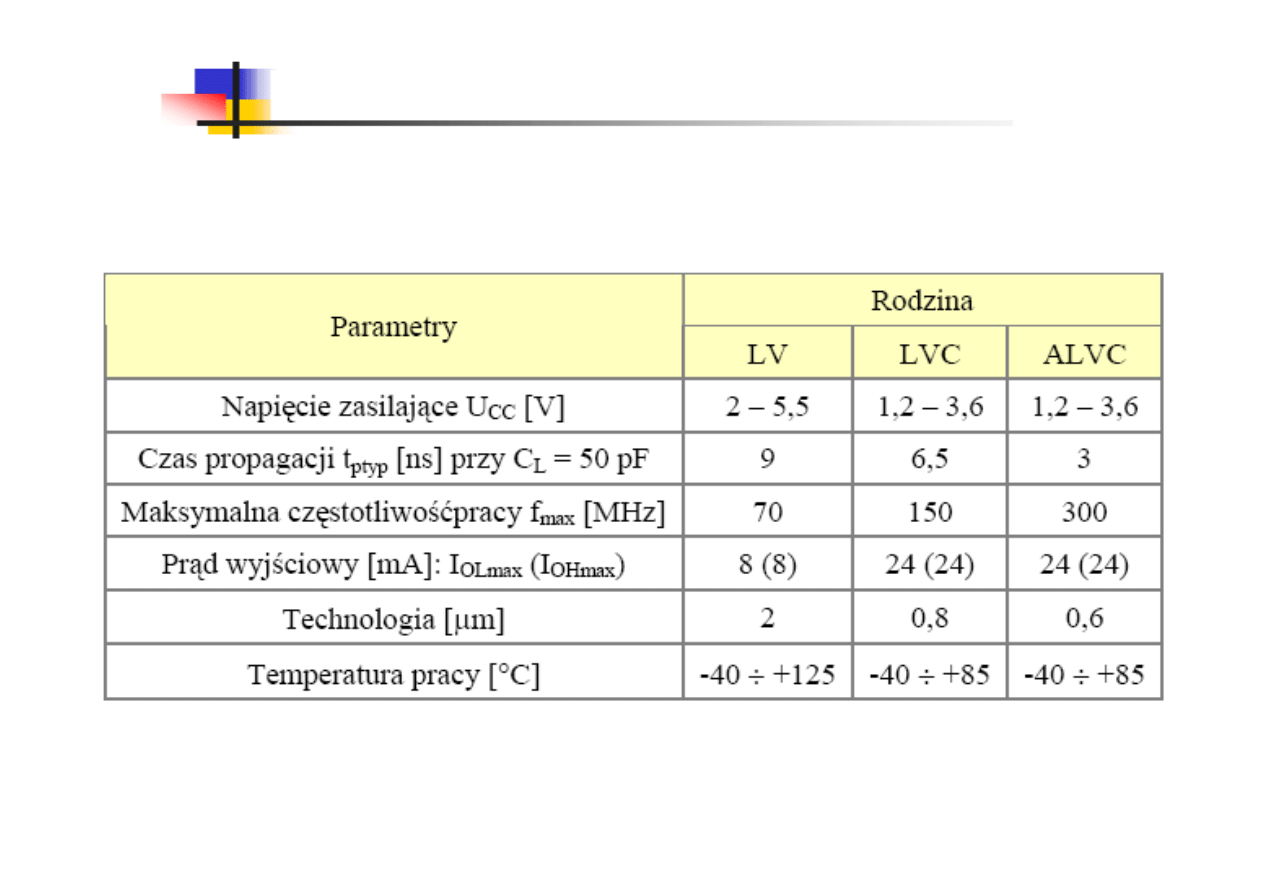

Zakresy typowych napięć rodziny CMOS

Parametry układów CMOS rodzin trzywoltowych

Budowa bramek scalonych

Chociaż bramki w wersjach TTL i CMOS

spełniają tę samą funkcję logiczną to wartości

poziomów logicznych, szybkość, moc zasilania,

prądy wejściowe itp. różnią się znacznie w obu

przypadkach. Należy być ostrożnym, gdy

zamierza się używać równocześnie obu rodzajów

bramek. Aby zrozumieć różnice, popatrzmy na

schematy bramek NAND. Stopnie wyjściowe

bramek TTL i CMOS zawierają obciążenie

aktywne dołączone do szyny dodatniego napięcia

zasilania.

+

U

DD

i

Dp

i

Dn

u

O

u

I

M

n

M

p

−

=

−

=

=

=

=

Dp

Dn

DD

I

GSp

I

GSn

I

Ip

In

i

i

U

u

u

u

u

u

u

u

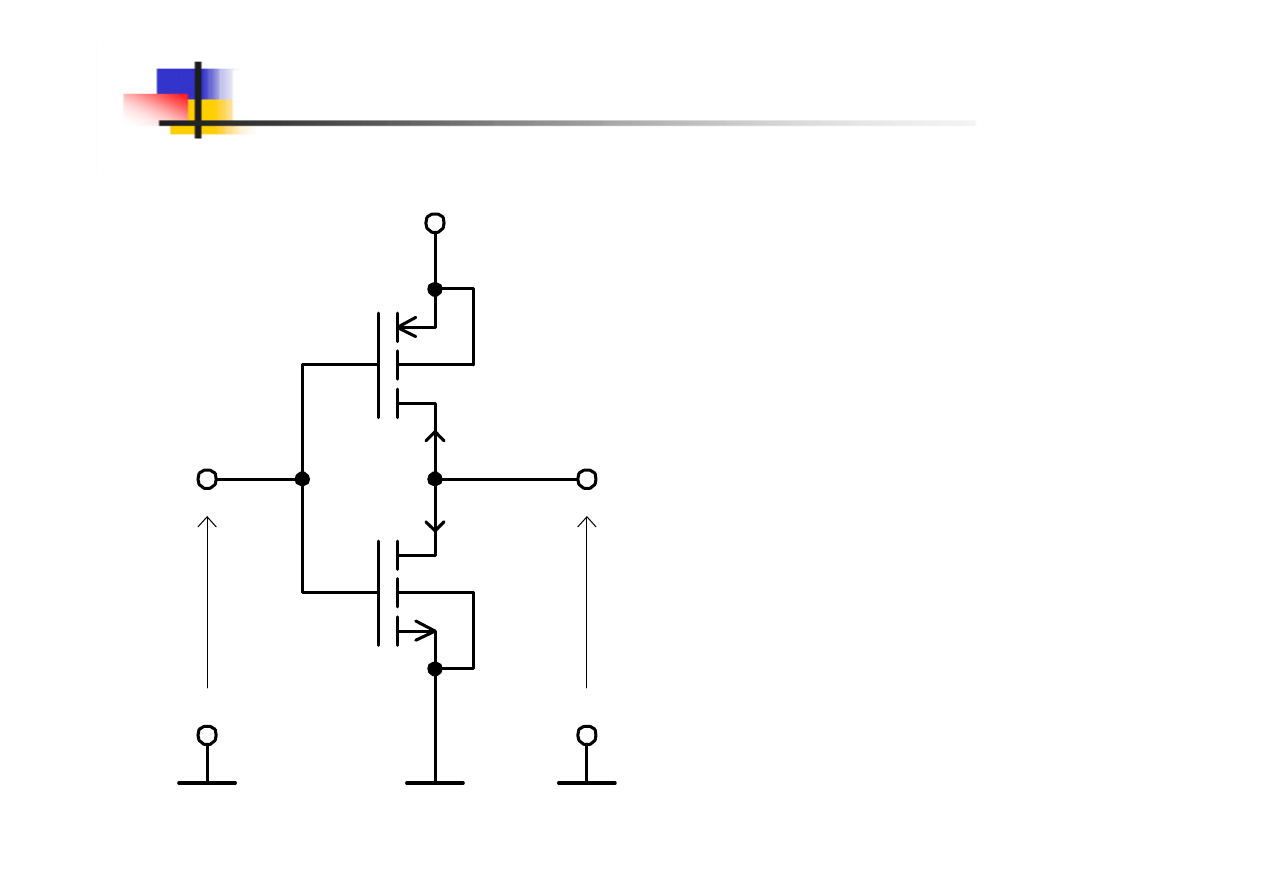

Inwerter CMOS

Charakterystyki inwertera CMOS

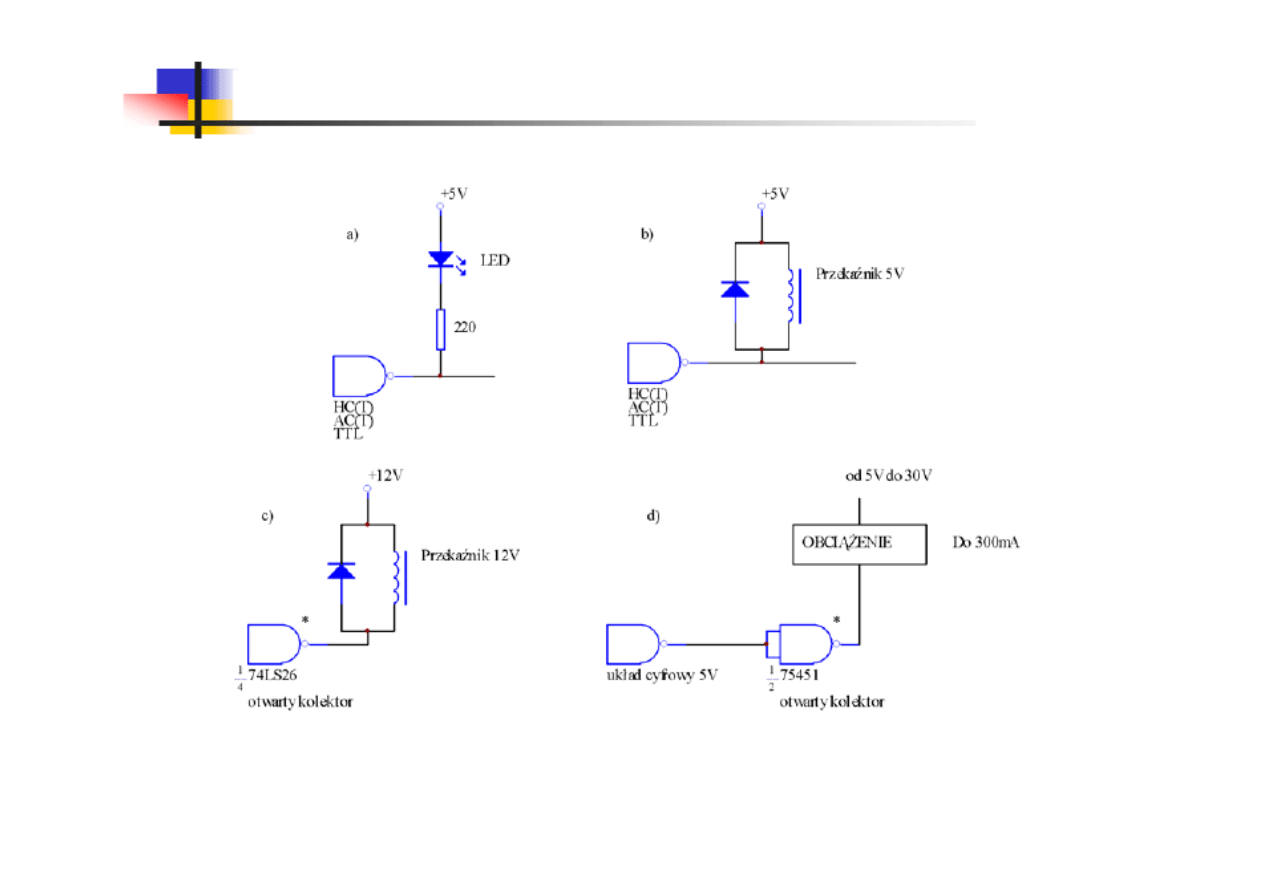

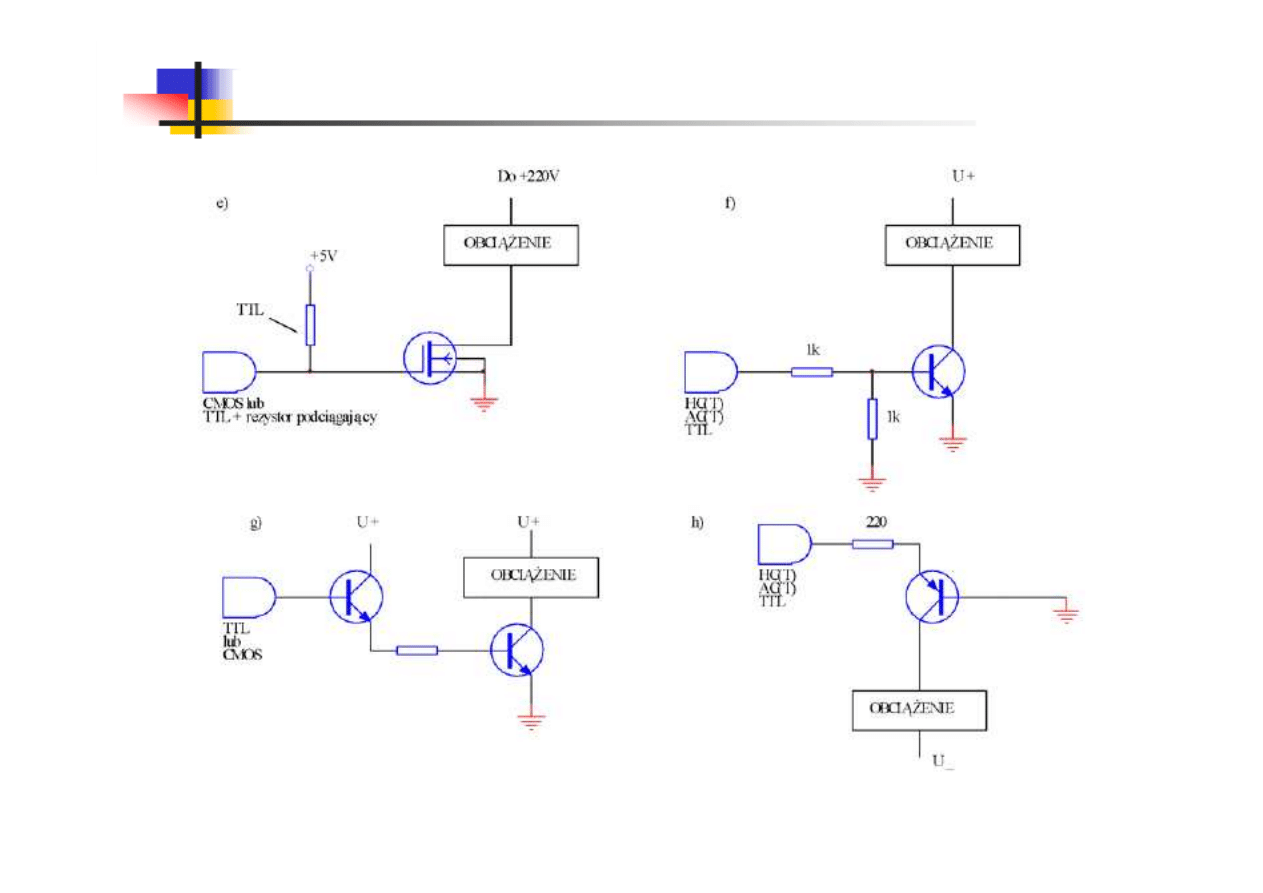

Łączenie obciążeń do wyjść bramek

Łączenie obciążeń do wyjść bramek

Wyszukiwarka

Podobne podstrony:

Bramki Logiczne

bramki logiczne, Szkoła, Systemy Operacyjnie i sieci komputerowe, utk, semestr I

Bramki logiczne

10 bramki logiczne, ZSS

Bramki logiczne, Księgozbiór, Studia, Elektronika i Elektrotechnika

BRAMKI LOGICZNE (1) id 92815 Nieznany

Bramki logiczne

Bramki logiczne 3 id 92812 Nieznany (2)

EEPodstawowe bramki logiczne

09 Bramki logiczne

instrukcje do sprawozdań, cw5 bramki logiczne, Laboratorium

cw5 bramki logiczne id 123545 Nieznany

01 Podstawowe bramki logiczne instrukcja poprawiona

Bramki logiczne

Bramki Logiczne

więcej podobnych podstron