Bramki logiczne - wst

ę

p

W technologii cyfrowej układy komunikuj

ą

si

ę

dwoma stanami logicznymi, tzn. "1" lub "0". Do

"1" i "0" s

ą

przyporz

ą

dkowane okre

ś

lone poziomy napi

ęć

. Działanie układów jest oparte na

systemie dwójkowym, czyli takim, w którym liczenie opiera si

ę

na 2. W systemie dziesi

ę

tnym

liczenie opiera si

ę

na 10.

L - stan niski - 0 odpowiada napi

ę

ciu 0-0,4V

H - stan wysoki - 1 odpowiada napi

ę

ciu 5V

Sygnał cyfrowy charakteryzuj

ą

dwa stany napi

ę

cia:

- wysoki poziom V

H

- niski poziom V

L

wysoki oznaczona si

ę

jako "1", a poziom niski jako "0". St

ą

d pochodzi nazwa sygnał cyfrowy.

V

H

= 1

V

L

= 0

Tablica prawdy - jest to (najcz

ęś

ciej) tabela, która ukazuje jak przy danych stanach logicznych

ustawionych na wej

ś

ciach bramki b

ę

dzie ustawione wyj

ś

cie bramki.

Stan logiczny - w bramkach logicznych mo

ż

na spotka

ć

si

ę

z dwoma mo

ż

liwymi stanami:

jedynk

ą

logiczn

ą

"1" lub zerem logicznym "0". W najpopularniejszej technologii TTL sygnałowi

"1" odpowiada napi

ę

cie ok. +5V, a sygnałowi "0" napi

ę

cie bliskie 0V

Układy s

ą

wykonywane w nast

ę

puj

ą

cych technologiach:

•

TTL - oparte na tranzystorach bipolarnych,

•

CMOS - oparte na tranzystorach CMOS ( NMOS, PMOS ),

•

ECL - oparte na wzmacniaczach ró

ż

nicowych zbudowanych na tranzystorach

bipolarnych, bardzo szybka technologia (cz

ę

stotliwo

ść

taktowania: 150-500 MHz),

wykorzystywane m.in. w wojskowym sprz

ę

cie.

Układy cyfrowe:

kombinacyjne - stan na wyj

ś

ciu w danej chwili jest funkcj

ą

stanu wej

ś

ciowego w tej samej

chwili,

sekwencyjne - stan na wyj

ś

ciu zale

ż

y od stanu na wej

ś

ciu i od historii stanów wej

ś

ciowych,

układy te posiadaj

ą

pami

ęć

.

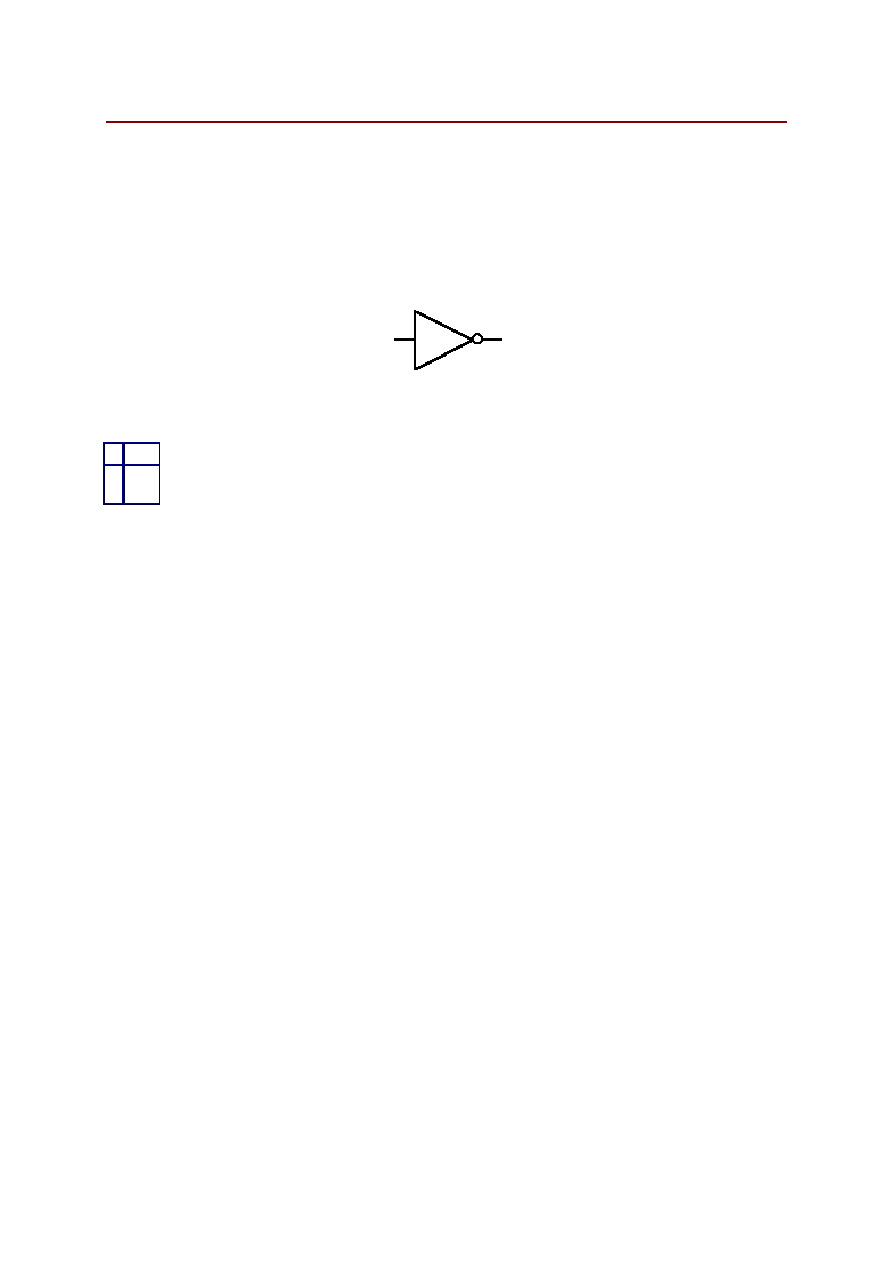

Bramki logiczne - inwerter NOT

Bramka realizuje funkcje logiczn

ą

: NOT, NIE - negacja

.

Bramka ma tylko jedno wej

ś

cie. Neguje, czyli zmienia sygnał wej

ś

ciowy na przeciwny.

Jest to najprostsza bramka. Gdy na wej

ś

ciu ustawimy sygnał "1" to na wyj

ś

ciu otrzymamy "0",

a gdy na wej

ś

ciu ustawimy "0" to na wyj

ś

ciu pojawi si

ę

"1". Bramka ta zawsze ma tylko jedno

wej

ś

cie i wyj

ś

cie.

Tablica prawdy:

IN

OUT

0

1

1

0

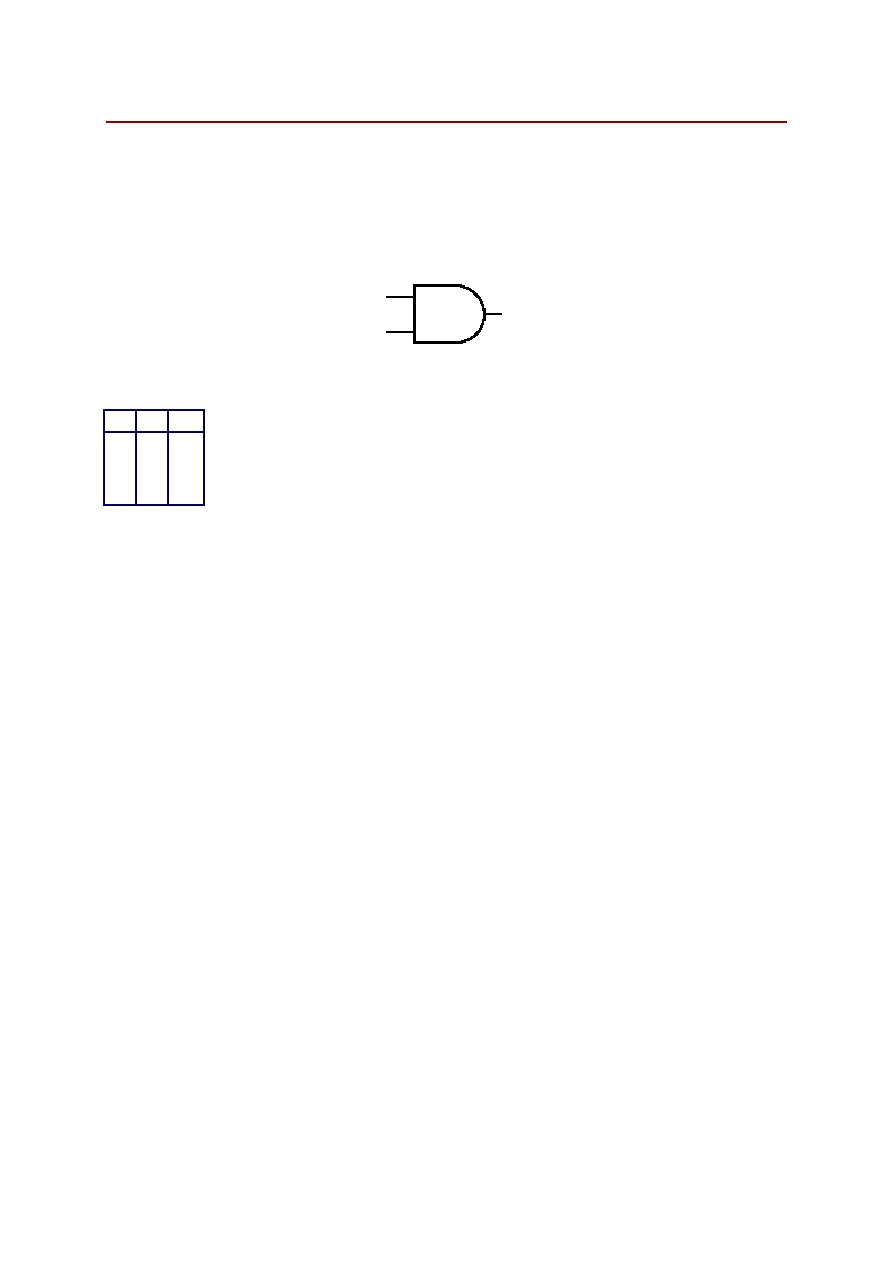

Bramki logiczne - suma AND

Bramka realizuje funkcje logiczn

ą

: AND, I - iloczyn

Je

ś

li na wszystkich wej

ś

ciach bramki s

ą

podane "1" to na wyj

ś

ciu jest "1". W spoczynku na

wyj

ś

ciu jest "0".

Bramka ta posiada conajmniej dwa do o

ś

miu wej

ś

cia i tylko jedno wyj

ś

cie.

Tablica prawdy:

IN 1

IN 2

OUT

0

0

1

1

0

1

0

1

0

0

0

1

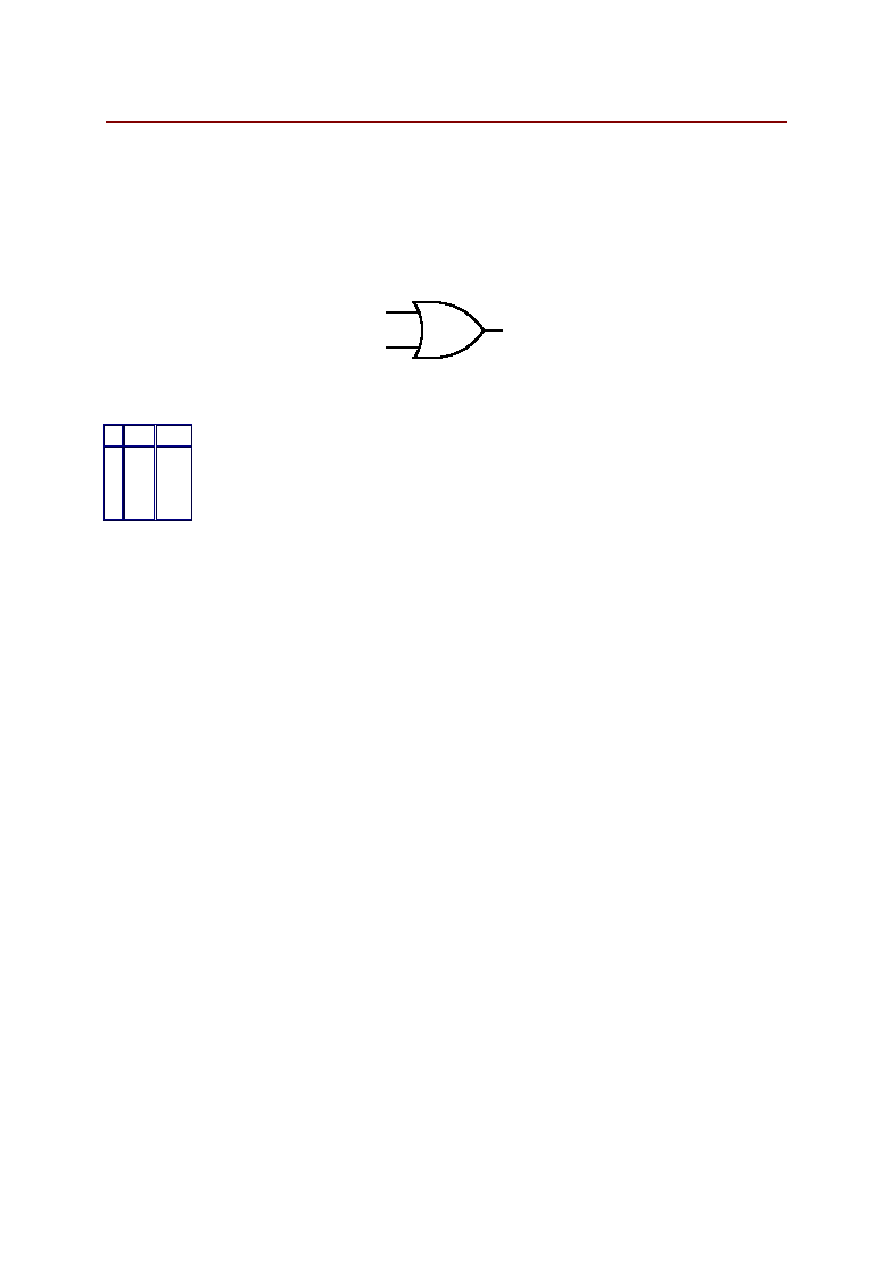

Bramki logiczne - suma OR

Bramka realizuje funkcje logiczn

ą

: OR, LUB - suma

Je

ś

li na przynajmniej jednym wej

ś

ciu bramki jest podana "1" to na wyj

ś

ciu jest "1". W

spoczynku na wyj

ś

ciu jest "0".

W przypadku tej bramki wystarczy aby cho

ć

na jednym z jej wej

ść

pojawił si

ę

stan "1" i wtedy

na wyj

ś

ciu równie

ż

pojawi si

ę

"1".

Tablica prawdy:

IN

IN 2

OUT

0

0

1

1

0

1

0

1

0

1

1

1

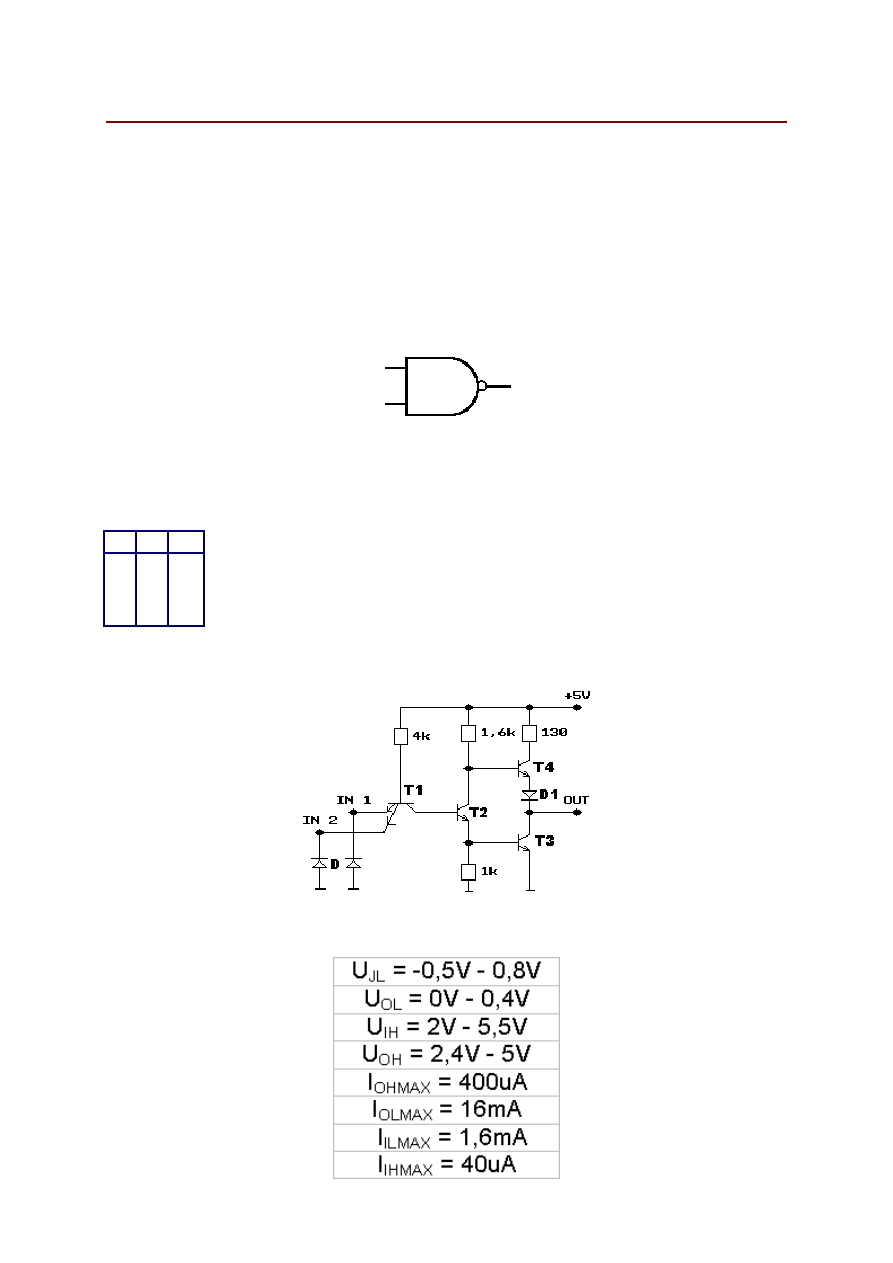

Bramki logiczne - negacja iloczynu NAND

Bramka realizuje funkcje logiczn

ą

: NAND, NIE I - negacja iloczynu

Bramka jest zło

ż

ona z bramki NOT i AND. Zasada działania jest taka sama jak bramki AND z t

ą

ró

ż

nic

ą

,

ż

e sygnał wyj

ś

ciowy jest jeszcze negowany. Bramka ta stanowi SYSTEM

FUNKCJONALNIE PEŁNY, czyli za jej pomoc

ą

mo

ż

na przedstawi

ć

ka

ż

d

ą

zło

ż

on

ą

funkcj

ę

logiczn

ą

.

Jest to poł

ą

czenie bramki AND z inwerterem. Zero logiczne "0" na wyj

ś

ciu jest ustawiane tylko

wtedy gdy na obu wej

ś

ciach jest jedynka logiczna "1". W pozostałych przypadkach na wyj

ś

ciu

zawsze jest stan "1".

Tablica prawdy:

IN 1

IN 2

OUT

0

0

1

1

0

1

0

1

1

1

1

0

Schemat wewn

ę

trzny bramki NAND wykonanej w technologii TTL:

Parametry bramki NAND wykonanej w technologii TTL:

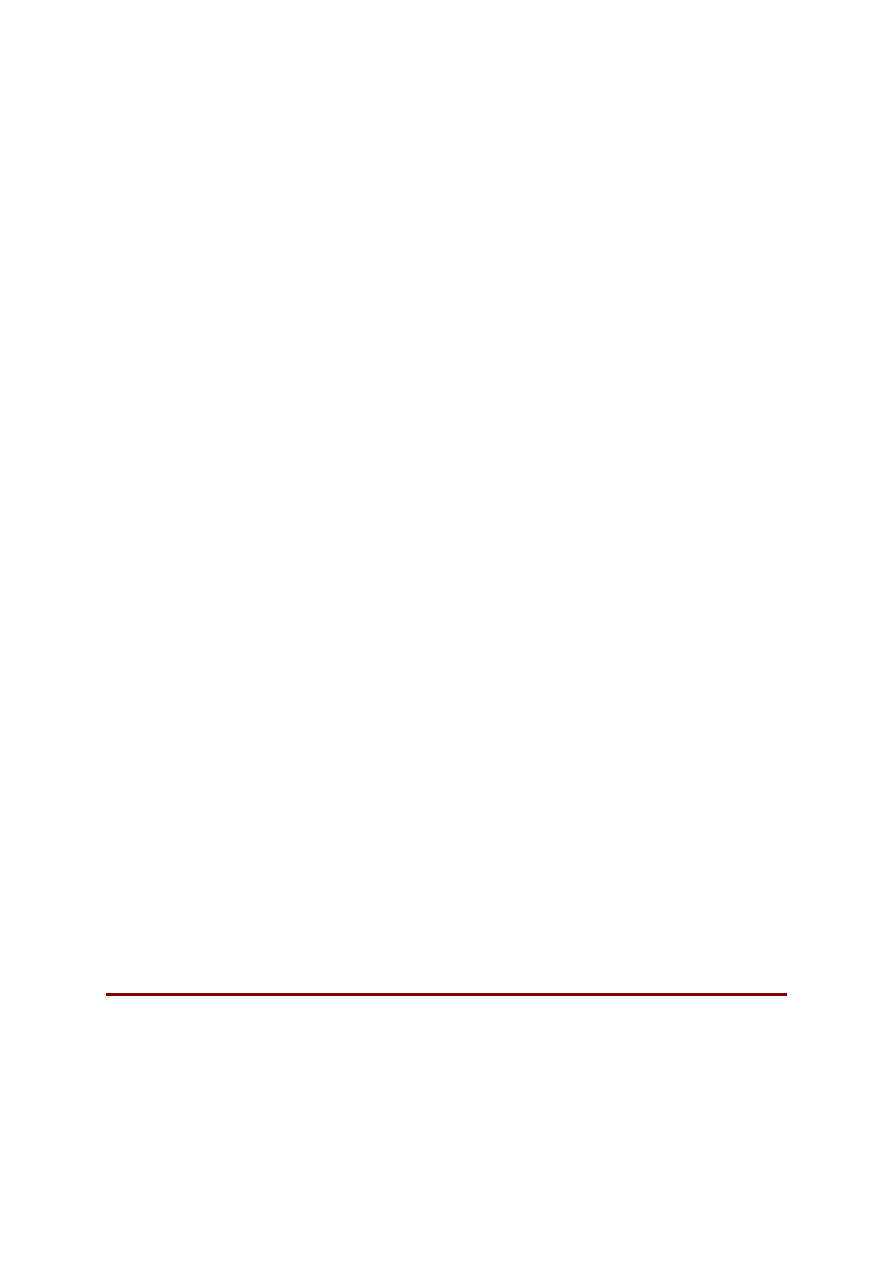

Bramki logiczne - negacja sumy NOR

Bramka realizuje funkcje logiczn

ą

:

NOR, NIE SUMA - negacja sumy

Bramka jest zło

ż

ona z bramki NOT i OR. Zasada działania jest taka sama jak bramki OR z t

ą

ró

ż

nic

ą

,

ż

e sygnał wyj

ś

ciowy jest jeszcze negowany. Bramka ta stanowi SYSTEM

FUNKCJONALNIE PEŁNY, czyli za jej pomoc

ą

mo

ż

na przedstawi

ć

ka

ż

d

ą

zło

ż

on

ą

funkcj

ę

logiczn

ą

.

Tablica prawdy:

IN 1

IN 2

OUT

0

0

1

1

0

1

0

1

1

0

0

0

Bramki logiczne - nieu

ż

ywane wej

ś

cia

Nie wykorzystane wej

ś

cia podł

ą

czamy w nast

ę

puj

ą

cy sposób:

Nieu

ż

ywane wej

ś

cia bramek

AND, NAND

i przerzutników nale

ż

y doł

ą

czy

ć

do szyny

napi

ę

cia zasilania Ucc przez rezystancj

ę

15k. Przez jedn

ą

rezystancj

ę

1k mo

ż

na doł

ą

czy

ć

1- 25

wolnych wej

ść

. Je

ż

eli mo

ż

na zagwarantowa

ć

,

ż

e napi

ę

cie zasilania Ucc nie przekracza warto

ś

ci

5,5 V, to nieu

ż

ywane wej

ś

cia mo

ż

na doł

ą

czy

ć

wprost do napi

ę

cia zasilania Ucc.

Nieu

ż

ywane wej

ś

cia bramek

AND, NAND, OR oraz NOR

mo

ż

na doł

ą

czy

ć

do wej

ść

u

ż

ywanych tych samych bramek, je

ż

eli dopuszczalna obci

ąż

alno

ść

układu steruj

ą

cego w

stanie wysokim (1) nie zostanie w ten sposób przekroczona.

Wolne wej

ś

cia bramek

AND, NAND

oraz przerzutników mo

ż

na doł

ą

czy

ć

do wyj

ś

cia

nieu

ż

ywanej bramki, na wej

ś

cie której nale

ż

y przyło

ż

y

ć

napi

ę

cie ustawiaj

ą

ce wyj

ś

cie w stanie

wysokim (1).

Wolne wej

ś

cia bramek

AND, NAND

oraz przerzutników mo

ż

na doł

ą

czy

ć

do niezale

ż

nego

ź

ródła napi

ę

cia zasilania o napi

ę

ciu wynosz

ą

cym 2,4-3,5 V.

Wolne wej

ś

cia bramek

OR

oraz

NOR

nale

ż

y doł

ą

czy

ć

do masy

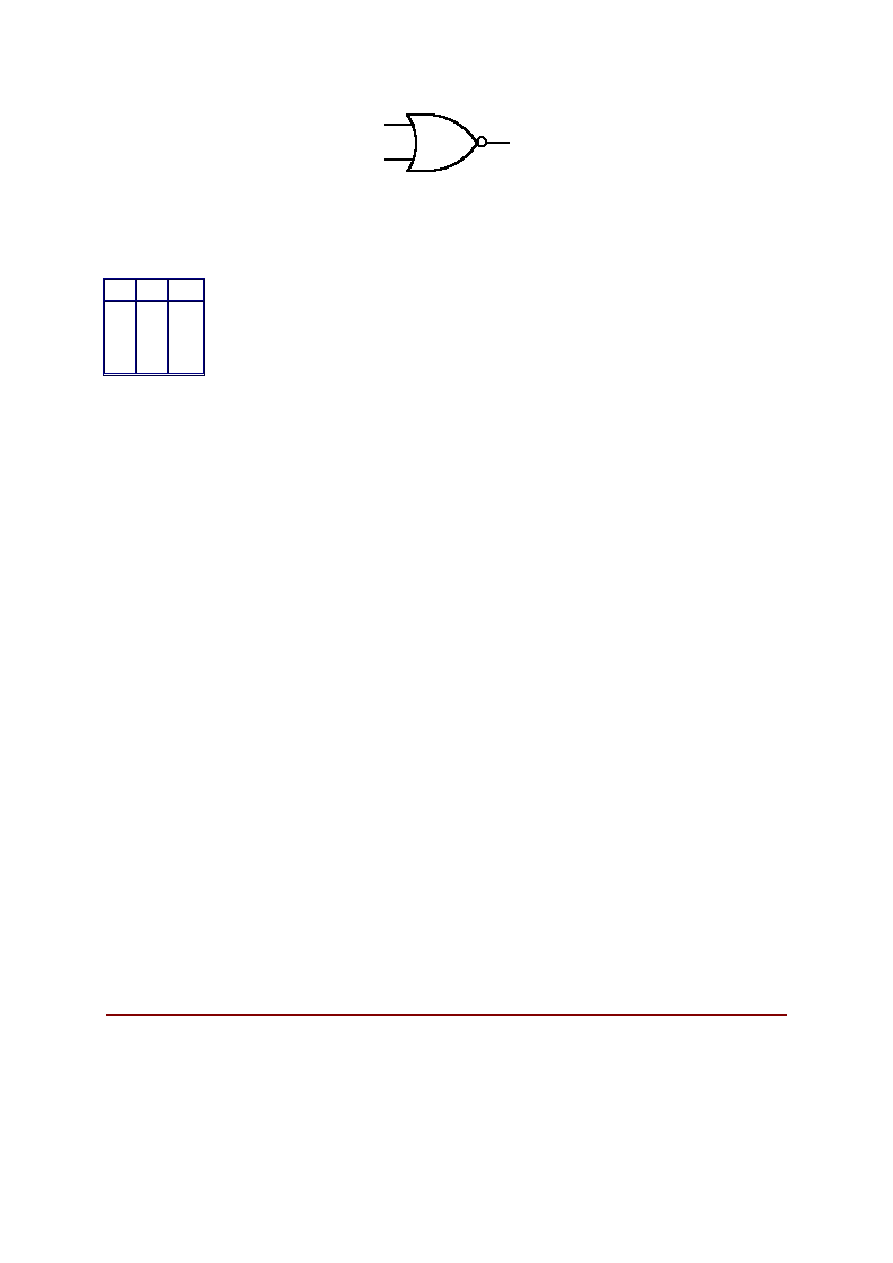

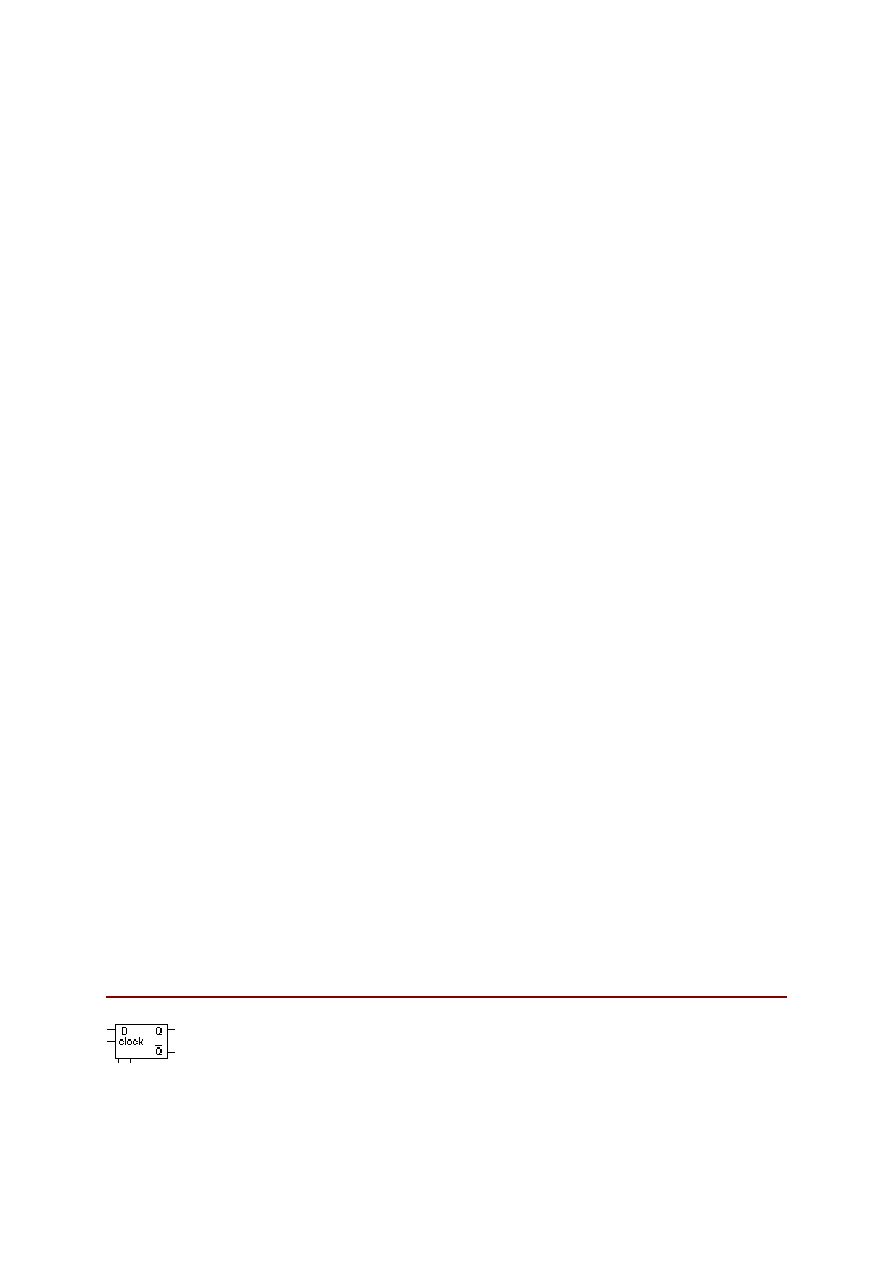

Przerzutnik typu D

Przerzutnik wyzwalany poziomem - schemat logiczny:

Przerzutnik wyzwalany zboczem narastaj

ą

cym - schemat logiczny:

S

ą

trzy rodzaje tego przerzutnika, tzn. wyzwalane poziomem, zboczem narastaj

ą

cym i zboczem

opadaj

ą

cym. Gdy na wej

ś

cie zegarowe jest podany odpowiedni sygnał (jeden z trzech)

przerzutnik sprawdza co jest podane na wej

ś

ciu D i przenosi ten stan na Q. Przerzutnik posiada

te

ż

wej

ś

cia asynchroniczne - SET, RESET. Ł

ą

cz

ą

c na stałe wej

ś

cie D z NIE Q otrzymujemy

przerzutnik T.

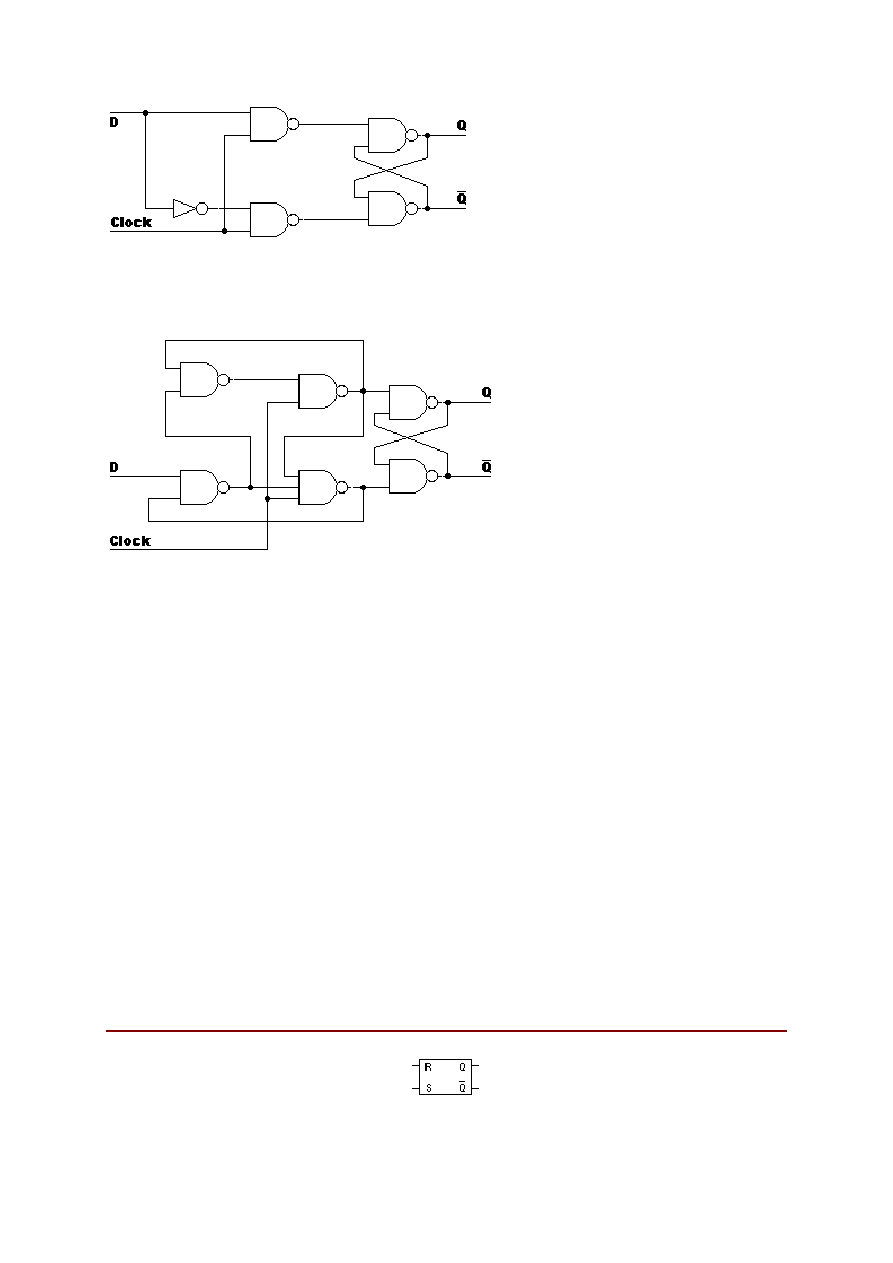

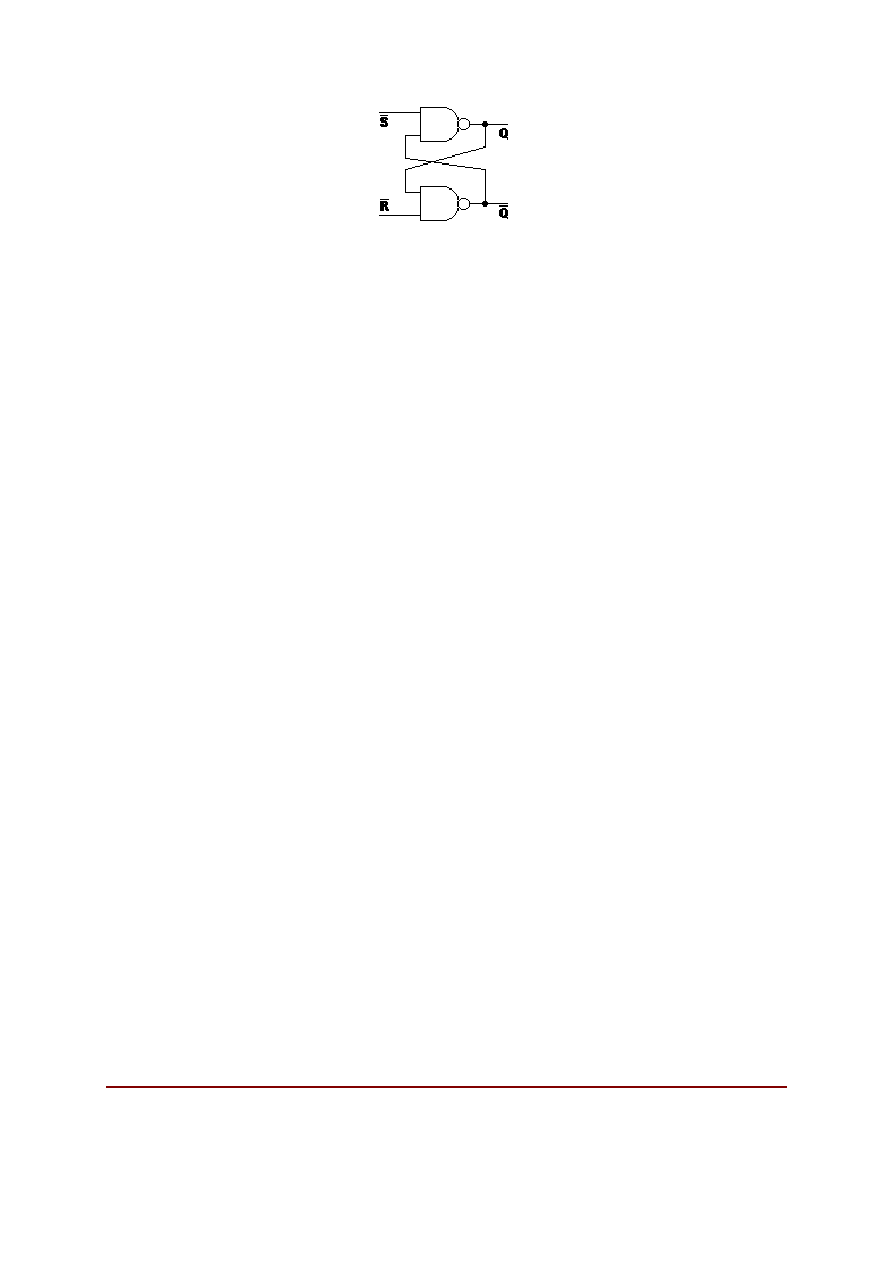

Przerzutnik typu RS

Dla przerzutnika zbudowanego na bramkach NAND sygnałem steruj

ą

cym jest "0", natomiast

dla NOR "1". Je

ś

li na wej

ś

cie SET zostanie podany sygnał steruj

ą

cy na wyj

ś

ciu Q b

ę

dzie "1" -

przerzutnik b

ę

dzie ustawiony, je

ś

li na wej

ś

cie RESET zostanie podany sygnał steruj

ą

cy na

wyj

ś

ciu Q b

ę

dzie "0" - przerzutnik b

ę

dzie zresetowany. Sygnał steruj

ą

cy mo

ż

e by

ć

impulsem.

Je

ś

li na wej

ś

ciach s

ą

narysowane kółeczka to przerzutnik jest sterowany "0". Wyj

ś

cia s

ą

komplementarne, tzn. na ich stany logiczne s

ą

przeciwne. Jest to przerzutnik asynchroniczny,

czyli bez zegara taktuj

ą

cego.

Przerzutnik typu JK

Master Slave:

Przerzutnik zachowuje si

ę

w zale

ż

no

ś

ci od kombinacji stanów wej

ś

ciowych na J i K.

Przerzutnik jest wyzwalany dwuzboczowo, tzn. gdy jest zbocze narastaj

ą

ce układ przepisuje

dane wej

ś

ciowe do wewn

ę

trznego przerzutnika Master a przy opadaj

ą

cym z przerzutnika

Master do przerzutnika Slave. Przerzutnik zachowuje si

ę

w nast

ę

puj

ą

cy sposób:

•

0 0 - stan na wyj

ś

cia nie ulega zmianie

•

1 0 - stan na Q jest ustawiany na "1"

•

0 1 - stan na Q jest ustawiany na "0"

•

1 1 - stan na wyj

ś

ciu zmienia si

ę

na przeciwny

Z przerzutników buduje si

ę

ró

ż

nego rodzaju pami

ę

ci, liczniki i rejestry i dzielniki.

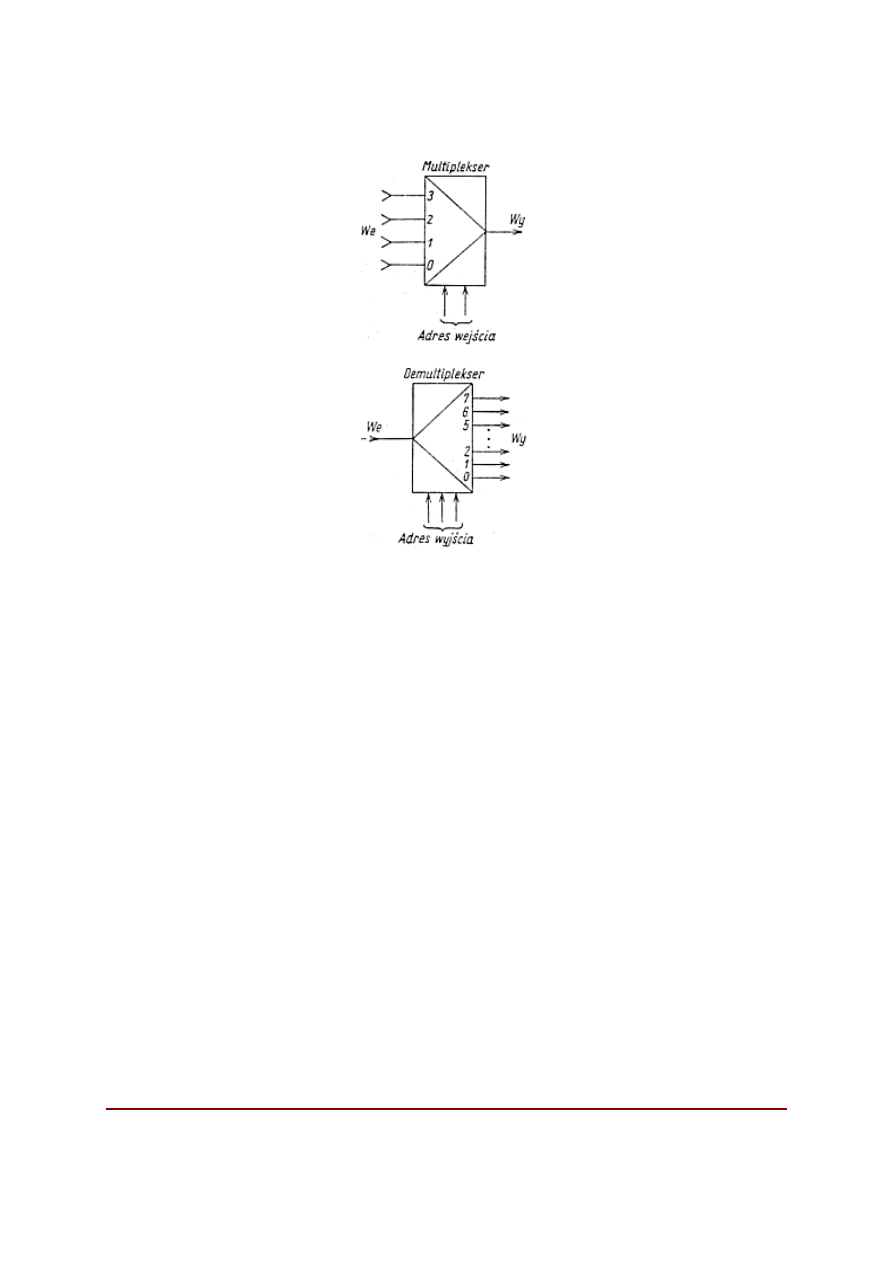

Multipleksery i demultiplreksery

Multiplekser cyfrowy jest to układ posiadaj

ą

cy n wej

ść

adresowych, 2

n

wej

ść

danych i jedno

wyj

ś

cie. W zale

ż

no

ś

ci od kombinacji na wej

ś

ciu adresowym multiplekser ł

ą

czy jedno z wej

ść

danych z wyj

ś

ciem. Demultiplekser działa odwrotnie, czyli posiada n wej

ść

adresowych, 2

n

wyj

ść

i jedno wej

ś

cie.

Oznaczenia układów scalonych TTL

Pierwsza litera oznaczenia okre

ś

la sposób wykonania według nast

ę

puj

ą

cych reguł:

U - układ półprzewodnikowy, monolityczny, bipolarny,

H - układ hybrydowy,

M - układ półprzewodnikowy monolityczny unipolarny.

Druga litera oznaczenia okre

ś

la rodzaj ogólnej funkcji układu scalonego:

C - układy cyfrowe,

L - układy analogowe,

R - inne układy scalone.

Trzecia litera okre

ś

la przeznaczenie układu scalonego:

A - do zastosowa

ń

specjalnych,

Y - do zastosowa

ń

profesjonalnych,

T - do zastosowa

ń

profesjonalnych o podwy

ż

szonej niezawodno

ś

ci,

Q - do zastosowa

ń

specjalnych o podwy

ż

szonej niezawodno

ś

ci,

X - prototypowe, do

ś

wiadczalne lub na zamówienia.

brak litery do zastosowa

ń

w sprz

ę

cie powszechnego u

ż

ytku.

Pierwsza cyfra okre

ś

la zakres dopuszczalnej temperatury otoczenia podczas pracy w °C:

4 - od -55 do +85

5 - od -35 do +i25

6 - od -40 do +85

7 - od 0 do +70

8 - od -25 do +85

Druga, trzecia, czwarta lub pi

ą

ta cyfra stanowi

ą

liczb

ę

porz

ą

dkow

ą

okre

ś

laj

ą

c

ą

dany typ

układu.

Po drugiej cyfrze w oznaczeniach monolitycznych cyfrowych układów scalonych mog

ą

by

ć

wprowadzone litery okre

ś

laj

ą

ce seri

ę

układu:

H - seria szybka,

S - seria bardzo szybka,

brak litery - seria standardowa

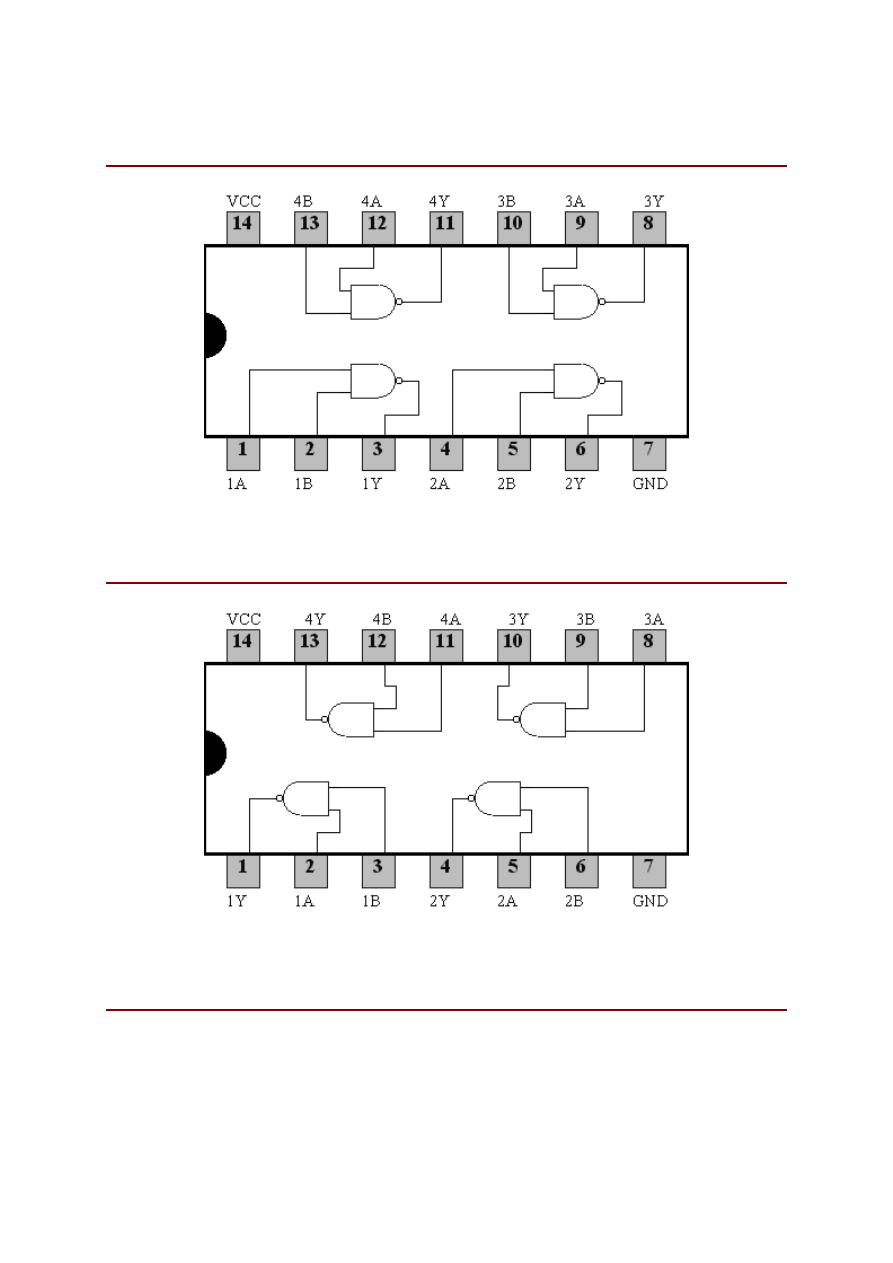

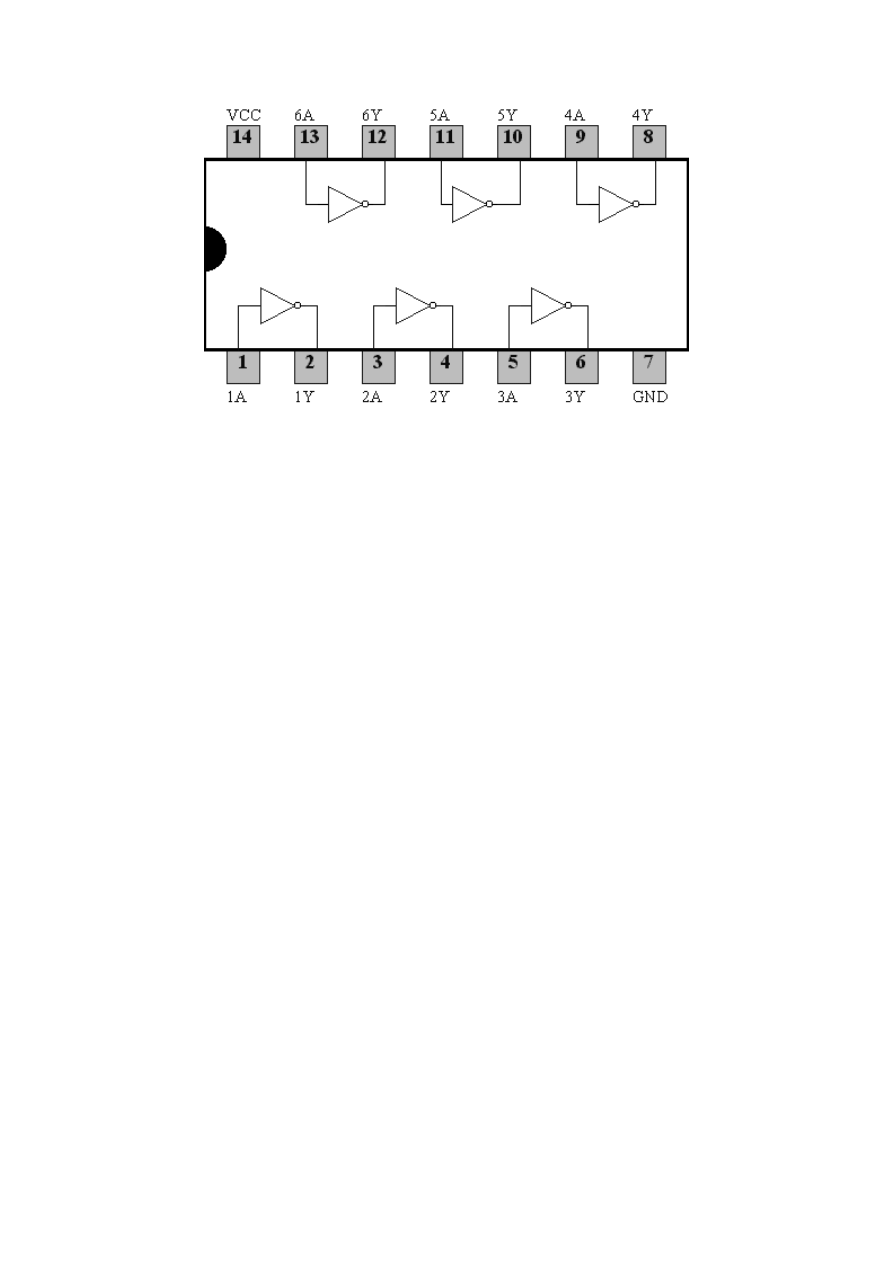

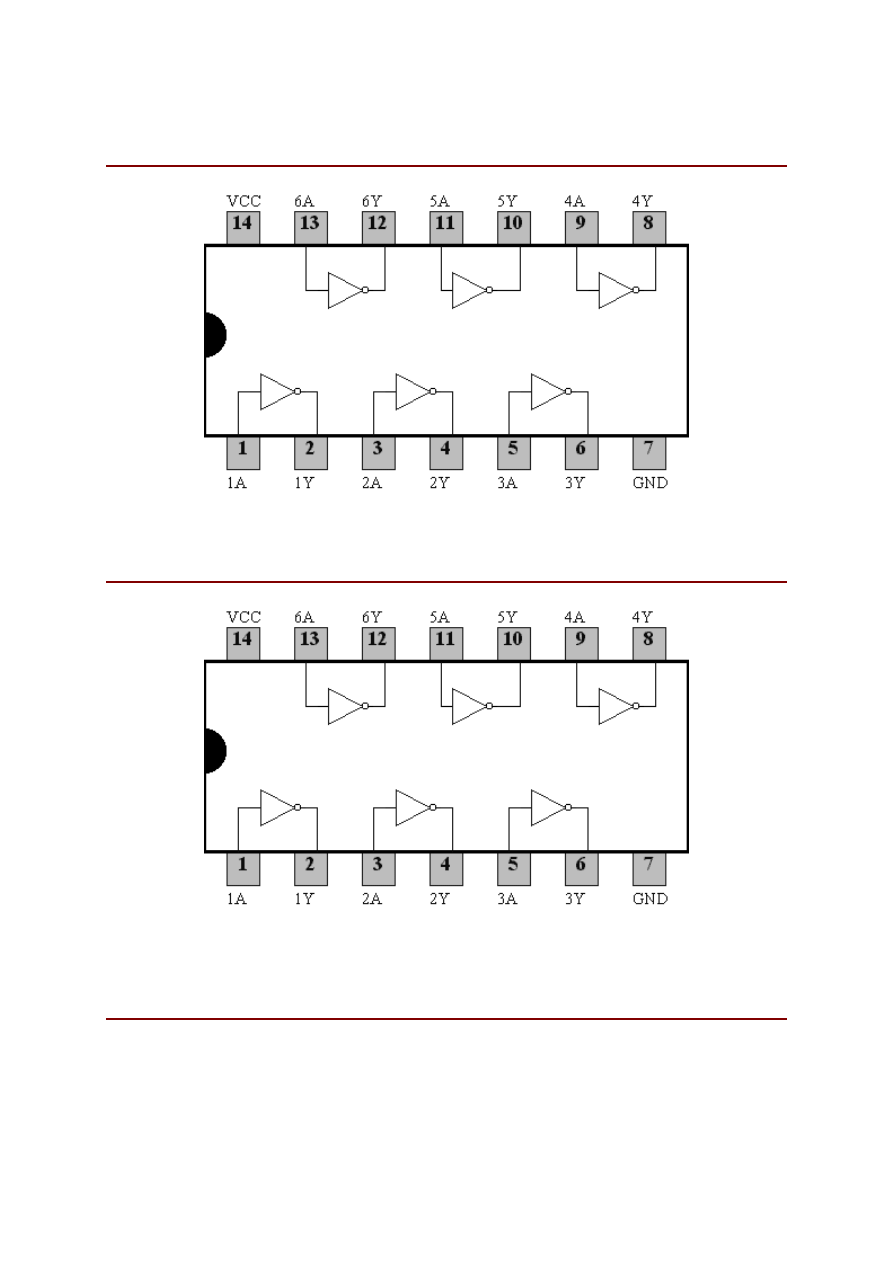

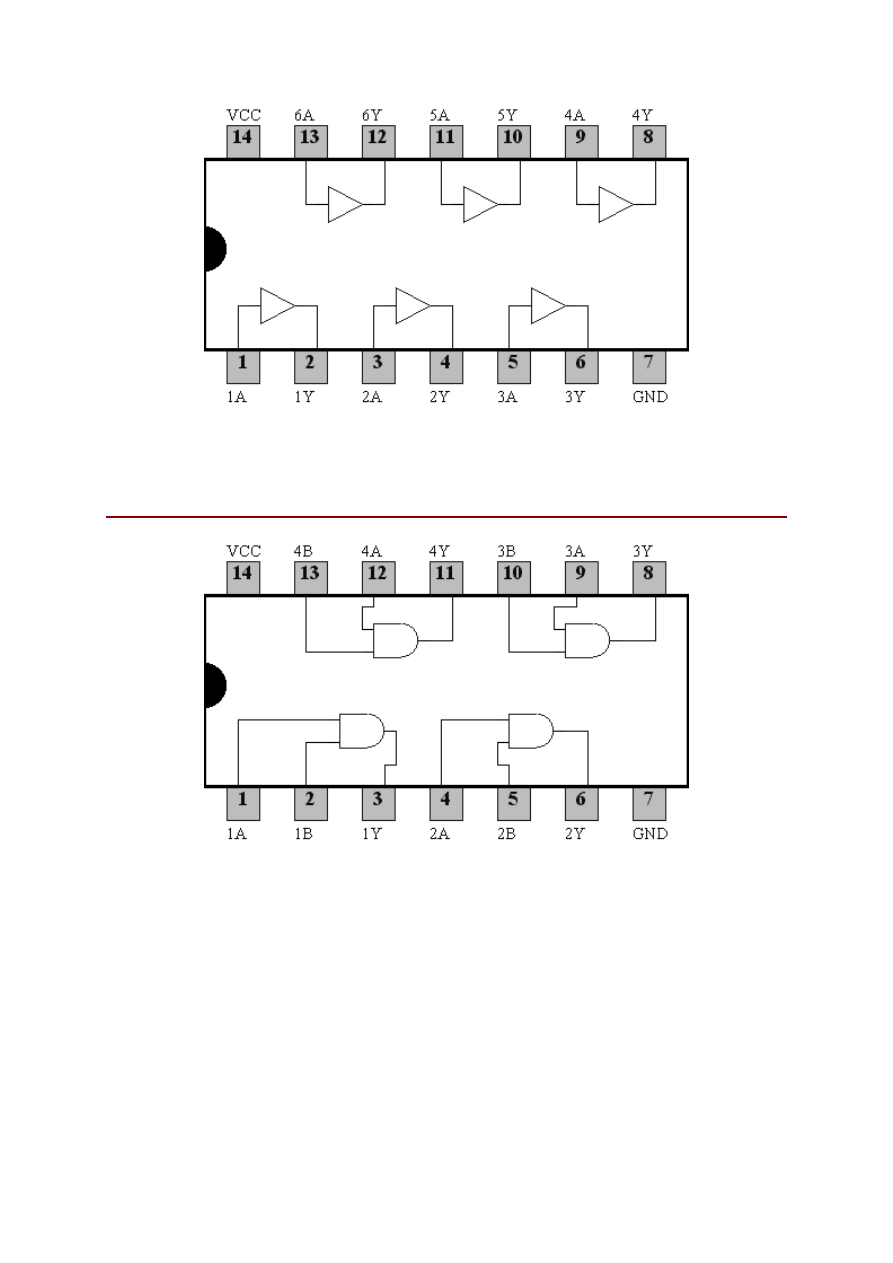

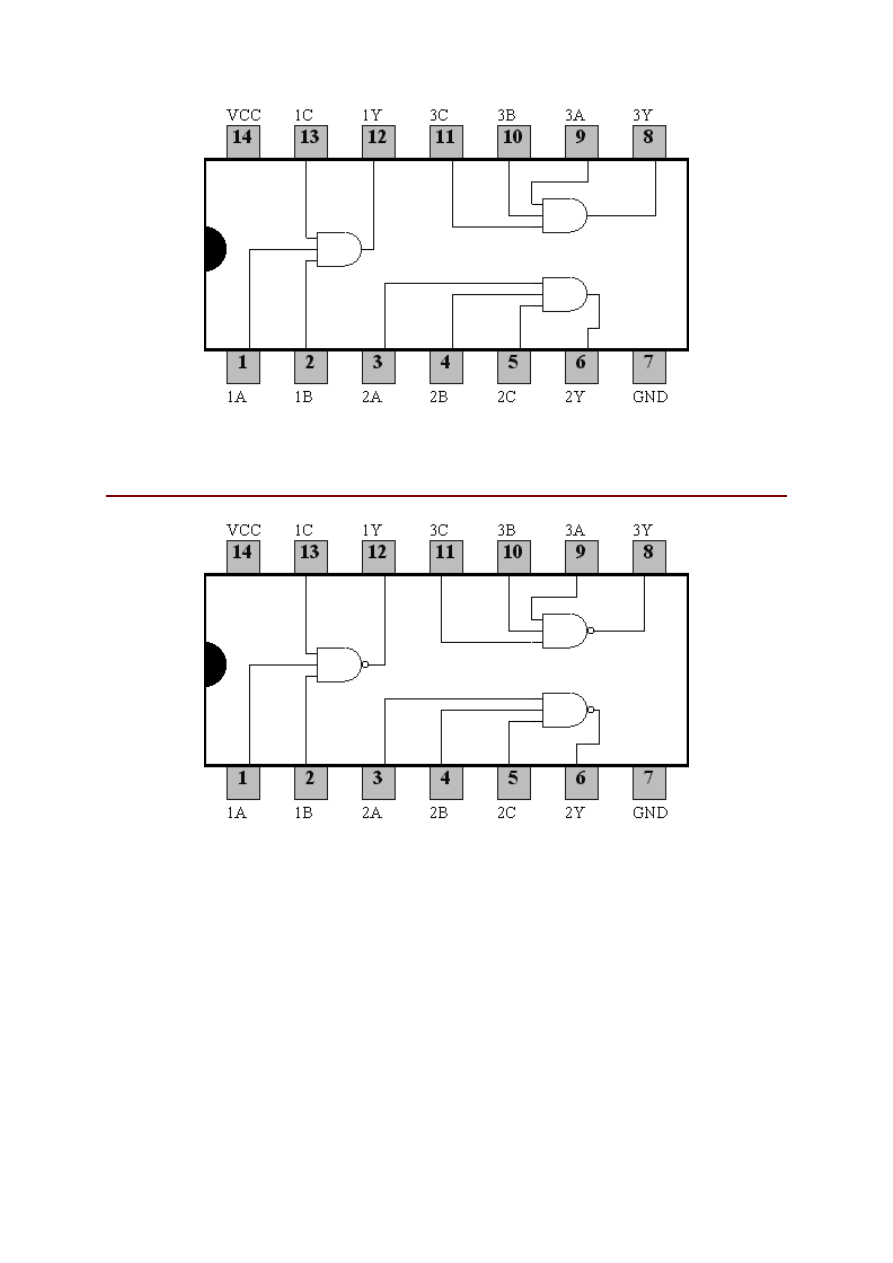

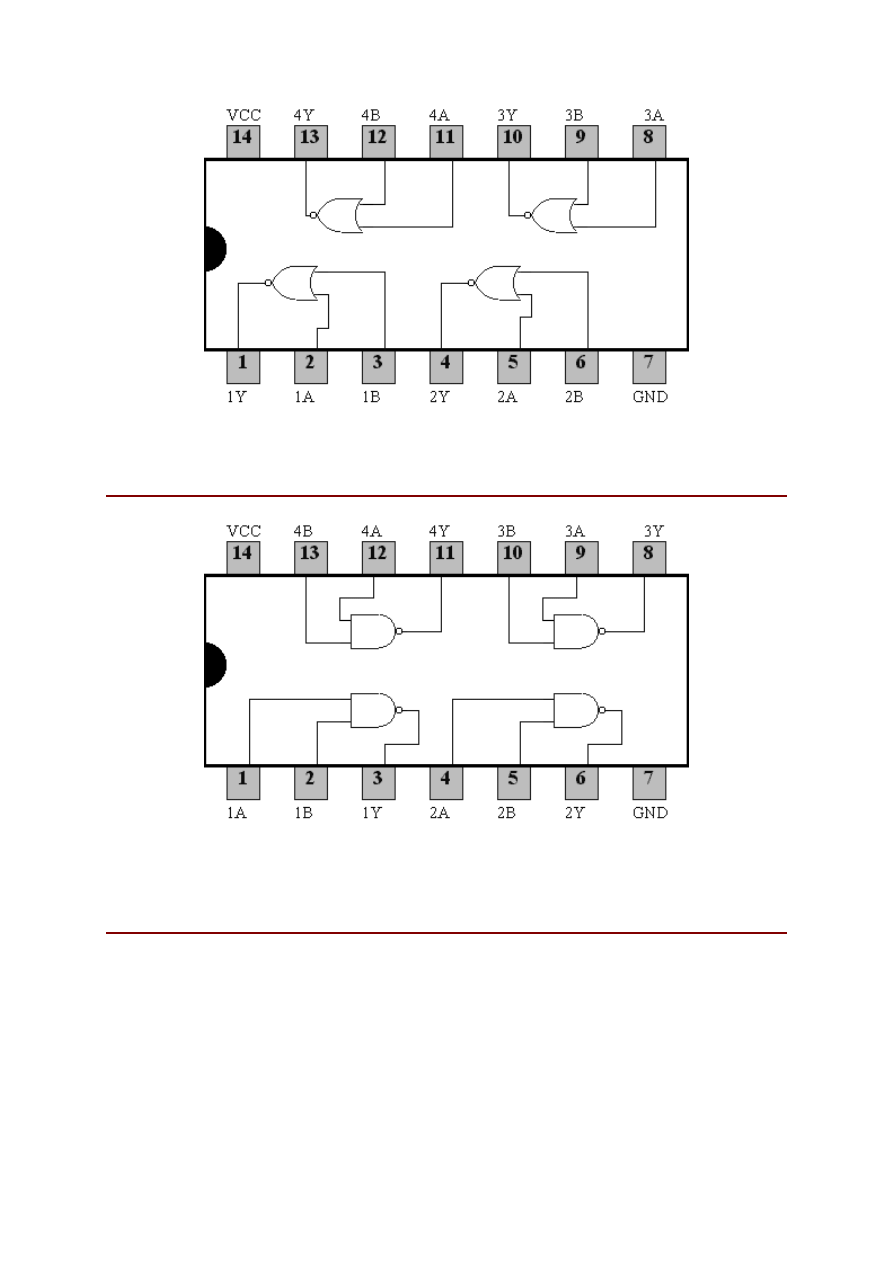

Podstawowe układy TTL: 7400; 7401; 7402; 7403; 7404

7400: 4x 2-wej

ś

ciowe bramki NAND

7401: 4x 2-wej

ś

ciowe bramki NAND z otwartym kolektorem tranzystora

wyj

ś

ciowego

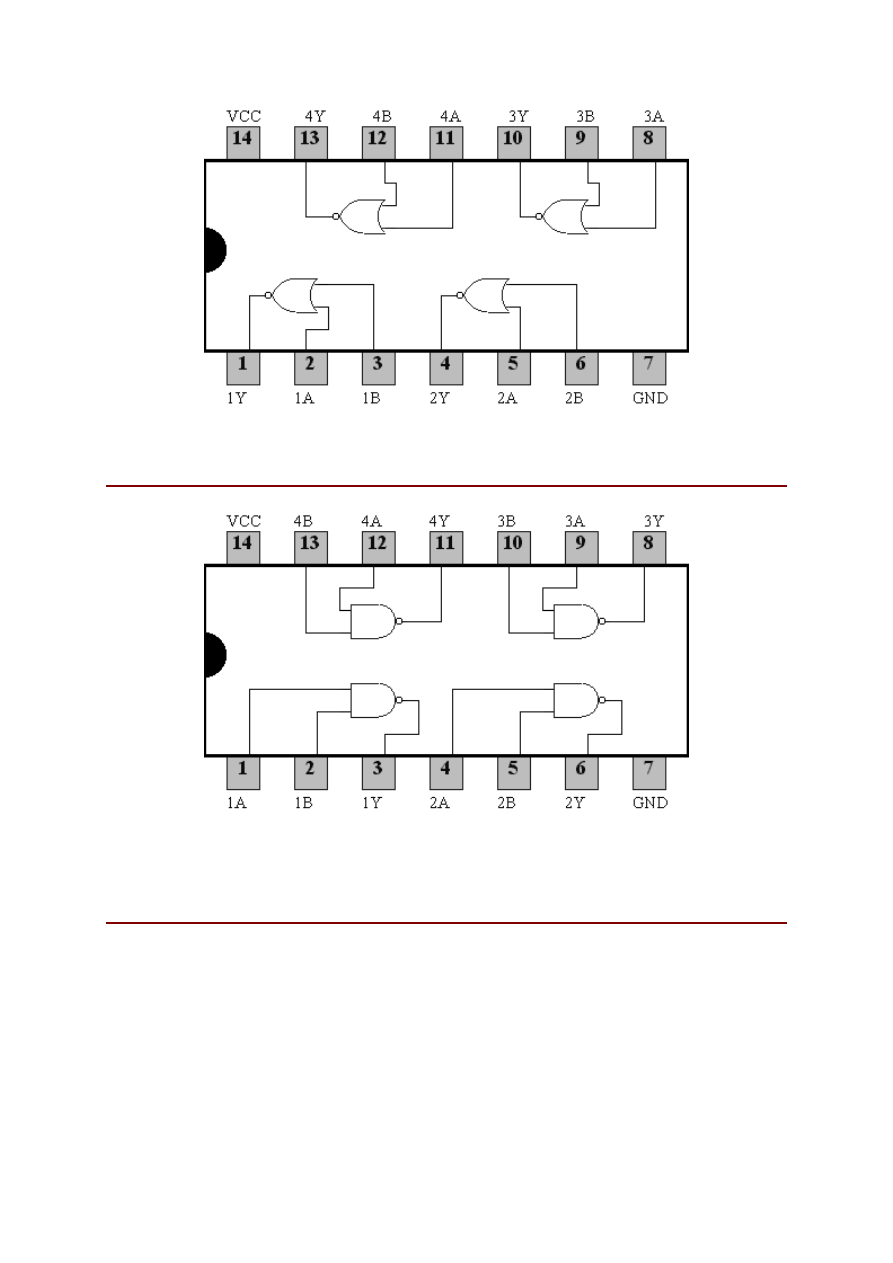

7402: 4x 2-wej

ś

ciowe bramki NOR

7403: 4x 2-wej

ś

ciowe bramki NAND z otwartym kolektorem/drenem tranzystora

wyj

ś

ciowego

6x inwerter

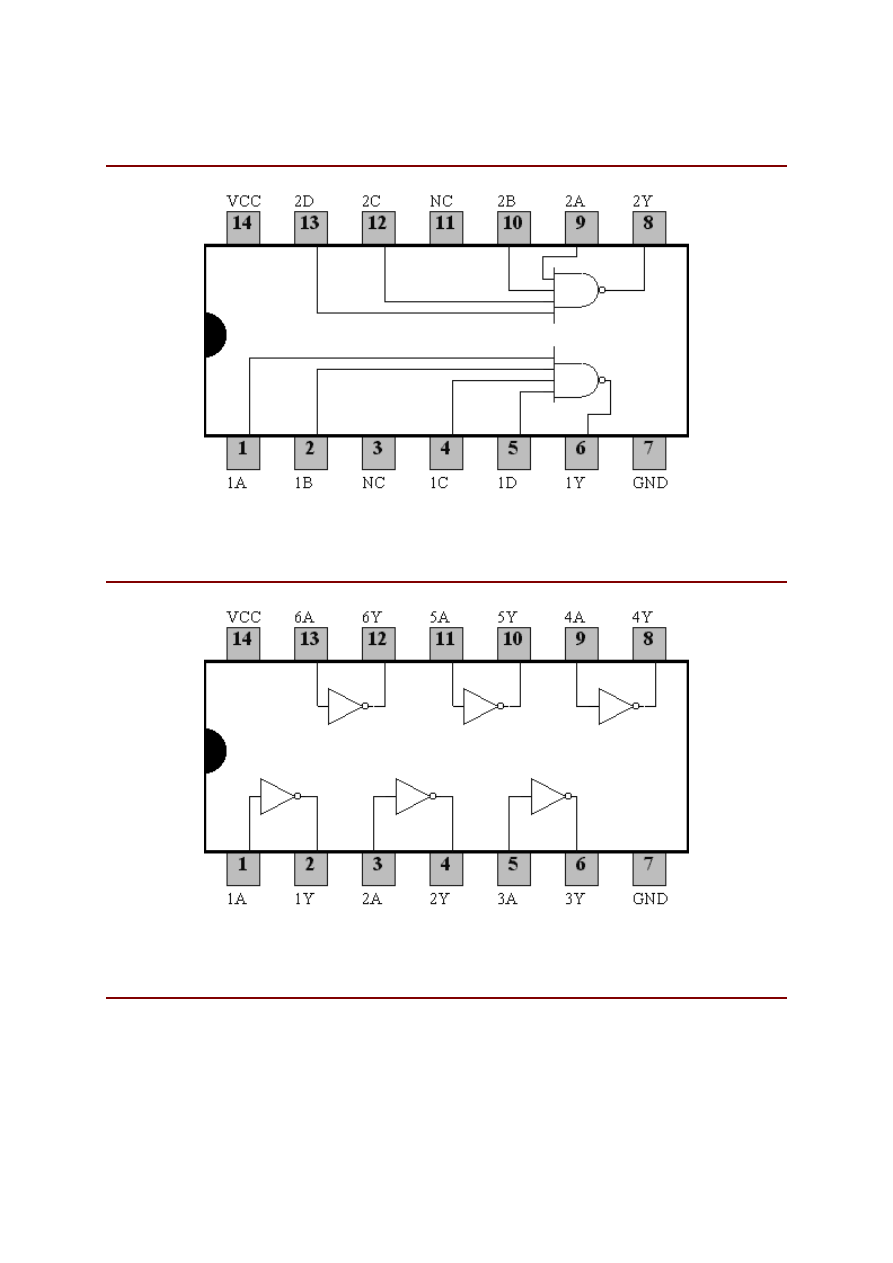

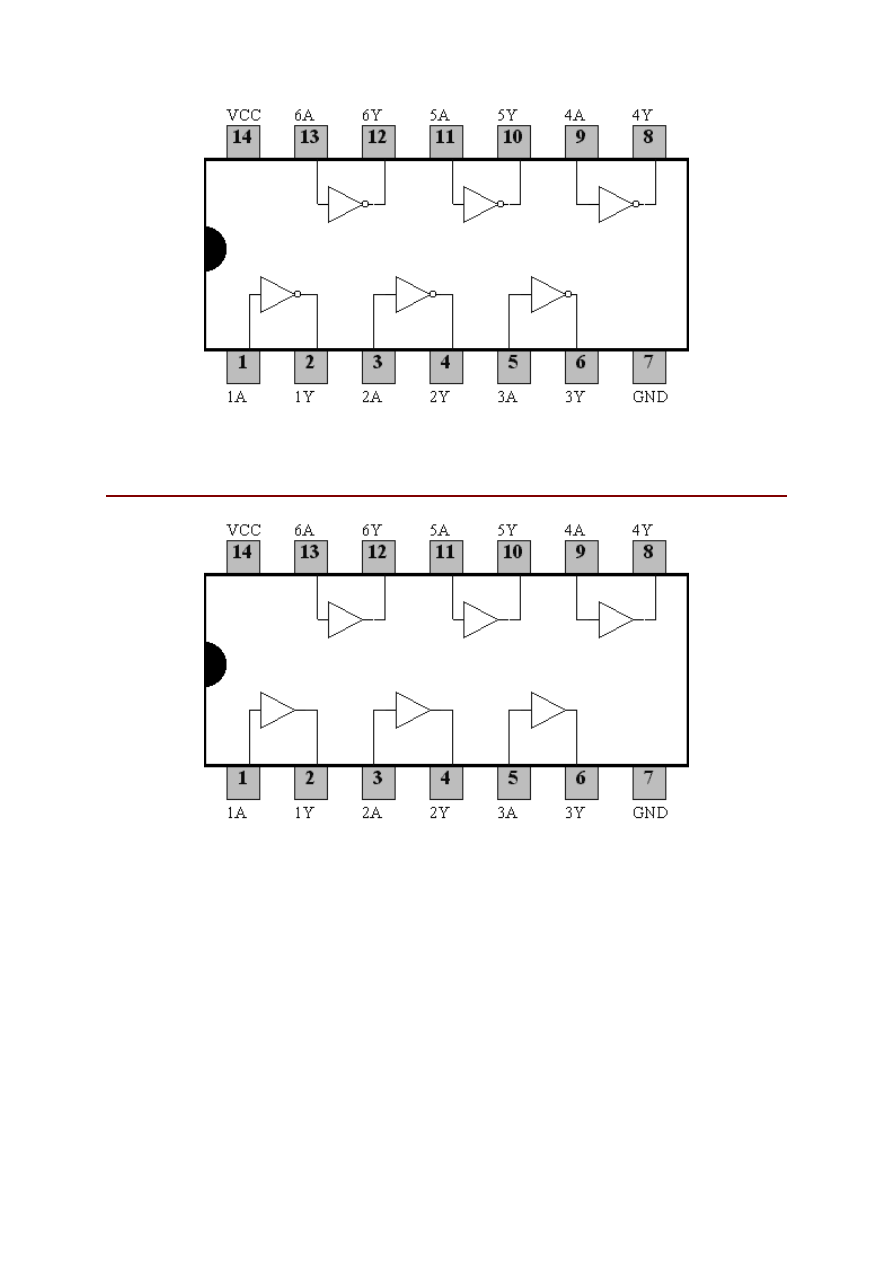

Podstawowe układy TTL: 7405; 7406; 7407; 7408

7405: 6x inwerter z otwartym kolektorem tranzystora wyj

ś

ciowego

7406: 6x inwerter buforowy z otwartym kolektorem tranzystora wyj

ś

ciowego

30V

7407: 6x wzmacniacz buforowy z otwartym kolektorem tranzystora

wyj

ś

ciowego 30V

7408: 4x 2-wej

ś

ciowe bramki AND

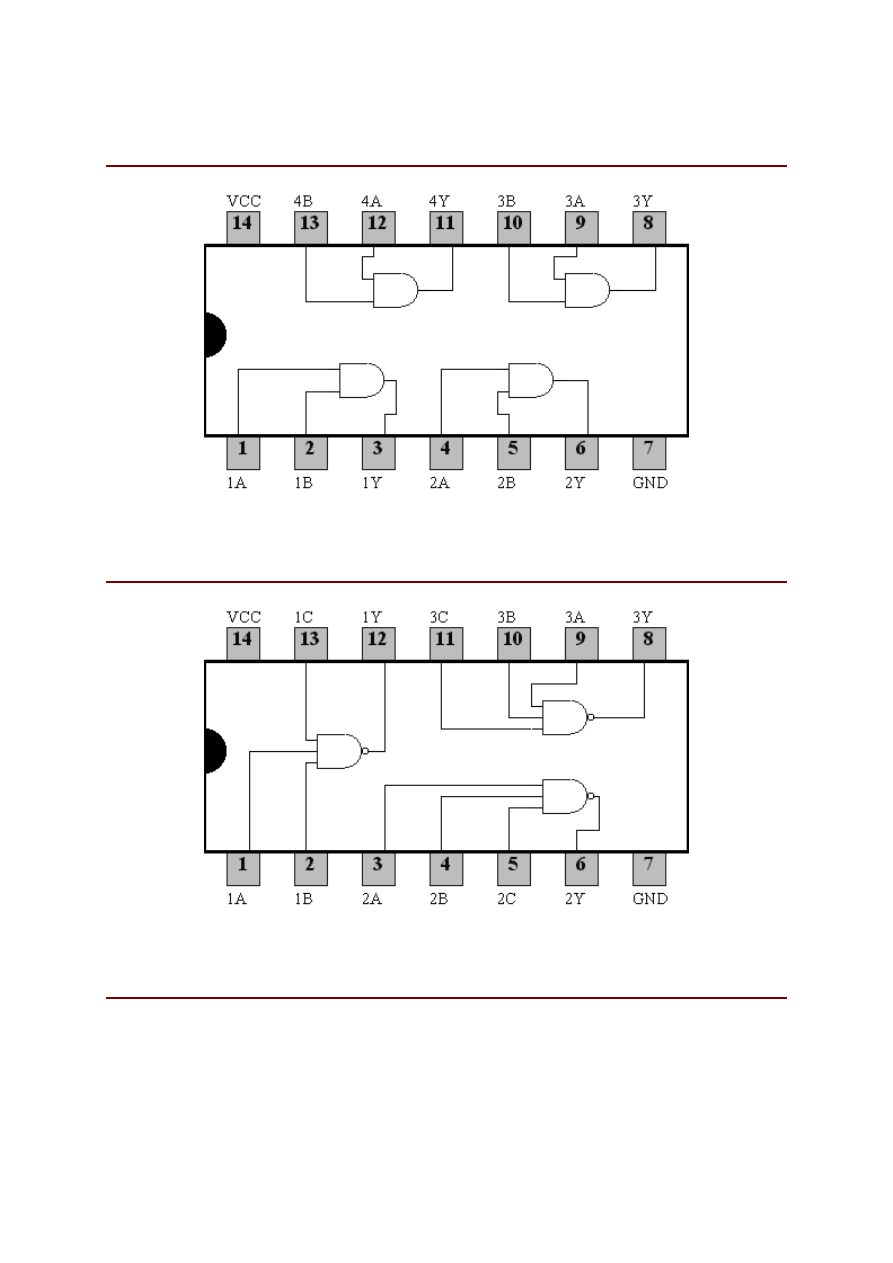

Podstawowe układy TTL: 7409; 7410; 7411; 7412

7409: 4x 2-wej

ś

ciowe bramki AND z otwartym kolektorem

7410: 3x 3-wej

ś

ciowe bramki NAND

7411: 3x 3-wej

ś

ciowe bramki AND

7412: 3x 3-wej

ś

ciowe bramki NAND z otwartym kolektorem

Podstawowe układy TTL: 7413;7414; 7416; 7417

7413: 2x 4-wej

ś

ciowe bramki NAND z przerzutnikiem Schmitta

7414: 6x inwerter z przerzutnikiem Schmitta

7416: 6x inwerter buforowy z otwartym kolektorem tranzystora wyj

ś

ciowego

7417: 6x wzmacniacz buforowy z otwartym kolektorem tranzystora

wyj

ś

ciowego 15V

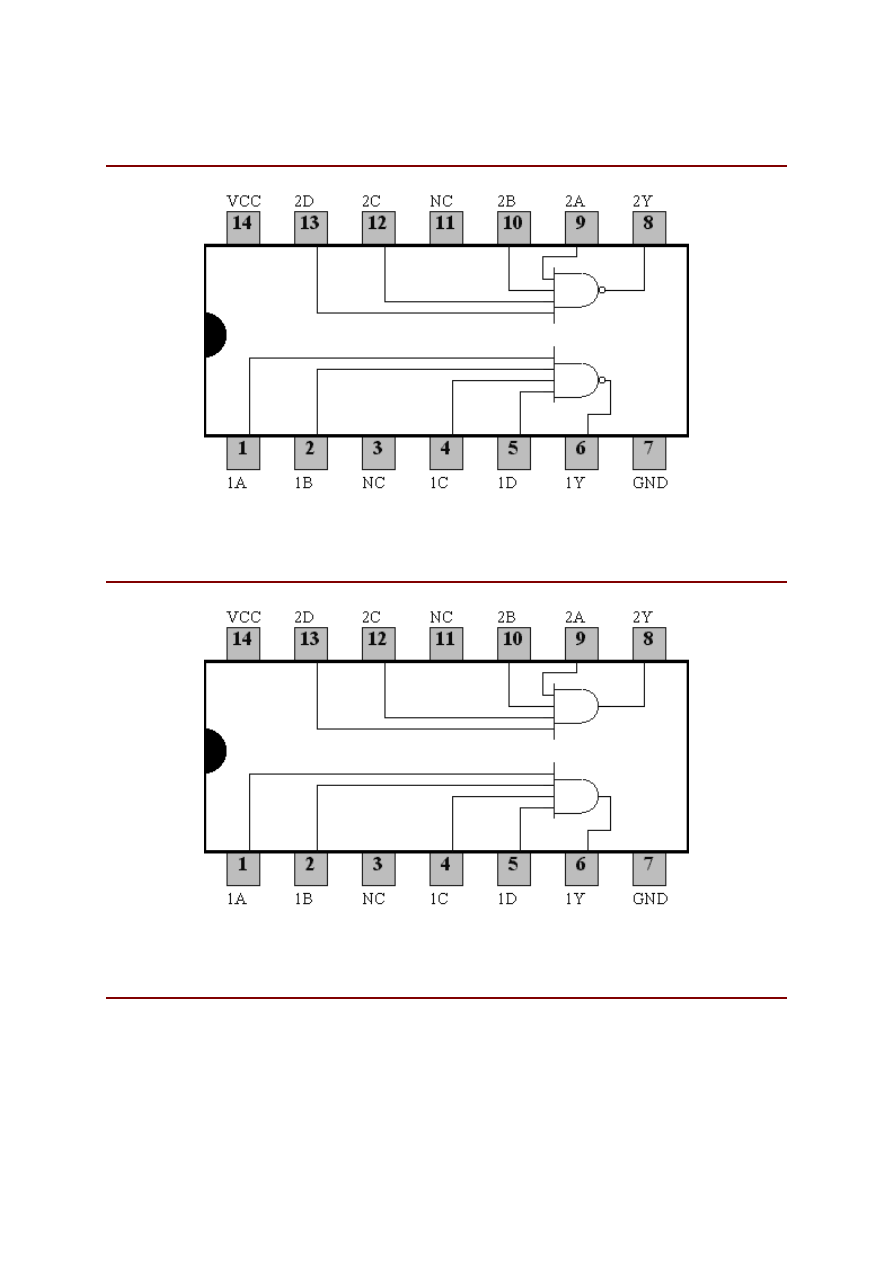

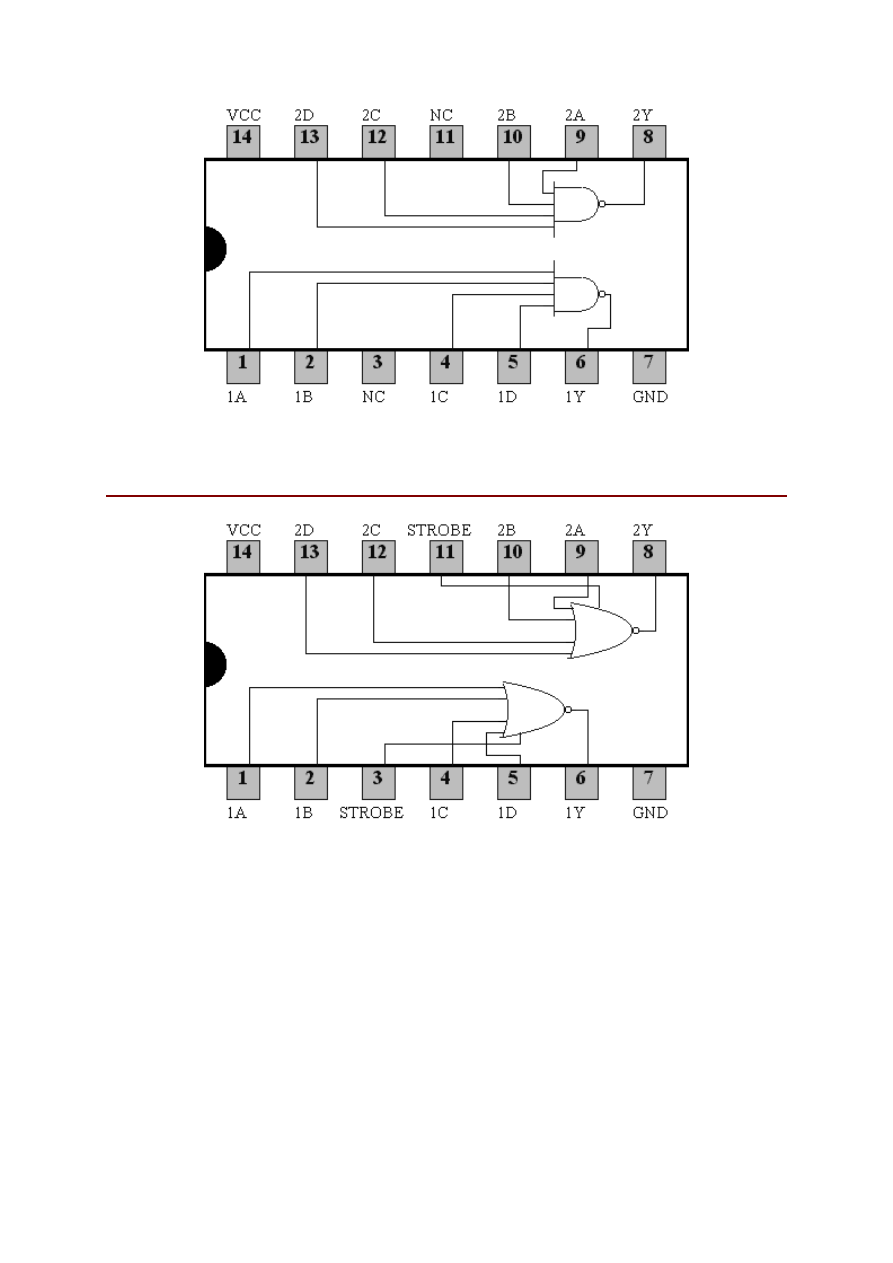

Podstawowe układy TTL: 7420; 7421; 7422; 7425

7420: 2x 4-wejściowe bramki NAND

7421: 2x 4-wejściowe bramki AND

7422: 2x 4-wejściowe bramki NAND z otwartym kolektorem tranzystora wyjściowego

7425: 2x 4-wejściowe bramki NOR z wejściem strobującym

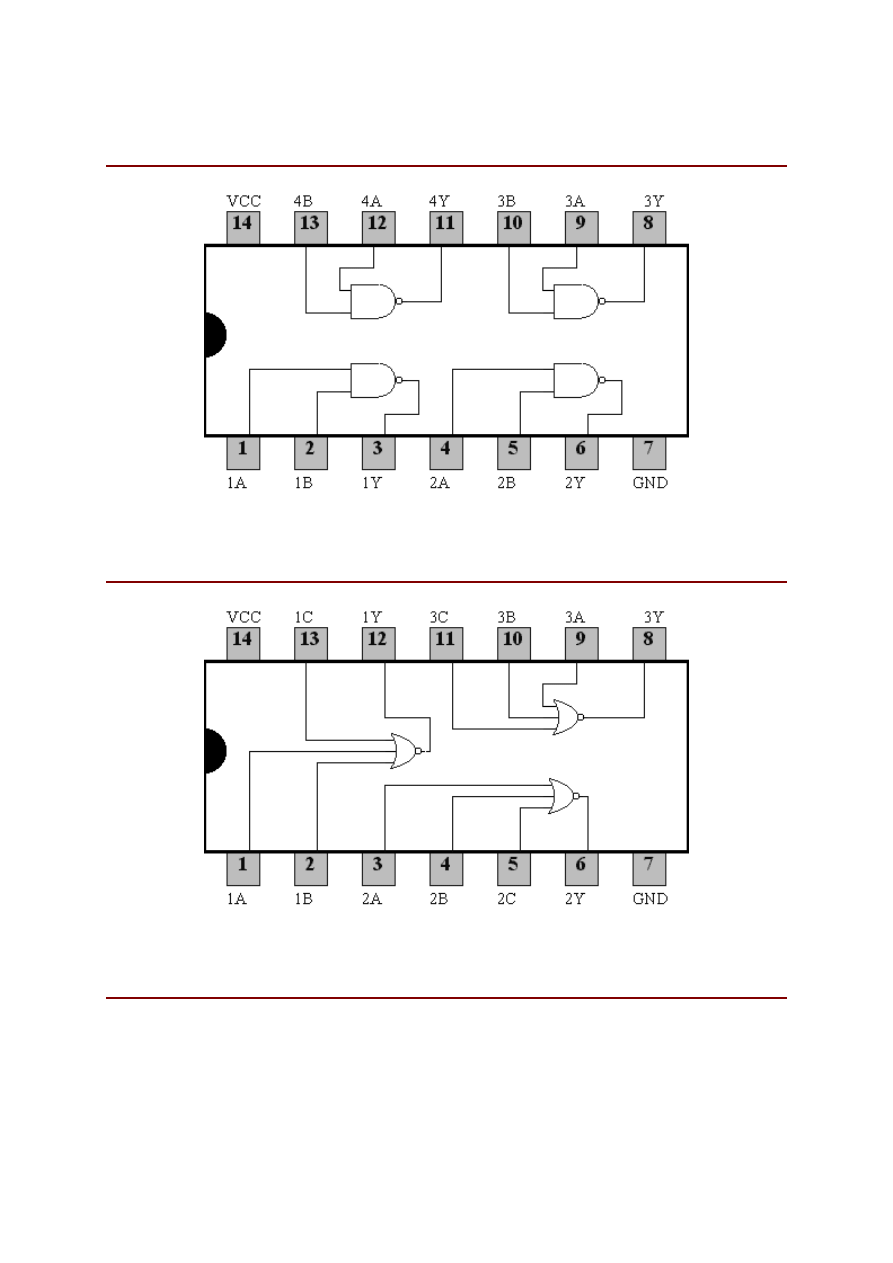

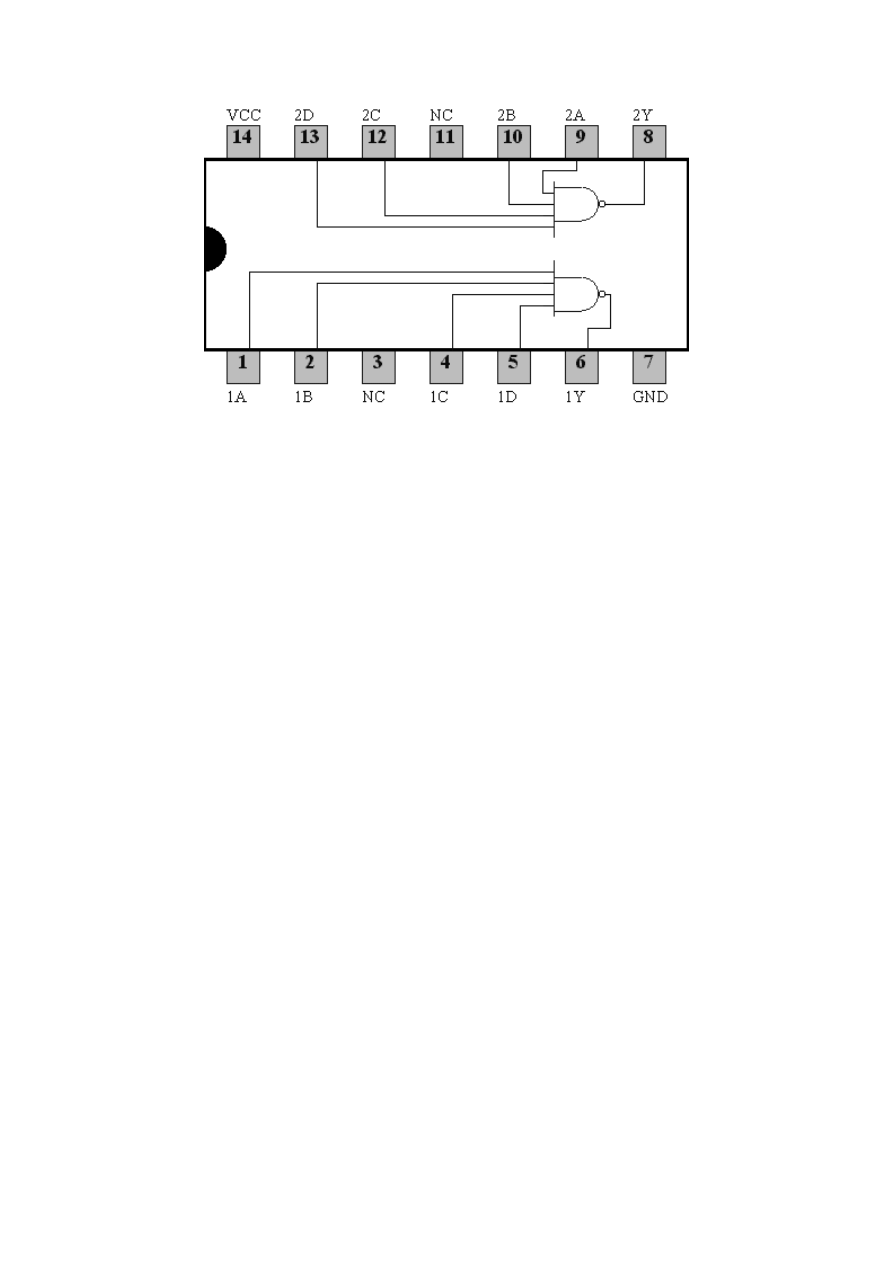

Podstawowe układy TTL: 7426; 7427; 7428; 7430

7426: 4x 2-wejściowe bramki NAND z otwartym kolektorem tranzystora wyjściowego

7427: 3x 3-wejściowe bramki NOR

7428: 4x 2-wejściowe buforowe bramki NOR

7430: 1x 8-wejściowa bramka NAND

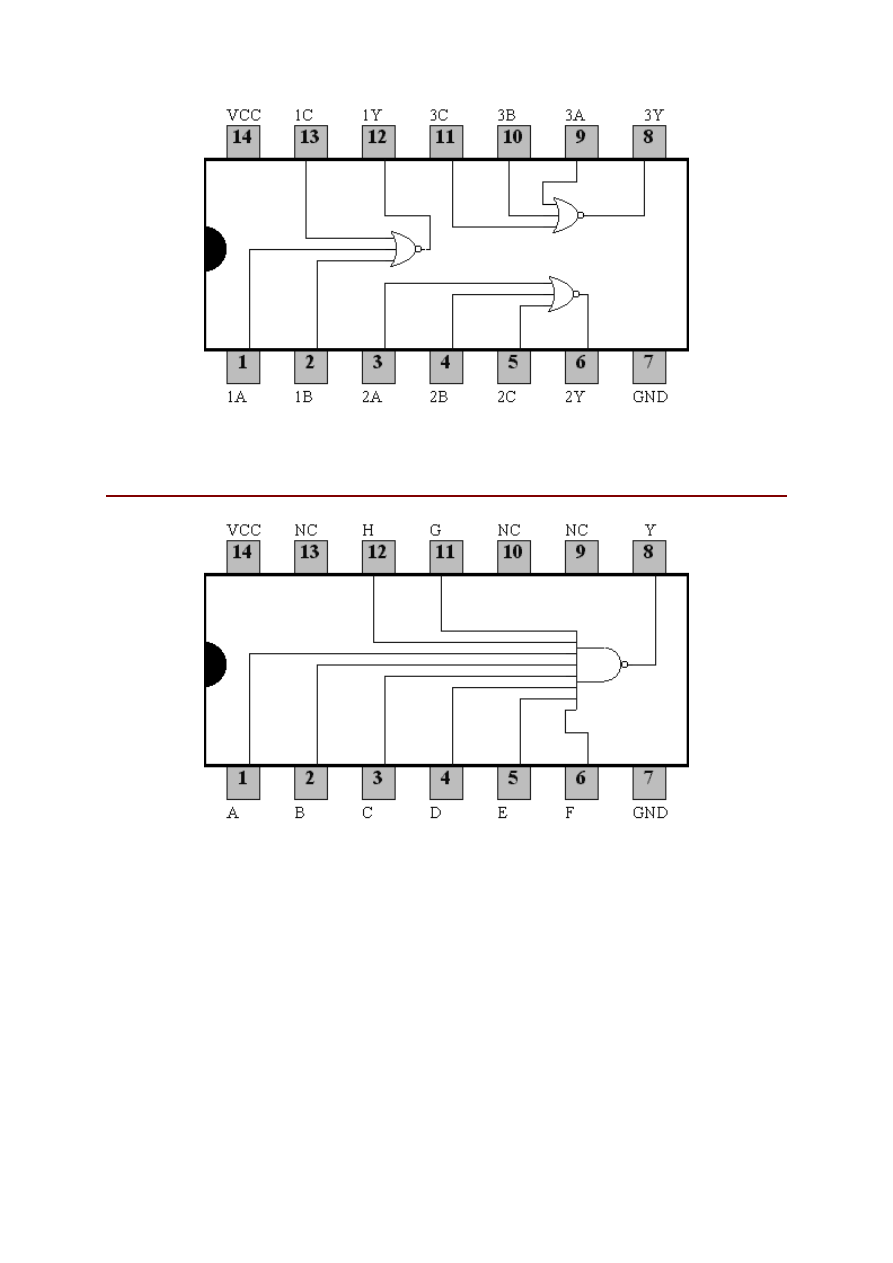

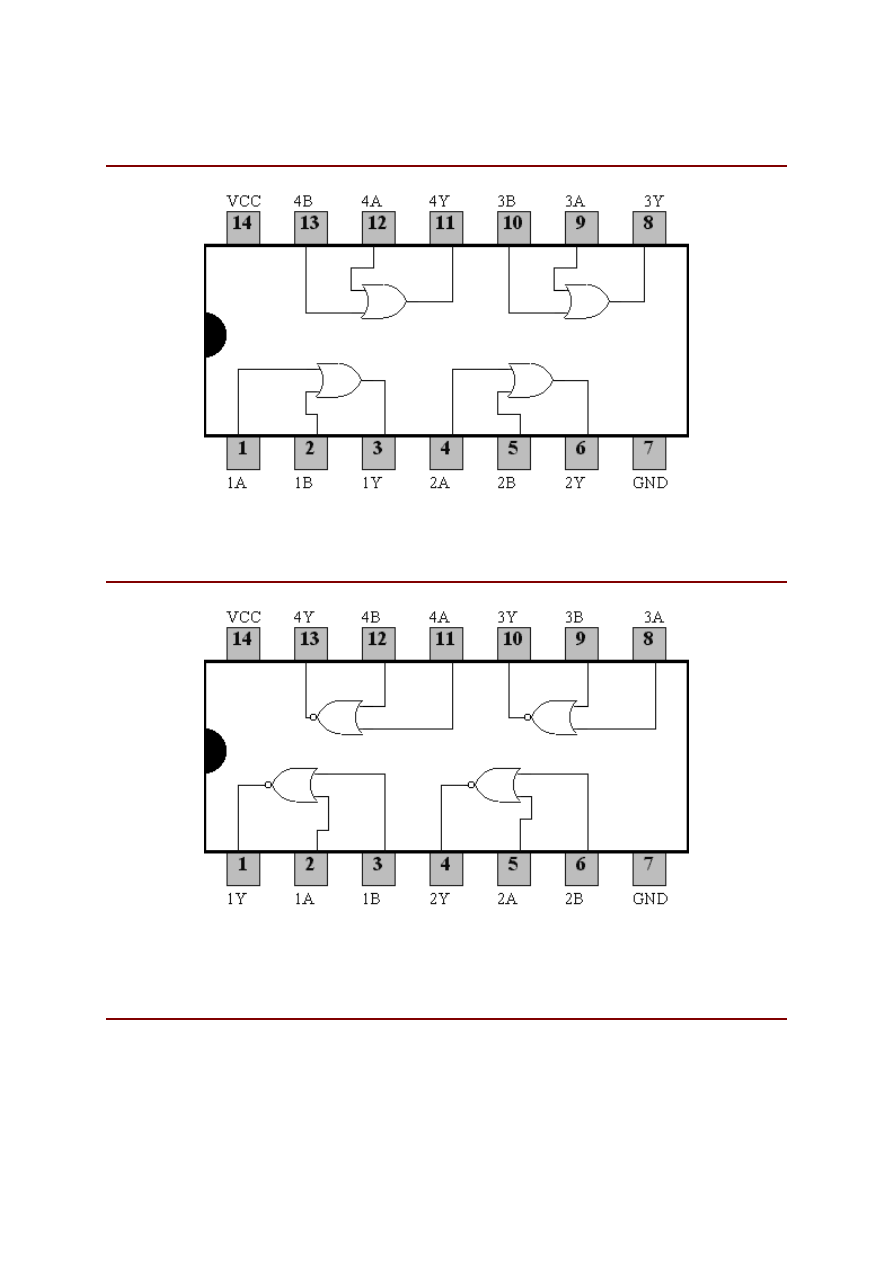

Podstawowe układy TTL: 7432;7433;7437;7438;7440

7432: 4x 2-wejściowe bramki OR

7433: 4x 2-wejściowe bramki buforowe NOR z otwartym kolektorem tranzystora

wyjściowego

7437: 4x 2-wejściowe bramki buforowe NAND

7438: 4x 2-wejściowe bramki buforowe NAND z otwartym kolektorem tranzystora

wyjściowego

7440: 2x 4-wejściowe bramki buforowe NAND

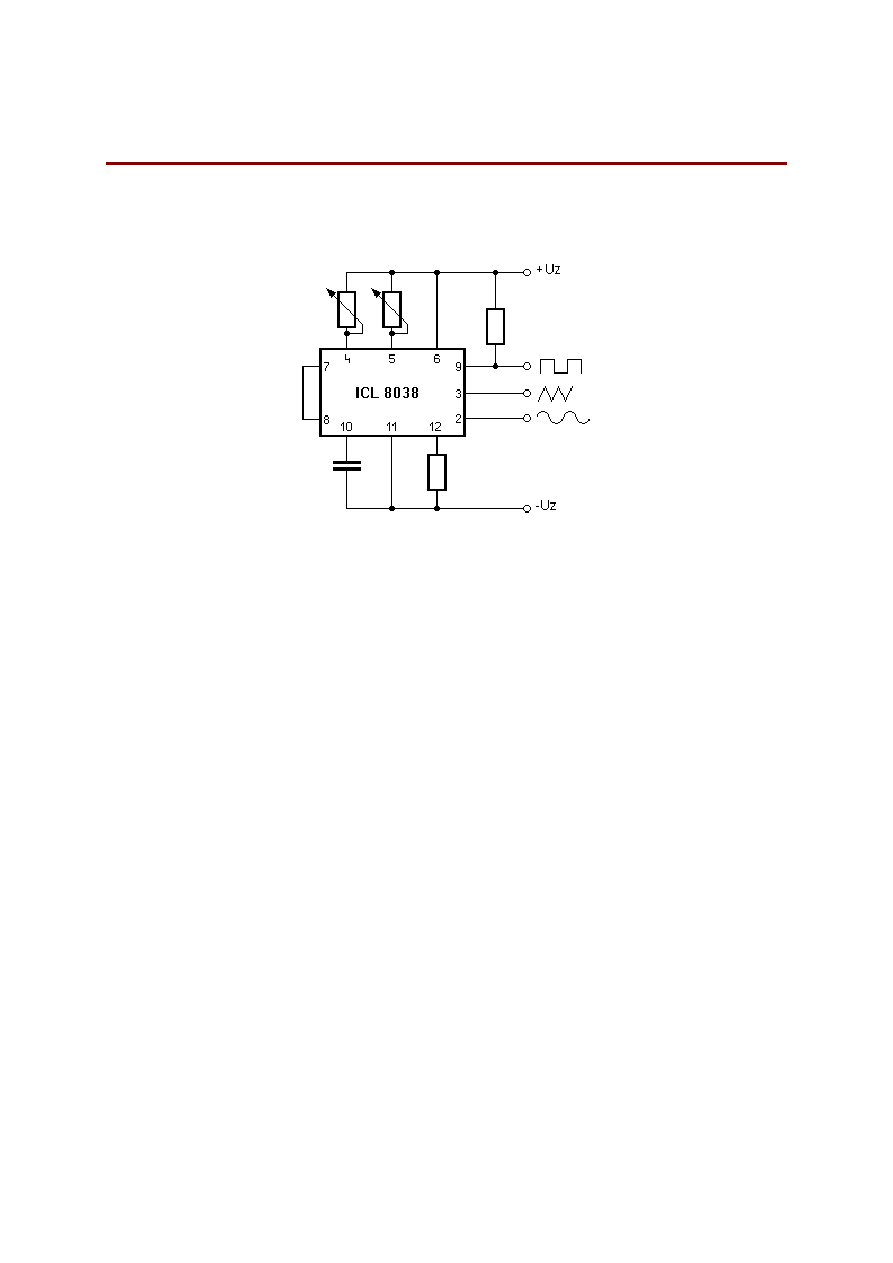

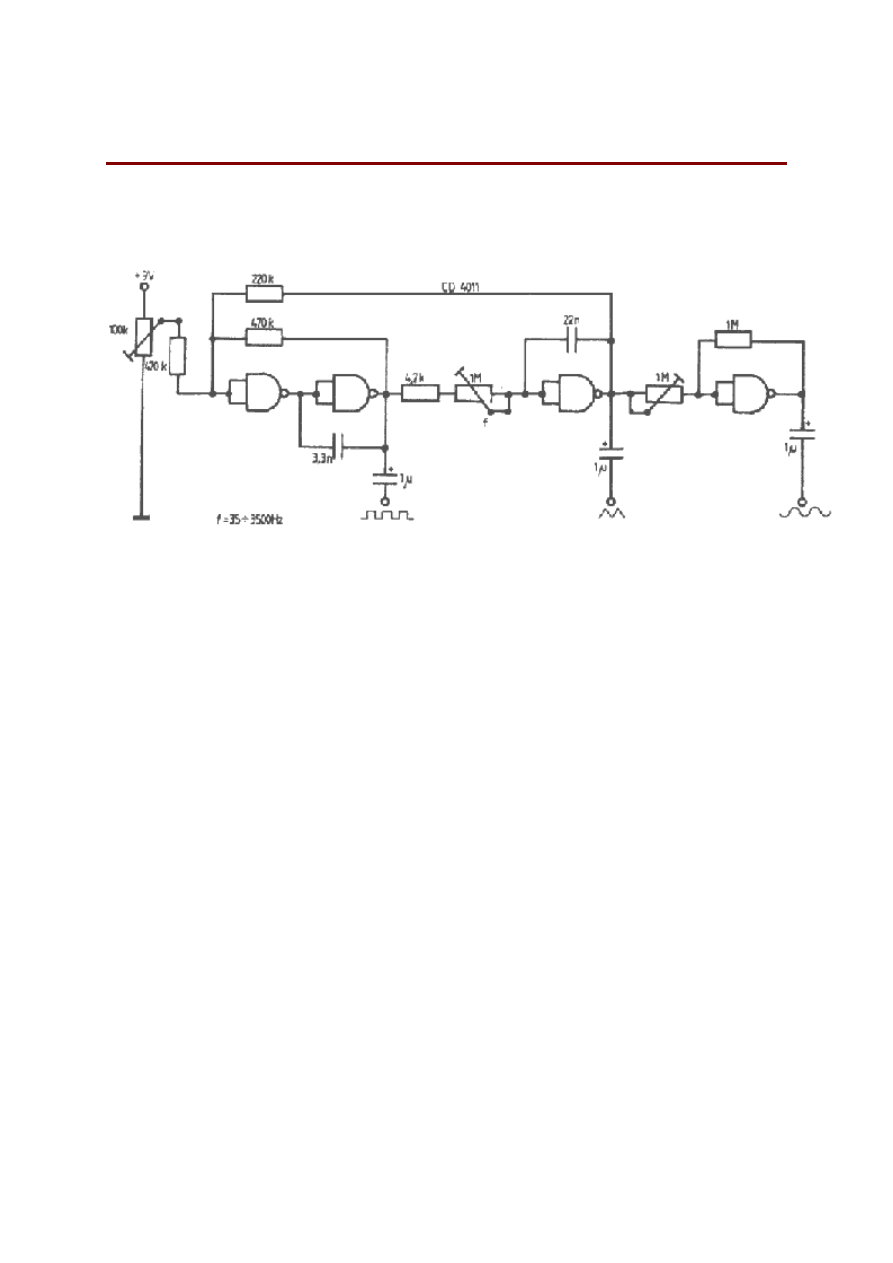

Generator przebiegów

Generator przydatny do eksperymentów z układami cyfrowymi. Elementy

dobieramy eksperymentalnie w zale

ż

no

ś

ci od potrzebnego sygnału.

Próbnik stanów logicznych

Układ słu

ż

y do sprawdzania stanów logicznych H lob L. Bardzo prosta

konstrukacja. Odzczytu dokonuje si

ę

za pomoc

ą

diod LED (np. czerwonej dla L

i zielonej dla H).

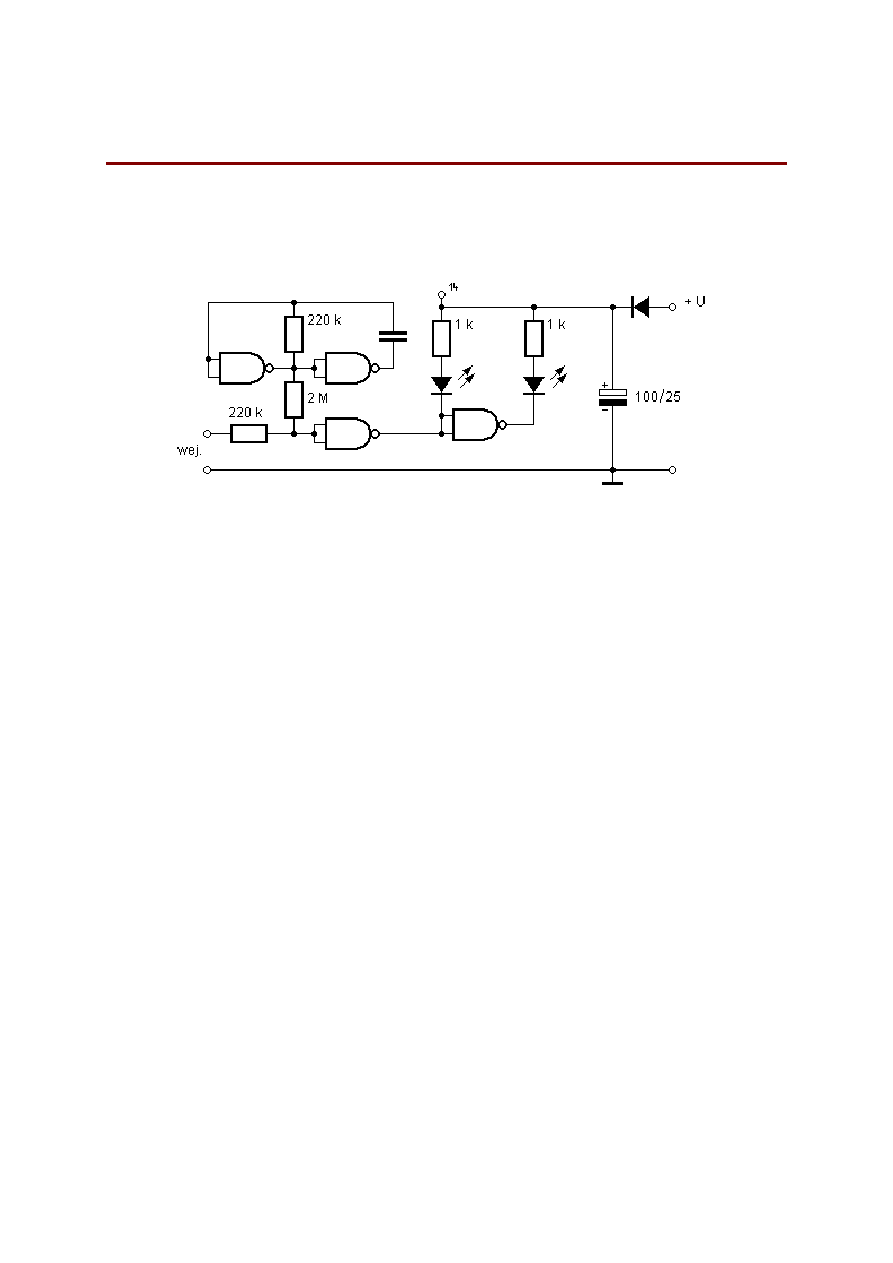

Generator funkcji

Prosty generator funkcji zbudowany na bramkach logicznych 4011 pracujący w

czestotliwości od 35 do 3500 Hz. Zasilanie 9V.

PIC16F84 - Charakterystyka ogólna

Procesory PIC firmy MICROCHIP s

ą

procesorami posiadaj

ą

cymi cechy architektury RISC to

oznacza,

ż

e posiadaj

ą

zminimalizowana list

ę

rozkazów. Zalet

ą

procesorów PIC (PIC16FXX) jest

przede wszystkim:

•

tylko 35 pojedynczych rozkazów łatwych do nauczenia,

•

wszystkie rozkazy wykonywane s

ą

w jednym cyklu (dla zegara taktuj

ą

cego 10 MHz

jeden cykl = 400 ns, a 1 cykl maszynowy jest równy 4 taktom oscylatora) wył

ą

czaj

ą

c

rozkazy skoków, które realizowane s

ą

w dwóch cyklach maszynowych,

•

maksymalna cz

ę

stotliwo

ść

zegara 10 MHz,

•

czternastobitowa długo

ść

słowa rozkazu,

•

o

ś

miobitowa długo

ść

słowa pami

ę

ci danych RAM oraz rejestrów steruj

ą

cych,

•

5 rejestrów specjalnych słu

żą

cych do konfigurowania układu,

•

o

ś

miopoziomowy stos,

•

natychmiastowy (bezpo

ś

redni) i po

ś

redni tryb adresowania,

•

o

ś

miobitowy licznik z o

ś

miobitowym podzielnikiem wst

ę

pnym,

•

cztery

ź

ródła wywołuj

ą

ce przerwania:

- zewn

ę

trzne, po wyst

ą

pieniu odpowiedniego zbocza (rodzaj zbocza definiowany

programowo) na nó

ż

ce RB0/INT procesora,

- wewn

ę

trzne, poprzez zmian

ę

stanu na jednej z nó

ż

ek portu B (porty RB4, RB5, RB6,

RB7),

- wewn

ę

trzne, poprzez przepełnienie TIMER-a,

- wewn

ę

trzne, wywoływane gdy zako

ń

czone zostanie programowanie jednej z komórek

pami

ę

ci danych w EEPROM-ie.

•

ponad 1.000.000 cykli programowania pami

ę

ci danych EEPROM,

•

zachowanie zawarto

ś

ci pami

ę

ci danych EEPROM ponad 40 lat,

•

wykonanie w technologii CMOS,

•

szeroki zakres napiec zasilaj

ą

cych oraz niewielki pobór pr

ą

du (<2mA dla 5V 4MHz,

15mA dla 2V 32kHz oraz poni

ż

ej 1mA w stanie u

ś

pienia).

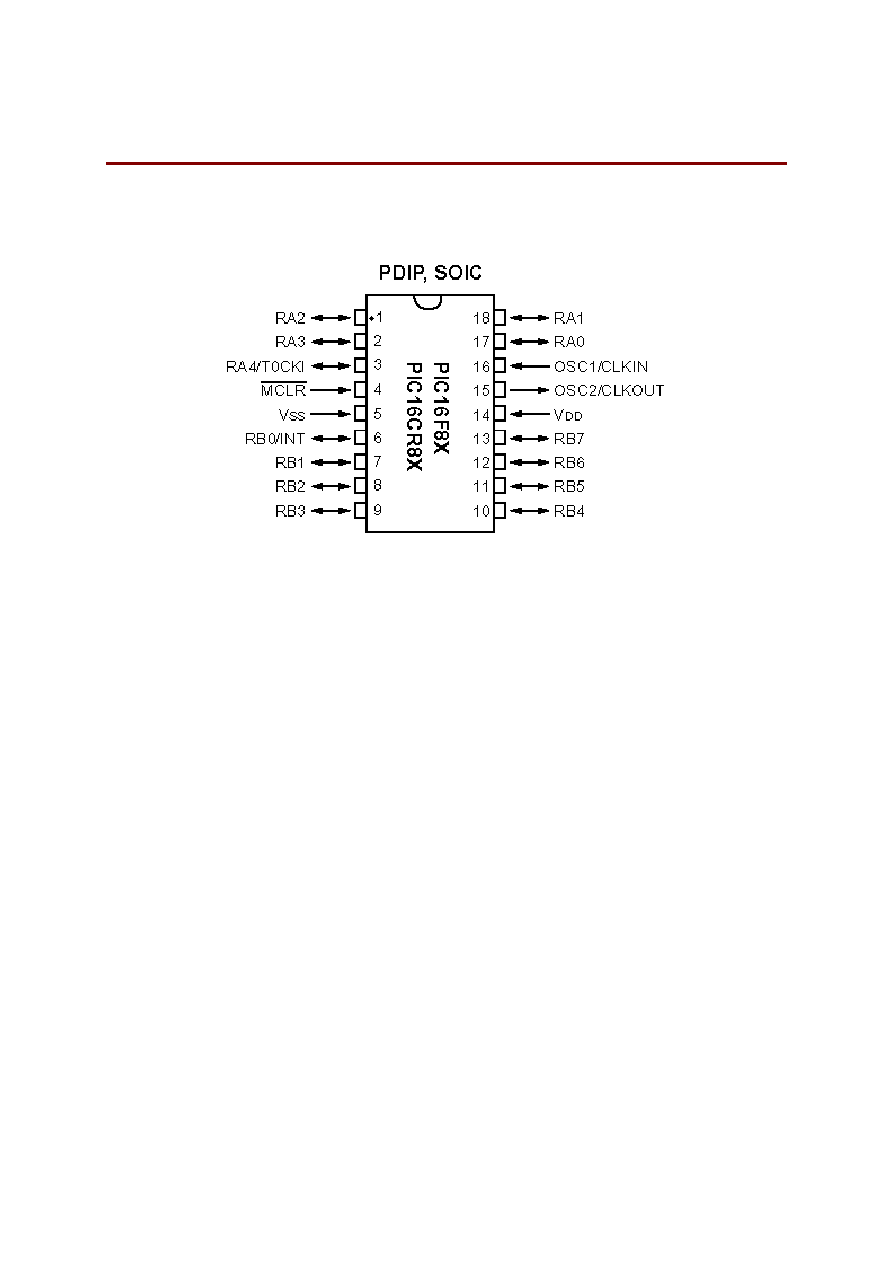

PIC16F84 - Opis wyprowadze

ń

Opis wyprowadze

ń

przedstawia rysunek (obudowa typu PDIP, SOIC). Procesor ma 13

uniwersalnych wyprowadze

ń

wejscia-wyjscia z indywidualna konfiguracja funkcji. Pr

ą

d

wpływaj

ą

cy do układu (sink) 25mA, wypływaj

ą

cy z układu (source) 20 mA.

PIC16F84 - Funkcje dodatkowe

•

POWER-ON RESET czyli zerowanie po wł

ą

czeniu zasilania,

•

POWER-UP TIMER tzn. przedłu

ż

enie sygnału zerowania po wł

ą

czeniu zasilania o 72

ms celem unikni

ę

cia niepo

żą

danych zachowa

ń

układów współpracuj

ą

cych np.

wy

ś

wietlacza LCD ze sterownikiem HD 77480 ,

•

OSCILLATOR START-UP TIMER układ do przedłu

ż

enia zerowania wewn

ę

trznego

procesora o 1024 takty sygnału zegarowego,

•

WATCHDOG TIMER - układ niezale

ż

nego timera wewn

ą

trz procesora, który w

przypadku jego zawieszenia zeruje go (informacja o

ź

ródle wyzerowania jest pami

ę

tana

w odpowiednim rejestrze),

•

CODE-PROTECTION - bit zabezpieczaj

ą

cy program

ź

ródłowy przed odczytem,

mo

ż

liwo

ść

wprowadzenia procesora w sposób programowy w stan u

ś

pienia (ang.

SLEEP MODE), tzn. zawieszenie wszystkich czynno

ś

ci (z zapami

ę

taniem zawarto

ś

ci

rejestrów). Powrót ze stanu SLEEP nast

ę

puje po wyst

ą

pieniu przerwania,

•

mo

ż

liwo

ść

wyboru oscylatora (rezonator kwarcowy 1-10 MHz lub 32 ? 400 kHz,

taktowanie sygnałem zewn

ę

trznym, zewn

ę

trzny oscylator RC),

•

wbudowany system programowania szeregowego, programowanie poprzez dwie

ko

ń

cówki RB6, RB7.

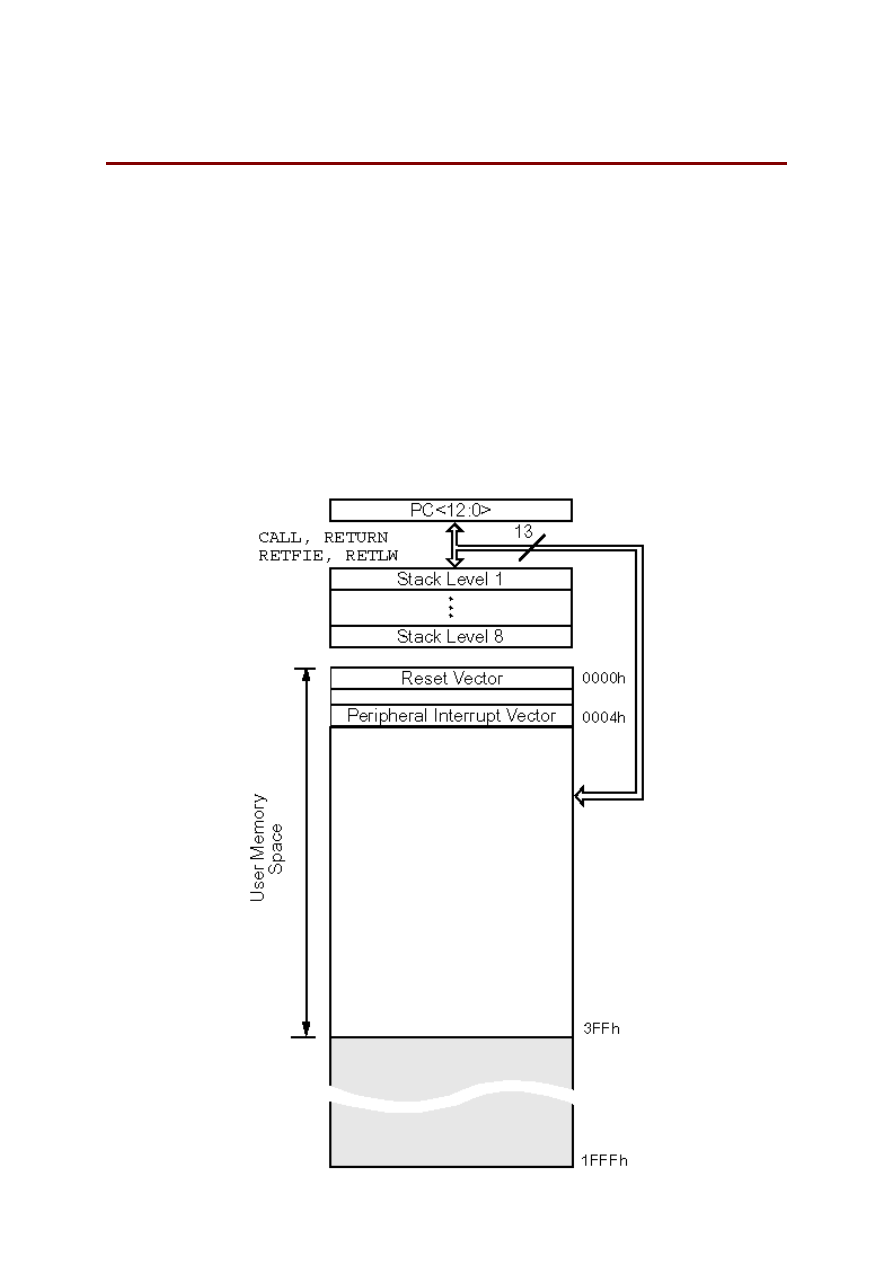

PIC16F84 - Organizacja pami

ę

ci

W procesorze PIC 16F84 znajduj

ą

si

ę

dwa bloki pami

ę

ci :

•

blok pami

ę

ci programu,

•

blok pami

ę

ci danych.

Organizacja pami

ę

ci programu.

Pami

ęć

programu w omawianym procesorze jest pami

ę

ci

ą

typu FLASH, co umo

ż

liwia

wielokrotne zapisywanie tej pami

ę

ci. W praktyce umo

ż

liwia to wykorzystanie jednego

procesora w wielu aplikacjach. PIC 16F84 posiada trzynastobitowy licznik programu co

umo

ż

liwia adresowanie bloku pami

ę

ci o maksymalnym rozmiarze 8KB. Opisywany procesor

posiada 1KB pami

ę

ci programu. Mikroprocesor posiada jeden wektor procedury przerwania

(adres 04h), dlatego rozpoznanie przyczyny przerwania spoczywa na programie w cz

ęś

ci

procedury przerwania.

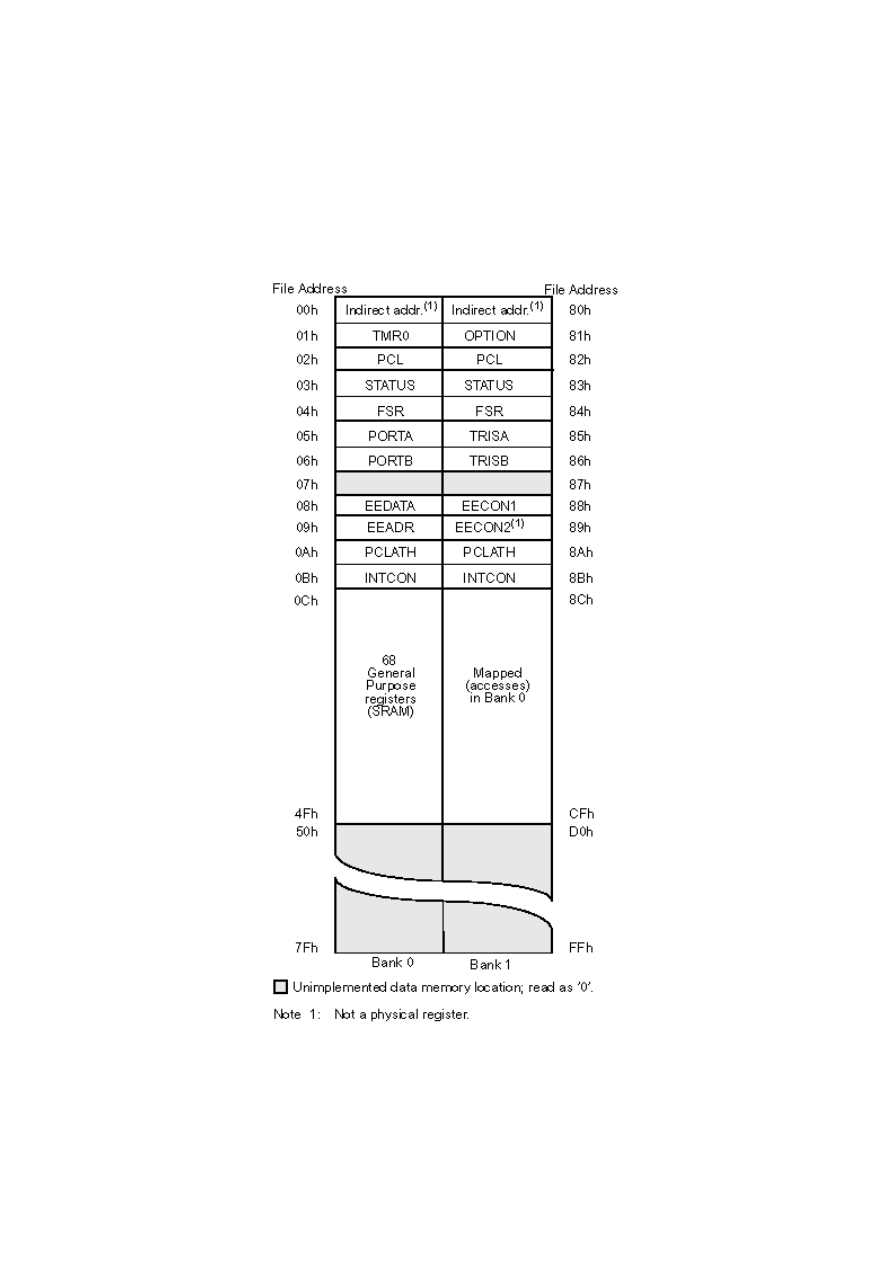

Organizacja pami

ę

ci danych.

Pami

ęć

danych jest podzielona na dwa obszary. Pierwszy obszar to rejestry specjalnego

przeznaczenia ? SFR ( adresy od 00h do 0bh i od 80h do 8bh ), które słu

żą

do sterowania oraz

kontrolowania mikroprocesora, drugi za

ś

to rejestry ogólnego przeznaczenia GPR słu

żą

ce jako

pami

ęć

operacyjna (statyczna) RAM . Pami

ęć

danych jest podzielona na banki w PIC 16F84

znajduj

ą

si

ę

dwa banki, patrz rysunek). Bezpo

ś

redni dost

ę

p do rejestrów jest mo

ż

liwy w

obr

ę

bie tylko jednego banku.

Aby przej

ść

do przeciwnego banku nale

ż

y zmieni

ć

bit IRP w rejestrze STATUS (nie dotyczy to

adresowania po

ś

redniego).

Opis rejestrów steruj

ą

cych.

Rejestry i ich znaczenie:

INDF - Indirect addr. - rejestr pomocniczy przy adresowaniu po

ś

rednim, tj. wpis (odczyt) do (z)

tego rejestru jest równoznaczne z wpisem do komórki pami

ę

ci o adresie umieszczonym w

rejestrze zwanym FSR,

OPTION - rejestr konfiguracji,

TMR0 - licznik,

PCL - młodsza cze

ść

( młodszy bajt ) licznika programu,

STATUS - rejestr flag ( znaczników ),

FSR - rejestr w którym umieszcza si

ę

adres do adresowania po

ś

redniego,

PORTA - rejestr odzwierciedlaj

ą

cy stan ko

ń

cówek portu A,

PORTB - rejestr odzwierciedlaj

ą

cy stan ko

ń

cówek portu B,

TRISA - konfiguracja kierunku portu A,

TRISB - konfiguracja kierunku portu B,

EEDATA, EECON1, EEADR, EECON2 - rejestry słu

żą

ce do obsługi pami

ę

ci EEPROM wewn

ą

trz

procesora,.

PCLATH - starsza cze

ść

( tj. piec bitów ) licznika programu,

INTCON - konfiguracja przerwa

ń

.

Ciekawym mo

ż

e by

ć

fakt, i

ż

rejestr PCL reprezentuje sob

ą

mniej znacz

ą

ca cze

ść

licznika

programu PC i dozwolone s

ą

manipulacje na tym rejestrze. Porty wejscia-wyjscia dost

ę

pne s

ą

poprzez rejestry PORTA oraz PORTB, przy czym kierunek poszczególnych linii ustala si

ę

wykorzystuj

ą

c par

ę

rejestrów TRISA oraz TRISB. Rejestr TMR0 odzwierciedla zawarto

ść

licznika i dozwolone s

ą

na nim operacje arytmetyczno-logiczne. W rejestrze STATUS oprócz

wspomnianych powy

ż

ej bitów przeł

ą

czania banków pami

ę

ci znajduj

ą

si

ę

bity przedstawiaj

ą

ce

stan jednostki arytmetyczno-logicznej (odpowiednik powszechnie znanego rejestru

znaczników) oraz bity informuj

ą

ce o przyczynie wyzerowania mikrokontrolera wł

ą

czenie

zasilania, zadziałanie układu WatchDog-a). Rejestr OPTION odpowiedzialny jest za konfiguracje

peryferii jednostki centralnej natomiast rejestr INTCON konfiguruje prace systemu przerwa

ń

.

Rejestry EEDATA, EEADR, EECON1, EECON2 umo

ż

liwiaj

ą

obsług

ę

wewn

ę

trznej pami

ę

ci typu

EEPROM. Dalej znajduje si

ę

68 rejestrów ogólnego przeznaczenia (odpowiednik pami

ę

ci RAM),

w których przechowywane s

ą

dane programu. Najcz

ęś

ciej u

ż

ywane rejestry s

ą

zaimplementowane w obu bankach jednocze

ś

nie by unikn

ąć

kłopotliwego przeł

ą

czania

banków. Interesuj

ą

cy mo

ż

e by

ć

fakt, i

ż

producent mikrokontrolera zapewnia tylko programowa

zgodno

ść

ró

ż

nych typów mikrokontrolerów w ramach jednej rodziny. Program napisany na

mikrokontroler okre

ś

lonego typu musi by

ć

ponownie skompilowany na mikrokontroler innego

typu by mógł pracowa

ć

poprawnie, gdy

ż

nie jest zapewniona sprz

ę

towa zgodno

ść

adresów

rejestrów steruj

ą

cych.

PIC16F84 - Znaczenie bitów w rejestrach

Rejestr STATUS (adres 03h, 83h)

Rejestr statusu zawiera znaczniki odzwierciedlaj

ą

ce:

- wynik ostatnio wykonanej operacji arytmetycznej,

- aktualny stan procesora tzn. informacje o

ź

ródle ewentualnego wyzerowania procesora oraz

informacje o aktywnym banku. Rejestr ten wykorzystywany jest przy sprawdzaniu wyniku

ostatnio wykonanej operacji arytmetyczno-logicznej.

Znaczenie poszczególnych bitów :

bit 7 IRP : Bit wybieraj

ą

cy bank ( u

ż

ywany do adresowania po

ś

redniego ):

0 - Bank 0, 1 (adres 00h - FFh),

1 - Bank 2, 3 (adres 100h - 1FFh),

Bit IRP nie jest wykorzystywany w procesorze PIC 16F8X. Zaleca si

ę

zerowanie tego bitu w

programie w celu zachowania kompatybilno

ś

ci tego programu z przyszłymi wersjami

procesorów .

bit 6-5 RP1:RP0 : Bity do selekcji banków (u

ż

ywane do adresowania bezpo

ś

redniego):

0,0 - Bank 0 (adres 00h - 7Fh),

0,1 - Bank 1 (adres 80h - FFh),

1,0 - Bank 2 (adres 100h - 17Fh),

1,1 - Bank 3 (adres 180h - 1FFh).

Ka

ż

dy bank jest 128-bajtowy . W PIC 16F8X wykorzystywany jest tylko bit RP0.

bit 4 TO :"Time out bit", bit informuj

ą

cy o zadziałaniu WatchDog-a:

1 - po wł

ą

czeniu zasilania , po instrukcji CLRWDT (zerowanie licznika WatchDog-a) oraz po

instrukcji SLEEP,

0 - po zadziałaniu WatchDog-a (po przepełnieniu licznika WatchDog-a),

bit 3 PD: "Power down bit" - Bit informuj

ą

cy o przyczynie wyzerowania procesora:

1 - po wł

ą

czeniu zasilania, po instrukcji CLRWDT (zerowanie licznika WatchDog-a),

0 - po wykonaniu instrukcji SLEEP,

bit 2 Z : Bit zera:

1 - je

ż

eli wynikiem ostatniej operacji arytmetycznej lub logicznej jest zero,

0 - je

ż

eli wynik jest ró

ż

ny od zera,

bit 1 DC : Znacznik przeniesienia pomocniczego (CARRY) lub po

ż

yczki (BORROW), do którego

w czasie operacji dodawania (ADDWF i ADDLW) jest wpisywane przeniesienie z bitu 3 lub

po

ż

yczka z bitu 4 (wykorzystywany przy korekcji dziesi

ę

tnej, dla BORROW obowi

ą

zuje logika

odwrotna):

1 - je

ż

eli wyst

ą

piło przeniesienie z bitu 3-go na 4-ty (z młodszej do starszej tetrady),

0 - przy braku przeniesienia,

bit 0 C: Znacznik przeniesienia (CARRY) oraz po

ż

yczki (BORROW), do którego wpisuje si

ę

przeniesienie z najbardziej znacz

ą

cego bitu, ustawiany w wyniku wykonania operacji

arytmetycznych oraz przesuni

ęć

a tak

ż

e rotacji:

1 - je

ż

eli nast

ą

piło przeniesienie z najbardziej znacz

ą

cego bitu aktualnego wyniku

0 - przy braku przeniesienia

Rejestr OPTION (adres 81h)

Znaczenie poszczególnych bitów :

Bit 7 RBPU: Bit polaryzuj

ą

cy wyprowadzenia portu B do potencjału +Vcc przez opory (tylko

przy konfiguracji portu jako wej

ś

ciowe):

1 - praca portu PORTB bez polaryzacji,

0 - praca portu PORTB z polaryzacja,

Bit 6 INTEDG: Wybór rodzaju zbocza jakie nale

ż

y poda

ć

na RB0/INT aby wywoła

ć

przerwanie:

1 - przerwanie po zboczu narastaj

ą

cym na pinie RB0/INT,

0 - przerwanie po zboczu opadaj

ą

cym na pinie RB0/INT,

Bit 5 T0CS: Wybór

ź

ródła sygnału zegarowego licznika TMR0:

1 - podł

ą

czenie do sygnału taktuj

ą

cego zewn

ę

trznego przez ko

ń

cówk

ę

RA4/T0CKI,

0 - podł

ą

czenie do wewn

ę

trznego sygnału taktuj

ą

cego,

Bit 4 T0SE: Wybór zbocza jakie musi wyst

ą

pi

ć

na ko

ń

cówce RA4/T0CKI aby zwi

ę

kszy

ć

licznik

TMR0 o jeden:

1 - zwi

ę

kszenie TMR0 o jeden po przej

ś

ciu ze stanu wysokiego na niski,

0 - zwi

ę

kszenie TMR0 o jeden po przej

ś

ciu ze stanu niskiego na wysoki,

Bit 3 PSA : Bit wyboru przeznaczenia podzielnika:

1 - podzielnik podł

ą

czony do WatchDog-a,

0 - podzielnik podł

ą

czony do licznika TMR0,

Bit 2-0 PS2,PS1,PS0: Ustawienie podziału podzielnika (ang. prescaler) dla licznika TMR0 i

WatchDog-a (WDT ):

Rejestr INTCON (adres 0Bh, 8Bh)

Rejestr INTCON słu

ż

y do konfigurowania systemu przerwa

ń

.

Bit 7 GIE: Wł

ą

czenie lub wył

ą

czenie wszystkich przerwa

ń

(bit GIE posiada najwy

ż

szy priorytet

):

1 - wł

ą

czenie wszystkich nie zamaskowanych przerwa

ń

,

0 - wył

ą

czenie wszystkich przerwa

ń

,

Bit 6 EEIE: Uaktywnienie przerwania wywoływanego po zako

ń

czeniu zapisu danej do pami

ę

ci

EEPROM wewn

ą

trz procesora:

1 - po zako

ń

czeniu zapisu zostanie wywołane przerwanie,

0 - po zako

ń

czeniu zapisu nie zostanie wywołane przerwanie,

Bit 5 T0IE: Bit uaktywniaj

ą

cy wywołanie przerwania po przepełnieniu licznika TMR0 ,

1 - je

ż

eli chcemy aby przerwanie zostało wywoływane po przepełnieniu TMR0 ,

0 - je

ż

eli nie chcemy aby przerwanie zostało wywoływane po przepełnieniu TMR0 ,

Bit 4 INTE: Uaktywnienie przerwania zewn

ę

trznego (z ko

ń

cówki RB0/INT ):

1 - przerwanie b

ę

dzie wywoływane,

0 - przerwanie nie b

ę

dzie wywoływane,

Bit 3 RBIE: Wł

ą

czenie przerwania pochodz

ą

cego od zmiany stanu na porcie PORTB :

1 - przerwanie b

ę

dzie wywoływane,

0 - przerwanie nie b

ę

dzie wywoływane,

Bit 2 T0IF: Przepełnienie licznika TMR0 powoduje jego ustawienie co jest równoznaczne z

natychmiastowym wywołaniem przerwania. Je

ż

eli programowo ustawimy bit T0IF.(bit T0IF =1)

to tak

ż

e zostanie wywołane przerwanie (od razu po rozkazie BSF INTCON , T0IF )

1 - nast

ą

piło przepełnienie (bit ten musi by

ć

zerowany programowo)

0 - nie nast

ą

piło przepełnienie,

Bit 1 INTF : Bit informuj

ą

cy o tym, ze ostatnie przerwanie zostało wywołane zboczem na

ko

ń

cówce RB0/INT:

1 - nast

ą

piło przerwanie pochodz

ą

ce od RB0/INT,

0 - nie nast

ą

piło przerwanie pochodz

ą

ce od RB0/INT,

Bit 0 RBIF: Bit informuj

ą

cy o tym, ze ostatnie przerwanie zostało wywołane zmiana stanu

na jednej z ko

ń

cówek portu B (RB7 do RB4):

1 - je

ż

eli nast

ą

piła zmiana stanu na której

ś

z ko

ń

cówek RB7:RB4 (bit musi by

ć

kasowany

programowo),

0 - je

ż

eli nie było zmiany stanów,

PIC16F84 - Porty wej

ś

cia-wyj

ś

cia

Dzi

ę

ki dobrym parametrom tranzystorów z których zbudowano wyj

ś

cia portów do koncówek

tych mo

ż

na podł

ą

czy

ć

bezpo

ś

rednio diody LED co jest ogromna zaleta tych procesorów. Porty

te mog

ą

pracowa

ć

zarówno jako układy wyj

ś

ciowe jak i wej

ś

ciowe. Konfiguracja kierunku

portu mo

ż

liwa jest w sposób programowy poprzez rejestr TRISA/B.

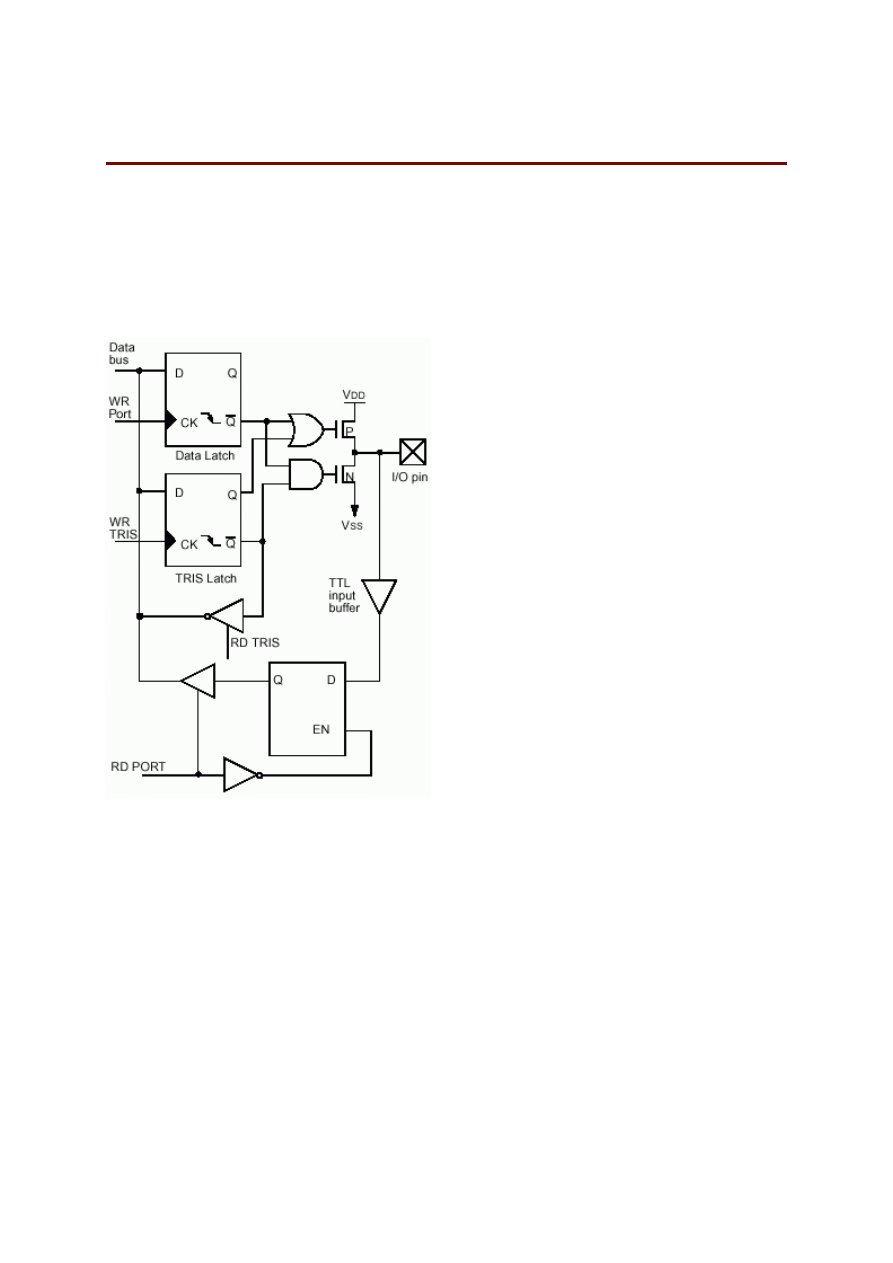

Port A

Struktur

ę

ko

ń

cówek RA0, RA1, RA2, RA3 portu PORTA przedstawia rys.4.

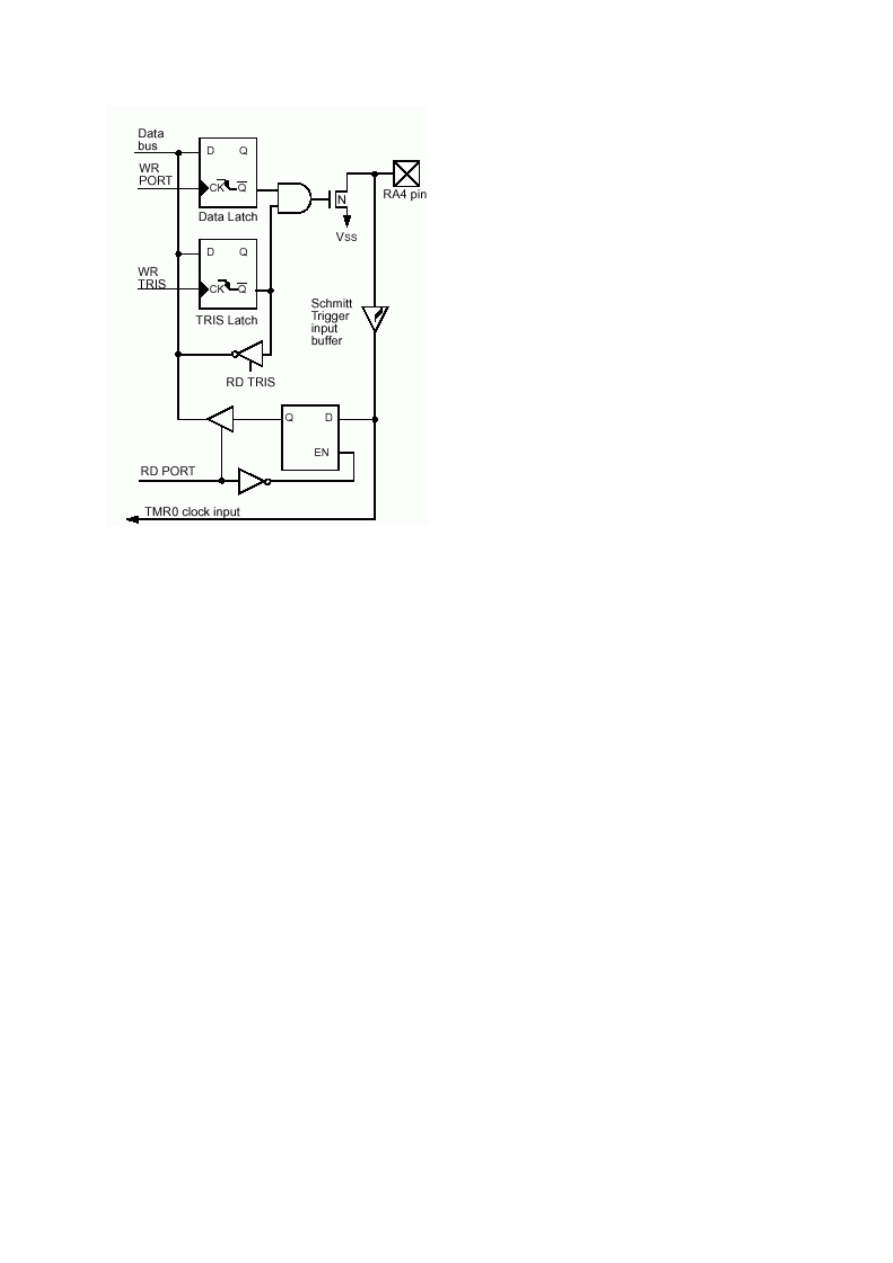

Struktur

ę

portu dla ko

ń

cówki RA4 przedstawia rys.5. Jest to wyprowadzenie typu otwarty dren,

z mo

ż

liwo

ś

ci

ą

wymuszenia na nim przez procesor stanu niskiego. Na wej

ś

ciu układ

wyposa

ż

ony jest w bramk

ę

Schmit'a co pozwala na wykorzystanie portu jako wej

ś

cie dla

sygnału taktuj

ą

cego licznik TMR0.

Ustawienie bitu TRISx (TRISx = 1) powoduje zdefiniowanie odpowiedniego wyprowadzenia

(RAx) jako wej

ś

cie, wyzerowanie jako wyj

ś

cie.

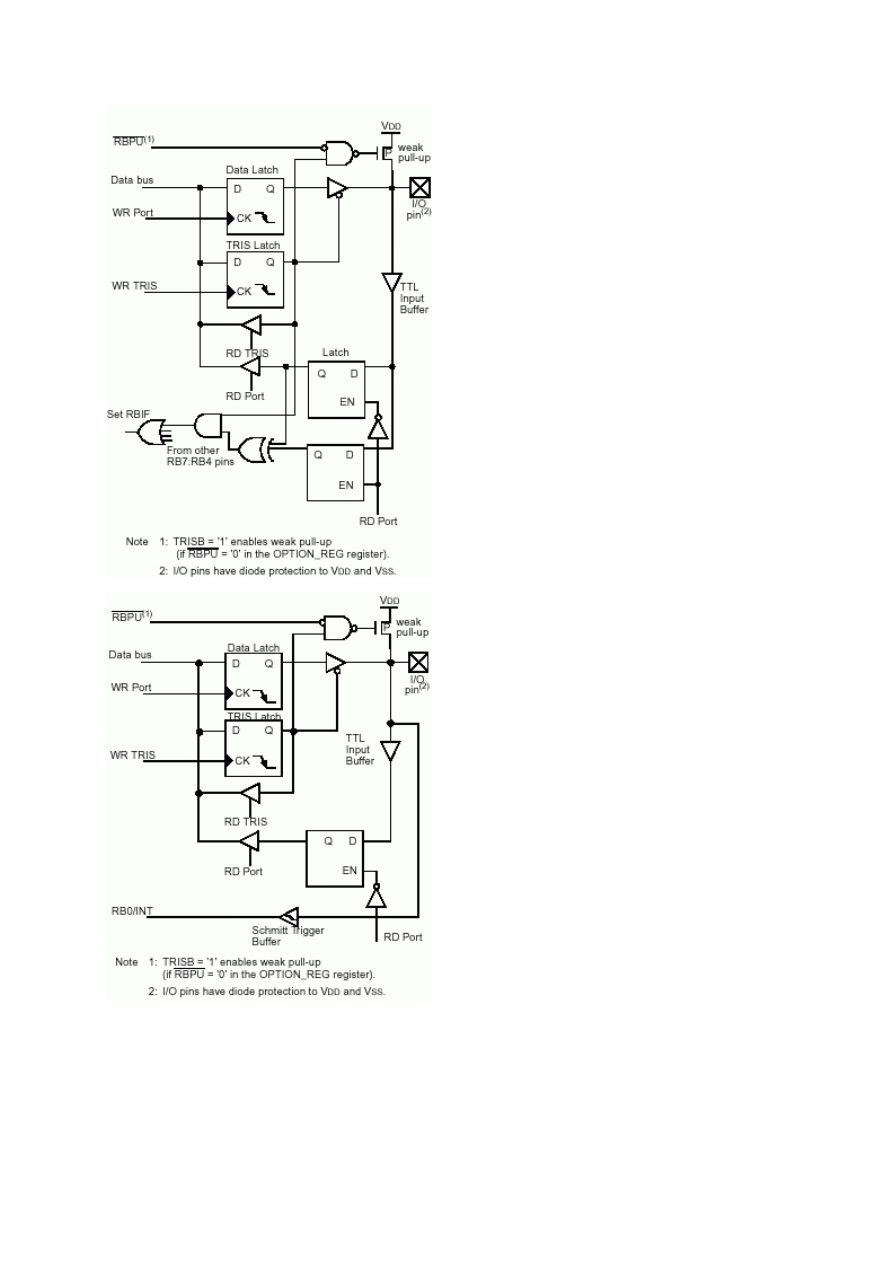

Port B

Port ten jest 8-bitowym dwukierunkowym portem równoległym z mo

ż

liwo

ś

ci

ą

wewn

ę

trznego

podci

ą

gni

ę

cia tych ko

ń

cówek do +Vcc poprzez tranzystor o du

ż

ej impedancji zł

ą

cza zródlo-

dren w stanie przewodzenia. Struktur

ę

ko

ń

cówek RB4, RB5, RB6, RB7 przedstawia rys.6.

Zmiana stanu na której

ś

z nó

ż

ek RB4, RB5, RB6, RB7 mo

ż

e by

ć

ź

ródłem wywołuj

ą

cym

przerwanie. Struktur

ę

ko

ń

cówek RB0-RB3 przedstawia rys.7.

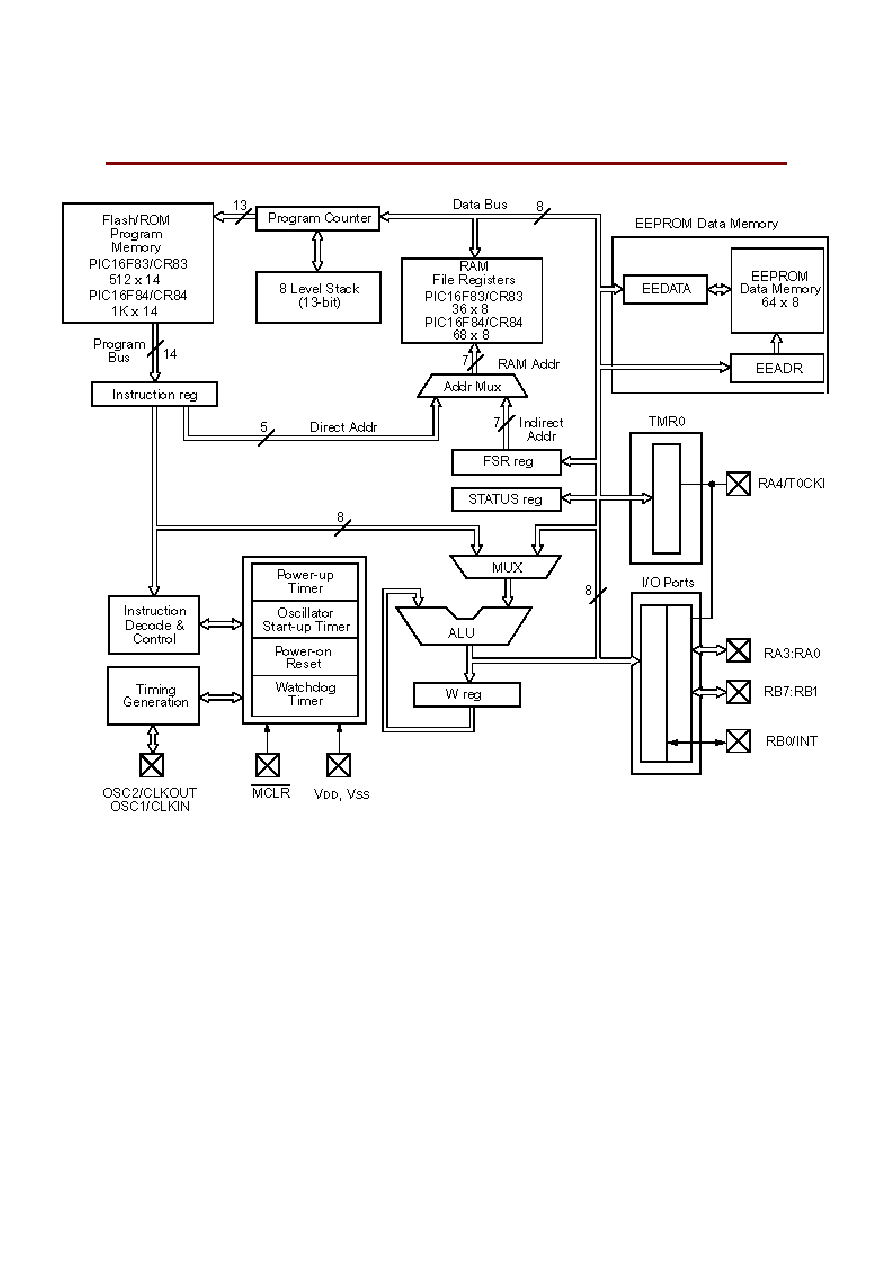

PIC16F84 - Architektura procesora

Procesor zbudowany jest w oparciu o harwardzka architektur

ę

, która w przeciwie

ń

stwie do

tradycyjnej (von Neumann'a) posiada rozdzielona magistrale programu i danych. Dzi

ę

ki temu

pami

ęć

danych została zorganizowana jako słowa 8-bitowe, natomiast pami

ęć

programu

posiada 14-bitow

ą

długo

ść

słowa. Zwi

ę

kszenie długo

ś

ci słowa pami

ę

ci programu umo

ż

liwiło,

przy jednoczesnym zmniejszeniu liczby instrukcji procesora, zmniejszenie czasu wykonywania

wi

ę

kszo

ś

ci instrukcji do jednego cyklu maszynowego gdy

ż

wszystkie instrukcje mieszcz

ą

si

ę

w jednym słowie pami

ę

ci i nie jest potrzebny dodatkowy cykl odczytu celem pobrania

argumentów rozkazu. Dalsze skrócenie czasu wykonywania instrukcji przyniósł zastosowany w

procesorze flow/pipelining to znaczy podczas cyklu wykonywania jednej instrukcji nast

ę

puje

pobranie kodu nast

ę

pnej instrukcji. Uzyskano tu dwukrotny wzrost pr

ę

dko

ś

ci pracy procesora.

Metoda ta nie sprawdza si

ę

podczas wykonywania instrukcji steruj

ą

cych programem typu

CALL lub GOTO, gdy

ż

nie jest wtedy pobierany kod nast

ę

pnej instrukcji. Zastosowanie w

procesorze wspomnianych mechanizmów doprowadziło do 4-taktowego cyklu maszynowego.

Na uwag

ę

zasługuje fakt, i

ż

w procesorze nie wyst

ę

puj

ą

tradycyjne instrukcje warunkowe typu

skocz gdy..., które nie zmie

ś

ciły by si

ę

w jednym słowie pami

ę

ci programu. W ich miejsce

zastosowano grup

ę

instrukcji typu testuj bit i nie wykonaj nast

ę

pnej instrukcji gdy.... List

ę

rozkazów uzupełniaj

ą

instrukcje p

ę

tli iteracyjnych typu zmniejsz-zwieksz komórk

ę

pami

ę

ci i

omi

ń

nast

ę

pn

ą

instrukcje gdy komórka pami

ę

ci jest równa zero.

Procesor posiada standardowa jednostk

ę

arytmetyczno-logiczna (ALU), która potrafi

wykonywa

ć

podstawowe operacje arytmetyczne (dodawanie, odejmowanie), logiczne (i, lub,

alternatyw

ę

, przesuni

ę

cia bitowe). Z jednostka arytmetyczno-logiczna zwi

ą

zany jest rejestr W

(ang. working register), w którym to pami

ę

tany jest jeden z argumentów operacji 2-

argumentowych. Nie nale

ż

y jednak uto

ż

samia

ć

tego rejestru ze znanym powszechnie rejestrem

akumulatora w procesorach konwencjonalnych, gdy

ż

pami

ę

tany jest w nim 2-gi argument

operacji. Rzadko spotykana cecha procesora jest to, ze wynik operacji mo

ż

e by

ć

zapami

ę

tany

w rejestrze W b

ą

d

ź

komórce pami

ę

ci (rejestrze) bior

ą

cej udział w operacji.

Podobnie jak w procesorach serii MCS51, wszystkie rejestry procesora (w tym rejestr

znaczników) le

ż

a w przestrzeni adresowej pami

ę

ci RAM lub inaczej w przestrzeni file registers.

Procesor posiada 8-poziomowy sprz

ę

towy stos dla instrukcji typu CALL oraz wykorzystywany

w systemie przerwa

ń

mikrokontrolera. Interesuj

ą

cym mo

ż

e tak

ż

e by

ć

fakt, ze procesor nie

posiada tradycyjnego trybu adresowania po

ś

redniego. W przestrzeni adresowej rejestrów

zaimplementowano specjalny, nieistniej

ą

cy fizycznie rejestr (INDF), do którego wpis lub odczyt

powoduje fizyczny wpis lub odczyt komórki pami

ę

ci o adresie zawartym w specjalnym

rejestrze FSR. Poniewa

ż

rejestry te s

ą

8-bitowe, a komórek pami

ę

ci mo

ż

e by

ć

wi

ę

cej ni

ż

256,

wiec ewentualne brakuj

ą

ce bity adresu pobierane s

ą

z innego rejestru (STATUS- bit IRP).

Ilustruje to rys.10.

Z inna sytuacja mamy do czynienia w przypadku adresowania bezpo

ś

redniego. Pami

ęć

danych

(rejestry ogólnego i specjalnego przeznaczenia) podzielona jest na 128 bajtowe banki, gdy

ż

w

kodzie operacji mikrokontrolera przewidziano tylko 7-bitów na adres bezpo

ś

redni. Dodatkowe,

brakuj

ą

ce bity adresu s

ą

uzupełnione podobnie jak w przypadku adresowania po

ś

redniego

bitami zawartymi w rejestrze STATUS (bity IRP1,IRP0).

Lista rozkazów mikrokontrolerów tej rodziny nie jest zbyt du

ż

a, ale została dobrana w taki

sposób, aby mo

ż

liwie najbardziej ułatwi

ć

pisanie prostych aplikacji dla celów sterowania. Nie

brakuje tu rozkazów operuj

ą

cych na pojedynczych bitach, oraz rozkazów p

ę

tli iteracyjnych

b

ę

d

ą

cych podstawa implementacji algorytmów sterowania.

Wyszukiwarka

Podobne podstrony:

BRAMKI LOGICZNE (1) id 92815 Nieznany

cw5 bramki logiczne id 123545 Nieznany

bramki logiczne id 92813 Nieznany (2)

BRAMKI LOGICZNE2 id 92822 Nieznany

EEPodstawowe bramki logiczne id Nieznany

kmd prawa logiczne id 236768 Nieznany

BLEDY LOGICZNE id 75111 Nieznany (2)

podzial logiczny id 369313 Nieznany

kmd prawa logiczne id 236768 Nieznany

Lab 8 (Bramki logiczne)id 10528

analizator stanow logicznych id Nieznany (2)

logicz mysl id 271908 Nieznany

Abolicja podatkowa id 50334 Nieznany (2)

4 LIDER MENEDZER id 37733 Nieznany (2)

katechezy MB id 233498 Nieznany

więcej podobnych podstron