AiR gr 5 sekcja 4 Gliwice 2003-05-10

Laboratorium podstaw elektroniki

(Bramki Logiczne)

Grupa 5 Sekcja 4:

Kamil Sokołowski

Paweł Puchałka

Krzysztof Brauner

Tomasz Ziaja

Wstęp

Przeprowadziliśmy badania Bramki logicznej NAND, zdjęliśmy charakterystyki wejściowe, przejściowe i wyjściowe dla stanu niskiego i wysokiego. Przeprowadziliśmy następujące pomiary.

Pomiary

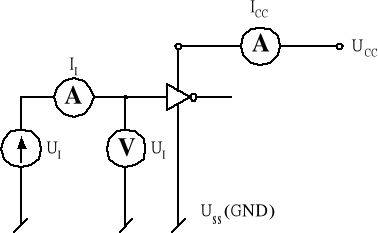

Charakterystyki Wejściową I1 = f(U1), Przejściową U0 = f(UI) oraz Poboru prądu ICC = f(UI) bramki NAND badaliśmy według schematu pomiarowego:

Charakterystyka Wyjściowa UOL = f(IOL) w stanie niskim:

Charakterystyka Wyjściowa UOH = f(IOH) w stanie wysokim:

Wykresy

(w załączniku)

Wnioski

Charakterystyka Wejściowa, Przejściowa oraz Poboru Prądu

W chwili zmiany stanu bramki zwiększa się pobór prądu. Pomiary umieściliśmy na wykresie zbiorczym oraz osobno. By dokładniej uwidocznić charakterystyki odrzuciliśmy niektóre pomiary (krańcowe). Mieliśmy nieznaczne kłopoty z odczytaniem wartości prądu ICC

Charakterystyki Wyjściowe

Nie różnią się zbytnio od umieszczonych w skrypcie charakterystyk „teoretycznych” zmianę obciążenia wyjścia bramki wymuszaliśmy niejako zmianą prądu wyjściowego.

Wyszukiwarka

Podobne podstrony:

Bramki Logiczne

EEKsem3 bramki logiczne w7

bramki logiczne, Szkoła, Systemy Operacyjnie i sieci komputerowe, utk, semestr I

Bramki logiczne

10 bramki logiczne, ZSS

Bramki logiczne, Księgozbiór, Studia, Elektronika i Elektrotechnika

BRAMKI LOGICZNE (1) id 92815 Nieznany

Bramki logiczne

Bramki logiczne 3 id 92812 Nieznany (2)

EEPodstawowe bramki logiczne

09 Bramki logiczne

instrukcje do sprawozdań, cw5 bramki logiczne, Laboratorium

cw5 bramki logiczne id 123545 Nieznany

01 Podstawowe bramki logiczne instrukcja poprawiona

Bramki logiczne

więcej podobnych podstron