Rozdział 5.

Pamięci dynamiczne

Pamięci dynamiczne RAM pozwalają na uzyskanie większych pojemności niż pamięci statyczne, są też od nich kilkakrotnie tańsze. Niestety nie ma róży bez kolców —[Author ID1: at Sat Dec 15 17:51:00 2001

]-[Author ID1: at Sat Dec 15 17:51:00 2001

] wymagają one bardziej skomplikowanych układów sterujących. Układy te muszą przede wszystkim zapewnić odświeżanie pamięci, bez którego pamięć traci zawartość pomimo tego, że jest ciągle zasilana. Każdy wiersz pamięci powinien być odświeżony przynajmniej raz na 2 - [Author ID1: at Sat Dec 15 17:54:00 2001

]-[Author ID1: at Sat Dec 15 17:54:00 2001

]8 ms. Innym powodem komplikacji układów sterujących jest konieczność podawania adresu w dwóch częściach. Pamięci dynamiczne mają bowiem zwykle dwukrotnie mniej wejść adresowych, niż wynikałoby to z ich organizacji. Takie podejście ma jednak na celu zmniejszenie ogólnej liczby wyprowadzeń w układzie, a w konsekwencji —[Author ID1: at Sat Dec 15 18:15:00 2001

]-[Author ID1: at Sat Dec 15 18:15:00 2001

] skrócenie połączeń i zmniejszenie powierzchni zajmowanej przez moduł pamięci. Należy podkreślić, że w układach o pojemności rzędu 1M słów pozwala to na usunięcie z każdego układu aż 10 wyprowadzeń (1M [Author ID1: at Sat Dec 15 18:16:00 2001

]= [Author ID1: at Sat Dec 15 18:16:00 2001

]220). Także czterokrotny wzrost pojemności wymaga dodania tylko jednego wyprowadzenia, podczas gdy w pozostałych pamięciach —[Author ID1: at Sat Dec 15 18:16:00 2001

]-[Author ID1: at Sat Dec 15 18:16:00 2001

] dwóch.

Przegląd układów pamięci DRAM

Najczęściej produkowane pamięci dynamiczne mają organizację 1- lub 4-bitową. Podobnie jak pamięci statyczne, układy pamięci dynamicznych o organizacji 1-bitowej mają rozdzielone wejście i wyjście danych, natomiast pamięci o organizacji 4-bitowej —[Author ID1: at Sat Dec 15 18:17:00 2001

]-[Author ID1: at Sat Dec 15 18:17:00 2001

] linie dwukierunkowe. Wszystkie układy mają wejścia sterujące ![]()

, ![]()

i ![]()

, a pamięci o organizacji 4-bitowej —[Author ID1: at Sat Dec 15 18:17:00 2001

]-[Author ID1: at Sat Dec 15 18:17:00 2001

] dodatkowo wejście ![]()

. Wszystkie wejścia[Author ID1: at Sat Dec 15 18:18:00 2001

]e[Author ID1: at Sat Dec 15 18:18:00 2001

] są aktywne w [Author ID1: at Sat Dec 15 18:18:00 2001

]stani[Author ID1: at Sat Dec 15 18:18:00 2001

]em[Author ID1: at Sat Dec 15 18:18:00 2001

] niskim. Znaczenie wejść ![]()

i ![]()

jest takie samo[Author ID1: at Sat Dec 15 18:18:00 2001

]e[Author ID1: at Sat Dec 15 18:18:00 2001

] jak w pamięciach statycznych —[Author ID1: at Sat Dec 15 18:19:00 2001

]-[Author ID1: at Sat Dec 15 18:19:00 2001

] [Author ID1: at Sat Dec 15 18:21:00 2001

] [Author ID1: at Sat Dec 15 18:19:00 2001

] [Author ID1: at Sat Dec 15 18:21:00 2001

]![]()

umożliwia odczyt z pamięci, a ![]()

—[Author ID1: at Sat Dec 15 18:20:00 2001

]-[Author ID1: at Sat Dec 15 18:20:00 2001

] zapis. Jeżeli brak sygnału ![]()

, to odczyt jest możliwy, gdy ![]()

jest nieaktywne.

Pewne zdziwienie może budzić brak wejścia typu ![]()

w pamięciach dynamicznych. Jego funkcję pełnią sygnały ![]()

i ![]()

. Służą one także do wskazywania, która część adresu znajduje się na wejściach adresowych pamięci. Sygnał ![]()

(ang. Row Address Strobe) to

-->

strob[Author:EK]

[Author ID1: at Sun Dec 16 23:46:00 2001

] adresu wiersza (mniej znaczącej części adresu), a sygnał[Author ID1: at Sat Dec 15 18:43:00 2001

] [Author ID1: at Sat Dec 15 18:44:00 2001

]![]()

(ang. Column Address Strobe) —[Author ID1: at Sat Dec 15 18:38:00 2001

]-[Author ID1: at Sat Dec 15 18:38:00 2001

]

-->

strob [Author:EK]

[Author ID1: at Sun Dec 16 23:47:00 2001

]adresu kolumny (części bardziej znaczącej). Podczas cyklu dostępu do pamięci zazwyczaj pierwszy podaje się adres wiersza i sygnał ![]()

, następnie adres kolumny i sygnał ![]()

(![]()

może być aktywny, gdy ![]()

[Author ID1: at Sat Dec 15 18:44:00 2001

]= [Author ID1: at Sat Dec 15 18:44:00 2001

]„0”, gdyż układ zapamiętuje adresy w czasie[Author ID1: at Sat Dec 15 18:44:00 2001

] trwania zbocza opadającego tych sygnałów). Tak zaadresowany układ pamięci uaktywnia się w celu dokończenia operacji (odczytu lub zapisu). Można więc rzeczywiście powiedzieć, że sygnały ![]()

i ![]()

[Author ID1: at Sat Dec 15 18:45:00 2001

]zastępują sygnał ![]()

.

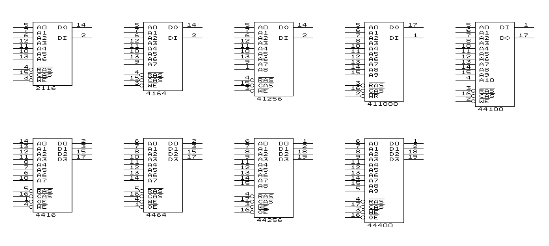

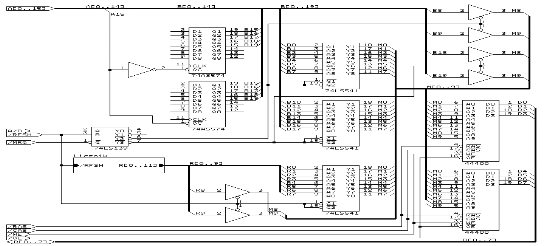

Rysunek 5.1 [Author ID1: at Sat Dec 15 18:45:00 2001

][Author ID1: at Sat Dec 15 18:45:00 2001

][Author ID1: at Sat Dec 15 18:45:00 2001

][Author ID1: at Sat Dec 15 18:45:00 2001

][Author ID1: at Sat Dec 15 18:45:00 2001

][Author ID1: at Sat Dec 15 18:45:00 2001

]Rysunek [Author ID1: at Sat Dec 15 18:45:00 2001

]1[Author ID1: at Sat Dec 15 18:45:00 2001

][Author ID1: at Sat Dec 15 18:45:00 2001

] [Author ID1: at Sat Dec 15 18:45:00 2001

]przedstawia wyprowadzenia niektórych układów pamięci dynamicznych o organizacji 1- i 4-bitowej i pojemnościach od 16K słów do 1M słów.

Rysunek 5.1. [Author ID1: at Sat Dec 15 18:46:00 2001

][Author ID1: at Sat Dec 15 18:46:00 2001

][Author ID1: at Sat Dec 15 18:46:00 2001

][Author ID1: at Sat Dec 15 18:46:00 2001

]1[Author ID1: at Sat Dec 15 18:46:00 2001

][Author ID1: at Sat Dec 15 18:46:00 2001

]. [Author ID1: at Sat Dec 15 18:46:00 2001

]Wyprowadzenia pamięci dynamicznych RAM

Przykłady

Przykład 1.[Author ID1: at Sat Dec 15 18:47:00 2001 ]

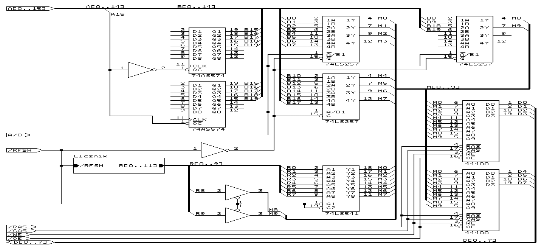

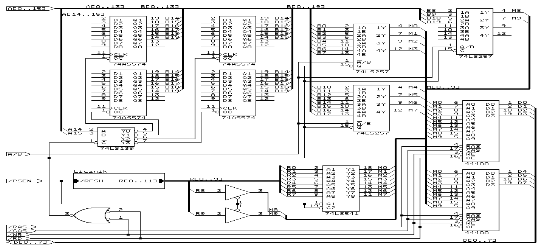

Zaprojektować moduł pamięci dynamicznej o pojemności 64 KB dla mikroprocesora Z-80. W zadaniu należy w[Author ID1: at Sun Dec 16 23:30:00 2001 ]ykorzystać układy pamięci o organizacji 64K [Author ID1: at Sat Dec 15 18:47:00 2001 ]× [Author ID1: at Sat Dec 15 18:47:00 2001 ]1. Do odświeżania należy [Author ID1: at Sun Dec 16 23:30:00 2001 ]wykorzystać wewnętrzny licznik mikroprocesora.

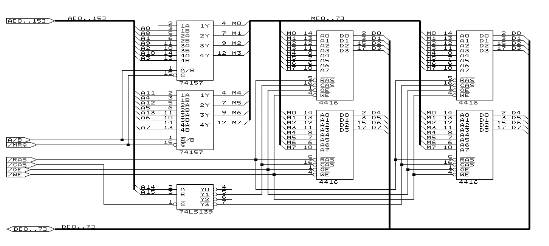

Jak już wspomniano wcześniej, pamięci dynamiczne wymagają specyficznego sterowania, które m. [Author ID1: at Sat Dec 15 18:47:00 2001

]in. zapewnia podział adresu na dwie połowy. Układ taki można wykonać z dwóch multiplekserów 74157. Każdy z nich przełącza 4 bity adresu. Wejścia multiplekserów są przyłączone do magistrali adresowej. W zasadzie[Author ID1: at Sat Dec 15 18:51:00 2001

]ogólnym przypadku[Author ID1: at Sat Dec 15 18:51:00 2001

] sposób ich przyporządkowania nie ma większego znaczenia. Jeżeli jednak korzystamy z [Author ID1: at Sat Dec 15 18:21:00 2001

] [Author ID1: at Sat Dec 15 18:21:00 2001

]mechanizmu wbudowanego w mikroprocesor Z-80, należy zapewnić, by zawartość[Author ID1: at Sat Dec 15 18:48:00 2001

]c[Author ID1: at Sat Dec 15 18:48:00 2001

] linii A0 - [Author ID1: at Sat Dec 15 18:48:00 2001

]-[Author ID1: at Sat Dec 15 18:48:00 2001

]A7 była przesłana na wejścia adresowe pamięci, gdy sygnał ![]()

jest w stanie aktywnym. Jest to warunek poprawnego odświeżenia pamięci.

Wyjścia multiplekserów tworzą 8-bitową magistralę multipleksowaną M0 - [Author ID1: at Sat Dec 15 18:52:00 2001

]-[Author ID1: at Sat Dec 15 18:52:00 2001

]M7, po której przesyłane są połówki adresów. Są one traktowane przez pamięć jako adresy wierszy (gdy ![]()

[Author ID1: at Sat Dec 15 18:53:00 2001

]= [Author ID1: at Sat Dec 15 18:53:00 2001

]„0”) lub kolumn (gdy ![]()

[Author ID1: at Sat Dec 15 18:53:00 2001

]= [Author ID1: at Sat Dec 15 18:53:00 2001

]„0”).

Wyjścia pamięci należy podłączyć do magistrali danych za pośrednictwem dwóch buforów 8216, podobnie jak w przyp[Author ID1: at Sat Dec 15 18:54:00 2001

]adku pamięci statycznej o rozdzielonych wejściach i wyjściach danych. Układy te są aktywne podczas dostępu mikroprocesora do przestrzeni adresowej pamięci, a ich wejścia ![]()

są w stanie aktywnym podczas cykli odczytu. Takie rozwiązanie zapewnia poprawne sprzężenie pamięci z dwukierunkową magistralą danych.

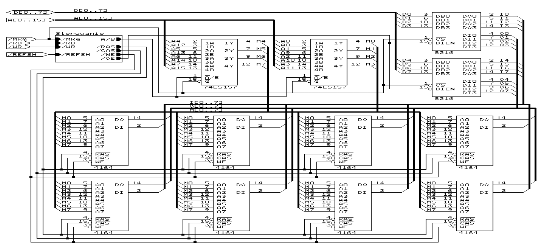

--> Rysunek 5.2. [Author ID1: at Sat Dec 15 18:55:00 2001 ][Author:EK] [Author ID1: at Sat Dec 15 18:56:00 2001 ][Author ID1: at Sat Dec 15 18:55:00 2001 ]

Poprawną pracę układu zapewnia odpowiedni układ sterujący, realizujący odpowiednie opóźnienia czasowe. Układ ten powinien także na podstawie sygnałów mikroprocesora (![]()

, ![]()

, ![]()

oraz ![]()

) generować sygnały dla pamięci dynamicznej (przede wszystkim ![]()

i ![]()

, lecz także ![]()

i ewentualnie ![]()

) oraz sygnał przełączania wejść multiplekserów 74157. Przykładowy układ pokazany jest na rys. Wykorzystano w nim także dodatkowy sygnał wyboru bloku pamięci ![]()

, który może pochodzić np. z dekodera adresów.

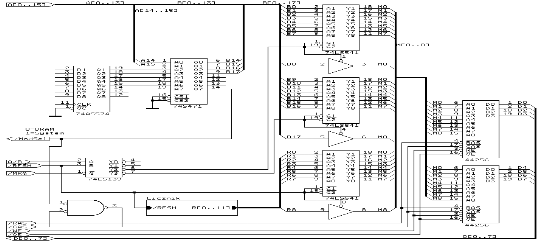

--> Rysunek 5.3. [Author ID1: at Sat Dec 15 18:57:00 2001 ][Author:EK] [Author ID1: at Sat Dec 15 18:58:00 2001 ][Author ID1: at Sat Dec 15 18:57:00 2001 ]

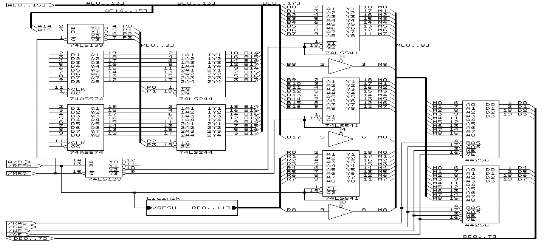

Najprostsze jest uzyskanie sygnałów ![]()

i [Author ID1: at Sat Dec 15 18:21:00 2001

] [Author ID1: at Sat Dec 15 18:21:00 2001

]![]()

, ponieważ odpowiadają one wprost sygnałom ![]()

i ![]()

mikroprocesora. Sygnał ![]()

jest nieznacznie opóźniony względem ![]()

o czas propagacji dwóch bramek negacji, tj. około 10 - [Author ID1: at Sat Dec 15 18:59:00 2001

]-[Author ID1: at Sat Dec 15 18:59:00 2001

]15 ns. Układ opóźniający, zbudowany z opornika i kondensatora, ma za zadanie opóźnić moment przełączenia wejść multiplekserów. Czas tego opóźnienia t nie może być krótszy od czasu potrzebnego pamięci na zapamiętanie adresu wiersza. Jeżeli sygnał ![]()

jest nieaktywny, to kondensator jest rozładowywany. Dlatego też na wejściu bramek Schmitta utrzymuje się stan niski przez czas t od chwili przejścia sygnału ![]()

w stan aktywny. W tym czasie na wyjściu bramki Schmitta jest stan wysoki, a więc sygnał przełączenia multiplekserów ma też stan wysoki.

Kondensator zaczyna się ładować, gdy ![]()

przechodzi w stan aktywny. Po czasie t napięcie na kondensatorze jest wystarczające do przełączenia bramek Schmitta. Ponieważ w czasie odczytu lub zapisu pamięci sygnał ![]()

jest nieaktywny, sygnał przełączania wejść multiplekserów zmienia stan na wysoki. Sygnał ![]()

może także się uaktywnić z pewnym opóźnieniem, o ile wejście ![]()

[Author ID1: at Sat Dec 15 18:21:00 2001

] [Author ID1: at Sat Dec 15 18:21:00 2001

]jest w stanie aktywnym („0”). Jeżeli tak jest, pamięć zapamiętuje adres kolumny i od tego momentu uaktywnia się w celu wykonania operacji odczytu lub zapisu. Jeśli natomiast pamięć nie jest wybrana, wykorzystuje podany adres wiersza w procesie odświeżania.

W czasie odświeżania pamięci mikroprocesor Z-80 generuje sygnały ![]()

oraz ![]()

. Wtedy sygnał przełączenia wejść multiplekserów jest w stanie wysokim.

Z przedstawionego opisu wynika, że sygnał wyboru wejść multiplekserów przyjmuje wartość „1” podczas podawania adresu wiersza i „0” podczas podawania adresu kolumny. Aby więc wykorzystać adres odświeżania generowany przez mikroprocesor, należy wejścia B multiplekserów dołączyć do młodszej połowy magistrali adresowej (A0 - [Author ID1: at Sat Dec 15 19:01:00 2001

]-[Author ID1: at Sat Dec 15 19:01:00 2001

]A7).

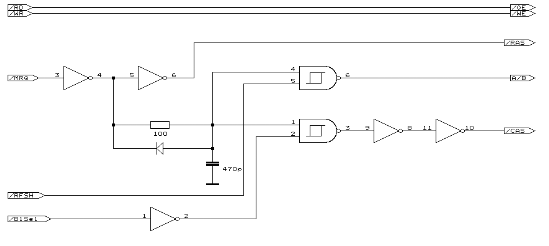

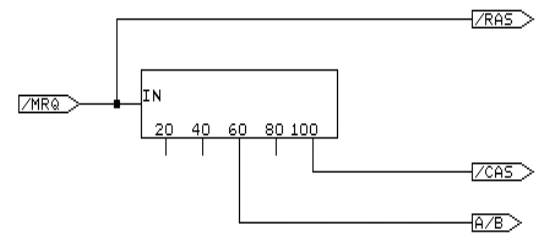

Układ sterujący pamięci dynamicznych nie musi być tak skomplikowany. Proste i eleganckie rozwiązanie wykorzystuje tzw. kaskadę opóźniającą TTL DL-20. Zaletą tego układu jest duża dokładność generowanych opóźnień. W tym przypadku sygnał przełączenia wejść multiplekserów jest opóźniony w stosunku do ![]()

o 60 ns, a sygnał ![]()

—[Author ID1: at Sat Dec 15 19:01:00 2001

]-[Author ID1: at Sat Dec 15 19:01:00 2001

] o 100 ns. Podobne rozwiązanie było zastosowane w module pamięci mikrokomputera osobistego IBM PC/XT.

--> Rysunek 5.4. [Author ID1: at Sat Dec 15 19:02:00 2001 ][Author:EK] [Author ID1: at Sat Dec 15 19:02:00 2001 ][Author ID1: at Sat Dec 15 19:02:00 2001 ]

Dodatkowe uproszczenie układu uzyskuje się, stosując pamięci o organizacji 4-bitowej. Można też wykorzystać scalony sterownik pamięci dynamicznych, np. układy 8202 albo 8203 firmy Intel.

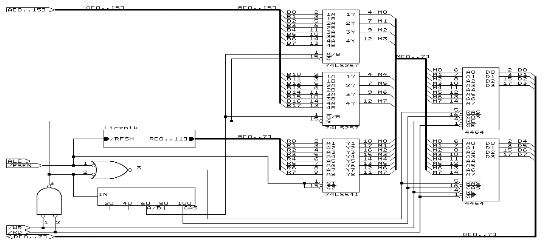

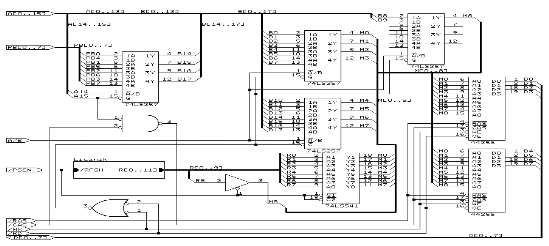

Przykład 2.[Author ID1: at Sat Dec 15 19:03:00 2001 ]

Zaprojektować moduł pamięci dynamicznej dla mikroprocesora Z-80, zawierający 32 KB pamięci dynamicznej, zajmującej adresy 4000 - [Author ID1: at Sat Dec 15 19:03:00 2001

]-[Author ID1: at Sat Dec 15 19:03:00 2001

]7FFFh oraz C000 - [Author ID1: at Sat Dec 15 19:03:00 2001

]-[Author ID1: at Sat Dec 15 19:03:00 2001

]FFFFh. Wykorzystać układy pamięci o organizacji 16K [Author ID1: at Sat Dec 15 19:03:00 2001

]× [Author ID1: at Sat Dec 15 19:03:00 2001

]4. Założyć, że są dostępne sygnały sterujące pamięciami dynamicznymi.

--> Rysunek 5.5. [Author ID1: at Sat Dec 15 19:04:00 2001 ][Author:EK] [Author ID1: at Sat Dec 15 19:04:00 2001 ][Author ID1: at Sat Dec 15 19:04:00 2001 ]

Do zbudowania modułu potrzebne są cztery układy pamięci, przy czym jeden zakres adresów jest wypełniony przez dwa układy. Sygnały sterujące pamięciami dynamicznymi i układem przełączającym linie adresowe są generowane poza modułem. Wobec tego pozostaje odpowiednie rozprowadzenie sygnałów do wejść pamięci. Sygnały ![]()

i ![]()

z układu sterującego oczywiście należy dołączyć równolegle do odpowiednich wejść pamięci. Podobnie sygnał ![]()

—[Author ID1: at Sat Dec 15 19:06:00 2001

]-[Author ID1: at Sat Dec 15 19:06:00 2001

] dołączenie go do wszystkich wejść pamięci nie powoduje żadnych niekorzystnych zjawisk. Wręcz przeciwnie —[Author ID1: at Sat Dec 15 19:06:00 2001

]-[Author ID1: at Sat Dec 15 19:06:00 2001

] pamięć z aktywnym wejściem ![]()

, a nie wybrana sygnałem ![]()

, potraktuje zawartość wejść adresowych jako adres odświeżanego wiersza i wykona cykl odświeżania. Inaczej jest w przypadku sygnału ![]()

, gdyż powinien on być aktywny tylko w tych układach pamięci, które znajdują się pod adresem wygenerowanym przez mikroprocesor. Dlatego też sygnał ten rozdziela się na podstawie stanu dwóch najstarszych linii adresowych (A14 - [Author ID1: at Sat Dec 15 19:07:00 2001

]-[Author ID1: at Sat Dec 15 19:07:00 2001

]A15) w demultiplekserze 74139.

Krótkiego komentarza wymaga jeszcze sposób multipleksowania linii adresowych. Otóż pamięć o organizacji 16K [Author ID1: at Sat Dec 15 19:07:00 2001

]× [Author ID1: at Sat Dec 15 19:07:00 2001

]4 wymaga nieco odmiennych zasad podawania adresów:[Author ID1: at Sat Dec 15 19:08:00 2001

] -[Author ID1: at Sat Dec 15 19:08:00 2001

] adres wiersza podaje się na wejściach A0 - [Author ID1: at Sat Dec 15 19:08:00 2001

]-[Author ID1: at Sat Dec 15 19:08:00 2001

]A7, natomiast adres kolumny — na wejściach [Author ID1: at Sat Dec 15 19:09:00 2001

]-[Author ID1: at Sat Dec 15 19:09:00 2001

] [Author ID1: at Sat Dec 15 19:08:00 2001

]A1 - [Author ID1: at Sat Dec 15 19:09:00 2001

]-[Author ID1: at Sat Dec 15 19:09:00 2001

]A6.

Przykład 3.[Author ID1: at Sat Dec 15 19:10:00 2001 ]

Zaprojektować moduł pamięci dynamicznej dla mikroprocesora Z-80, zawierający 256 KB pamięci widzianej jako 16 stron po 16 KB każda. Jako rejestr numeru strony należy [Author ID1: at Sun Dec 16 23:36:00 2001

]wykorzystać dwa układy 74574 w ten sposób, że jeden z nich zawiera numery stron widzianych pod adresami 0000 - [Author ID1: at Sat Dec 15 19:10:00 2001

]-[Author ID1: at Sat Dec 15 19:10:00 2001

]3FFFh i 4000 - [Author ID1: at Sat Dec 15 19:10:00 2001

]-[Author ID1: at Sat Dec 15 19:10:00 2001

]7FFFh, drugi natomiast —[Author ID1: at Sat Dec 15 19:11:00 2001

]-[Author ID1: at Sat Dec 15 19:11:00 2001

] pod adresami [Author ID1: at Sat Dec 15 19:11:00 2001

]8000 - [Author ID1: at Sat Dec 15 19:11:00 2001

]-[Author ID1: at Sat Dec 15 19:11:00 2001

]BFFFh i C000 - [Author ID1: at Sat Dec 15 19:11:00 2001

]-[Author ID1: at Sat Dec 15 19:11:00 2001

]FFFFh. Należy również w[Author ID1: at Sun Dec 16 23:37:00 2001

]W[Author ID1: at Sun Dec 16 23:37:00 2001

]ykorzystać układy pamięci o organizacji 256K [Author ID1: at Sat Dec 15 19:11:00 2001

]× [Author ID1: at Sat Dec 15 19:11:00 2001

]4. Sygnały sterujące pamięcią są generowane przez układ zewnętrzny. Założyć (zgodnie z prawdą), że mechanizm odświeżania wbudowany w mikroprocesor nie jest wystarczający do odświeżenia pamięci o tak dużej pojemności.

Mechanizm stronicowania umożliwia podłączenie do mikroprocesora pamięci o większej pojemności niż jego przestrzeń adresowa. Zastosowany podział na strony o pojemności 16 KB powoduje, że mikroprocesor w każdej chwili może „widzieć” co najwyżej cztery strony. Jeżeli istnieje potrzeba odwołania się do strony „niewidocznej”, musi ono być poprzedzone zapisaniem jej numeru do odpowiedniego rejestru strony. W przypadku Z-80 rejestr taki powinien być umieszczony w przestrzeni adresowej wejścia-wyjścia.

--> Rysunek 5.6. [Author ID1: at Sat Dec 15 19:15:00 2001 ][Author:EK] [Author ID1: at Sat Dec 15 19:15:00 2001 ][Author ID1: at Sat Dec 15 19:15:00 2001 ]

W rozpatrywanym przykładzie rejestr strony zbudowany jest z wykorzystaniem dwóch rejestrów 74574. Każdy z nich przechowuje numery dwóch stron. Wybór odpowiedniego numeru odbywa się na podstawie stanu dwóch najstarszych linii adresowych, które wobec tego nie mogą być użyte do dalszego adresowania. Wybór ten dokonuje się w demultiplekserze 74139, który w czasie trwania cyklu dostępu do pamięci uaktywnia odpowiednią część jednego z dwóch buforów 74244. Wyjścia tych buforów tworzą cztery najstarsze linie 18-bitowej magistrali adresowej B, użytej do adresowania pamięci (218 [Author ID1: at Sat Dec 15 20:33:00 2001

]= [Author ID1: at Sat Dec 15 20:34:00 2001

]256 K), tj. linie B14 - [Author ID1: at Sat Dec 15 20:34:00 2001

]-[Author ID1: at Sat Dec 15 20:34:00 2001

]B17. Pozostałe linie tej magistrali (B0 - [Author ID1: at Sat Dec 15 20:35:00 2001

]-[Author ID1: at Sat Dec 15 20:35:00 2001

]B13) powielają bezpośrednio stan odpowiednich bitów magistrali adresowej mikroprocesora —[Author ID1: at Sat Dec 15 20:36:00 2001

]-[Author ID1: at Sat Dec 15 20:36:00 2001

] A0 - [Author ID1: at Sat Dec 15 20:36:00 2001

]-[Author ID1: at Sat Dec 15 20:36:00 2001

]A13.

Zamiast buforów 74244 można użyć multiplekserów 74257 z wyjściami trójstanowymi lub analogicznych 74157 z wyjściami przeciwsobnymi. Obie wersje fragmentu schematu głównego pokazano na rysunku 5.7[Author ID1: at Sat Dec 15 20:37:00 2001

]rys[Author ID1: at Sat Dec 15 20:37:00 2001

].

--> Rysunek 5.7. [Author ID1: at Sat Dec 15 20:38:00 2001 ][Author:EK] [Author ID1: at Sat Dec 15 20:39:00 2001 ][Author ID1: at Sat Dec 15 20:38:00 2001 ]

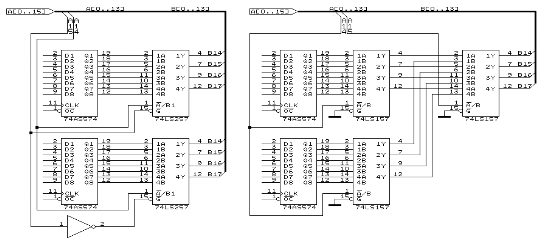

Tak uzyskany 18-bitowy adres pamięci dzieli się na dwie połowy po 9 bitów. W poprzednich przykładach pokazano sposób podziału przy użyciu multiplekserów, natomiast tutaj wykorzystano do tego celu 8-bitowe bufory z wyjściami trójstanowymi 74541 oraz bramki trójstanowe 74125. Bramki te są potrzebne, ponieważ adresy przesyła się w porcjach po 9 bitów. Wyjścia buforów i bramek tworzą 9-bitową magistralę M, do której bezpośrednio dołączono wejścia adresowe obu układów pamięci.

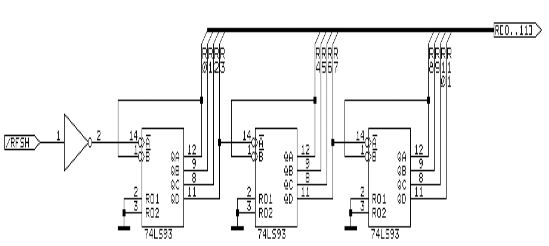

Ponieważ licznik odświeżania w mikroprocesorze Z-80 jest 8-bitowy, jego pojemność nie wystarcza do odświeżenia pamięci 256 KB, której adres wiersza ma 9 bitów. Dlatego też konieczne jest włączenie do układu dodatkowego licznika o pojemności co najmniej 9 bitów. Licznik ten zawiera adres odświeżanego wiersza, zatem jego stan jest zwiększany o 1 po każdym cyklu odświeżania. Do jego budowy można oczywiście wykorzystać układy liczników asynchronicznych (jak w załączonym przykładzie) lub synchronicznych. Należy jeszcze zadbać, aby zwiększenie stanu licznika nastąpiło na koniec cyklu odświeżania, tj. podczas trwania zbocza narastającego sygnału ![]()

mikroprocesora. W przypadku stosowania liczników reagujących na zbocze opadające sygnał ten należy zatem zanegować.

--> Rysunek 5.8. [Author ID1: at Sat Dec 15 20:41:00 2001 ][Author:EK] [Author ID1: at Sat Dec 15 20:41:00 2001 ][Author ID1: at Sat Dec 15 20:41:00 2001 ]

Uzyskany w ten sposób 9-bitowy adres odświeżanego wiersza należy także wprowadzać w odpowiednich momentach na magistralę M. Mamy zatem trzy różne adresy, wprowadzane na tę magistralę: adres wiersza, adres kolumny i adres wiersza odświeżanego. Każdy z nich podaje się przez bufor 74541 oraz bramkę 74125. Wybór odpowiedniego adresu dokonuje się w drugim demultiplekserze 74139. Jeżeli pamięć nie jest odświeżana (sygnał ![]()

jest nieaktywny), to wybór między adresem wiersza i kolumny odbywa się na podstawie stanu sygnału A/B. Sygnał ten pochodzi z układu sterującego. W poprzednich przykładach był stosowany do przełączania wejść multiplekserów, pełnił zatem tę samą funkcję. Podczas odświeżania pamięci sygnał ![]()

włącza bufor przekazujący zawartość licznika odświeżanego wiersza na wejścia adresowe pamięci. Ponieważ adres odświeżania generowany przezz[Author ID1: at Sat Dec 15 20:43:00 2001

] mikroprocesor można zignorować, sposób multipleksowania magistrali B na magistrali M jest całkowicie dowolny.

Dokładny sposób dołączenia rejestrów strony do magistrali wykracza poza zakres pamięci dynamicznych i zostanie omówiony w rozdziale dotyczącym układów równoległego wejścia-wyjścia.

Przykład 4.[Author ID1: at Sat Dec 15 20:45:00 2001 ]

Zaprojektować moduł pamięci dynamicznej dla mikroprocesora Z-80, zawierający 1 MB pamięci widzianej jako 32 stron po 32 KB każda. Jako rejestr numeru strony należy [Author ID1: at Sun Dec 16 23:38:00 2001

]wykorzystać dwa układy 74574 w ten sposób, że jeden z nich zawiera numer strony widzianej pod adresami 0000 - [Author ID1: at Sat Dec 15 20:46:00 2001

]-[Author ID1: at Sat Dec 15 20:46:00 2001

]7FFFh, drugi natomiast —[Author ID1: at Sat Dec 15 20:47:00 2001

]-[Author ID1: at Sat Dec 15 20:47:00 2001

] pod adresami [Author ID1: at Sat Dec 15 20:47:00 2001

]8000 - [Author ID1: at Sat Dec 15 20:47:00 2001

]-[Author ID1: at Sat Dec 15 20:47:00 2001

]FFFFh. Należy również w[Author ID1: at Sun Dec 16 23:39:00 2001

]W[Author ID1: at Sun Dec 16 23:39:00 2001

]ykorzystać układy pamięci o organizacji 1M [Author ID1: at Sat Dec 15 20:47:00 2001

]× [Author ID1: at Sat Dec 15 20:47:00 2001

]4. Sygnały sterujące pamięcią są generowane przez układ zewnętrzny. Mechanizm odświeżania wbudowany w mikroprocesor nie jest wystarczający do odświeżenia pamięci o tak dużej pojemności.

--> Rysunek 5.9. [Author ID1: at Sat Dec 15 20:48:00 2001 ][Author:EK] [Author ID1: at Sat Dec 15 20:48:00 2001 ][Author ID1: at Sat Dec 15 20:48:00 2001 ]

Rozwiązanie jest bardzo podobne do poprzedniego przykładu, zawiera jednak kilka różnic. Przede wszystkim 64-kilobajtową przestrzeń adresową wypełniają teraz dwie strony pamięci, a nie cztery. W związku z tym stosuje się tylko dwa numery aktywnych stron. Ponieważ numery te są 5-bitowe, a użyto rejestrów 8-bitowych z wyjściami trójstanowymi, wystarczy odpowiednio sterować wejścia ![]()

tych rejestrów, aby w odpowiednim momencie uzyskać na magistrali B właściwą informację. Eliminuje to konieczność stosowania dodatkowych buforów lub multiplekserów, które były niezbędne w poprzednim przykładzie. Układy te byłyby jednak niezbędne, gdyby rejestry stron zrealizować na układach nie wyposażonych w wyjścia trójstanowe.

Koe[Author ID1: at Sat Dec 15 20:51:00 2001

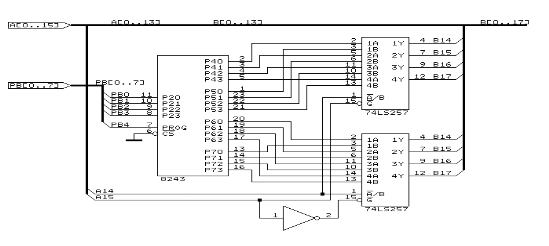

]lejna zmiana wynika ze stosowania 20-bitowych adresów pamięci, zatem układy przełączające połówki magistrali B oraz magistralę R w magistralę M muszą przekazywać po 10 bitów. Dlatego też do każdego bufora 74541 dołączono aż dwie bramki trójstanowe. W alternatywnym rozwiązaniu można wykorzystać multipleksery, np. tak jak

-->

na rysunku[Author ID1: at Sat Dec 15 20:52:00 2001

][Author:EK]

[Author ID1: at Sat Dec 15 20:53:00 2001

]. Są to multipleksery 74257 z wyjściami trójstanowymi, które są aktywne, gdy nie odświeża się pamięci (sygnał ![]()

w stanie wysokim). Zależnie od stanu sygnału sterującego A/B przekazują one jedną lub drugą połówkę magistrli B na magistralę M, przy czym przedstawione przyporządkowanie jest nieco inne niż w rozwiązaniu z buforami. Nie ma to jednak znaczenia, ponieważ adres odświeżania generowany przez mikroprocesor jest ignorowany. Podczas cyklu odświeżania wyjścia multiplekserów są w stanie wysokiej impedancji, natomiast na magistralę M podawany jest adres odświeżanego wiersza pochodzący z układu licznikowego.

Jeszcze inne rozwiązanie polega na zastosowaniu dwóch poziomów multiplekserów 74157. Jeden z nich wybiera połówki magistrali B, drugi natomiast —[Author ID1: at Sat Dec 15 21:01:00 2001

]-[Author ID1: at Sat Dec 15 21:01:00 2001

] przełącza między wyjściami układów pierwszego poziomu a adresem odświeżanego wiersza. Wymaga to aż 6 układów 74157. Lepiej zatem byłoby zastosować multipleksery 74153. Ponieważ każdy z nich może przełączać dwa bity magistrali M, potrzebnych jest pięć takich układów.

--> Rysunek 5.10. [Author ID1: at Sat Dec 15 21:01:00 2001 ][Author:EK] [Author ID1: at Sat Dec 15 21:02:00 2001 ][Author ID1: at Sat Dec 15 21:01:00 2001 ]

Przykład 5.[Author ID1: at Sat Dec 15 21:02:00 2001 ]

Zaprojektować moduł pamięci dynamicznej dla mikroprocesora Z-80, zawierający 256 KB pamięci widzianej jako 16 stron po 16 KB każda. Zapewnić możliwość pracy modułu w wielu trybach, zapisanych w pamięci PROM i określających widoczność poszczególnych stron w wybranych przedziałach adresowych. Wykorzystać układy pamięci o organizacji 256K [Author ID1: at Sat Dec 15 21:03:00 2001

]× [Author ID1: at Sat Dec 15 21:03:00 2001

]4. Sygnały sterujące pamięcią są generowane przez układ zewnętrzny, a mechanizm odświeżania wbudowany w mikroprocesor nie jest wystarczający do odświeżenia pamięci o tak dużej pojemności. Dodatkowo moduł powinien generować sygnał, włączający pamięć znajdującą się poza nim („systemową”), jeżeli w wybranym trybie pod pewnymi adresami nie jest aktywna strona pamięci dynamicznej. Przykładowe tryby pracy modułu podaje

-->

tabela.[Author:EK]

[Author ID1: at Sat Dec 15 21:04:00 2001

]

W przykładzie tym nie występuje rejestr strony, ponieważ numery stron aktywnych w określonych przedziałach adresów zapisane są w pamięci PROM. Do sterowania modułem wystarczy zatem tylko jeden rejestr, który przechowuje bieżący numer trybu. W przypadku rejestru 8-bitowego do dyspozycji jest 256 trybów, co powinno być wielkością wystarczającą. W naszym przykładzie użytych jest tylko 6 bitów rejestru trybu, a więc liczba trybów wynosi 64.

--> -->Rysunek 5.11[Author ID1: at Sat Dec 15 21:05:00 2001 ][Author ID1: at Sat Dec 15 21:06:00 2001 ]. [Author ID1: at Sat Dec 15 21:05:00 2001 ][Author:EK] [Author ID1: at Sat Dec 15 21:05:00 2001 ] [Author ID1: at Sat Dec 15 21:05:00 2001 ]

Rejestr trybu steruje wejściami adresowymi pamięci PROM o organizacji 256 [Author ID1: at Sat Dec 15 21:06:00 2001

]× [Author ID1: at Sat Dec 15 21:06:00 2001

]8 (układ 74S471). Pozostałe dwa wejścia adresowe podłączone są do dwóch najstarszych bitów magistrali adresowej (A14 - [Author ID1: at Sat Dec 15 21:06:00 2001

]-[Author ID1: at Sat Dec 15 21:06:00 2001

]A15). W odniesieniu do opisu trybów

-->

(tabela x) [Author:EK]

[Author ID1: at Sat Dec 15 21:06:00 2001

]zawartość rejestru trybu określa kolumnę tabeli, natomiast jej wiersz zależy od stanu linii A14 i A15. Można więc powiedzieć, że wszystkie wejścia adresowe pamięci PROM określają położenie w tabeli z dokładnością do jednej komórki.

Z założeń zadania wynika, że moduł powinien generować sygnał informujący, czy pod podanym przez mikroprocesor adresem jest aktywna strona pamięci. Na schemacie sygnał ten oznaczony jest jako ![]()

. Oczywiście stan tego sygnału zależy nie tylko od adresu, lecz także od bieżącego trybu pracy modułu. Jeżeli ![]()

[Author ID1: at Sat Dec 15 21:12:00 2001

]= [Author ID1: at Sat Dec 15 21:12:00 2001

]„0”, to sygnał ![]()

przechodzi do układów pamięci. Pamięć DRAM jest zatem aktywna. Gdy natomiast ![]()

jest w stanie wysokim, to ![]()

nie dochodzi do pamięci. Aktywność pamięci nie wpływa zatem na jej odświeżanie, bo pobudzana[Author ID1: at Sat Dec 15 21:13:00 2001

]e[Author ID1: at Sat Dec 15 21:13:00 2001

] jest sygnałem ![]()

.

Pozostałe wyjścia pamięci PROM wyprowadza się na magistralę B (linie B14 - [Author ID1: at Sat Dec 15 21:13:00 2001

]-[Author ID1: at Sat Dec 15 21:13:00 2001

]B17). Stanowią one numer wybranej strony. Jest to strona aktywna w bieżącym trybie pracy i znajdująca się w tym samym przedziale adresowym, co adres wygenerowany przez mikroprocesor. Sposób podziału magistrali B na magistralę M jest całkowicie dowolny, ponieważ używane adresy odświeżanych wier[Author ID1: at Sat Dec 15 21:14:00 2001

]szy nie pochodzą z mikroprocesora.

Aby układ przełączał strony pamięci zgodnie z założeniami, należy odpowiednio zaprogramować pamięć PROM. Fragment jej zawartości podano w tabeli. Adres komórek tej pamięci tworzy się na podstawie numeru trybu i stanu najstraszych linii adresowych, natomiast żądaną zawartość komórki —[Author ID1: at Sat Dec 15 21:14:00 2001

]-[Author ID1: at Sat Dec 15 21:14:00 2001

] przez określenie numeru strony i stanu sygnału ![]()

. Jeżeli ![]()

[Author ID1: at Sat Dec 15 21:14:00 2001

]= [Author ID1: at Sat Dec 15 21:15:00 2001

]„1”, to numer strony jest dowolny, ponieważ pamięć DRAM jest wówczas nieaktywna.

Przykład 6.[Author ID1: at Sat Dec 15 21:16:00 2001 ]

Zaprojektować moduł pamięci dynamicznej dla mikroprocesora 8051, zawierający 64 KB pamięci widzianej jako zewnętrzna pamięć danych. Wykorzystać moduły pamięci o organizacji 64K [Author ID1: at Sat Dec 15 21:16:00 2001 ]× [Author ID1: at Sat Dec 15 21:16:00 2001 ]4. Zapewnić odpowiedni mechanizm odświeżania. Przedstawić układ sterujący pracą modułu pamięci dynamicznej na podstawie stanu sygnałów sterujących mikroprocesora 8051.

W przypadku dołączania modułu pamięci dynamicznej do mikroprocesora 8051 niezbędne sygnały sterujące (![]()

, ![]()

, przełączanie multiplekserów) poninny być wygenerowane na podstawie stanu tych sygnałów sterujących mikroprocesora, których używa on przy współpracy z pamięciami zewnętrznymi. Są to sygnały ALE, ![]()

, ![]()

i ![]()

. Pierwszy z nich jest wytwarzany praktycznie zawsze —[Author ID1: at Sat Dec 15 21:17:00 2001

]-[Author ID1: at Sat Dec 15 21:17:00 2001

] mikroprocesor pomija go tylko wtedy, gdy aktywny jest ![]()

lub ![]()

. Z kolei ![]()

pojawia się, jeżeli mikroprocesor odwołuje się do zewnętrznej pamięci programu, co nie zawsze musi nastąpić. Podobnie jak ALE, sygnał ten nie jest wytwarzany podczas cyklu dostępu do zewnętrznej pamięci danych. Można więc powiedzieć, że momenty adresowania zewnętrznej pamięciu[Author ID1: at Sat Dec 15 21:18:00 2001

] programu i danych nie pokrywają się. Jest to dość ważne, można [Author ID1: at Sat Dec 15 21:19:00 2001

]bowiem dzięki temu określa się[Author ID1: at Sat Dec 15 21:19:00 2001

]ić[Author ID1: at Sat Dec 15 21:19:00 2001

] chwile, kiedy można przeprowadzić odświeżanie pamięci. Musi być to odświeżanie synchroniczne, ponieważ mikroprocesor 8051 nie ma wejść takich jak np. ![]()

czy ![]()

w Z-80. Nie można zatem —[Author ID1: at Sat Dec 15 21:20:00 2001

]-[Author ID1: at Sat Dec 15 21:20:00 2001

] tak jak w Z-80 —[Author ID1: at Sat Dec 15 21:20:00 2001

]-[Author ID1: at Sat Dec 15 21:20:00 2001

] ani odłączyć mikroprocesora od magistrali, ani wydłużyć cyklu maszynowego.

--> Rysunek 5.12. [Author ID1: at Sat Dec 15 21:20:00 2001 ][Author:EK] [Author ID1: at Sat Dec 15 21:21:00 2001 ][Author ID1: at Sat Dec 15 21:20:00 2001 ]

Jeżeli aktywny jest sygnał ![]()

, to mikroprocesor na pewno nie adresuje zewnętrznej pamięci danych. Można więc w tym czasie wykonać odświeżanie wiersza pamięci dynamicznej. Adres tego wiersza powinien być podany z dodatkowego licznika, inkrementowanego po każdym cyklu odświeżania. Pomiędzy tym licznikiem a wejściami adresowymi pamięci znajduje się bufor z wyjściami trójstanowymi, dzięki któremu układ odświeżania nie zakłóca normalnych cykli dostępu do pamięci.

Mikroprocesor 8051 nie generuje też sygnału żądania dostępu do pamięci typu ![]()

. Zbliżony sygnał ten [Author ID1: at Sat Dec 15 21:26:00 2001

]M[Author ID1: at Sat Dec 15 21:25:00 2001

]m[Author ID1: at Sat Dec 15 21:25:00 2001

]ożna jednak wytworzyć sygnał zbliżony [Author ID1: at Sat Dec 15 21:25:00 2001

]—[Author ID1: at Sat Dec 15 21:23:00 2001

]-[Author ID1: at Sat Dec 15 21:22:00 2001

] powinien on być aktywny, gdy któryś z sygnałów ![]()

lub ![]()

przyjmuje stan niski. Tak uzyskany sygnał włącza multipleksery 74257, przełączające połówki adresów. Powinien on także sterować wejścia ![]()

układów pamięci. Wejścia te muszą być jednak aktywne także podczas odświeżania, dlatego sygnał ![]()

uwzględnia także stan sygnału ![]()

. Sygnały A/B i ![]()

są opóźnione w stosunku do ![]()

o 60 i 100 ns. Pierwszy z nich steruje multiplekserami, a drugi —[Author ID1: at Sat Dec 15 21:28:00 2001

]-[Author ID1: at Sat Dec 15 21:28:00 2001

] układami pamięci.

Jeżeli mikroprocesor nie korzysta z zewnętrznej pamięci programu, sygnał ![]()

nie jest generowany. Do odświeżania pamięci można wówczas stosować sygnał ALE. Odświeżanie może nastąpić, gdy ALE jest w stanie wysokim. Sytuacja taka nie występuje bowiem, gdy aktywny jest sygnał ![]()

lub ![]()

.

Ze względu na sposób wykonania układu odświeżania moduł pamięci dynamicznej nie może być stosowany jako łączona pamięć programu i danych.

Przykład 7.[Author ID1: at Sat Dec 15 21:28:00 2001 ]

Zaprojektować moduł pamięci dynamicznej dla mikroprocesora 8051, zawierający 1 [Author ID1: at Sat Dec 15 21:29:00 2001

]MB pamięci widzianej jako zewnętrzna pamięć danych i podzielonej na 64 strony po 16 KB. Jako rejestry stron należy [Author ID1: at Sat Dec 15 21:30:00 2001

]wykorzystać cztery układy 74574.[Author ID1: at Sat Dec 15 21:30:00 2001

],[Author ID1: at Sat Dec 15 21:30:00 2001

] Każdy z nich zawiera jeden numer strony, aktywnej w zakresie adresów 0000 - [Author ID1: at Sat Dec 15 21:31:00 2001

]-[Author ID1: at Sat Dec 15 21:31:00 2001

]3FFFh, 4000 -[Author ID1: at Sat Dec 15 21:31:00 2001

] [Author ID1: at Sat Dec 15 21:31:00 2001

]-[Author ID1: at Sat Dec 15 21:31:00 2001

]7FFFh, 8000 - [Author ID1: at Sat Dec 15 21:32:00 2001

]-[Author ID1: at Sat Dec 15 21:32:00 2001

]BFFFh i C000 - [Author ID1: at Sat Dec 15 21:32:00 2001

]-[Author ID1: at Sat Dec 15 21:32:00 2001

]FFFFh. Wykorzystać moduły pamięci o organizacji 1M [Author ID1: at Sat Dec 15 21:32:00 2001

]× [Author ID1: at Sat Dec 15 21:32:00 2001

]4. Zapewnić odpowiedni mechanizm odświeżania. Założyć, że sygnały sterujące pamięcią dynamiczną są wytwarzane w układzie zewnętrznym.

--> Rysune[Author ID1: at Sat Dec 15 21:33:00 2001 ]k 5.13. [Author ID1: at Sat Dec 15 21:33:00 2001 ][Author:EK] [Author ID1: at Sat Dec 15 21:34:00 2001 ][Author ID1: at Sat Dec 15 21:33:00 2001 ]

Podział pamięci na 64 strony o pojemności 16 KB wymusza użycie 6-bitowych numerów stron i 14-bitowych adresów w ramach jednej strony. W zależności od stanu dwóch najstarszych linii adresowych wybierany jest jeden z czterech rejestrów numeru strony, którego zawartość tworzy 6 najstarszych bitów magistrali B. Wraz z 14-bitowym adresem w ramach strony tworzy to 20-bitowy adres, który wystarcza do zaadresowania 1 MB pamięci. Adres ten dzieli się w trzech multiplekserach 74257 (z wyjściami trójstanowymi) na dwie połówki. Wybór połówki przekazywanej na magistralę M odbywa się na podstawie stanu sygnału A/B. Opisany mechanizm działa podczas cykli odczytu lub zapisu zewnętrznej pamięci danych. Podczas cyklu odświeżania wyjścia multipl[Author ID1: at Sat Dec 15 21:36:00 2001

]k[Author ID1: at Sat Dec 15 21:36:00 2001

]ekserów są w stanie wysokiej impedancji, a na magistralę M podawana jest[Author ID1: at Sat Dec 15 21:37:00 2001

]je się[Author ID1: at Sat Dec 15 21:37:00 2001

] —[Author ID1: at Sat Dec 15 21:37:00 2001

]-[Author ID1: at Sat Dec 15 21:37:00 2001

] poprzez bufor i bramki trójstanowe —[Author ID1: at Sat Dec 15 21:37:00 2001

]-[Author ID1: at Sat Dec 15 21:37:00 2001

] zawartość licznika odświeżanego wiersza.

Sygnał ![]()

staje się aktywny tylko podczas cykli odczytu i zapisu pamięci, natomiast ![]()

—[Author ID1: at Sat Dec 15 21:38:00 2001

]-[Author ID1: at Sat Dec 15 21:38:00 2001

] także podczas cykli odświeżania, które są realizowane, gdy mikroprocesor pobiera kody rozkazów z zewnętrznej pamięci programu. Sygnały te wytwarza się w taki sam sposób, jak w poprzednim przykładzie.

Przykład 8.[Author ID1: at Sat Dec 15 21:38:00 2001 ]

Zaprojektować moduł pamięci dynamicznej dla z[Author ID1: at Sat Dec 15 21:39:00 2001

] mikroprocesora 8051, zawierający 256 KB pamięci podzielonej na 16 stron po 16 KB. W danej chwili widziane są tylko dwie strony, których numery znajdują się na wyjściach portu PB. Pamięć zajmuje adresy 0000 - [Author ID1: at Sat Dec 15 21:39:00 2001

]-[Author ID1: at Sat Dec 15 21:39:00 2001

]7FFFh. Założyć, że niezbędne sygnały sterujące są już dostępne w systemie.

W przypadku użycia portu mikroprocesora jako rejestru strony można zmieścić w nim tylko dwa numery stron przy zadanym rozmiarze tego numeru (4 bity). Dlatego też jednocześnie [Author ID1: at Sat Dec 15 21:41:00 2001

]naraz [Author ID1: at Sat Dec 15 21:41:00 2001

]widoczne są tylko dwie strony. Jeżeli wygenerowany adres znajduje się w zakresie 0000 - [Author ID1: at Sat Dec 15 21:42:00 2001

]-[Author ID1: at Sat Dec 15 21:42:00 2001

]3FFFh, to widoczna jest strona o numerze podanym na wyjścia portu PB0 - [Author ID1: at Sat Dec 15 21:42:00 2001

]-[Author ID1: at Sat Dec 15 21:42:00 2001

]PB3, podczas gdy zakres 4000 - [Author ID1: at Sat Dec 15 21:42:00 2001

]-[Author ID1: at Sat Dec 15 21:42:00 2001

]7FFFh obsługują pozostałe linie portu (PB4 - [Author ID1: at Sat Dec 15 21:42:00 2001

]-[Author ID1: at Sat Dec 15 21:42:00 2001

]PB7). Wybór odbywa się na podstawie stanu linii A14 pod warunkiem, że A15 jest w stanie niskim. Dodatkowo stan wysoki tej linii adresowej blokuje sygnał ![]()

dochodzący do układów pamięci, co uniemożliwia zaadresowanie ich, gdy podany adres nie należy do zakresu przeznaczonego dla modułu pamięci dynamicznej.

--> Rysunek 5.14. [Author ID1: at Sat Dec 15 21:43:00 2001 ][Author:EK] [Author ID1: at Sat Dec 15 21:43:00 2001 ][Author ID1: at Sat Dec 15 21:43:00 2001 ]

Przykład 9.[Author ID1: at Sat Dec 15 21:43:00 2001 ]

Zaprojektować układ stronicowania dla modułu pamięci dynamicznej z przykładu 8. W danej chwili widziane są cztery strony, których numery znajdują się na wyjściach ekspandera dołączonego do portu PB.

--> Rysunek 5.15. [Author ID1: at Sat Dec 15 21:44:00 2001 ][Author:EK] [Author ID1: at Sat Dec 15 21:44:00 2001 ][Author ID1: at Sat Dec 15 21:44:00 2001 ]

Dzięki zastosowaniu ekspandera 8243 liczba użytych linii portu mikroprocesora maleje,[Author ID1: at Sat Dec 15 21:46:00 2001

] mimo tego, [Author ID1: at Sat Dec 15 21:46:00 2001

]że liczba jednocześnie aktywnych stron wzrosła dwukrotnie. Każdy port ekspandera przechowuje numer jednej strony: P4 w zakresie adresów 0000 - [Author ID1: at Sat Dec 15 21:47:00 2001

]-[Author ID1: at Sat Dec 15 21:47:00 2001

]3FFFh, P5 —[Author ID1: at Sat Dec 15 21:49:00 2001

]-[Author ID1: at Sat Dec 15 21:49:00 2001

] 4000 - [Author ID1: at Sat Dec 15 21:49:00 2001

]-[Author ID1: at Sat Dec 15 21:49:00 2001

]7FFFh, P6 —[Author ID1: at Sat Dec 15 21:49:00 2001

]-[Author ID1: at Sat Dec 15 21:49:00 2001

] 8000 - [Author ID1: at Sat Dec 15 21:49:00 2001

]-[Author ID1: at Sat Dec 15 21:49:00 2001

]BFFFh i P7 —[Author ID1: at Sat Dec 15 21:49:00 2001

]-[Author ID1: at Sat Dec 15 21:49:00 2001

] C000 - [Author ID1: at Sat Dec 15 21:49:00 2001

]-[Author ID1: at Sat Dec 15 21:49:00 2001

]FFFFh. W zależności od adresu podanego przez mikroprocesor jeden z tych numerów wykorzystuje się do zaadresowania pamięci. Wybór numeru odbywa się na podstawie stanu dwóch najstarszych linii adresowych (A14 i A15) w układzie złożonym z dwóch multiplekserów 74257 z wyjściami trójstanowymi. Linia A14 przełącza grupy wejść w tych multiplekserach, z których jeden się uaktywnia w zależności od stanu linii A15.

W poprzednim przykładzie stan niski na linii A15 blokował sygnał ![]()

. Ponieważ omawiany układ zajmuje całe 64 KB przestrzeni adresowej zewnętrznej pamięci danych, mechanizm ten nie jest już potrzebny.

2 Część I ♦ Podstawy obsługi systemu WhizBang (Nagłówek strony)

2 C:\Moje dokumenty\Korekta\Uklady mikro\1 Od autora\r5-1.doc

[Author ID1: at Sun Dec 16 23:46:00 2001 ][Author ID1: at Sun Dec 16 23:46:00 2001 ][Author ID1: at Sun Dec 16 23:46:00 2001 ][Author ID1: at Sun Dec 16 23:46:00 2001 ][Author ID1: at Sun Dec 16 23:46:00 2001 ] Czy to poprawne określenie?[Author ID1: at Sun Dec 16 23:46:00 2001 ]

[Author ID1: at Sun Dec 16 23:47:00 2001 ][Author ID1: at Sun Dec 16 23:47:00 2001 ][Author ID1: at Sun Dec 16 23:47:00 2001 ][Author ID1: at Sun Dec 16 23:47:00 2001 ][Author ID1: at Sun Dec 16 23:47:00 2001 ] Jw.[Author ID1: at Sun Dec 16 23:47:00 2001 ]

[Author ID1: at Sat Dec 15 18:56:00 2001 ][Author ID1: at Sat Dec 15 18:56:00 2001 ][Author ID1: at Sat Dec 15 18:56:00 2001 ][Author ID1: at Sat Dec 15 18:56:00 2001 ][Author ID1: at Sat Dec 15 18:56:00 2001 ][Author ID1: at Sat Dec 15 18:56:00 2001 ] Brak podpisu.[Author ID1: at Sat Dec 15 18:56:00 2001 ]

[Author ID1: at Sat Dec 15 18:58:00 2001 ][Author ID1: at Sat Dec 15 18:58:00 2001 ][Author ID1: at Sat Dec 15 18:58:00 2001 ][Author ID1: at Sat Dec 15 18:58:00 2001 ][Author ID1: at Sat Dec 15 18:58:00 2001 ] Brak podpisu.[Author ID1: at Sat Dec 15 18:58:00 2001 ]

[Author ID1: at Sat Dec 15 19:02:00 2001 ][Author ID1: at Sat Dec 15 19:02:00 2001 ][Author ID1: at Sat Dec 15 19:02:00 2001 ][Author ID1: at Sat Dec 15 19:02:00 2001 ][Author ID1: at Sat Dec 15 19:02:00 2001 ] Brak podpisu.[Author ID1: at Sat Dec 15 19:02:00 2001 ]

[Author ID1: at Sat Dec 15 19:04:00 2001 ][Author ID1: at Sat Dec 15 19:04:00 2001 ][Author ID1: at Sat Dec 15 19:04:00 2001 ][Author ID1: at Sat Dec 15 19:04:00 2001 ][Author ID1: at Sat Dec 15 19:04:00 2001 ] Brak podpisu.[Author ID1: at Sat Dec 15 19:04:00 2001 ]

[Author ID1: at Sat Dec 15 19:15:00 2001 ][Author ID1: at Sat Dec 15 19:15:00 2001 ][Author ID1: at Sat Dec 15 19:15:00 2001 ][Author ID1: at Sat Dec 15 19:15:00 2001 ][Author ID1: at Sat Dec 15 19:15:00 2001 ] Brak podpisu.[Author ID1: at Sat Dec 15 19:15:00 2001 ]

[Author ID1: at Sat Dec 15 20:39:00 2001 ][Author ID1: at Sat Dec 15 20:39:00 2001 ][Author ID1: at Sat Dec 15 20:39:00 2001 ][Author ID1: at Sat Dec 15 20:39:00 2001 ][Author ID1: at Sat Dec 15 20:39:00 2001 ] Brak podpisu.[Author ID1: at Sat Dec 15 20:39:00 2001 ]

[Author ID1: at Sat Dec 15 20:41:00 2001 ][Author ID1: at Sat Dec 15 20:41:00 2001 ][Author ID1: at Sat Dec 15 20:41:00 2001 ][Author ID1: at Sat Dec 15 20:41:00 2001 ][Author ID1: at Sat Dec 15 20:41:00 2001 ] Podpis.[Author ID1: at Sat Dec 15 20:41:00 2001 ]

[Author ID1: at Sat Dec 15 20:48:00 2001 ][Author ID1: at Sat Dec 15 20:48:00 2001 ][Author ID1: at Sat Dec 15 20:48:00 2001 ][Author ID1: at Sat Dec 15 20:48:00 2001 ][Author ID1: at Sat Dec 15 20:48:00 2001 ] Podpis.[Author ID1: at Sat Dec 15 20:48:00 2001 ]

[Author ID1: at Sat Dec 15 20:53:00 2001 ][Author ID1: at Sat Dec 15 20:53:00 2001 ][Author ID1: at Sat Dec 15 20:53:00 2001 ][Author ID1: at Sat Dec 15 20:53:00 2001 ][Author ID1: at Sat Dec 15 20:53:00 2001 ] Nie wiem, o który rysunek chodzi.[Author ID1: at Sat Dec 15 20:53:00 2001 ]

[Author ID1: at Sat Dec 15 21:02:00 2001 ][Author ID1: at Sat Dec 15 21:02:00 2001 ][Author ID1: at Sat Dec 15 21:02:00 2001 ][Author ID1: at Sat Dec 15 21:02:00 2001 ][Author ID1: at Sat Dec 15 21:02:00 2001 ] Podpis.[Author ID1: at Sat Dec 15 21:02:00 2001 ]

[Author ID1: at Sat Dec 15 21:04:00 2001 ][Author ID1: at Sat Dec 15 21:04:00 2001 ][Author ID1: at Sat Dec 15 21:04:00 2001 ][Author ID1: at Sat Dec 15 21:04:00 2001 ][Author ID1: at Sat Dec 15 21:04:00 2001 ] Jaka tabela?[Author ID1: at Sat Dec 15 21:04:00 2001 ]

[Author ID1: at Sat Dec 15 21:05:00 2001 ][Author ID1: at Sat Dec 15 21:05:00 2001 ][Author ID1: at Sat Dec 15 21:05:00 2001 ][Author ID1: at Sat Dec 15 21:05:00 2001 ][Author ID1: at Sat Dec 15 21:05:00 2001 ] [Author ID1: at Sat Dec 15 21:05:00 2001 ]Podpis.[Author ID1: at Sat Dec 15 21:05:00 2001 ]

[Author ID1: at Sat Dec 15 21:06:00 2001 ][Author ID1: at Sat Dec 15 21:06:00 2001 ][Author ID1: at Sat Dec 15 21:06:00 2001 ][Author ID1: at Sat Dec 15 21:06:00 2001 ][Author ID1: at Sat Dec 15 21:06:00 2001 ] Co to za tabela i gdzie się znajduje?[Author ID1: at Sat Dec 15 21:06:00 2001 ]

[Author ID1: at Sat Dec 15 21:21:00 2001 ][Author ID1: at Sat Dec 15 21:21:00 2001 ][Author ID1: at Sat Dec 15 21:21:00 2001 ][Author ID1: at Sat Dec 15 21:21:00 2001 ][Author ID1: at Sat Dec 15 21:21:00 2001 ] Podpis.[Author ID1: at Sat Dec 15 21:21:00 2001 ]

[Author ID1: at Sat Dec 15 21:34:00 2001 ][Author ID1: at Sat Dec 15 21:34:00 2001 ][Author ID1: at Sat Dec 15 21:34:00 2001 ][Author ID1: at Sat Dec 15 21:34:00 2001 ][Author ID1: at Sat Dec 15 21:34:00 2001 ] Podpis.[Author ID1: at Sat Dec 15 21:34:00 2001 ]

[Author ID1: at Sat Dec 15 21:43:00 2001 ][Author ID1: at Sat Dec 15 21:43:00 2001 ][Author ID1: at Sat Dec 15 21:43:00 2001 ][Author ID1: at Sat Dec 15 21:43:00 2001 ][Author ID1: at Sat Dec 15 21:43:00 2001 ] Podpis.[Author ID1: at Sat Dec 15 21:43:00 2001 ]

[Author ID1: at Sat Dec 15 21:44:00 2001 ][Author ID1: at Sat Dec 15 21:44:00 2001 ][Author ID1: at Sat Dec 15 21:44:00 2001 ][Author ID1: at Sat Dec 15 21:44:00 2001 ][Author ID1: at Sat Dec 15 21:44:00 2001 ] Podpis.[Author ID1: at Sat Dec 15 21:44:00 2001 ]

Zakres adresów |

Tryb 0 |

Tryb 1 |

Tryb 2 |

Tryb 3 |

0000-3FFFh |

„systemowa” |

„systemowa” |

strona 0 |

strona 0 |

4000-7FFFh |

strona 0 |

strona 2 |

strona 2 |

strona 1 |

8000-BFFFh |

strona 1 |

strona 3 |

strona 3 |

strona 2 |

C000-FFFFh |

„systemowa” |

„systemowa” |

„systemowa” |

strona 3 |

Numer trybu A7-A2 |

Zakres adresów A1-A0 |

Numer strony D3-D0 |

D7 |

|

000000 |

00 01 10 11 |

dowolny 0000 0001 dowolny |

1 0 0 1 |

|

000001 |

00 01 10 11 |

dowolny 0010 0011 dowolny |

1 0 0 1 |

|

000010 |

00 01 10 11 |

0000 0010 0011 dowolny |

0 0 0 1 |

|

000011 |

00 01 10 11 |

0000 0001 0010 0011

|

0 0 0 0 |

|

Wyszukiwarka

Podobne podstrony:

3640

3640

Polaczenia nierozlaczne id 3640 Nieznany

3640

3640

3640

3640

3640

3640

3640

3640 plan prezentacji do matury ustnej z j polskiego nt wybrane motywy mitologiczne w literaturze i

więcej podobnych podstron