Bramki, przerzutniki, układy sekwencyjne

Wstęp

Celem ćwiczenia jest zapoznanie się z bramkami logicznymi, układami kombinacyjnymi (układami bez pamięci) oraz sekwencyjnymi (układami z pamięcią).

Ćwiczenie rozpoczyna się od badania podstawowych rodzajów bramek oraz ich najważniejszych parametrów elektrycznych. Następnym etapem będzie zapoznanie się z zastosowaniem bramek do budowy układów kombinacyjnych oraz sekwencyjnych.

Przebieg ćwiczenia

1. Inwerter CMOS

Podstawowe parametry elektryczne bramek logicznych zostaną zobrazowane na przykładzie najprostszej bramki, którą jest inwerter realizujący negację logiczną, wykonanej w najpopularniejszej obecnie technologii wytwarzania układów scalonych - technologii CMOS (Complementary Metal Oxide Semiconductor).

a) działanie inwertera

Inwerter CMOS jest zbudowany z dwóch tranzystorów MOS o przeciwnym typie przewodnictwa: n i p. Rysunek 1 przedstawia jego schemat umieszczony w układzie pomiarowym. Jako wskaźniki stanów logicznych zastosowano diody świecące. Zakłada się, że świecenie diody oznacza stan logiczny „1”. Zastosowane woltomierze pozwalają na pomiar napięć wejściowych i wyjściowych. Dodatkowo przebieg zmian sygnałów wejściowych i wyjściowych można zaobserwować na oscyloskopie.

Rys.1. Schemat układu do badania podstawowych parametrów inwertera

Pomiary

Zmieniając napięcie wejściowe za pomocą przełącznika J1 zaobserwować zachowanie diod świecących (LED1, LED2) na wejściu i wyjściu bramki oraz wartości napięć wejściowych i wyjściowych bramki.

Opracowanie wyników

Zanotować stany logiczne na wejściu i wyjściu bramki, sformułować zasadę opisującą działanie bramki, oraz podać równanie logiczne opisujące inwerter. Zanotować wartości napięć na wejściu i wyjściu inwertera. Zaobserwować zmiany tych napięć za pomocą oscyloskopu i odpowiednie oscylogramy zamieścić w sprawozdaniu.

b) zjawiska dynamiczne - przełączanie inwertera

Układ do obserwacji i pomiarów czasów przełączania inwertera przedstawiono na rysunku 2.

Rys. 2. Schemat układu do badania efektów przełączania inwertera

Pomiary

Generator funkcyjny XFG1 przełączyć w tryb generacji przebiegu prostokątnego o częstotliwości 100MHz, amplitudzie 5V i offsecie 5V. Tak dobrać nastawy oscyloskopu, aby na ekranie zaobserwować jeden-dwa okresy przebiegu wejściowego i wyjściowego, co pozwoli to na dokładniejszy pomiar czasów propagacji bramki. Zmierzyć oscyloskopem z wykorzystaniem kursorów czasy opóźnień sygnału wyjściowego względem wejściowego w przypadku zmiany stanu wejściowego z „0” na „1” i z „1” na „0”. Następnie zmienić nastawy oscyloskopu tak aby obserwować tylko zbocze narastające lub opadające napięcia na wyjściu inwertera i dokonać pomiarów czasów narastania lub opadania.

Opracowanie wyników

W sprawozdaniu zamieścić wyniki pomiarów czasów opóźnień, narastania i opadania oraz oscylogramy wykorzystane do tych pomiarów.

Uwaga!

W przypadku pojawienia się błędów podczas symulacji należy zwiększyć nieco czas narastania i opadania przebiegów generowanych przez generator XFG1. W tym celu należy nacisnąć przycisk Set Rise/Fall Time i w otwartym oknie dialogowym ustawić czas równy np. 100ps zamiast domyślnej wartości 1ps.

c) pomiar charakterystyki przejściowej bramki

W celu dokonania obserwacji charakterystyki przejściowej inwertera należy w układzie z rys. 2:

przełączyć napięcie generatora na trójkątne oraz ustawić częstotliwość 1kHz oraz amplitudę i offset na 5V,

przełączyć oscyloskop w tryb pracy X-Y, który jest oznaczony jako B/A. Zaleca się aby wzmocnienia obu kanałów były jednakowe.

Pomiary i opracowanie wyników

Zanotować wartość napięcia progu przełączania bramki logicznej, tj. napięcie wejściowe, przy którym następuje przełączenie poziomu logicznego na wyjściu bramki. Zamieścić w sprawozdaniu otrzymaną charakterystykę.

2. Podstawowe bramki logiczne

W tej części ćwiczenia będą badane podstawowe bramki logiczne. Zadanie polega na zaobserwowaniu funkcji logicznych realizowanych przez poszczególne bramki. Schematy pomocne do analizowania działania bramek zamieszczono na rys. 3.

Rys. 3. Schematy układów do badań bramek

Pomiary

Zaobserwować stany logiczne na wyjściu każdej bramki dla wszystkich kombinacji wejściowych stanów sygnałów.

Opracowanie wyników

Zanotować stany logiczne na wejściach i wyjściach bramek w formie tabeli prawdy. Sformułować zasady opisujące działanie każdej z bramek, podać odpowiednie równania logiczne.

3. Przykładowe układy kombinacyjne

Układy kombinacyjne przebadamy na podstawie bardzo prostych przykładów. Zadaniem studentów jest zrealizowanie jednej z dwóch poniższych funkcji przy pomocy poznanych wcześniej bramek:

funkcja ALBO (EXOR)

,funkcja ALBO-NIE (EXNOR)

.

Pomiary i opracowanie wyników

Podać tabelę prawdy realizowanej funkcji oraz narysować schemat i sprawdzić działanie układu.

4. Przykładowe układy sekwencyjne

Układy sekwencyjne charakteryzują się posiadaniem pamięci, czyli wyjście takich układów nie zależy tylko od wektorów podawanych na wejście, ale także od stanów wewnętrznych tych układów. Analizę takich układów zaczniemy od najprostszego układu pamiętającego jakim jest przerzutnik RS.

a) przerzutnik RS

Zasada działania przerzutników zostanie zobrazowana na przykładzie przerzutnika RS, który jest zbudowany z dwóch bramek NOR połączonych jak na rys. 4. Jako wskaźniki stanów logicznych zastosowano, podobnie jak poprzednio, diody świecące. Ponadto na rysunku zaznaczono i nazwano wejścia oraz wyjścia przerzutnika. Do budowy przerzutnika zaleca się użyć elementów z biblioteki MISC.

Rys. 4. Schemat układu do badania przerzutnika RS

Pomiary

Zmieniając wejściowe stany logiczne za pomocą przełączników J1 i J2 zaobserwować

zachowanie się diod świecących na wejściach i wyjściach przerzutnika. Ponieważ odpowiedź układu zależy nie tylko od sygnałów wejściowych, należy zwrócić uwagę aby przeanalizować przypadki dla różnych wartości zapisanych w przerzutniku, np. podać na wejście układu wektor (1, 0) dwa razy: gdy na wyjściu przerzutnika jest „0” i „1”.

Opracowanie wyników

Zanotować stany logiczne na wejściach i wyjściach - podać tabelę prawdy przerzutnika. Sformułować zasadę opisującą pracę przerzutnika. Wyjaśnić zachowanie się przerzutnika w przypadku jednoczesnego wystąpienia jedynek na wejściach R i S.

Uwaga!

W przypadku włączenia zasilania (rozpoczęcie symulacji) przy zerach logicznych ustawionych na wejściach R i S może wystąpić migotanie diod sygnalizujących stany wyjściowe. Na wyjściach generowany jest przebieg prostokątny o częstotliwości uzależnionej od czasów propagacji bramek NOR użytych do budowy przerzutnika. Jest to efekt wynikający z zasady działania programu Multisim, w którym założono identyczne czasy propagacji bramek. W rzeczywistym układzie sytuacja taka praktycznie nie wystąpi, ponieważ czasy propagacji bramek oraz czasy narastania i opadania zboczy przebiegów różnią się nieco, więc jakiś stan stabilny („0” bądź „1”) zostanie ustalony na wyjściach.

b) zatrzask D (D-latch)

Na przykładzie przerzutnika D wyzwalanego poziomem zostanie zobrazowana synchronizacja wysokim stanem logicznym. Układ pomiarowy przedstawiono na rysunku 5.

Rys. 5. Schemat układu do badania przerzutnika D wyzwalanego poziomem

Pomiary

Zmieniając wejściowe stany logiczne za pomocą przełączników J1 i J2 zaobserwować zachowanie się diod świecących na wejściach i wyjściach przerzutnika. Co jest na wyjściu przerzutnika podczas gdy na wejściu EN panuje „1”, „0”, lub zmienia się stan logiczny (zbocze). Podobnie jak dla poprzedniego przykładu należy przeanalizować przypadki dla różnych stanów zapisanych w przerzutniku.

Opracowanie wyników

Zanotować stany logiczne na wejściach i wyjściach - podać tabelę prawdy przerzutnika. Sformułować zasadę opisującą pracę przerzutnika. Na podstawie obserwacji wyjaśnić, na czym polega synchronizacja poziomem.

c) przerzutnik D (D flip-flop)

Na przykładzie przerzutnika D wyzwalanego zboczem zostanie zobrazowana synchronizacja zboczem sygnału. Podstawowy schemat pomiarowy przedstawiono na rysunku 6.

Rys. 6. Schemat układu do badania przerzutnika D wyzwalanego zboczem

Pomiary

Zmieniając wejściowe stany logiczne za pomocą przełączników J1 i J2 zaobserwować zachowanie się diod świecących na wejściach i wyjściach przerzutnika. Co jest na wyjściu przerzutnika podczas gdy na wejściu zegara (oznaczonym trójkątem) panuje „1”, „0”, lub zmienia się stan logiczny (zbocze). Należy przeanalizować przypadki dla różnych stanów zapisanych w przerzutniku.

Opracowanie wyników

Zanotować stany logiczne na wejściach i wyjściach - podać tabelę prawdy przerzutnika. Sformułować zasadę opisującą pracę przerzutnika. Na podstawie obserwacji wyjaśnić, na czym polega synchronizacja zboczem. Czym różnią się przerzutnik D od zatrzasku D?

Powyższe zadanie można zrealizować także za pomocą generatora, oscyloskopów oraz analizatora stanów logicznych. Schemat pomiarowy przedstawiono na rysunku 7.

Rys. 7. Schemat układu do badania przerzutnika D

za pomocą oscyloskopów i analizatora stanów logicznych

Pomiary

Generator funkcyjny XFG1 przełączyć w tryb generacji przebiegu prostokątnego. Ustawić częstotliwość 1kHz, amplitudę 2,5V i offst 2,5V. Podstawę czasu oscyloskopów ustawić na 1ms/Div, a wzmocnienia we wszystkich kanałach na 2V/Div. W oknie analizatora stanów logicznych ustawić parametr Clocks/Div na 16. Po włączeniu zasilania (start symulacji) kilkanaście razy przełączyć przełącznik J1 (klawiszem D) obserwując zmiany sygnałów wejściowych i wyjściowych przerzutnika. Za pomocą oscyloskopów zaobserwować przebiegi wejściowe i wyjściowe przerzutnika. Ponownie zaobserwować przebiegi wejściowe i wyjściowe przerzutnika wykorzystując analizator stanów logicznych.

Opracowanie wyników

Zamieścić w sprawozdaniu oscylogramy przebiegów wejściowych i wyjściowych przerzutnika (można wykorzystać Grapher z menu View). W przypadku oscyloskopów należy znaleźć „ten sam” przedział czasu. Zaznaczyć na rysunkach momenty zmiany stanu wyjściowego przerzutnika. Wyjaśnić, na czym polega synchronizacja (wyzwalanie) przerzutnik zboczem.

d) przerzutniki JK i T

Oprócz uprzednio poznanych przerzutników w technice cyfrowej stosuje się także przerzutniki JK i T, których symbole graficzne przedstawiono na rysunku 8. W oparciu o poprzednie schematy pomiarowe należy zbadać działanie tych przerzutników.

Rys. 8. Symbole przerzutników JK i T

Pomiary

Wykorzystując poprzednie schematy pomiarowe należy zaobserwować stany logiczne na wejściach i wyjściach przerzutników. Co jest na wyjściu przerzutnika podczas gdy na wejściu zegara (oznaczonym trójkątem) panuje „1”, „0”, lub zmienia się stan logiczny (zbocze). Należy przeanalizować przypadki dla różnych stanów zapisanych w przerzutniku.

Opracowanie wyników

W sprawozdaniu podać stany logiczne na wejściach i wyjściach przerzutników w formie tabel prawdy. Sformułować zasady opisujące pracę przerzutników.

e) rejestr

Wykorzystując przerzutniki D można zbudować najprostszy rejestr służący do przechowywania danych. Układ taki pełni rolę pamięci, jednakże ze względu na nadmierną złożoność nie należy go traktować jako „cegiełkę” do budowy układów pamięci danych. Jako pomięć służącą do przechowywania danych „na dużą skalę” (np.: pamięć komputerowa) produkuje się specjalne układy pamięciowe o bardzo prostej strukturze komórki. Pozwala to na uzyskanie bardzo dużych pojemności pamięci w jednym układzie scalonym. Przykładem rejestru zbudowanego z przerzutników D flip-flop może być układ scalony 74LS374 wykonany w technologii TTL. Jest on zbudowany z ośmiu przerzutników D-ff. Zatem ma osiem wejść i wyjść, a wejścia zegarowe przerzutników są połączone razem. Schemat do obserwacji pracy tego układu przedstawiono na rysunku 9.

Rys. 9. Schemat układu do badania rejestru

Pomiary

Należy wybrać układ 74LS374N z biblioteki TTL. Zmieniając wejściowe stany logiczne za pomocą przełączników zaobserwować zachowanie się diod świecących na wejściach i wyjściach rejestru. Zwrócić uwagę na moment zmiany stanów wyjściowych.

Opracowanie wyników

Sformułować zasadę opisującą pracę rejestru. Podać warunek zmiany stanów wyjściowych. Jakie tryby pracy można wyróżnić dla tego rejestru?

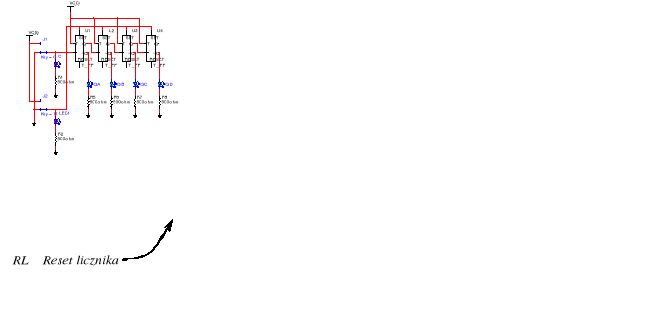

f) licznik 4-bitowy z przerzutnikami T flip-flop

Układy, które zliczają liczbę impulsów wejściowych nazywane są licznikami. Na rysunku 10 przedstawiono 4-bitowy licznik zbudowany w oparciu o przerzutniki T flip-flop. Wejściem licznika jest wejście zegarowe pierwszego przerzutnika (przełącznik J1 - klawisz C), a wyjściami są wyjścia zanegowane przerzutników. Liczba zliczonych impulsów jest reprezentowana binarnie, przy czym najmłodszy bit to wyjście QA. Licznik dodatkowo wyposażono w wejście zerujące sterowane przełącznikiem J2 - klawisz R.

Rys. 10. Schemat układu do badania licznika

Pomiary

Zmieniając kilkanaście razy stan logiczny za pomocą przełącznika J1 zaobserwować zachowanie się diod świecących na wyjściach licznika. Zwrócić uwagę na moment zmiany stanów wyjściowych. Sprawdzić wpływ stanu logicznego na wejściu RL (Reset Licznika - przeł. J2) na pracę licznika.

Opracowanie wyników

Zamieścić w sprawozdaniu tabelę stanów wyjściowych dla kolejnych impulsów wejściowych (uzyskanych przez przełączanie J1). Omówić znaczenie wejścia RL i jego wpływ na pracę licznika.

Wyszukiwarka

Podobne podstrony:

opracowanie programowanie obiektowe, Politechnika Poznańska, Studia- materiały, Semestr 5, PO

WSZECHWIEDZA OC, Politechnika Poznańska, Studia- materiały, Semestr 2, Obróbka plastyczna- wykłady,

WSZECHWIEDZA S i OC, Politechnika Poznańska, Studia- materiały, Semestr 2, Obróbka plastyczna- wykła

TEST ROBOTY, Politechnika Poznańska, Studia- materiały, Semestr 5, CiEP, egzamin, test robotyka, Rob

Tworzywa polimerowe ściąga druk, Politechnika Poznańska, Studia- materiały, Semestr 2, Przetwórstwo

sc egzm diag do nauki, Politechnika Poznańska, Studia- materiały, Semestr 5, DiW, Egzamin, EGZAMIN W

2008724720218-opracowanie wibro, Politechnika Poznańska, Studia- materiały, Semestr 5, DiW, Egzamin,

MiUTopracowanie, Politechnika Poznańska, Studia- materiały, Semestr 5, MiUT, MUT

produkty, Politechnika Poznańska, Studia- materiały, Semestr 2, Przetwórstwo tworzyw sztucznych- ćwi

WSZECHWIEDZA S, Politechnika Poznańska, Studia- materiały, Semestr 2, Obróbka plastyczna- wykłady, M

sprawko materiały 4, studia, studia Politechnika Poznańska - BMiZ - Mechatronika, 1 semestr, materia

materialoznastwo-sciaga, studia, studia Politechnika Poznańska - BMiZ - Mechatronika, 1 semestr, mat

sprawko materiały 3, studia, studia Politechnika Poznańska - BMiZ - Mechatronika, 1 semestr, materia

W4 Materialy i cywilizacje(1), studia, studia Politechnika Poznańska - BMiZ - Mechatronika, 1 semest

108. Wyznaczanie modułu Younga metodą ugięcia, studia, studia Politechnika Poznańska - BMiZ - Mechat

Klasyfikacja stali wg składu chemicznego, studia, studia Politechnika Poznańska - BMiZ - Mechatronik

więcej podobnych podstron