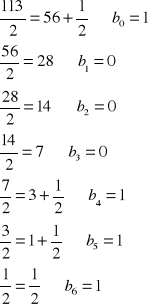

1.Zapisać liczbę 113 w kodzie binarnym, BCD i Graya oraz liczbę 113 w zapisie uzupełnień do 113. Wszystkie kody przedstawić w zapisie zero-jedynkowym i heksadecymalnym.

2.Omówić właściwości tranzystora bipolarnego bipolarnego zakresie odcięcia i nasycenia.

W stanie nasycenia oba złącza tranzystora są spolaryzowane w kierunku przewodzenia. Złącze kolektor-baza zaczyna przewodzić (przy przewodzącym drugim złączu), gdy napięcie C-E osiągnie wartość napięcia nasycenia ![]()

. ![]()

wynosi od ok. 0,20 do kilku V. Stan nasycenia odpowiada zwarciu na zaciskach C-E. Charakteryzuje go duża wartość ![]()

przy bardzo małym ![]()

. Rezystancja wyjścia ![]()

jest mała (w nasyceniu). Wynosi od ułamka ![]()

do kilkuset ![]()

.

W stanie nieprzewodzenia (odcięcia) obydwa złącza tranzystora są spolaryzowane w kierunku wstecznym. Odpowiada to rozwarciu na zaciskach kolektor-emiter. Płynący prąd jest mały. Granicę między zakresami aktywnymi i odcięcia stanowi prąd zerowy ![]()

.

![]()

-nap. Progowe (dla krzem. 0,5-0,8V)

Transformator nasycony: ![]()

Transformator odcięty ![]()

-duże, ![]()

-duże

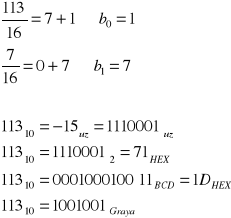

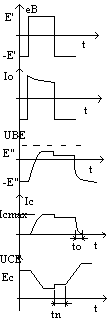

3.Narysować i omówić przebieg napięć wyjścia klucza z tranzystorem bipolarnym npn w układzie WE, sterowanego napięciem prostokątnym.

Klucz tranzystora dostarcza energię odpowiedniej częstotliwości do obciążenia przy możliwie najmniejszych stratach.

Napięcie wyjściowe jest opóźnione względm napięcia sterującego. Czas opadania ![]()

wynika z rozkładu pojemności złącza B i CB. W tym czasie ![]()

maleje od![]()

do ![]()

; następuje narastanie napięcia.

W czasie narastania I napięcie wyjściowe maleje. Czas wzrostu prądu wynika z czasu przejścia nośników przez obszar bazy.

tn- czas magazynowania (wyjścia ze stanu nasycenia)

4.Narysować i omówić przebieg napięcia wyjściowego klucza z tranzyt. MOSFET indukowanym kanałem n w ukł. wspólnego źródła sterowanego napięciem prostokątnym:

Tranzystor unipolarny MOSFET kanałem n indukowanym:

S-źródło D- dren G- bramka B- podłoże K- kanał indukowany

Gdy do bramki doprowadzone jest napięcie ujemne w stosunku do podłoża B, wówczas źródło zostaje oddzielone od D drenu przeciwnie spolaryzowanego zł. PN- stan komutacji. Prąd SD stanowi wówczas pr. Wsteczny jednego ze złączy ma znikomą wartość. Znikomy prąd płynie też przy UGS =0.

Gdy do bramki dopr. napięcie + w stosunku do podłoża wtedy po przekroczeniu napięcia progowego UT=-5V powstaje przy powierzchni warstwa inwersyjna- indukowany kanał, który po doprowadzeniu napięcia polaryzacyjnego SD umożliwia przepływ prądu od S do D. Ze wzrostem UGS prą d drenu wzrasta

Stała czasowa decyduje o czasie włączenia lub wyłączenia kanału . Po ustaleniu się UG następuje etap przełączania tranzystora- ustalenie się UD. Kondensator rozładowuje się przez zmienną rezystancję kanału.

5.Omówić przebieg charakt. wyjściowych tranzystora MOSFET (dlaczego raz strome raz płaskie)

Tranzystor MOSFET jest to unipolarny tranzystor z izolowaną bramką (najczęściej SiO2)

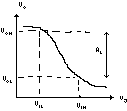

Charakterystyka wyjściowa:

Zależnie od relacji między napięciami Ut, Uas, Uds tranzystory mogą pracować w dwóch trybach:

nasycenie (płaskie), gdy

nienasycone (strome), gdy

Charakterystyki w zakresie liniowym (nienasycenia), gdy S jest uziemione (Us=0) to ![]()

. W zakresie nasycenia ![]()

β- współczynnik transkonduktancji, zależny od struktury tranzystora, β=µ*Ci*z gdzie: µ-ruchliwość nośników w krzemie; Ci- pojemność warstwy izolatora przypadająca na jednostkę powierzchni z-szerokość kanału

l-długość kanału Ut- napięcie progowe wyznaczone praktycznie jako Usg, przy którym prąd drenu ma określoną wartość

wzmocnienie = transkonduktancja ![]()

-tryb nienasycenia ![]()

-tryb nasycenia ![]()

Konduktancja wyjściowa jest to przewodność kanału, czyli nasycenie ch-ki wyjściowej w określonym punkcie pracy![]()

-tryb nienasycenia ![]()

-tryb nasycenia z def. ![]()

=0, ale ze względu na zjawisko skracania elektrycznej długości kanału ![]()

>0

6.Wyjaśnić pojęcie obciążalności bramek logicznych:

Obciążalność bramek logicznych jest to maksymalna liczba wejść innych układów, które można dołączyć do 1 wyjścia danego układu. Liczba ta zależy od maksym. wartości prądów wyjściowych i wejściowych danego układu i np. dla TTL=10

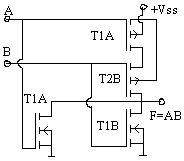

7.Narysować schemat bramki NAND (NOR) w techn.. CMOS, omówić jej działanie.

Bramka NAND w ukł. CMOS (pary komplementarne tr MOS).

Gdy na obu wejściach A i B jest stan jedynki logicznej (napięcie bliskie Vss). Oba dolne tranzystory są przewodzące, o górne odcięte i na wyjściu F jest stan „0”. Gdy choć na jednym wejściu jest 0 logiczne powoduje to odcięcie odpowiedniego szeregowego dolnego tranzystora, a przewodzenie górnego. Prowadzi to do pojawienia się stanu „1” na wyjściu.

Bramka NOR w układzie CMOS.

Gdy na obu wejściach A i B jest poziom napięcia odpowiadający „0” logicznemu oba górne tranzystory ![]()

i ![]()

są przewodzące, a dolne odcięte. Na wyjściu F mamy „1” logiczną. Gdy choć na jednym wejściu jest „1” logiczna powoduje to przewodzenie jednego z dolnych szeregowych tranzystorów, a odcięcie górnego, co prowadzi do pojawienia się stanu „0” na wyjściu F.

8.Zasada budowy bramek CMOS, właściwości:

Ukł. CMOS zbudowane są par tranzystorów unipolarnych przeciwstawnych kanałem p i n. Ukł. inwertora CMOS jest ukł. wejściowym dla podstawowych bramek logicznych. Gdy na wej, jest 0 to T1 jest zablokowany, a T2 przewodzi na wyj. b panuje nap. Ed, czyli „1” logiczne. Gdy na wej. Jest 1 to T1 przewodzi, a T2 jest zatkany i na wyj. b panuje napięcie 0V. Czyli stan „0” logicznego. Układ CMOS w odróżnieniu od bramek z kanałem jednego typu odznaczają się znacznie krótszymi czasami przełączania (50ns). Stroma ch-ka przejściowa zapewnia znacznie większe marginesy zakłóceń. Bramki CMOS charakteryzują się znacznie większym wzmocnieniem logicznym i większą możliwością realizacji ukł. wielowejściowych, zapewniają poziomy logiczne niezależne od liczby wejść i obciążenia. Podstawową zaletą ukł. CMOS jest znikomy pobór mocy. W obu stanach logicznych przez bramkę nie płynie prąd, gdyż bądź dolne bądź górne tranzystory są odcięte.

9. Wyjaśnić pojęcie czasów propagacji bramki logicznej, podać rząd wartości tego parametru dla współczesnych bramek logicznych.

![]()

Wielkość określająca zbiorowy czas trwania wszystkich zjawisk z opóźnieniem włącznie zachodzących przy przetłaczaniu bramki .

![]()

- czas przejścia ze stanu H do L, liczony jako czas między połową zboczy imp. Wejść i wyjścia (czas propagacji do stanu niskiego na wyjściu)

TTL ![]()

ECL ![]()

CMOS ![]()

|

10. Wyjaśnić pojęcie gwarantowanego i typowego marginesu zakłóceń. Czy wartość marginesu zakłóceń całkowicie określa odpowiedź na zakłócenie?

Margines zakłóceń M określa odpowiednią wartość sygnału zakłócającego, dodany do sygnału wejściowego nie spowoduje nieprawidłowej pracy układu.

Wartości gwarantowane

- dla st. L:![]()

-dla st. H: ![]()

przy zakłóceniu >![]()

gwarantowane jest L na wyjściu

przy zakłóceniu <![]()

gwarantowane jest H na wyjściu

Wart gwarantowanego marginesu zakłóceń jest podawana dla najlepszego umownego przypadku i najbardziej niekorzystnych wartości parametrów. Wartość typowa marginesu zakłóceń podawana jest przy 25˚C i typowych napięciach zasilania i obciążenia. Wartość marginesu zakłócenia nie zawsze określa całkowicie odporność na zakłócenie, bo wpływ maja także inne czynniki np. impedancja obwodu powstałą w wyniku połączenia bramki wejściowej z wyjściową poprzez indukcję magnetyczna doprowadzony zostaje sygnał zakłócający.

11. Czy rezystancja wyjściowa układu wpływa na odporność układu na zakłócenia?

|

Tak, R wyjściowa wpływa na odporność układu na zakłócenia, z marginesem zakłóceń jest powiązane. Gdy zmieniamy Rc zmieniamy też poziom ![]()

.

![]()

12. Co to są dynamiczne bramki MOS (zastosowanie, działanie - schemat Inwertera)

Układ typu MOS stosuje się przy realizacji złożonych funkcji cyfrowych. Duże poziomy impedancji umożliwiają realizacje dynamicznych bramek. Bramka T2 jest przyłączona do wejścia zegarowego, T na którym z określoną częstotliwością pojawiają się ujemne impulsy. Wyjście bramki jest połączone z punktem A tranzystorów T1, T2 przez kanał T3. W układzie jest wykorzystywana rozproszona pojemność C obciążająca bramkę. Gdy na T jest nap.=0V wówczas T1 i T2 są odcięte i wyjście jest podłączone do punktu A. W chwili gdy nap. Na T =-Eo T1 i T2 sa połączone jak w statycznym inwerterze, T3 zaś przewodzi i przez rezystancje jego kanału C ładuje sie do napięcia odpowiadającego stanowi punktu A. Po zakończeniu ujemnego impulsu zegara kanał T3 zostaje ponownie odcięty i nap. Na C utrzymuje się dzięki wysokiemu poziomowi impedancji wyjściowej i wejściowej bramkę obciążających. Zaleta: pobór mocy jedynie w czasie trwania ujemnego trwania impulsu zegarowego w przypadku, gdy na wyjściu jest 0 mały pobór mocy (jak w CMOS), lecz mamy tranzystory o jednym typie kanału. Wada: możliwość zmiany stanu jedynie w chwili pojawienia sie ujemnego impulsu zegarowego.

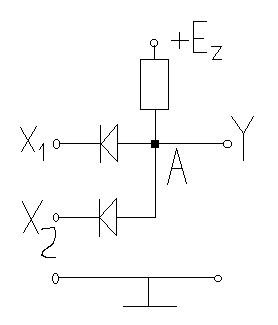

13. Narysować schemat i omówić działanie diodowych bramek sumy i iloczynu

Bramka sumy

X1 X2 Y

0 0 0

1 0 1

0 1 1

1 1 1

Gdy napięcie na X1 lub/i będzie większe od 0,7V to znaczy na wejściach X1 lub/i X2 będzie poziom wysoki, jedynka logiczna to na wyjściu Y otrzymamy napięcie odpowiadające również stanowi wysokiemu „1”. Jeżeli natomiast na obu wejściach X1, X2 napięcie<0,7V, co odpowiada „0” logicznemu to na wyjściu otrzymamy poziom napięcia odpowiadający „0”.

Bramka iloczynu

X1 X2 Y

0 0 0

0 1 0

1 0 0

1 1 1

Gdy napięcie na X1 lub/i X2 będzie mniejsze od 0,7V to znaczy będzie odpowiadać „0” logicznemu to potencjał w punkcie A będzie wynosił 0,7V czyli na wyjściu Y będziemy mieli poziom napięcia odpowiadający „0” logicznemu. Jeżeli na X1 i X2 napięcie>0,7V co odpowiada stanom wysokim na wejściach to potencjał w punkcie A≈+Ez (5V) co odpowiada poziomowi wysokiemu na wyjściu Y

14. Jakie są zakresy napięć dla poziomów logicznych na wyjściach układu TTL.

Układy TTL (ang. Transistor-Transmitor Ligic) Posiadają napięcie zasilania 5V (4.75 do 5,25), przy poborze mocy małym ok. 10mV na bramkę.

Dla wejść poziomy napięć posiadają:

„0” - 0V do 0,8V

„1” - 2V do 5V

dla wyjść:

„0” - 0V do 0,4V

„1” - 2,4V do 5V

![]()

- amplituda logiczna

Przeciętny egzemplarz w normalnych warunkach ma parametry korzystniejsze (większe zakresy poziomów wejściowych i mniejsze zakresy poziomów wyjściowych).

Typowe wartości:

Wyj: ![]()

![]()

Wej: ![]()

![]()

Wyszukiwarka

Podobne podstrony:

PIII - teoria, Studia, SiMR, II ROK, III semestr, Elektrotechnika i Elektronika II, Elektra, Elektro

elektra P4, Studia, SiMR, II ROK, III semestr, Elektrotechnika i Elektronika II, Elektra, Elektronik

elektra M4, Studia, SiMR, II ROK, III semestr, Elektrotechnika i Elektronika II, Elektra, Elektronik

jasiek pytania, Studia, SiMR, II ROK, III semestr, Elektrotechnika i Elektronika II, Elektra, Elektr

M2, Studia, SiMR, II ROK, III semestr, Elektrotechnika i Elektronika II, Elektra, Elektronika i Elek

Wnioski do stanu jałowego trafo, Studia, SiMR, II ROK, III semestr, Elektrotechnika i Elektronika II

Elektra M-2spr, Studia, SiMR, II ROK, III semestr, Elektrotechnika i Elektronika II, Elektra, Elektr

elektra M5, Studia, SiMR, II ROK, III semestr, Elektrotechnika i Elektronika II, Elektra, Elektronik

Transformator, Studia, SiMR, II ROK, III semestr, Elektrotechnika i Elektronika II, Elektra, Elektro

Pomiary-protokół, Studia, SiMR, II ROK, III semestr, Elektrotechnika i Elektronika II, Elektra, Elek

elektra M6a, Studia, SiMR, II ROK, III semestr, Elektrotechnika i Elektronika II, Elektra, Elektroni

Wnioski M2, Studia, SiMR, II ROK, III semestr, Elektrotechnika i Elektronika II, Elektra, Elektronik

pytania na egzamin z elektrotechniki ii ciag 1, Studia, SiMR, II ROK, III semestr, Elektrotechnika i

Tabele-elektraP1, Studia, SiMR, II ROK, III semestr, Elektrotechnika i Elektronika II, Elektra, Elek

elektra M4 tab, Studia, SiMR, II ROK, III semestr, Elektrotechnika i Elektronika II, Elektra, Elektr

Sprawko z P2, Studia, SiMR, II ROK, III semestr, Elektrotechnika i Elektronika II, Elektra, Elektron

elektra p1, Studia, SiMR, II ROK, III semestr, Elektrotechnika i Elektronika II, Elektra, Elektronik

więcej podobnych podstron