Image119

czasu propagacji sygnału do stanu 0 na wyjściu od temperatury dla przerzutni-ka D przedstawiono na rys. 4.59. Czas ustalania ts przerzutnika 74 wynosi 20 ns, natomiast czas przetrzymywania th — 5 ns.

Podobnie do przerzutnika 74 zbudowany jest przerzutnik H74. W tablicy 4.6 przedstawiono podstawowe parametry dynamiczne przerzutników 74 i H74.

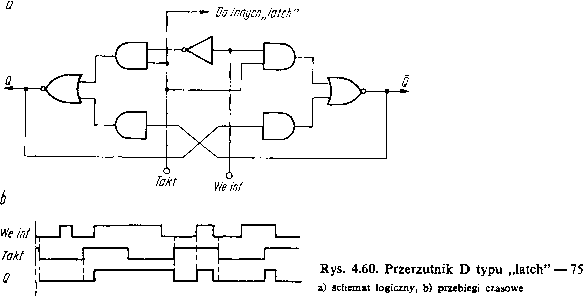

4.2.4. Przerzutnik „latch” (zatrzask)

W układach pamięciowych często jest stosowany przerzutnik D typu „latch” wyzwalany poziomem — rys, 4.60. Przerzutnik ten różni się od przerzutnika D tym, że w czasie, gdy na jego wejściu zegarowym panuje napięcie o poziomie jedynki logicznej, wówczas wejście informacyjne (D) oddziałuje bezpośrednio na wyjście fi. Wszystkie zmiany stanów wejścia A zachodzące w tym czasie są natychmiast powtarzane przez stany wyjścia fi, Kiedy stan wejścia zegarowego zmieni się z 1 na 0, wyjście fi pozostaje w stanie logicznym, odpowiadającym stanowi wejścia D występującemu bezpośrednio przed pojawieniem się zmiany z 1 na 0 sygnału zegarowego. Stan wyjścia fi nie ulega zmianie tak

długo, jak długo potencjał wejścia zegarowego nie wzrośnie ponownie do poziomu jedynki logicznej. Taka odmiana przerzutnika znajduje zastosowanie głównie w układach pamięciowych i rejestrach okresowo przechowujących informację. Wadą układu jest to, że w stanie 1 przebiegu synchronizującego na wyjście układu przenoszą się wszystkie zmiany stanu wejścia D (również zakłócenia).

9 Układy TTL

Wyszukiwarka

Podobne podstrony:

Image087 tpHL — czas propagacji do stanu 0 na wyjściu; jest to czas mierzony od chwili osiągnięcia p

w stanie q, a z czubka stosu zdjąłeś b, to przejdź do stanu q a na czubek stosu włóż słowo w. Taki a

http ://l ay er. uci. agh. edu. pl/ maglay/wrona sów jest mniejszy od czasu propagacji sygnału w bra

9. Stosunek mocy sygnału do s/umu na wejściu odbiornika horyzontowej linii radiowej po zmianie

Image426 Rys. 4.506. Zależność stałości czasu trwania impulsu wyjściowego od temperatury Rys. 4

96 pokazano na rys. 7.3a. Czas inkubacji do osiągnięcia przez szczelinę jej krytycznego rozwarcia 5*

96 pokazano na rys. 7.3a. Czas inkubacji do osiągnięcia przez szczelinę jej krytycznego rozwarcia 5*

img074 (31) I Na rysunku 3.20 przedstawiono zależność rozpuszczalności tlenu w vs•* dzie od temperat

056 5 Przykładowy przebieg ruchu tłoka i wypornika przedstawiono na rys. Z.14. Czas zatrzymania wypo

28630 img074 (31) I Na rysunku 3.20 przedstawiono zależność rozpuszczalności tlenu w vs•* dzie od te

28630 img074 (31) I Na rysunku 3.20 przedstawiono zależność rozpuszczalności tlenu w vs•* dzie od te

Rozszerzalność cieplna - zdolność do zmiany objętości pod wpływem temperatury dla /= 10°C ip= 10- Pa

page02 (3) 14. Przedstawić na wykresach zależność entalpii reakcji od temperatury&

img074 (31) I Na rysunku 3.20 przedstawiono zależność rozpuszczalności tlenu w vs•* dzie od temperat

więcej podobnych podstron