Image294

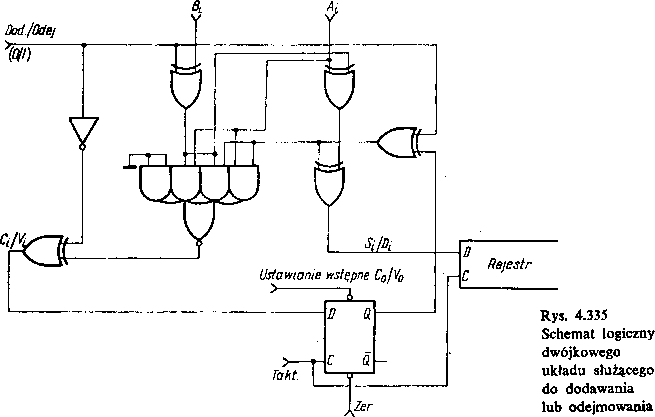

realizację operacji dodawania. Układ przedstawiony na rys. 4.335 umożliwia realizację operacji dodawania i odejmowania.

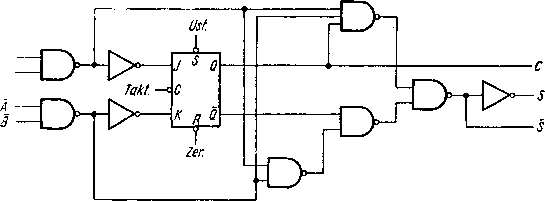

Na rysunku 4.336 przedstawiono schemat logiczny sumatora z zastosowaniem przerzutnika JK. Jeśli AiBi — 1, to przerzutnik przeniesienia — niezależnie od stanu poprzedniego — powinien być ustawiony w stan 1, natomiast jeśli A{BX — = 1, to w stan 0. W innych przypadkach stan przerzutnika nie powinien ulec zmianie.

Cb

Rys. 4.336. Schemat logiczny dwójkowego sumatora szeregowego z wykorzystaniem przerzutnika JK-MS

Na rysunku 4.337 przedstawiono układ analogiczny jak na rys. 4.336, służący do dodawania albo odejmowania. Szybsze odpowiedniki układu przedstawionego na rys. 4.337 są podane na rys. 4.338 i 4.339. Sumator szeregowy przedstawiony na rys. 4.339 służy do realizacji operacji A ± B. W sumatorze należy zastosować taki układ sumy, jak w sumatorze poprzednim. Przerzutnik przeniesienia powinien być ustawiony w stan 1, niezależnie od poprzedniego stanu, jeśli AXBX = = 1 — dla operacji dodawania, albo AXBX = 1 — dla operacji odejmowania.

Wyszukiwarka

Podobne podstrony:

Image325 Układ przedstawiony na rys. 4.372, spełniający równanie (14), jest układem najszybszym, gdy

Image446 Funkcję, która ma być spełniona przez układ przedstawiono na rys. 4.538a, natomiast symbol

1. Dla jakich wartości A* układ przedstawiony na rys. 1 będzie stabilny? 2.

CCF20110506�009 1 cd. tabl. 7.17.2.2. Przetwornice transformatorowe Układ przedstawiony na rys. 7.12

6.1. UKŁADY PODSTAWOWE. WŁAŚCIWOŚCI I WIELKOŚCI ZALEŻNE 291 Układ przedstawiony na rys. 6.7a został

Image073 Układ służący do realizacji tej funkcji, zbudowany z bramek I (AND), LUB (OR), NIE (NOT) pr

Image050 operację sumy logicznej Y, jest przedstawiony na rys. 3.4. Napięcie baterii roz-świeci żaró

Image114 Przerzutnik JK-MS — 72 przedstawiono na rys. 4.53. Bramki 1 i 2 realizują funkcje K = KX*K2

Image183 Struktura logiczna układów FPLA Schemat logiczny typowego układu FPLA przedstawiono na rys.

Image229 Schemat logiczny dekady liczącej w kodzie 8421 przedstawiono na rys. 4.230. Maksymalna częs

Image250 Schemat logiczny synchronicznego dwukierunkowego licznika dwójkowego (193) przedstawiono na

Image262 nęgo z dekad liczących 192 i nastawników dziesiętnych, zawierających enko-dery, przedstawio

Image277 oraz przebiegi napięć na wyjściu W przedstawiono na rys. 4.309. Blokadę zliczania zrealizow

Image355 Implementacje układów realizujących funkcje (3) oraz funkcje (4) przedstawiono na rys. 4.40

Image371 Schemat logiczny układu realizującego powyższe funkcje przełączające przedstawiono na rys.

więcej podobnych podstron