Image325

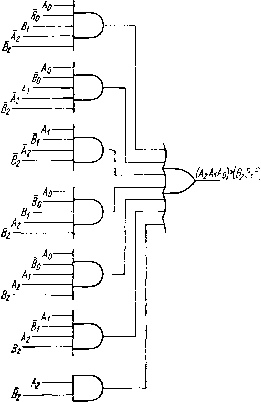

Układ przedstawiony na rys. 4.372, spełniający równanie (14), jest układem najszybszym, gdyż sygnał propaguje albo przez dwie bramki, albo przez dwie bramki i inwerter.

Rys. 4.372. Schemat logiczny układu realizującego wyrażenie (14)

Scalone komparatory równoległe liczb 4-bitowych

W ramach serii standardowej TTL jest produkowany układ scalony 85, służący do równoległej komparacji liczb 4-bitowych. Jest to komparator uniwersalny, umożliwiający porównanie dwu liczb dwójkowych lub liczb dziesiętnych przedstawionych w kodzie 8421 BCD. Komparator ten (rys. 4.373) ma oprócz wejść:

|

f_ |

A3 | |

|

az 85 | ||

|

*t | ||

|

*0 | ||

|

- |

A>8 A>B | |

|

A=8 A-B | ||

|

£ |

— |

A<8 A<8 |

|

B, R. | ||

|

^ - |

B Bq |

Rys. 4.373. Schemat blokowy równoległego komparatora scalonego 85

A3, A2, A19 A0 i wejść: Bz, Bz, B19 B0 dla porównywanych liczb A i B również wejścia: A> B, A — B oraz A <LB umożliwiające łączenie komparatorów, a tym samym tworzenie układów służących do porównywania liczb o liczbie bitów większej niż 4. Komparator 85 jest układem realizującym następujące

Wyszukiwarka

Podobne podstrony:

Image446 Funkcję, która ma być spełniona przez układ przedstawiono na rys. 4.538a, natomiast symbol

Image294 realizację operacji dodawania. Układ przedstawiony na rys. 4.335 umożliwia realizację opera

Image348 W układzie przedstawionym na rys. 4.399 sygnał przeniesienia blokującego propaguje tylko pr

1. Dla jakich wartości A* układ przedstawiony na rys. 1 będzie stabilny? 2.

CCF20110506�009 1 cd. tabl. 7.17.2.2. Przetwornice transformatorowe Układ przedstawiony na rys. 7.12

6.1. UKŁADY PODSTAWOWE. WŁAŚCIWOŚCI I WIELKOŚCI ZALEŻNE 291 Układ przedstawiony na rys. 6.7a został

Image078 Tablica wartości tej funkcji jest przedstawiona na rys. 3.36a. Ponieważ rozważana funkcja j

034(1) Wykres funkcji przedstawiono na rys. 27. 5) Funkcja logarytmiczna >’ = Ig u jest określona

Image349 Implementacja równań (6) jest przedstawiona na rys. 4.400. Typowy czas propagacji sygnału w

Image455 a o E Y +27~ Funkcję spełnianą przez układ oraz jego schemat logiczny przedstawiono na rys.

Image073 Układ służący do realizacji tej funkcji, zbudowany z bramek I (AND), LUB (OR), NIE (NOT) pr

Image183 Struktura logiczna układów FPLA Schemat logiczny typowego układu FPLA przedstawiono na rys.

więcej podobnych podstron