088 4

172

6.3. Projektowanie układów sterujących w postaci rozdzielaczy warunkowych

W technice układów cyfrowych, mianem rozdzielacza określa się wielowyjściowy układ, na którego kolejnych wyjściach, w rytm impulsów zegarowych, pojawia się cyklicznie stan jedynki logicznej (tzn. w danym momencie występuje ona tylko na jednym wyjściu). Tego typu rozdzielacz można nazwać bezwarunkowym.

Jeśli natomiast rozdział impulsów wyjściowych jest uzależniony od spełnienia pewnych warunków, wówczas mamy do czynienia z rozdzielaczami warunkowym i.

W niniejszym rozdziale przedstawimy metody projektowania układów sterujących w postaci tzw. prostych rozdzielaczy warunkowych o stanach wewnętrznych kodowanych kodem “1 z k" oraz w postaci różnych typów rozdzielaczy warunkowych o stanach kodowanych naturalnym kodem dwójkowym, w tym rozdzielaczy typu Moore'a i Mealy’ego dla tzw. liniowych sieci działań oraz rozdzielaczy Moore’a dla dowolnych sieci działań.

Wszystkie przedstawione tu rozwiązania będą miały postać układów synchronicznych (zgodnie z tytułem całego rozdziału). Można spotkać również rozdzielacze asynchroniczne (51 ale ze względu na dużo mniejszą uniwersalność są one znacznie rzadziej stosowane.

6.3.1. Proste rozdzielacze warunkowe

Mając określoną sieć działań projektowanego układu, należy w niej nanieść stany wewnętrzne (według wersji Moore’a albo Mealy’ego). Dalsza część procedury projektowej opiera się na dwóch założeniach:

a) stany wewnętrzne koduje się w kodzie "1 z k" (k - liczba stanów), zatem każdemu stanowi odpowiada jeden przerzutnik (najlepiej typu D).

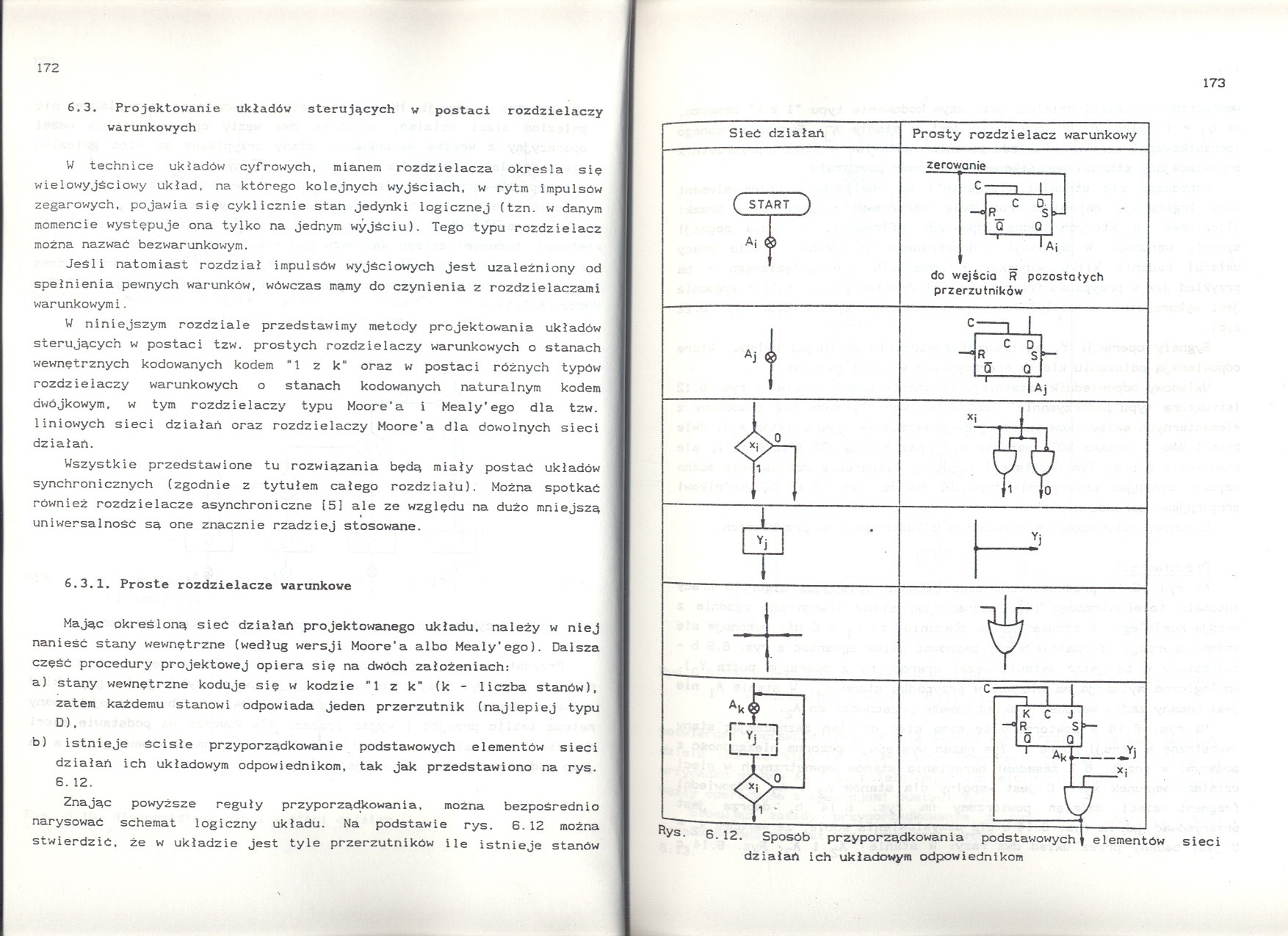

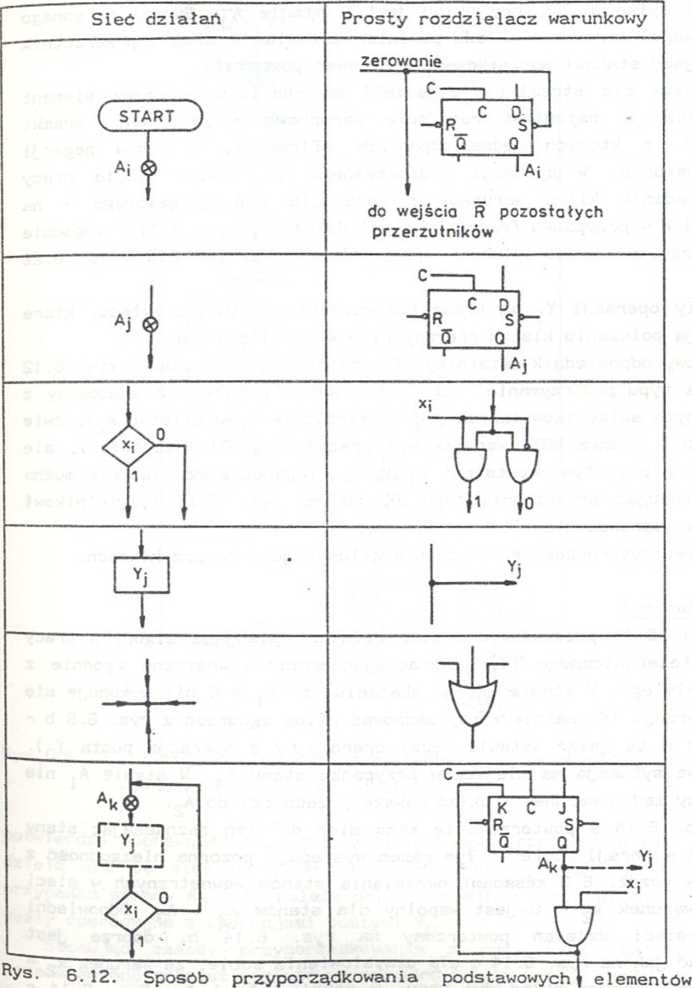

b) istnieje ścisłe przyporządkowanie podstawowych elementów sieci działań ich układowym odpowiednikom, tak jak przedstawiono na rys. 6. 12.

Znając powyższe reguły przyporządkowania, można bezpośrednio narysować schemat logiczny układu. Na podstawie rys. 6.12 można stwierdzić, że w układzie jest tyle przerzutników ile istnieje stanów

sieci

działań ich układowym odpowiednikom

Wyszukiwarka

Podobne podstrony:

Kotwica0087 172 6. Projektoioanie belek drewnianych Sprawdzenie warunku stanu granicznego użylkowaln

Image509 silnych zakłóceń. Z tych powodów podczas projektowania układów sprzęgających wejściowych na

skanuj0076 (34) Rozdział 3. ♦ Instrukcje sterujące i funkcje Rozdział 3. ♦ Instrukcje sterujące i fu

Spis treści 11 Rozdział 9 Kierunki projektowanych zmian prawa cywilnego Rozdziano Wybór

PwTiR061 120 Rozdział 5 Warunki pobytu specjalistycznego, jak też warunki typowego pobytu turystów n

s 92 93 92 ROZDZIAŁ 4 - warunków i trybu przyjmowania uczniów do szkół i placówek

seminarium tematy Tematy Seminarium Specjalnościowego: 1. Problemy rozmieszczenie bloków w projektow

PwTiR061 120 Rozdział 5 Warunki pobytu specjalistycznego, jak też warunki typowego pobytu turystów n

Projekt MES Comsol Multiphysics 3.4 Rys. 3 Warunki początkowe - utwierdzenie modelu. Rys. 4 Warunki

Projekt MES Comsol Multiphysics 3.4 Rys. 5 Warunki początkowe — wartość obciążająca model. Rys. 6

Katedra Dróg i Mostów Blok: Projektowanie układów komunikacyjnych EGZAMINATORZY: 1.

L3. Projektowanie i implementacja programów z zastosowaniem instrukcji warunkowej IF. L4. Projektowa

1. Wstęp Janusz Czapiński1.1. Cel i ogólne założenia projektu Istnieją dwa sposoby opisu warunków i

Ćwiczenia: Zastosowanie wspomagania komputerowego do projektowania układów wlewo-wo - zasilających

Główne założenia projektu przewidują: - zmianę zasad rozdzielania środków z

więcej podobnych podstron