1tom190

7. ELEKTRONIKA 382

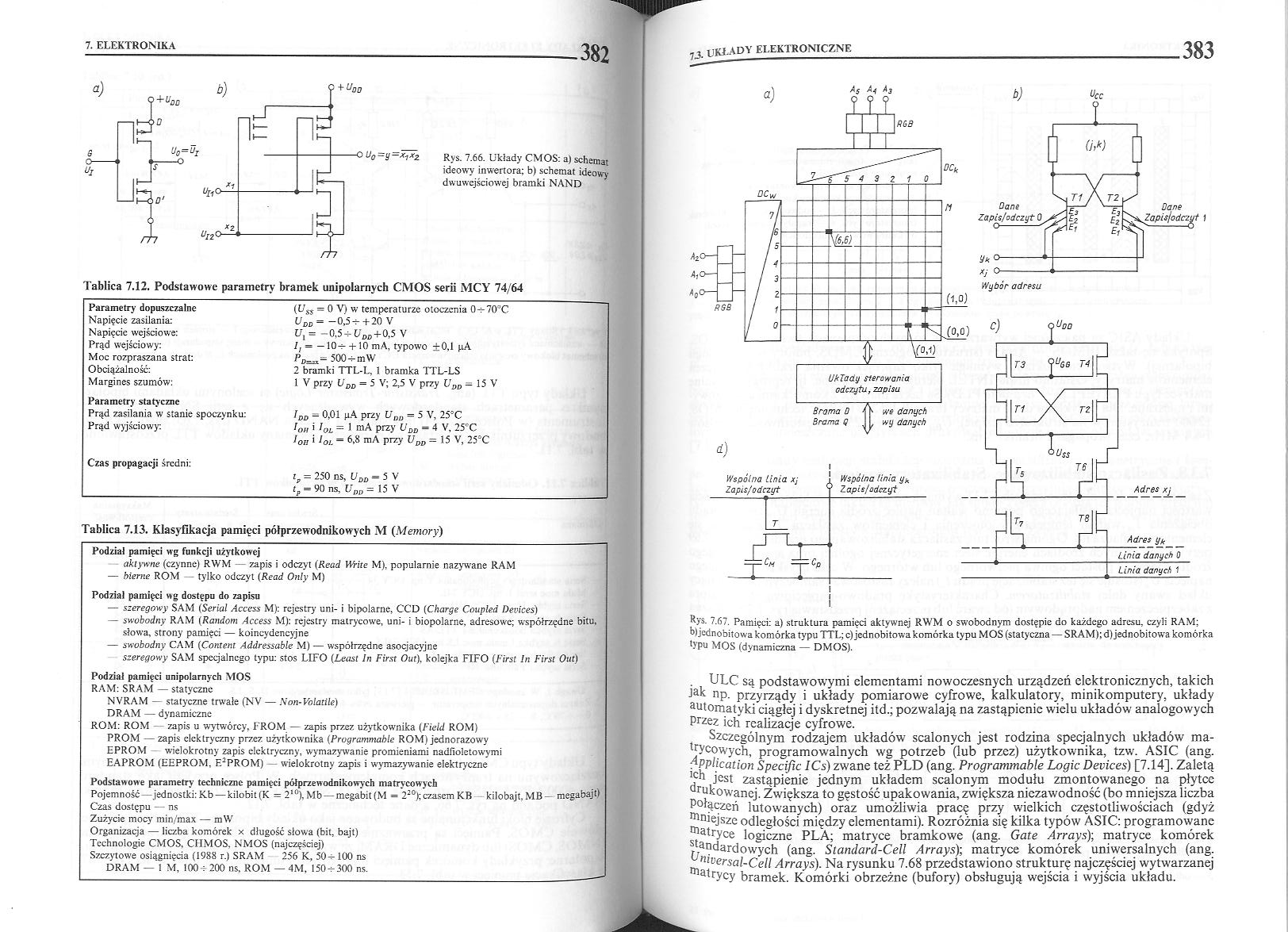

Rys. 7.66. Układy CMOS: a) schemat ideowy inwertora; b) schemat ideowy dwuwcjściowej bramki NAND

Tablica 7.12. Podstawowe parametry bramek unipolarnych CMOS serii MCY 74/64

|

Parametry dopuszczalne |

(£/$$• = 0 V) w temperaturze otoczenia 0—70°C |

|

Napięcie zasilania: |

U DD = —0,5-r +20 V |

|

Napięcie wejściowe: |

U, = -0.5^C/'DO+0,5 V |

|

Prąd wejściowy: |

I,= —10— +10 m.A, typowo ±0,1 p.A |

|

Moc rozpraszana strat: |

Pan»= 500-mW |

|

Obciążalność: |

2 bramki TTL-I., 1 bramka TTL-LS |

|

Margines szumów: |

1 V przy UDD = 5 V; 2.5 V przy VBB = 15 V |

|

Parametry statyczne | |

|

Prąd zasilania w stanie spoczynku: |

'dd - W1 mA przy U „„ = 5 V, 25°C |

|

Prąd wyjściowy: |

'on ' V = 1 mA przy UDD = 4 V, 25‘C |

|

Czas propagacji średni: |

'on > 'oi. = mA przy VPB = 15 V, 25‘C r„ = 250 ns, UBB - 5 V tp = 90 ns, U„„ = 15 V |

Tablica 7.13. Klasyfikacja pamięci półprzewodnikowych M (Memory)

Podział pamięci wg funkcji użytkowej

aktywne (czynne) RWM — zapis i odczyt (Read H-Wre M), popularnie nazywane RAM

— bierne ROM — tylko odczyt (Read Only M)

Podział pamięci wg dostępu do zapisu

— szeregowy SAM (Seria/ Access M): rejestry uni- i bipolarne. CCD (Charge Coupled Deuices)

— swobodny RAM (Random Access M): rejestry matrycowe, uni- i biopolarne, adresowe; współrzędne bitu, słowa, strony pamięci — koincydencyjne

— swobodny CAM (Content Addressable M) — współrzędne asocjacyjne

szeregowy SAM specjalnego typu: stos LIFO (Least In First Out), kolejka FIFO (First In First Out)

Podział pamięci unipolarnych MOS

RAM: SRAM — statyczne

NVRAM — statyczne trwałe (NV — Non-Volatiłe)

DRAM — dynamiczne

ROM: ROM — zapis u wytwórcy, FROM — zapis przez użytkownika (Field ROM)

PROM — zapis elektryczny przez użytkownika (Frogrammahle ROM) jednorazowy EPROM wielokrotny zapis elektryczny, wymazywanie promieniami nadfioletowymi EAPROM (EEPROM, E2PROM) wielokrotny zapis i wymazywanie elektryczne

Podstawowe parametry techniczne pamięci półprzewodnikowych matrycowych

Pojemność —jednostki:Kb—kilobit(K = 210), Mb —megabit(M = 220); czasem KB kilobajt,MB- megabajt)

Czas dostępu — ns

Zużycie mocy min/max — raW

Organizacja — liczba komórek x długość słowa (bil. bajt)

Technologie CMOS, CIIMOS. NMOS (najczęściej)

Szczytowe osiągnięcia (1988 r.) SRAM 256 K, 50- 100 ns DRAM — 1 M, 100 : 200 ns. ROM — 4M, 150-300 ns.

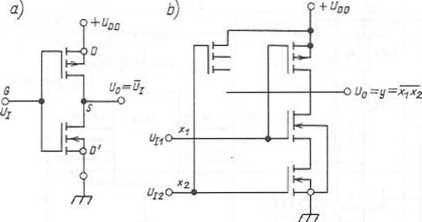

Rys- 7-67. Pamięci: a) struktura pamięci aktywnej RWM o swobodnym dostępie do każdego adresu, czyli RAM; b) jednobitowa komórka typu TTL; c) jednobitowa komórka typu MOS (statyczna — SRAM); d) jednobitowa komórka typu MOS (dynamiczna — DMOS).

ULC są podstawowymi elementami nowoczesnych urządzeń elektronicznych, takich jak np. przyrządy i układy pomiarowe cyfrowe, kalkulatory, minikomputery, układy automatyki ciągłej i dyskretnej itd.; pozwalają na zastąpienie wielu układów analogowych Przez ich realizacje cyfrowe.

Szczególnym rodzajem układów scalonych jest rodzina specjalnych układów marcowych, programowalnych wg potrzeb (lub przez) użytkownika, tzw. ASIC (ang. Application Specific ICs) zwane też PLD (ang. Programmahle Logic Decices) [7.14]. Zaletą 'ch jest zastąpienie jednym układem scalonym modułu zmontowanego na płytce urukowancj. Zwiększa to gęstość upakowania, zwiększa niezawodność (bo mniejsza liczba Połączeń lutowanych) oraz umożliwia pracę przy wielkich częstotliwościach (gdyż utnięjsze odległości między elementami). Rozróżnia się kilka typów ASIC: programowane ruatryce logiczne PLA; matryce bramkowe (ang. Gate Arrays); matryce komórek tandardowych (ang. Siandard-Cell Arrays); matryce komórek uniwersalnych (ang. _ niŁ’ersal-Cell Arrays). Na rysunku 7.68 przedstawiono strukturę najczęściej wytwarzanej matrycy bramek. Komórki obrzeżne (bufory) obsługują wejścia i wyjścia układu.

Wyszukiwarka

Podobne podstrony:

1tom193 7. ELEKTRONIKA 388 Rys. 7.75. Schematy ideowe samowzbudnych przetwornic DC-DC: a) zasada dzi

182 183 182 Rys. 5.66. Dekada 7490: a) schemat, b, c) sposoby łączenia (rys. 5.66b). Dekada z dwójką

1tom192 7. ELEKTRONIKA 386 Rys. 7.72. Stabilizator ze sprzężeniem zwrotnym (parametr regulacyjny rez

1tom337 13. ELEKTROTERMIA 676 Rys. 13.27. Uproszczony schemat zastępczy stalowniczego urządzenia łuk

3tom087 2. WYTWARZANIE ENERGII ELEKTRYCZNEJ 176 Rys. 2.88. Układy wielomaszynowe w elektrowniach pom

410 3 10. AUTOMATYZACJA W ELEKTROWNIACH PAROWYCH Rys. 10.5. Układy automatycznej regulacji podstawow

491 2 12.4. ROZWIĄZANIA ELEKTROWNI WODNYCH 12.4. ROZWIĄZANIA ELEKTROWNI WODNYCH Rys. 12.18. Uproszcz

496 ELEKTROWNIE WODNE Rys. 12.23. Uproszczony schemat układu elektrycznego połączeń głównych

2tom190 5. MASZYNY ELEKTRYCZNE 382 Rys. 5.113. Układ połączeń silnika bocznikowego Rys. 5.114. Kszta

Uklady cyfrowe kolo I2003? Zad. 4. Mając dany schemat elektryczny logiczny (rys. poniżej) wyjaśnij,

Uklady cyfrowe kolo I2003? vcc Gr. B Sterowanie Zad. 4. Mając dany schemat elektryczny logiczny (rys

1tom191 7. ELEKTRONIKA 7>3. UKŁADY ELEKTRONICZNE .385 Ujsn UDD ■ m Im. Rys. 7.68. Programowalna

1tom198 398 u lVV4C[ o konstrukcji układów elektronicznych399 7. ELEKTRONIKA Rys. 7.88. Układy: a) M

368 2 8. TURBOGENERATORY I UKŁADY ELEKTRYCZNE W ELEKTROWNIACH PAROWYCH Rys. 8.25. Schemat układu ele

368 2 8. TURBOGENERATORY I UKŁADY ELEKTRYCZNE W ELEKTROWNIACH PAROWYCH Rys. 8.25. Schemat układu ele

więcej podobnych podstron