02

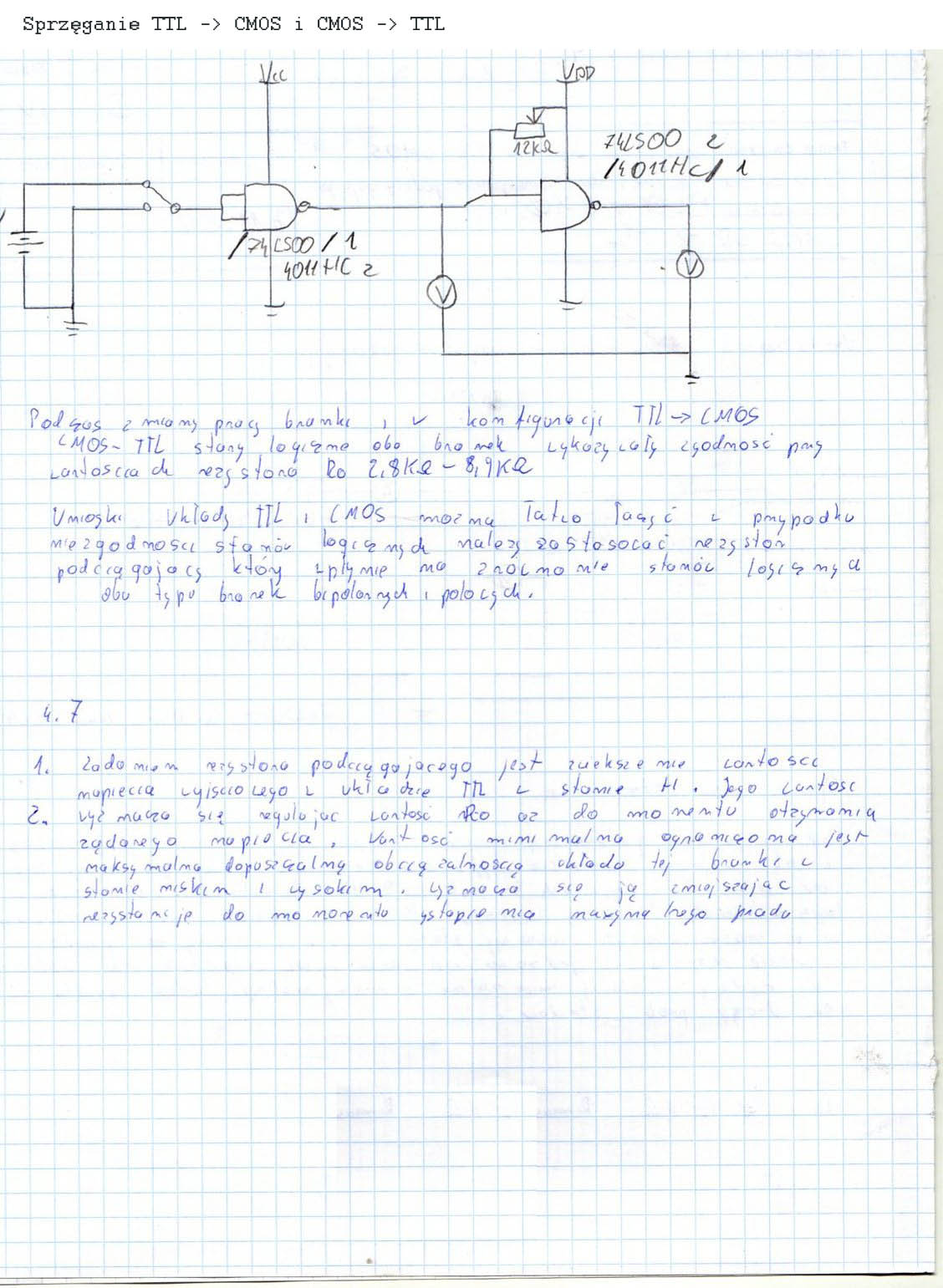

Sprzęganie TTL -> CMOS i CMOS -> TTL

|

\k |

: |

ypp | ||||||||||||||||

|

_^r |

i | |||||||||||||||||

|

4ŹML |

m^oo | |||||||||||||||||

|

• |

/iOrtncJ A. | |||||||||||||||||

|

r~ | ||||||||||||||||||

|

J | ||||||||||||||||||

|

/ | ||||||||||||||||||

|

A |

LSCO / i | |||||||||||||||||

|

Wtf/tfC Ł |

' fl |

/) | ||||||||||||||||

|

(v) | ||||||||||||||||||

|

~~ | ||||||||||||||||||

|

ć*isc / rv~\((j /ns Dno C■ |

1} Al/ VI l<< 1 tX |

Loai 1/Cj |

iy\ to cj{ T fl H> L O /c ć |

CMty | ||||||||||||||

|

i\L s4^ oS cca ch_ *e?, 5 |

) |

O 4; C bo 0.0 Pft Z i $ I'- |

i) A O |

Ar* |

lc |

ŁOSOSI |

Pr') | |||||||||||

|

& |

7 | |||||||||||||||||

|

J | ||||||||||||||||||

|

l/Lfoc/i |

tjl 1 |

r^vi©r |

rvi C/ |

lO. 1 L O |

lo*?; c |

Ł- p |

c- | |||||||||||

|

M ? 2 Cj a <ł ęc^ 5^c *0 J C (Ci qy \ o C \ ^ |

vyul |

? 2o 5 7 |

O SOC-O c' |

? c 5 i < |

/ ' 3 A | |||||||||||||

|

lo^j Lp nt lc L/fltf/c>A/v» tA |

rM& |

P c.OL /ii O |

oa.'<f > ^0 /nO ^ /vj 9 |

a | ||||||||||||||

|

dvv U p o 1}-.o |

i polo cM, / | |||||||||||||||||

|

k: 7 | ||||||||||||||||||

|

l |

la "W 'Y > |

^OtC» poJcca q» l0rjpqO |

/*>7 L~ |

?u |

e k w if nt‘*' |

ŁOa 1/ |

0 £e< | |||||||||||

|

l-Ci/WO U</0 L l/Uo c4/ |

Ć' |

Ttl |

<, łiJM/ f |

* )cye> |

C-o^Josc | |||||||||||||

|

V |

qjio >C UC/aI<>S |

C |

Ho |

o^ |

C^<2 |

/wio M Suju |

C-lr^O ry\ , | |||||||||||

|

/ *■ Z y J Q Ki y o r^M Jp (*Uf #5', $OY |

/ *> |

' 1 ' I k^lCL L/(s*, |

°£C |

'Wj / /V?/ |

■Arnd |

/tt o ®y/7 |

6> /»7/ 0 |

/ ns\ C/ A | ||||||||||

|

oWCrolwb ol) C( |

< c'Cl/aiO $<7 O |

oUto |

c/c; 7ry 1 c ^ |

i’i/* 4 |

/ 0 | |||||||||||||

|

' 1 f 5J c; mI ? at/£ ICć /w. |

t |

t-V >©4v a-h , |

c> |

s ? rtO |

*to |

\u>l'<iCtii <■ |

c | |||||||||||

|

rJt?^-}o r*< ,? Jo |

v>łO <*vw |

» / |

on/f |

/n<c. |

sn ^ |

tM/Mf' '^lż'f-0 jfUCtcłc/ | ||||||||||||

|

T | ||||||||||||||||||

|

/ | ||||||||||||||||||

|

*1 | ||||||||||||||||||

|

— | ||||||||||||||||||

Wyszukiwarka

Podobne podstrony:

Slajd15 (120) Magistrale Bramki TTL i CMOS mają na wyjściu wzmacniacz przeciwsobny (ang. pusch-pull)

DSC07319 (3) CMOS TTL/CMOS AC-HC ACTHCT AHC-C AHCT-FCT TTL FS-AS

Image527 Układy mogą być wykorzystywane do współpracy z elementami CMOS, RTL itp. Rys. 4.675. Transl

układy Parametry układów scalonych z bramkami CMOS i TTL Nazwa Liczba wejść Liczba

54 (293) Grcuitos & SoluęóesINTERFACE CMOS/TTL Interlacear circuilos CMOS com circuitos TTL exig

uklady logiczne 18 Bramko TTl z otwartym kolektorem Bramka CMOS lfco=5V!) =o— Bramka CMOS Bramk

Rysunek 3.4. Charakterystyka przejściowa bramki TTL LS (Zakreskowane granice tolerancji) Bramki CMOS

Tablica 3.2. Przegląd najbardziej rozpowszechnionych rodzin układów TTL, ECL i CMOS Wady tej nie maj

R Rys. 8.30. Przerzutnik astabilny z prze-rzutnikiem Schmitta Okres drgań (TTL) T - 1,4... 1,8 RC (C

IDEHARD ROM PCI/ISA BIOS (nr wersji BIOS-u) CMOS SETUP UTILITY AWARD SOFTWARE, INC. IDEs (HDDs)

Image013 SSI w podklasie CMOS jest uzasadnione zaletami tych układów, głównie znikomym statycznym po

więcej podobnych podstron