DSC07319 (3)

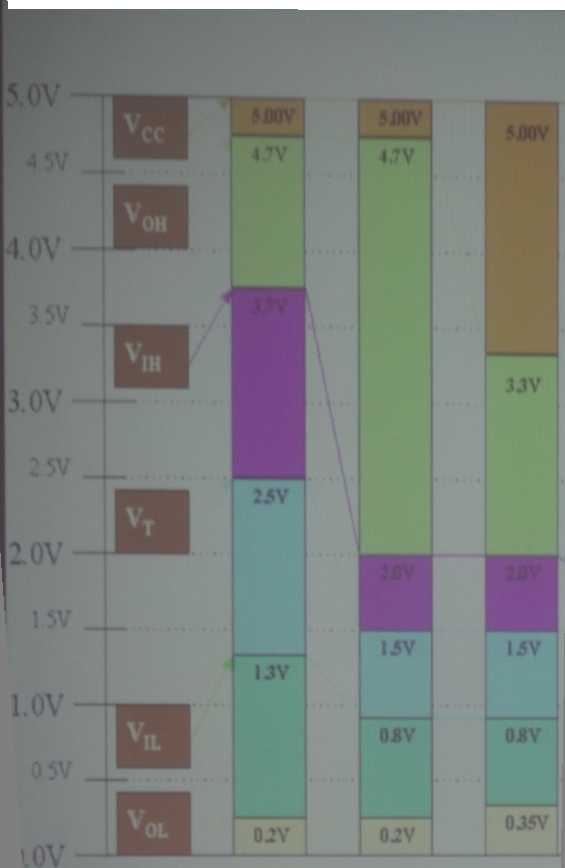

CMOS TTL/CMOS

AC-HC ACTHCT

AHC-C AHCT-FCT

TTL

FS-AS

LSALS

Vgf Input High level Voltage VŁ: Input Law level Voltage

Vai: Output High level Yoltagt Output Law Ievel Yoitage VT: Threshold Yoitage

www.interfacebut.com

“ijr

Typicłl vahu% Avtraftdom Ftmilies

uv

1JV

•IV

0.75Y

04V

04V

LowY BIL GIL

Wyszukiwarka

Podobne podstrony:

Image527 Układy mogą być wykorzystywane do współpracy z elementami CMOS, RTL itp. Rys. 4.675. Transl

Slajd15 (120) Magistrale Bramki TTL i CMOS mają na wyjściu wzmacniacz przeciwsobny (ang. pusch-pull)

układy Parametry układów scalonych z bramkami CMOS i TTL Nazwa Liczba wejść Liczba

54 (293) Grcuitos & SoluęóesINTERFACE CMOS/TTL Interlacear circuilos CMOS com circuitos TTL exig

uklady logiczne 18 Bramko TTl z otwartym kolektorem Bramka CMOS lfco=5V!) =o— Bramka CMOS Bramk

DSC07324 (3) Podstawy techniki cyfrowej Technologia CMOS - podejście stosowane obecnie tmyfrp-kmotm/

Sprzęganie TTL -> CMOS i CMOS ->

Rysunek 3.4. Charakterystyka przejściowa bramki TTL LS (Zakreskowane granice tolerancji) Bramki CMOS

Tablica 3.2. Przegląd najbardziej rozpowszechnionych rodzin układów TTL, ECL i CMOS Wady tej nie maj

R Rys. 8.30. Przerzutnik astabilny z prze-rzutnikiem Schmitta Okres drgań (TTL) T - 1,4... 1,8 RC (C

fiz lab 402 V *• J ^Hc,cue J— Wdif- ZcrA/lJE -fG-ĄC)(S -¥ wo-pięa? fftfl Oi/ . . Sb /VlOC J Pr

IDEHARD ROM PCI/ISA BIOS (nr wersji BIOS-u) CMOS SETUP UTILITY AWARD SOFTWARE, INC. IDEs (HDDs)

Image013 SSI w podklasie CMOS jest uzasadnione zaletami tych układów, głównie znikomym statycznym po

więcej podobnych podstron