20 (69)

*

W połowic lat 60-łych opracowano nową, w stosunku do układów ówcześnie istniejących, technikę konstrukcji układów logicznych, nazwaną techniką TTL (ang iretnsistor - Transistor logie)

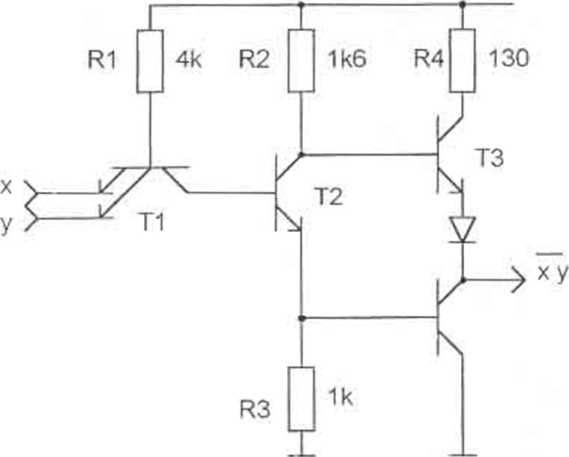

Przykładowy schemat elektroniczny funktora wykonanego w technologii TTL przedstawiono na przykładzie dwuwcjściowcj bramki NAND (rys 16)

+ 5V

Rys. 16 Dwuwejściowa bramka NAND w technice TTL.

n

PARAMETRY UKŁADÓW SCALONYCH

Zastosowanie układów scalonych wymaga znajomości podstawowych ich parametrów

1) Obciążalność wejściowa (anu fan - in) - określa ile razy dane wejście stanowi większe obciążenie niż wejście standardowe. Dla techniki TTL wynosi 10

2) Obciążalność wyjściowa (ang. fan - out) - określa liczbę standardowych wejść, którymi można obciążyć dane wyjście. Dla techniki TTL wynosi 10.

3) Poziomy logiczne - każdemu z możliwych stanów logicznych wejścia/wyjścia przyporządkowane są dla danej technologii dwa typowe napięcia W układach serii TTL narzucono następującą konwencję sygnałów odpowiadających zbiorowi elementów algebry Boolc’ a:

" 0 w - napięcie 0V " 1 " - napięcie +5V

4) Margines szumów - ze względu na występujące niestabilności napięć wytwarzanych przez zasilacz _ oraz niedoskonałą powtarzalność parametrów wszystkich tranzystorów występujących w układach scalonych nic jest możliwe sztywne utrzymanie wszystkich sygnałów na podanych poziomach Z tego względu skojarzono poszczególne elementy boolowskie z pewnymi przedziałami napięć. Dla technologii TTL przyjmuje się:

" 0 " - napięcie z przedziału [0; +0,8V]

" 1 " - napięcie z przedziału [+2,4V. +5 V]

Napięcie na wejściu/wyjściu układu logicznego przyjmujące wartość z przedziału (+0,8; +2,4V) traktowane jest jako stan niestabilny (przejściowy).

3) Czas propagacji Jv - jest czasem opóźnienia sygnału wyjściowego w stosunku do sygnału wejściowego (pobudzenia). Czas ten jest /.definiowany zgodnie ze wzorem podanym na rys. 17.

-20-

Wyszukiwarka

Podobne podstrony:

Szybkie koleje w Polsce 231 Nieco wcześniej, jeszcze w pierwszej połowie lat 60. Polskie Koleje Pańs

Wiśniowski (wychowanie muzyczne). W drugiej połowie lat 60-tych trwała budowa sali gimnastycznej.

Rock psychodeliczny jest starszy od hard rocka i powstał już w połowie lat 60-tych. Był związany z&n

WSPÓŁTWÓRCY BIBLIOTEKARSTWA POLSKIEGO 11 Poznałam Ją w połowie lat 60-tych, kiedy będąc jeszcze

P1020980 (3) 7. Postfordyzm W połowie lat 60. niewielu Amerykanów zdawało sobie śgw jak radykalne zm

1.3. Definicja pojęcia „nowe media” Termin „nowe media” funkcjonuje od lat 60. XX w. Używa się go do

(nawet do 20 %) 100% poboru i o mniejszej nierównomierności godzinowej odpływu Nh w stosunku do pobo

IMG?69 na obniżenie napięcia emocjonalnego po powrocie z pracy do domu. Podstawą wielu technik dekom

IMG!87 (5) Socjologiczne teorie młodzieży Hartmui Griesc, autor opublikowanego w Polsce w połowic la

CCF20090907�003 2009-02-20 , T*- Bankowość w PRL -lata 80-te A zatem zapoczątkowana na początku lat

DSCi Atomizacja elektrotermiczna > Atomizer elektrotermiczny (ETAA8) - opracowany pod koniec lat

więcej podobnych podstron