ScanImage04

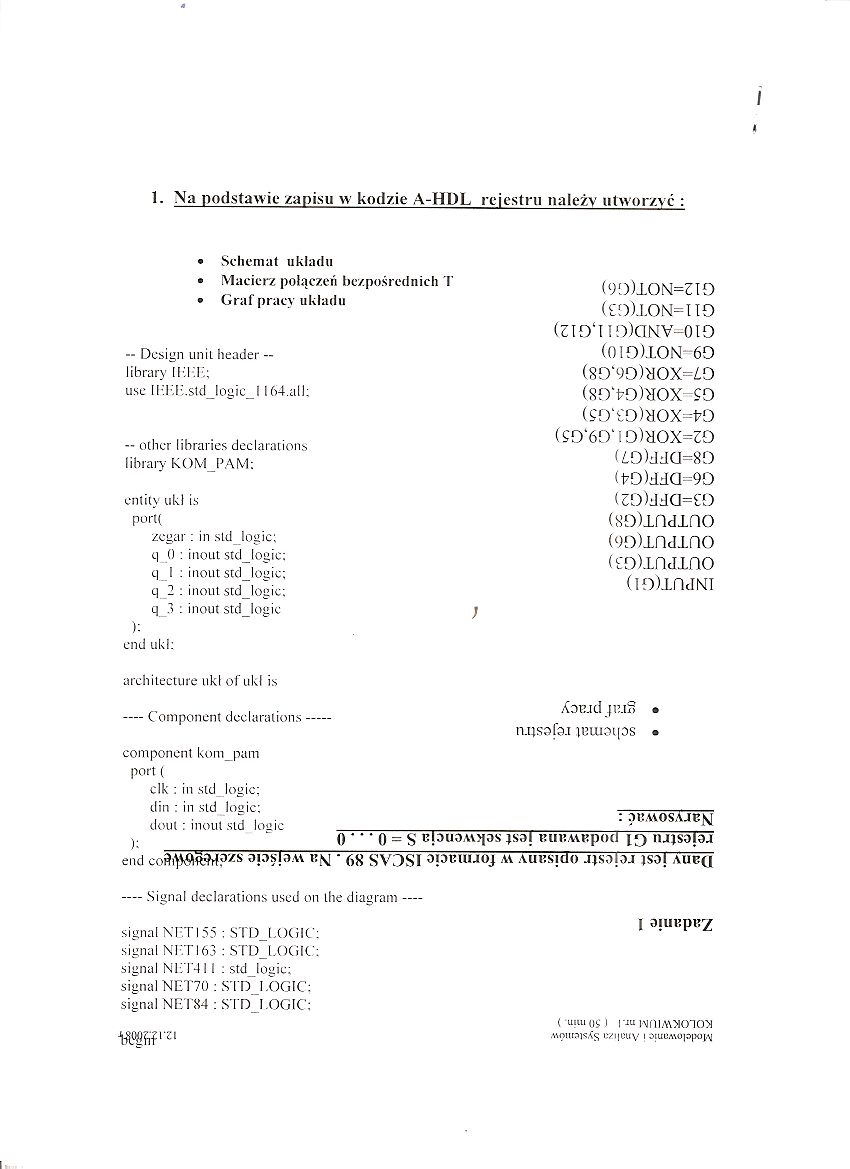

1. Na podstawie zapisu w kodzie A-HDL rejestru należy utwor/.yć :

Schemat układu

.Macierz połączeń bezpośrednich T Graf pracy układu

— Design unit header --

library IKKE;

usc IKKłi.stdJogicJ 164.all;

— other librarics declarations library KOM PA M:

entily ukł is port(

zegar: in sldjogic; q 0 : inout std_logic: q I : inout stdjogic; q 2 : inout stdjogic; q_3 : inout stdjogic

):

end ukł:

(99)lON=3I9 (£9)lOM=IIO (2IO‘H9)CINV=OtO (0!9).I.ON- 60 (89‘99)dOX=Z.9 (S9>9)>I0X ęo (?o‘eo)aox=t’9 (eo‘60'iO)aox=30

(£9)ddG=89

<X9):XIG90

(ć9)JJG=Ł‘9

(89)indlOO

(99)xndino

(to).Lnjino

(in)in<iMi

archiLecture ukł of ukł is

— Component declarations

n.usofai luuioips •

component kom_pam port (

clk : in std logie;

din : in std logie; doul: inout std logie

end oaW&ftMpzs " ,!.M

: 3BH0SAJBM

O • • • O = S Bl3U0Aił|as łsaj tunutttpou [Q iujsoIoj

■ 68 SV9SI OpBUMOJ Al AUBSldo JłSOlOJ )S01 AUB(|

— Signal declarations uscd on ihe diagram —

signal NET 155 : STDJ.OGIC: signal NET 163 : STD_EOGICi: signal NET4II : stdjogic: signal NET70 : STD LOGIC: signal NET84 : STDJ.OGIC:

i umi os i !'««lam.Moiott

M9Ut?]S,\S CZI|CUV I 0|UCA\0p|K)J,5J

Wyszukiwarka

Podobne podstrony:

ScanImage01 / / 1. Na podstawie zapisu w kodzie A-HDL rejestru należy utworzyć: <* Schemat układu

ScanImage03 1. Na podstawie zapisu w kodzie A-HDL rejestru należy utworzyć : • Sch

I. Na podstawie zapisu w kodzie A-HDL rejestru należy utworzyć: • Schemat układu •

ScanImage01 1. Na podstawie zapisu >v kodzie A-HDI. rejestru należy utworzyć : ® Schemat układu o

1- Na podstawie zapisu w kodzie A-HDI. rejestru należy ut>vor/vć : • Schemat

zestaw1a ZESTAW I Na podstawie zapisu w konturze mapy glebowo-rolniczej - 8 A gl:gs należy przyjąć,

img120 ZESTAWIII l.Na podstawie zapisu w konturze mapy glebowo-rolniczej -IB glp:gs należy przyjąć,

ScanImage12 Na podstawie pomiarów należy dokonać oceny spełnienia warunku sam o wyłączenia: Uf Z,, g

76862 Obraz (1721) Na podstawie obliczonego prądu obciążenia lB należy dobrać zabezpieczenie przewod

I (4) 5 16 Na podstawie zapisu siły napędowej uzyskanego na drodze pomiaru tensometrycznego, dokonaj

więcej podobnych podstron