img033

91

Opis interfejsu monitora graficznego.

Interfejs monitora graficznego jest zbudowany w oparciu o kontroler CRT M6845 firmy Motorola.

Aby zaoszczędzić lokacji adresowych w systemie mikroprocesorowym, pamięć VRAM jest dostępna pośrednio poprzez porty zatrzaskowe układu 18255.

Interfejs zajmuje 7 lokacji w przestrzeni adresowej mikroprocesora, kontroler CRT 6845 dostępny jest po dwiema lokacjami adresowymi:

FF44h - adres rejestru adresowego FF45h - adres rejestru danych

Układ 8255 pod czterema lokacjami:

FF40h - adres portu A (młodsza część adresu VRAM)

FF41h - adres portu B (starsza część adresu VRAM)

FF42h - adres portu C

FF43h - adres rejestru sterującego

Dodatkową lokacją jest bufor danych pamięci VRAM pod adresem:

FF46h

Adresacja VRAM.

Pamięć VRAM ma organizację 8- bitową.

Każdemu bitowi odpowiada jeden punkt na ekranie monitora.

Dostęp do pamięci jest pośredni.

Aby wpisać daną dla komórki VRAM należy najpierw na port PA układu 8255 wpisać młodszą część adresu komórki, na port PB (czyli pod adres FF41h) starzą część adresu komórki.

Daną dla tak zaadresowanej komórki VRAM (Video Ram) należy przesłać pod adres bufora danych czyli FF46h.

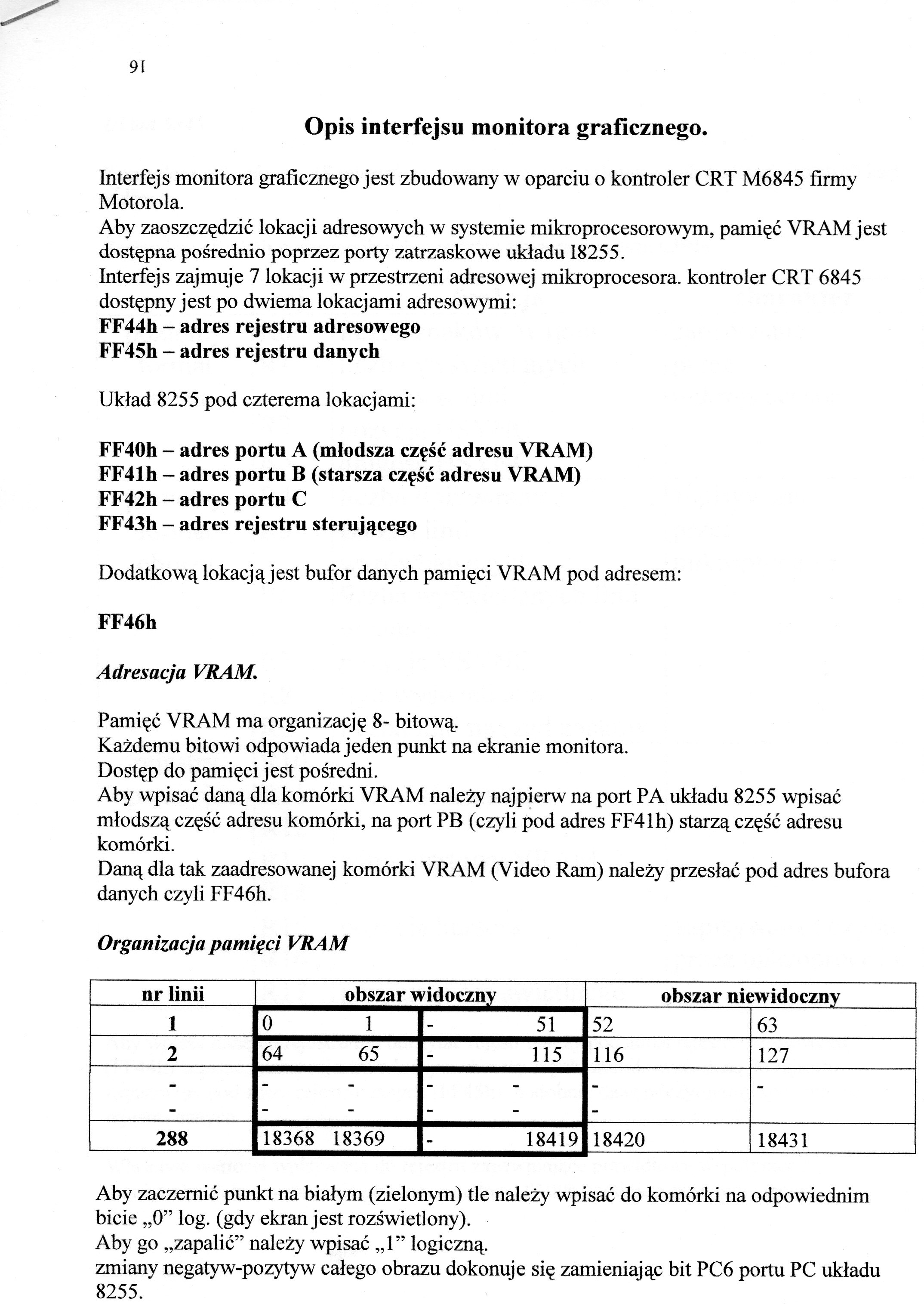

Organizacja pamięci VRAM

|

nr linii |

obszar widoczny |

obszar niewidoczny | ||

|

1 |

0 1 |

51 |

52 |

63 |

|

2 |

64 65 |

115 |

116 |

127 |

|

- |

- |

- |

- |

- |

|

288 |

18368 18369 |

18419 |

18420 |

18431 |

Aby zaczernić punkt na białym (zielonym) tle należy wpisać do komórki na odpowiednim bicie „0” log. (gdy ekran jest rozświetlony).

Aby go „zapalić” należy wpisać „1” logiczną.

zmiany negatyw-pozytyw całego obrazu dokonuje się zamieniając bit PC6 portu PC układu

8255.

Wyszukiwarka

Podobne podstrony:

img176 (12) Po włączeniu, ekran monitora podzielony jest na dwa okna: 1. okno prez

skanowanie0033 (14) Ustawienie monitora • Korzystne jest stosowanie filtrów przeci

- dyktando graficzne jest najtrudniejszym ćwiczeniem i wymaga doskonałej

skanuj0178 (2) Ponieważ K, dla danego okresu są niezmienne, czyli ich wartość jest stalą liczbą, gra

RETROKONWERSJA KATALOGÓW BIBLIOTECZNYCH 269 graficznymi (import — eksport rekordów), kontrola rekord

fiz11 0O.yjak jest zbudowany interferometr Michelsona ??? W interferometrze tym monochromatyczne świ

Ręczne pisanie kodu Programista ma pełną kontrolę nad wyglądem interfejsu. Jednak zmuszony jest pisa

img5 (3) Wersje HTML HTML 3.0, HTML 3.2 zawierają rozszerzenia graficzne, tabele oraz elementy kontr

Kryteria wyboru skanera cd. 2. Interfejs - najpopularniejszy obecnie jest interfej

287 (10) Określanie pozycji metodami graficznymi jest nieskomplikowane i mało pracochłonne. Istnieje

Adres procedury obsługujące.} monitory umieszczony Jest w wektorze przerwania i oh, czyli pod adrese

więcej podobnych podstron