062 063

62

O

definiująca poszukiwany blok lteracyjny. W wyniku syntezy tego układu otrzymujemy schemat bloku Jak na rys. 2.16.

Dla skompletowania układu lteraoyjnego należy zaprojektować blok wyjściowy oraz określić sygnały początkowe o^. V naszym przypadku układ ma dawać na wyjściu jedynkę, jeżeli została wykryta seria trzech Jedynek,czyli blok wyjściowy zadany jest funkcją y » P11P21- Dla prawidłowego działania układu należy ponadto przyjąć ■ 0, o2 ■ O. tt

Z powyższego przykładu wynika metodyka projektowania układu lteracyj-nego. Ogólnie składa się ono z następujących etapów:

- ustalenie ilości wejść podawanych do jednego bloku,

- zdefiniowanie 1 zakodowanie stanów, co określa liczbę sygnałów przesyłanych między blokami, a więc ogólną liczbę wejść 1 wyjść bloku,

- konstrukcja tablloy przejść stanów,

- synteza bloku na podstawie tej tablicy,

- ustalenie sygnałów początkowych c^,

- synteza bloku wyjściowego.

Jak to będzie omawiane w rozdziale 5, szereg podstawowych układów scalonych konstruowanych Jest jako układy iteraoyjne, np. sumatory i komparatory.

Generalną wadą układów lteraeyjnych jest Ich duży czas propagacji będący sumą czasów propagacji poszczególnych bloków. Jest to dużo w porównaniu z czasem propagacji układu nieiteracyjnego, który teoretycznie może być realizowany jako układ trójwarstwowy. Oczywiście w praktyce taka realizacja wymagałaby funktorów o dużej Ilości wejść, które nie są produkowane (maksymalnie 8 wejść).

Istnieją metody przyśpieszenia działania układów lteraeyjnych, ale będziemy o nich mówili przy omawianiu konkretnych układów lteraeyjnych w rozdziale 5*

2.4. HAZARD W UKIADACH KOiiBHTŚCTJHTCH

Jeżeli uwzględnimy istnienie czasu propagacji bramek, to w układach kombinacyjnych, podczas zmiany wartości sygnałów wejściowych, w sygnale wyjściowym mogą pojawiać się krótkie stany przejściowe zwane hazardem. Te stany przejściowe mogą czasami powodować nieprawidłowe działanie układów współpracujących z danym układem kombinacyjnym. Analizą przyczyn powstawania hazardu i Jego usuwaniem zajmiemy się poniżej.

Hazard statyczny jest to zjawisko polegające na tym, że przy zmianie wartości sygnału wejściowego, nie powodującej, z definicji danego układu, zmiany wartości sygnału wyjściowego, sygnał wyjściowy na chwilę się zmienia.

Przykład 2.10

Rozpatrzmy układ kombinacyjny realizujący funkcję

r'

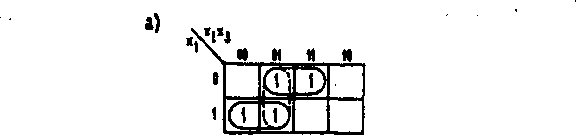

Rys. 2.19. Tablica Earnaugha (a) oraz schemat (b) układu z przykładu_2.10. Linią przerywaną oznaczono pary Jedynek, której odpowiada lmpllkant 52x3 oraz schemat układu po dodaniu tego impllkantu

|

*1 |

-1 |

|

i | |

|

H | |

|

i | |

|

1 | |

|

i r | i - | |

|

I |

-- i J f |

|

-u__ |

Rys. 2.20. Przykładowe przebiegi czasowe w układzie z rys. 2.19b ilustrujące powstawanie hazardu statycznego

Przeprowadzając minimalizację przy pomocy tabeli Karnaugba (rys. 2.l9a), otrzymujemy

7 = x1*3 + x1x2

b)

oraz schemat na bramkach NAND przedstawiony na rys. 2.19b.

Wyszukiwarka

Podobne podstrony:

062 063 62 O definiująca poszukiwany blok lteraoyjny. W wyniku syntezy tego układu otrzymujemy schem

062 063 62 Eliza Mytych. Ludwik Kumańskicp(to) Rys. 3.14. Charakterystyka logarytmiczna fazowa4. Ele

062 063 2 62 Programowanie liniowe ~l -1 -0,25 ~ V ~0~ 0 0,5 -0,125 8 2 0 0 0

062 063 62 Eliza Mytych. Ludwik Kumański Rys. 3.14. Charakterystyka logarytmiczna fazowa4. Elementy

PICT6413 Rzetelność definiowaną jako stosunek wariancji wyniku prawd/ wariancji wyników otrzymanych

IMG236 236 ‘l - 2**x •k ♦ 4 -c W wyniku rozwiązania tego równania otrzymujemy ■ 0,096 lub w procenta

page0068 62 DEFINIOYA I EPOKI FILOZOFII GRECKIEJ. pójść ta epoka trzecia? Czy do Justyniana? Byłaby

17836 shepherd c 062 063 Central Europę, 919—1125. (C) Yelhagen & Klafing.

Podstawowe definicje Błąd pomiaru - niezgodność wyniku pomiaru z wartością rzeczywistą

więcej podobnych podstron