Image49 (5)

JlLEKTRONIKAfPUfJjJ _

JlLEKTRONIKAfPUfJjJ _

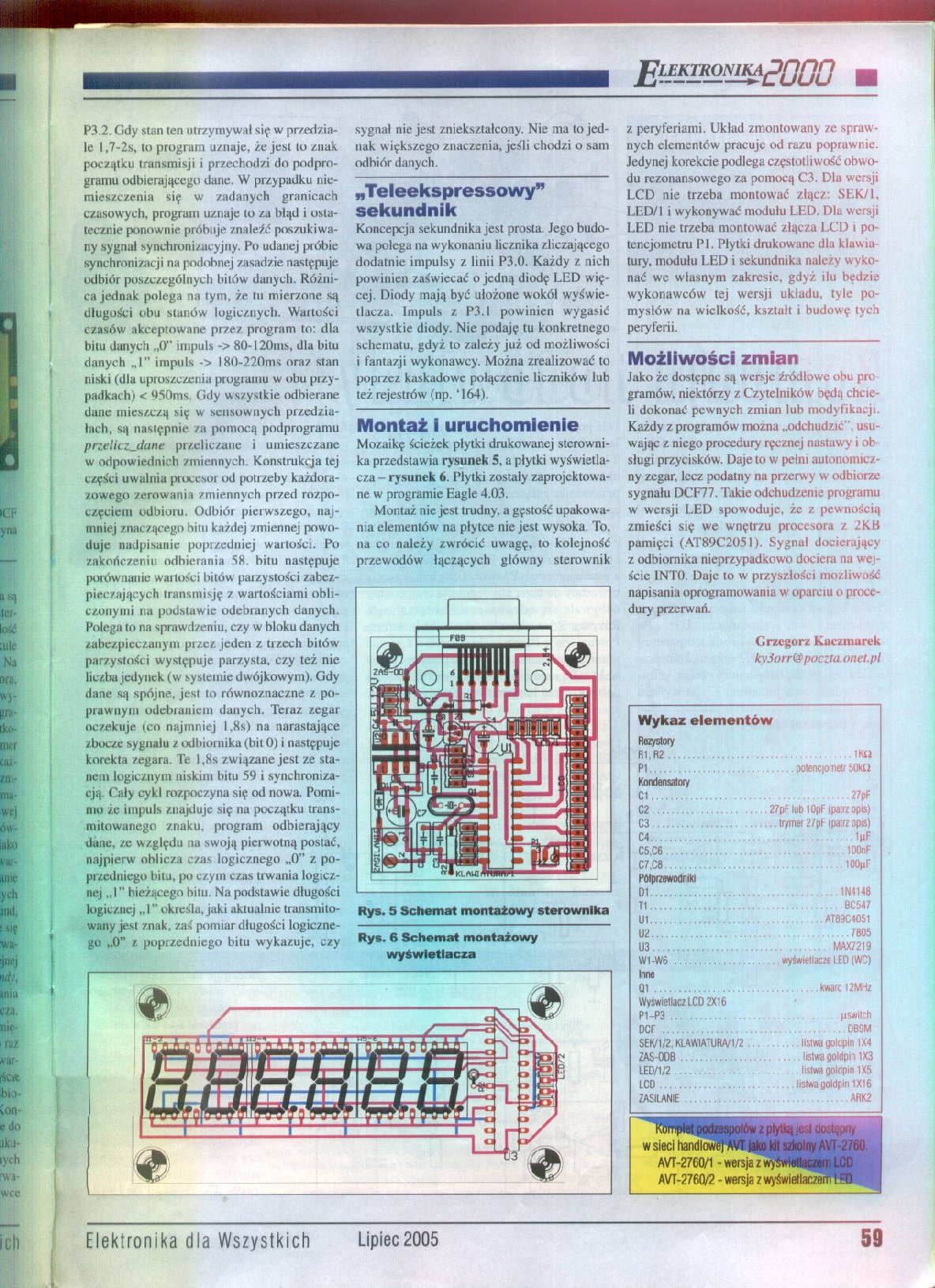

Rys. 6 Schemat montażowy wyświetlacza

P3.2. Gdy stan ten utrzymywał się w przedziale l,7-2s, to program uznaje, że jest to znak. początku transmisji i przechodzi do podprogramu odbierającego dane. W przypadku nie-mieszczenia się w zadanych granicach czasowych, program uznaje to za błąd i ostatecznie ponownie próbuje znaleźć poszukiwany sygnał synchronizacyjny. Po udanej próbie synchronizacji na podobnej zasadzie następuje odbiór poszczególnych bilów danych. Różnica jednak polega na tym, że tu mierzone są długości obu stanów logicznych. Wartości czasów akceptowane przez program to: dla bitu danych „0" impuls -> 80-120ms, dla bitu danych „1” impuls -■> 180-220ms oraz stan niski (dla uproszczenia programu w obu przypadkach) < 950ms. Gdy wszystkie odbierane dane mieszczą się w sensownych przedziałach, są następnie za pomocą podprogramu przelicz_dune przeliczane i umieszczane w odpowiednich zmiennych. Konstrukcja tej części uwalnia procesor od potrzeby każdorazowego zerowania zmiennych przed rozpoczęciem odbioru. Odbiór pierwszego, najmniej znaczącego bitu każdej zmiennej powoduje nadpisanie poprzedniej wartości. Po zakończeniu odbierania 58. hitu następuje porównanie wartości bitów parzystości zabezpieczających transmisję z wartościami obliczonymi na podstawie odebranych danych. Polega to na sprawdzeniu, czy w bloku danych zabezpieczanym przez jeden z trzech bitów parzystości występuje parzysta, czy też nie liczba jedynek (w systemie dwójkowym). Gdy dane są spójne, jest to równoznaczne z poprawnym odebraniem danych. Teraz zegar oczekuje (co najmniej 1,8s) na narastające zbocze sygnału z odbiornika (bit 0) i następuje korekta zegara. Te l,8s związane jest ze stanem logicznym niskim bitu 59 i synchronizacją. Gały cykl rozpoczyna się od nowa. Pomimo że impuls znajduje się na początku transmitowanego znaku, program odbierający dane, ze względu na swoją pierwotną postać, najpierw oblicza czas logicznego „0” z poprzedniego bitu, po czym czas trwania logicznej „I” bieżącego bitu. Na podstawie długości logicznej „1" określa, jaki aktualnie transmitowany jest znak, zaś pomiar długości logicznego „0" z poprzedniego bitu wykazuje, czy

sygnał nie jest zniekształcony. Nie ma to jednak w iększego znaczenia, jeśli chodzi o sam odbiór danych.

„Teleekspressowy”

sekundnik

Koncepcja sekundnika jest prosta. Jego budowa polega na wykonaniu licznika zliczającego dodatnie impulsy z linii P3.0. Każdy z nich powinien zaświecać o jedną diodę LED więcej. Diody mają być ułożone wokół wyświetlacza. Impuls z P3.1 powinien wygasić wszystkie diody. Nie podaję tu konkretnego schematu, gdyż to zależy już od możliwości i fantazji wykonawcy. Można zrealizować to popr zez kaskadowe połączenie liczników lub też rejestrów (np. ‘ 164).

Montaż i uruchomienie

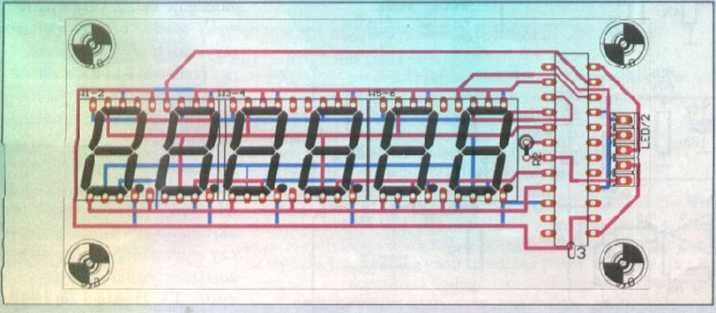

Mozaikę ścieżek płytki drukowanej sterownika przedstawia rysunek 5. a płytki wyświetlacza - rysunek 6. Płytki zostały zaprojektowane w programie Eagle 4.03.

Montaż nic jest trudny, a gęstość upakow a-nia elementów na płytce nie jest wysoka To. na co należy zwrócić uwagę, to kolejność przewodów łączących główny sterownik

Rys. 5 Schemat montażowy sterownika

z peryferiami. Układ zmontowany ze sprawnych elementów pracuje od razu poprawnie. Jedynej korekcie podlega częstotliwość obwodu rezonansowego za pomocą C3. Dla wersji LCD nie trzeba montować złącz: SEK/1, LED/1 i wykonywać modułu LED. Dla wersji LED nie trzeba montować złącza LUD i potencjometru PI. Płytki drukowane dlu klawiatury, modułu LED i sekundnika należy wykonać wc własnym zakresie, gdyż ilu będzie wykonawców tej wersji układu, tyle pomysłów na wielkość, kształt i budowę tych peryferii.

Możliwości zmian

Jako żc dostępne są wersje źródłowe obu programów. niektórzy z Czytelników będą chcieli dokonać pewnych zmian lub modyfikacji. Każdy z programów można „odchudzić”, usuwając z niego procedury ręcznej nustawy i ob sługi przycisków. Daje to w pełni autonomiczny zegar, lecz podatny na przerwy w odbiorze sygnału DCF77. Takie odchudzenie programu w wersji LED spowoduje, że z pewnością zmieści się we wnętrzu procesora z 2KB pamięci (AT89C2051). Sygnuł docierający z odbiornika nieprzypadkowo dociera na wejście INT0. Daje to w przyszłości możliwość napisania oprogramowania w oparciu o procedury przerwań.

Grzegorz Kaczmarek

kv3orr($ poczta. onet.pl

Wykaz elementów

Rez/story

|

R1.R2............... |

....................IKSZ |

|

P1.................... |

........Dotencjonar 50tó2 |

|

Kondensator/ Cl.................... |

..................27pF |

|

C2 ................. |

.. 27pF lub lOpF ipatrz opis) |

|

C3 ................... |

.....tr/mer 2/pP ipa:rz ope) |

|

C4.................. |

..................IliF |

|

C5.C6................... |

................ IDOnF |

|

C7.C8.................. |

............... lOOpF |

|

Pótprzewodrlkl 01...................... |

................1N4148 |

|

T1..................... |

................ BC547 |

|

Ul.................. |

............. AT89C4051 |

|

U2.................... |

..................7805 |

|

U3...................... |

.............. MAX7219 |

|

W1-W6 ................ |

. ... wyświetlacze LED (W") |

|

hne Q1 ................... |

............Kwarc 12MHz |

|

Wyświetlacz LCD 2X16 | |

|

P1-P3 ............... |

............... pswitsh |

|

ocr.................. |

.................DBGM |

|

SfiK/1/2, KLW1ATURA/1/2 .. |

........listwa golcpin 1X4 |

|

2AS-0DB.............. |

........listwa goldph 1X3 |

|

LED/1/2.............. |

listwa goldpin 1X5 |

|

LCD.................... |

.......listwa goldpin 1X16 |

|

ZASILANIE ............. |

..................ARK2 |

w sieci handlt AVT-2760/1 - wersja z i WT-2760/2 - wersja z wyświetlacze!

Elektronika dla Wszystkich Lipiec2005 59

Wyszukiwarka

Podobne podstrony:

Image44 (8) J^LEKTROMKA^UUjJ — Rys. 2 Schemat montażowyDo czego to służy? Wszystkie układy elektroni

Image48 (7) O 2 C2 47uF/25V R13 Rys. 1 Schemat ideowy Rys. 2 Schemat montażowy Rozpoczyna się

Image44 (3) Forum Czytelników Forum Czytelników Rys. 2 Schemat montażowy Rys. 3 Połączenie gniazda D

15690 Pict0039 (4) JjLEKTRONIKAPjJjJjJ JjLEKTRONIKAPjJjJjJ Rys. 2 Schemat montażowy Wykaz

81584 Image221 (2) Forum Czytelników Rys. 4 Schemat montażowy zasilacza Rys. 5 Schemat montażowy kla

więcej podobnych podstron