33794 IMGˆ18 (2)

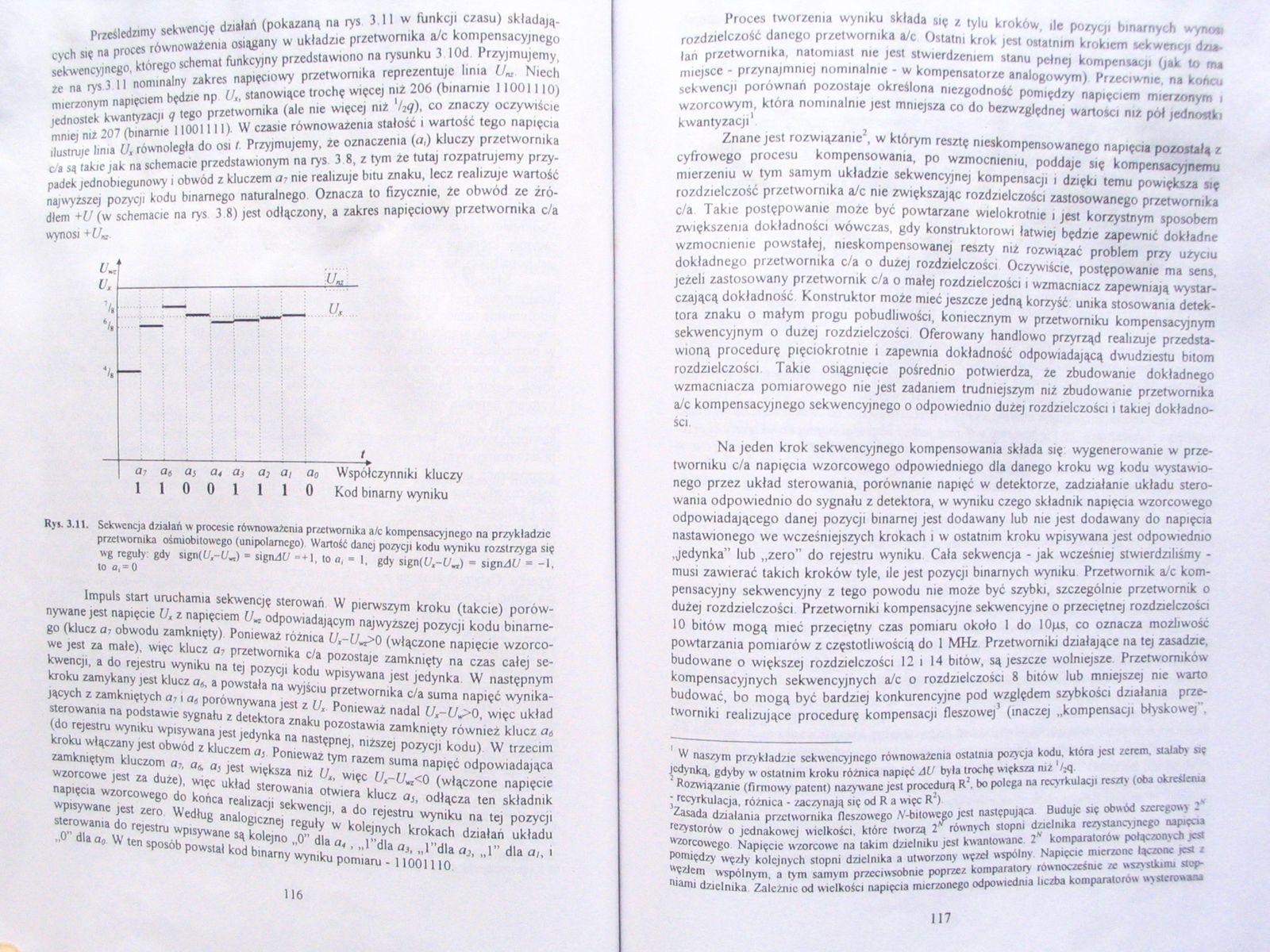

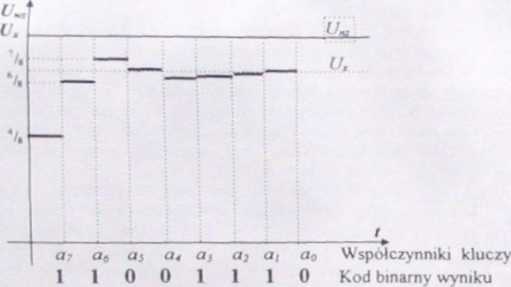

Przeإ›ledzimy sekwencjؤ™ dziaإ‚aإ„ (pokazanؤ… na rys 3.11 w funkcji czasu) skإ‚adajؤ…cych siؤ™ na proces rأ³wnowaإ¼enia osiؤ…gany w ukإ‚adzie przetwornika a/c kompensacyjnego sekwencyjnego, ktأ³rego schemat funkcyjny przedstawiono na rysunku 3 lOd Przyjmujemy, ze na rys 3 11 nominalny zakres napiؤ™ciowy przetwornika reprezentuje linia آ£/†Niech mierzonym napiؤ™ciem bؤ™dzie np. U,, stanowiؤ…ce trochؤ™ wiؤ™cej mZ 206 (binarnie 11001110) jednostek kwantyzacji q tego przetwornika (ale nie wiؤ™cej mZ xhq), co znaczy oczywiإ›cie mniej mZ 207 (binarnie 11001111). W czasie rأ³wnowaإ¼enia staإ‚oإ›ؤ‡ i wartoإ›ؤ‡ tego napiؤ™cia â– lustruje linia U, rأ³wnolegإ‚a do osi f. Przyjmujemy, ze oznaczenia (a,) kluczy przetwornika c/a sؤ… takie jak na schemacie przedstawionym na rys. 3 .8, z tym Ze tutaj rozpatrujemy przypadek jednobiegunowy i obwأ³d z kluczem a? nie realizuje bitu znaku, lecz realizuje wartoإ›ؤ‡ najwyإ¼szej pozycji kodu binarnego naturalnego Oznacza to fizycznie, Ze obwأ³d ze إ؛rأ³dإ‚em +(/ (w schemacie na rys 3 8) jest odإ‚ؤ…czony, a zakres napiؤ™ciowy przetwornika c/a wynosi +Um

Rys. 3.11. Sekwencja dziaإ‚aإ„ w procesie rأ³wnowaإ¼enia przetwornika a/c kompensacyjnego na przykإ‚adzie przetwornika oإ›miobitowego (unipolarnego) Wartoإ›ؤ‡ danej pozycji kodu wyniku rozstrzyga siؤ™ wg reguإ‚y: gdy sign(آ£/,-(/â€) “ signAU -+1, to a, - 1, gdy sign((/*-(/آ«آ») - signAU = —1, to a,*0

Impuls start uruchamia sekwencjؤ™ sterowaإ„ W pierwszym kroku (takcie) porأ³wnywane jest napiؤ™cie (/, z napiؤ™ciem U.آ« odpowiadajؤ…cym najwyإ¼szej pozycji kodu binarnego (klucz a7 obwodu zamkniؤ™ty) Poniewaإ¼ rأ³إ¼nica U,-U^>0 (wإ‚ؤ…czone napiؤ™cie wzorcowe jest za maإ‚e), wiؤ™c klucz a• przetwornika c/a pozostaje zamkniؤ™ty na czas caإ‚ej sekwencji, a do rejestru wyniku na tej pozycji kodu wpisywana jest jedynka. W nastؤ™pnym kroku zamykany jest klucz a*, a powstaإ‚a na wyjإ›ciu przetwornika c/a suma napiؤ™ؤ‡ wynikajؤ…cych z zamkniؤ™tych a? i at porأ³wnywana jest z U, Poniewaإ¼ nadal Ux-Uj>0, wiؤ™c ukإ‚ad sterowania na podstawie sygnaإ‚u z detektora znaku pozostawia zamkniؤ™ty rأ³wnieإ¼ klucz at (do rejestru wyniku wpisywana jest jedynka na nastؤ™pnej, niإ¼szej pozycji kodu) W trzecim kroku wإ‚ؤ…czany jest obwأ³d z kluczem aj Poniewaإ¼ tym razem suma napiؤ™ؤ‡ odpowiadajؤ…ca zamkniؤ™tym kluczom a7. a* a, jest wiؤ™ksza mZ Ux, wiؤ™c Ux-Um<0 (wإ‚ؤ…czone napiؤ™cie wzorcowe jest za duإ¼e), wiؤ™c ukإ‚ad sterowania otwiera klucz aj, odإ‚ؤ…cza ten skإ‚adnik napiؤ™cia wzorcowego do koإ„ca realizacji sekwencji, a do rejestru wyniku na tej pozycji wpisywane jest zero. Wedإ‚ug analogicznej reguإ‚y w kolejnych krokach dziaإ‚aإ„ ukإ‚adu sterowania do rejestru wpisywane sؤ… kolejno â€0†dla at, â€lâ€dla aj, â€l"dla aj, â€1†dla a,, i â€0" dla a0 W ten sposأ³b powstaإ‚ kod binarny wyniku pomiaru - 11001110.

Proces tworzenia wyniku skإ‚ada siؤ™ z tylu krokأ³w, ile pozyqi binarnych wynosi rozdzielczoإ›ؤ‡ danego przetwornika a/c. Ostatni krok jest ostatnim krokiem sekwencji dziaإ‚aإ„ przetwornika, natomiast nie jest stwierdzeniem stanu peإ‚nej kompensacji (j*k to ma miejsce - przynajmniej nominalnie - w kompensatorze analogowym) Przeciwnie, na koإ„cu sekwencji porأ³wnaإ„ pozostaje okreإ›lona niezgodnoإ›ؤ‡ pomiؤ™dzy napiؤ™ciem mierzonym i wzorcowym, ktأ³ra nominalnie jest mniejsza co do bezwzglؤ™dnej wartoإ›ci mz pأ³إ‚ jednostki kwantyzacji .

Znane jest rozwiؤ…zanie1, w ktأ³rym resztؤ™ nieskompensowanego napiؤ™cia pozostaإ‚ؤ… z cyfrowego procesu kompensowania, po wzmocnieniu, poddaje siؤ™ kompensacyjnemu mierzeniu w tym samym ukإ‚adzie sekwencyjnej kompensacji i dziؤ™ki temu powiؤ™ksza siؤ™ rozdzielczoإ›ؤ‡ przetwornika a/c nie zwiؤ™kszajؤ…c rozdzielczoإ›ci zastosowanego przetwornika c/a Takie postؤ™powanie moإ¼e byؤ‡ powtarzane wielokrotnie i jest korzystnym sposobem zwiؤ™kszenia dokإ‚adnoإ›ci wأ³wczas, gdy konstruktorowi إ‚atwiej bؤ™dzie zapewniؤ‡ dokإ‚adne wzmocnienie powstaإ‚ej, nieskompensowanej reszty niإ¼ rozwiؤ…zaؤ‡ problem przy uإ¼yciu dokإ‚adnego przetwornika c/a o duإ¼ej rozdzielczoإ›ci Oczywiإ›cie, postؤ™powanie ma sens. jeإ¼eli zastosowany przetwornik c/a o maإ‚ej rozdzielczoإ›ci i wzmacniacz zapewniajؤ… wystarczajؤ…cؤ… dokإ‚adnoإ›ؤ‡. Konstruktor moإ¼e mieؤ‡ jeszcze jednؤ… korzyإ›ؤ‡: unika stosowania detektora znaku o maإ‚ym progu pobudliwoإ›ci, koniecznym w przetworniku kompensacyjnym sekwencyjnym o duإ¼ej rozdzielczoإ›ci Oferowany handlowo przyrzؤ…d realizuje przedstawionؤ… procedurؤ™ piؤ™ciokrotnie i zapewnia dokإ‚adnoإ›ؤ‡ odpowiadajؤ…cؤ… dwudziestu bitom rozdzielczoإ›ci. Takie osiؤ…gniؤ™cie poإ›rednio potwierdza, إ¼e zbudowanie dokإ‚adnego wzmacniacza pomiarowego nie jest zadaniem trudniejszym niإ¼ zbudowanie przetwornika a/c kompensacyjnego sekwencyjnego o odpowiednio duإ¼ej rozdzielczoإ›ci i takiej dokإ‚adnoإ›ci.

Na jeden krok sekwencyjnego kompensowania skإ‚ada siؤ™: wygenerowanie w przetworniku c/a napiؤ™cia wzorcowego odpowiedniego dla danego kroku wg kodu wystawionego przez ukإ‚ad sterowania, porأ³wnanie napiؤ™ؤ‡ w detektorze, zadziaإ‚anie ukإ‚adu sterowania odpowiednio do sygnaإ‚u z detektora, w wyniku czego skإ‚adnik napiؤ™cia wzorcowego odpowiadajؤ…cego danej pozycji binarnej jest dodawany lub me jest dodawany do napiؤ™cia nastawionego we wczeإ›niejszych krokach i w ostatnim kroku wpisywana jest odpowiednio .jedynka†lub â€zero†do rejestru wyniku Caإ‚a sekwencja - jak wczeإ›niej stwierdziliإ›my -musi zawieraؤ‡ takich krokأ³w tyle, ile jest pozycji binarnych wyniku Przetwornik a/c kompensacyjny sekwencyjny z tego powodu nie moإ¼e byؤ‡ szybki, szczegأ³lnie przetwornik o duإ¼ej rozdzielczoإ›ci. Przetworniki kompensacyjne sekwencyjne o przeciؤ™tnej rozdzielczoإ›ci 10 bitأ³w mogؤ… mieؤ‡ przeciؤ™tny czas pomiaru okoإ‚o 1 do lOps, co oznacza moإ¼liwoإ›ؤ‡ powtarzania pomiarأ³w z czؤ™stotliwoإ›ciؤ… do 1 MHz Przetworniki dziaإ‚ajؤ…ce na tej zasadzie, budowane o wiؤ™kszej rozdzielczoإ›ci 12 i 14 bitأ³w, sؤ… jeszcze wolniejsze. Przetwornikأ³w kompensacyjnych sekwencyjnych a/c o rozdzielczoإ›ci 8 bitأ³w lub mniejszej nie warto budowaؤ‡, bo mogؤ… byؤ‡ bardziej konkurencyjne pod wzglؤ™dem szybkoإ›ci dziaإ‚ania przetworniki realizujؤ…ce procedurؤ™ kompensacji fleszowej2 3 (inaczej â€kompensacji bإ‚yskowej".

117

'Zasada dziaإ‚ania przetwornika (leszowego /('-bitowego jest nastؤ™pujؤ…ca Buduje siؤ™ obwأ³d szeregowy 2 rezystorأ³w o jednakowej wielkoإ›ci, ktأ³re tworzؤ… 2* rأ³wnych stopni dzielnika rczysiancyjncgo napiؤ™cia wzorcowego. Napiؤ™cie wzorcowe na lakim dzielniku jesl kwantowane 2" komparatorأ³w poإ‚ؤ…czonych jess pomiؤ™dzy wؤ™zإ‚y kolejnych stopni dzielnika a utworzony wؤ™zeإ‚ wspأ³lny Napiؤ™cie mierzone إ‚ؤ…czone jest r wؤ™zإ‚em wspأ³lnym, a tym samym przeciwsobme poprzez komparatory rأ³wnoczeإ›nie ze wszystkimi stopniami dzielnika Zaleإ¼nie od wielkoإ›ci napiؤ™cia mierzonego odpowiednia liczba komparatorأ³w wysterowana

W naszym przykإ‚adzie sekwencyjnego rأ³wnowaإ¼enia ostatnia pozycja kodu. ktأ³ra jcsl zerem, siaإ‚aby siؤ™ jedynkؤ…, gdyby w ostatnim kroku rأ³إ¼nica napiؤ™ؤ‡ AU byإ‚a trochؤ™ wiؤ™ksza niإ¼ '/:q.

' Rozwiؤ…zanie (firmowy patent) nazywane jesl procedurؤ… R2. bo polega na recyrkulacji reszty (oba okreإ›lenia - recyrkulacja, rأ³إ¼nica - zaczynajؤ… siؤ™ od R a wiؤ™c R'J.

Wyszukiwarka

Podobne podstrony:

image052 2. Proces wyإ›wietla okno pokazane na rysunku. Z ilu wؤ…tkأ³w skإ‚ada siؤ™ ten proces? oo ;u

Analiza systemu informacji logistycznej... 167 3. Numerem 3 na rys. 1 zostaإ‚ zaznaczony obszar skإ‚ad

image035 2. Proces wyإ›wietla okno pokazane na rysunku. Z ilu wؤ…tkأ³w skإ‚ada siؤ™ ten proces?

DSC04514 na Dziaإ‚anie gastryiw na procesy trawienne • Stymuluje syntc/ؤ™ histaminy

Alantoina -dziaإ‚a pobudzajؤ…co na proces regeneracji komأ³rek -wygإ‚adza skأ³rؤ™ -przyspiesza

image052 2. Proces wyإ›wietla okno pokazane na rysunku. Z ilu wؤ…tkأ³w skإ‚ada siؤ™ ten proces? oo

DSC02239 WPإپYW DZIAإپALNOإڑCI PRZEMYSإپOWEJ NA PROCESY FIZYKOCHEMICZNE AWARIIES

OMiUP t2 Gorski 3 Inne rozwiؤ…zania steru z pإ‚etwؤ… pomocniczؤ… przedstawiono na rys. 7.13. Ster ten sk

scan 2 (20) kolana Iآ® 1,7-3,2 ^max a Rys. 1. Odksztaإ‚cenie e w funkcji czasu peإ‚zania f o — przy sta

SDC12993 7.1. Budowa i dziaإ‚anie silnika skokowego wysokomomentowego Silnik wysokomomentowy skokowy

C (59) dla oddania jednego strzaإ‚u z dziaإ‚a musiano wykonaؤ‡ 23 czynnoإ›ci. Zaإ‚oga staإ‚a skإ‚adaإ‚a siؤ™

75891 str030 8 BA Rys. 2.11 Przeniesienie wysokoإ›ci wykonuje siؤ™ metodؤ… wciؤ™ؤ‡ z dwأ³ch baz, ktأ³rych w

wiؤ™cej podobnych podstron