38033 Untitled34

60 7. Port\

wyjściowym portu. Informacja wpisywana do rejestru jest przekazywana bez pośrednio na końcówkę portu.

60 7. Port\

odczyt rejestru

VCC

wewnętrzna

magistrala

danych

jestru -^1

t

wpis do rejestru

|

- o Q C Q |

T—T ij i |

|

'h | |

|

J_ |

końcówka

Pin

-o

odczyt pH końcówki i

Rys. 7-4. Schemat portu jednofunkcyjnego.

Zastosowanie jako obciążenia tranzystora wyjściowego portu źródła prądi wego daje to, że zwarcie wyjść portów do masy nie powoduje ich zniszcz nia. Natomiast zwarcie końcówki do zasilania przy stanie zera logiczneg końcówki może zniszczyć tranzystor wyjściowy.

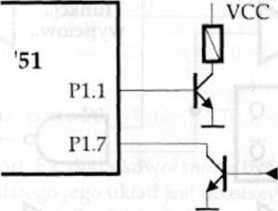

Do wejść portów można dołączać układy typu „otwarty kolektor", rys nek 7-5 - linia PI .7, gdyż obciążeniem dla nich jest właśnie źródło prądowe po tu, albo bezpośrednio sterować bazę tranzystora ponieważ odpowiedni prą< bazy jest dostarczany ze źródła prądowego portu, rysunek 7-5 linia Pl.l.

Rys. 7-5. Bezpośrednie połączenie tranzystorów z portami.

W wykonaniach standardowych mikrokontrolerów rodziny '51 wyjść portów, poza portem PO, mogą sterować czterema wejściami TTL LS, natom mogą być sterowane układami TTL lub NMOS z otwartym kolektorem lub nem. Wyjścia portu PO mogą sterować ośmioma bramkami TTL LS. Jakie są czywiste dopuszczalne obciążenia portów należy sprawdzać w danych kat

krokontrolery rodziny '51 firmy ATMEI. dopuszczają wartość prądu płynącego przez tranzystor wyjściowy portu do 20 mA, co umożliwia bezpośrednie dołączenie do wyjścia portu diody LED lub wskaźnika 7-segmentowego.

Z rysunków 7-1 •*- 7-4 wynika, że na wewnętrzną magistralę danych można przesyłać stan wyjścia rejestru portu lub jego końcówki. Może to wprowadzać niejednoznaczność przy pobieraniu informacji z portu. Na przykład, jeżeli sterujemy tranzystor, jak na rysunku 7-5, to w celu włączenia tranzystora do komórki rejestru portu (Pl.l) wpisujemy stan jedynki logicznej. Ponieważ napięcie nasycenia złącza baza - emiter tranzystora wynosi 0,6 + 0,7 V, to odczytując stan końcówki tego portu otrzymamy wartość zera logicznego.

Rozkazy odczytujące zawartość rejestru portu są to rozkazy, których wykonanie równocześnie modyfikuje ich zawartość (Read-Modify-Write Instruc-tions), natomiast rozkazy czytające stan końcówki portu są to rozkazy, które nie wpisują wyniku operacji do rejestru portu.

Zestawy tych rozkazów są przedstawione w tabeli 7-1.

iTabela 7-1 Wykaz rozkazów operujących na rejestrach lub końcówkach portów.

|

Rozkazy czytające rejestry portów |

Rozkazy czytające końcówki portów | ||||||

|

IIanl |

Pn,r |

(ANL |

Pl/A) |

ANL |

r,Pn |

(ANL |

DPL,P1) |

|

IjORL |

Pn,r |

(ORL |

P3,B) |

ORL |

r,Pn |

(ORL |

B,P3) |

|

IUrl |

Pn,r |

(XRL |

Pl,2Fh) |

XRL |

r,Pn |

(XRL |

23h,Pl) |

|

[Ijbc |

Pn.y,E TA (JBC |

PI.3,PĘTLA) |

JB |

Pn.y,E TA (JB |

PI.7,SKOK) | ||

|

ICPL |

Pn.y |

(CPL |

P3.4) |

JNB |

Pn.y,E_TA (JNB |

P1.2,TAB1) | |

|

[INC |

Pn |

(INC |

PI) |

CJNE |

A,Pn,E-TA |

(CJNE |

A,P3,Z 1) |

|

II DEC |

Pn |

(DEC |

P3) |

MOV |

r,Pn |

(MOV |

A,PI) |

|

|DJN7 |

Pn,E-TAl |

(DJNZ |

P1,PETLA2) |

ADD |

A,Pn |

(ADD |

A,P2) |

|

|| VIO V |

Pn.y,C |

(MOV |

P3.4,C) |

ADDC |

A,Pn |

(ADDC A,P3) | |

|

■CLK |

Pn.y |

(CLR |

PI .5) |

SUBB |

A,Pn |

(SUBB |

A,PI) |

|

■SET |

Pn.y |

(SET |

Pl.l) |

XCH |

A,Pn |

(XCH |

A,P3) |

|

PUSH |

Pn |

(PUSH PI) | |||||

idzie: n - numer portu

r - rejestr SFR lub komórka pamięci

y - numer bitu portu E_TA - etykieta

Rejestry portów PO * P3 znajdują się w obszarze SFR pod tymi samymi Iresami we wszystkich mikrokontrolerach rodziny '51. Wszystkie bity tych '.terech portów mają tę właściwość, że posiadają własny indywidualny adres i logą być ustawiane niezależnie odpowiednimi rozkazami. Najmniej znaczący it ma adres odpowiadający adresowi całego rejestru.

Wyszukiwarka

Podobne podstrony:

Image144 stany: A = 1, B — C — ... / = 0. Następnie informacja jest wpisywana do rejestru. Po ośmiu

System informacyjny (2) Wyjściami są informacje dostarczane do otoczenia lub do innych systemów

Image144 stany: A = 1, B — C — ... / = 0. Następnie informacja jest wpisywana do rejestru. Po ośmiu

35 (29) 70 Port szeregowy, tryby 1, 2,3 jest wpisywane do rejestru wejściowego SBUF. W trybach 2 i 3

Image170 — przesłanie informacji z akumulatora do rejestru pamięci (otwarte

Image534 wyjść enkodera jest wpisywany do rejestru równoległego. Jeśli żaden klawisz klawiatury nie

Fundacja dla Zwierząt ARGOS Informacja dodatkowa do sprawozdania finansowego za 2008 r. Bilans

DODATKOWE INFORMACJE I OBJAŚNIENIA DO SPRAWOZDANIA FINANSOWEGO ZA 2010 ROKSTOWARZYSZENIA NA RZECZ RO

Szkoła Podstawowa nr 92 w Gdańsku informuje o naborze do klasy sportowej o profilu piłki ręcznej na

Podmioty wpisywane do Rejestru dłużników niewypłacalnych: osoby fizyczne wykonujące działalność

59 (100) ma związek z kanałami dystrybucji informacji i dostosowaniem do nich formy przekazu. Wyróżn

60 (164) gdzie: k-1 (58) / 2ic przy czym zł/? jest to spadek ciśnienia na długości rury, a pQ —

więcej podobnych podstron