24 (48)

48 Zegar systemowy, cykl rozkazowy

zegara zewnętrznego, poza wymaganiem minimalnego czasu trwania (20 ns) stanu niskiego i wysokiego (patrz punkt 1.22).

Z sygnału zegarowego o częstotliwości £ktal (zewnętrznego lub wewnętrznego) jest wytwarzany właściwy dwufazowy sygnał taktujący procesor o częstotliwości dwukrotnie mniejszej. Sygnał ten nie jest dostępny na zewnątrz układu.

Cykl ludwnouy

Cykl iitMiunouy

| SI i S2 j S3 j S4 : SS | 56 j Sl i S2 i S3 ; S4 : SS ; SS i SI jPl P8iPl P2»>1 P2 jpi P2!P1 P2iPl P2>»1 P2ŚP1 P2|P1 P2lpi P2iPl P2 5P1 P2iPi P2

■innitniiiiM^ i_4n__n_|n_TL_tn

| fPobr«i b > ^ M.rożka:

1 bajt, 1 cykl Cnp. ADD A.R5> f

Pobrani* kodu ["Pobrani* kodu

iZU

pj n**t«5Pn*oo roikty LCJ*iou*5 | I Pobrani * kodu

r----i na»t«pn*90 rozkazu

I i LCpoutórna>

|

Sl |

S2 |

S3 |

S4 |

SS |

Pobrani* kodu fPobrani* dru9i*90

2 bajtw, 1 cykl Cna. ADO A.*55

|

Si |

S2 |

53 |

54 |

SS |

("Pobrani* kodu n.na*t^pn*90 rozkazu

I

di I

1 bajt, 2 cykl* Cna. RET 5 1

|

("Pobrani* kodu |

_ i {Pobrani* kodu |

J |

|

Lrozkazu |

pi na»t*pn*90 rozkazu l_CJaVow*3ł |

rt |

|

r |

« i |

^ L |

Pobrani* kodu na*t*pn*90 rozkazu Cpoutdrn*i

|

Si |

S2 |

53 |

S4 |

SS |

S6 |

Sl |

52 |

S3 |

54 |

SS |

SS |

~y_

Si

Pobrani* kodu naat«tan*90 rozkazu!

("Pobrani* kodu {"Pobrani* ("Pobrani*

[Lrozkazu pjdrugi*90 | pjtrx«ci*go

Lbajtu

|

LJMP > 1 ♦ |

t t |

si i | ||||||||||||

|

Sl |

52 |

S3 |

S4 |

SS |

SS |

Sl |

52 |

S3 |

54 |

SS |

SS | |||

|

("Pobrani* kodu Lrozkazu |

fPobrani* kodu |

ni* <n* |

|

pj na»t*pn*ao rozkazu ipobrani 1CJal-ou*) 1 1 | ||

|

1 |

nl* ma ALE | |

|

4 |

' | |

t >

MOVX

ł

Pobrani* kodu n«»tępnggo rozkazu

■ Cpoutdr^ł.2--

SS

Si

Do»t«P do z«unątrxn*J aamiRci danych

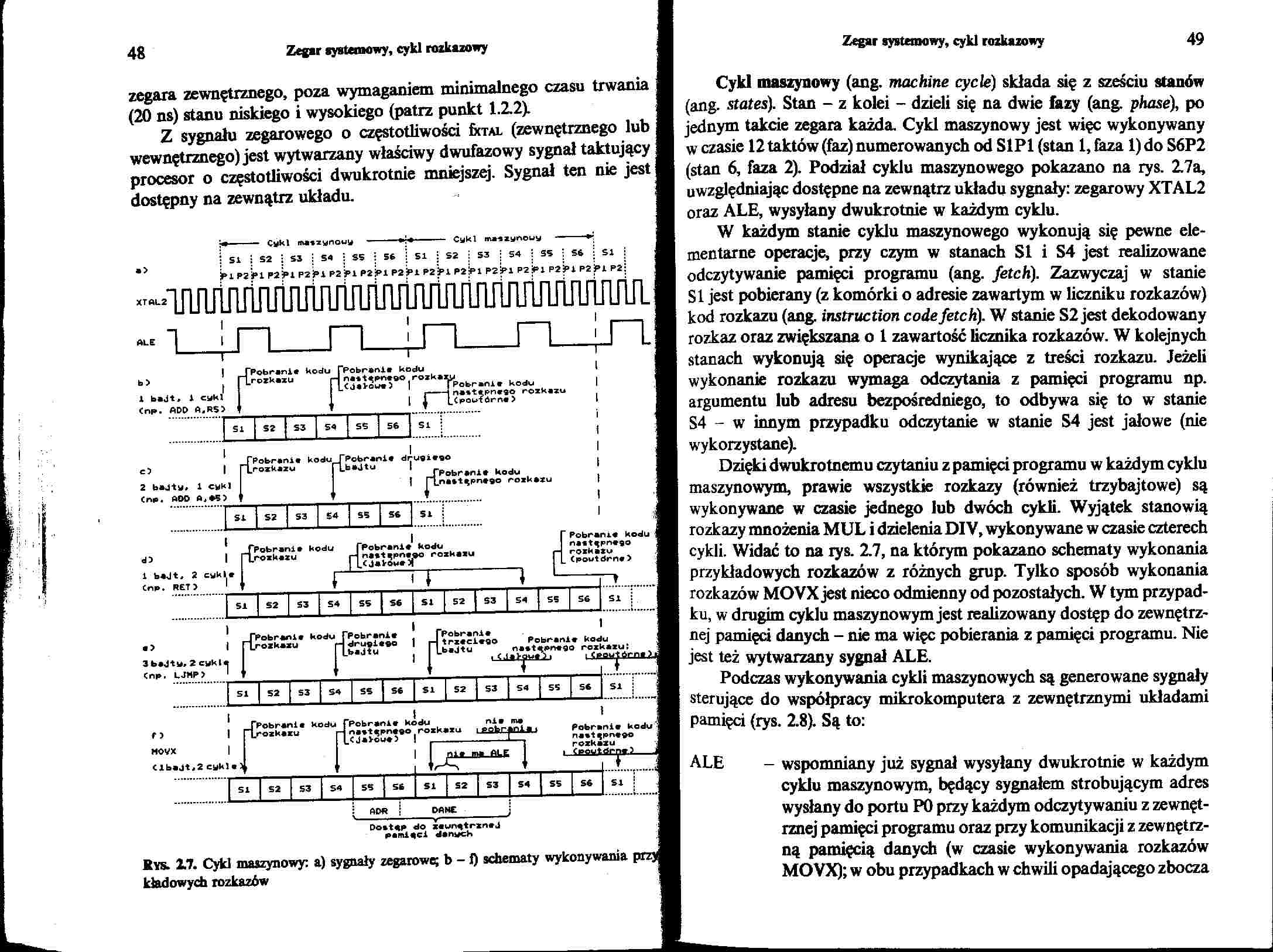

Rys. 2.7. Cykl maszynowy, a) sygnały zegarowe; b - f) schematy wykonywania przj kładowych rozkazów

Cykl maszynowy (ang. machinę cycle) składa się z sześciu stanów (ang. States). Stan - z kolei - dzieli się na dwie fazy (ang phase), po jednym takcie zegara każda. Cykl maszynowy jest więc wykonywany w czasie 12 taktów (faz) numerowanych od S1P1 (stan 1, faza 1) do S6P2 (stan 6, faza 2). Podział cyklu maszynowego pokazano na rys. 17a, uwzględniając dostępne na zewnątrz układu sygnały: zegarowy XTAL2 oraz ALE, wysyłany dwukrotnie w każdym cyklu.

W każdym stanie cyklu maszynowego wykonują się pewne elementarne operacje, przy czym w stanach Sl i S4 jest realizowane odczytywanie pamięci programu (ang. fetch). Zazwyczaj w stanie Sl jest pobierany (z komórki o adresie zawartym w liczniku rozkazów) kod rozkazu (ang instruction codę fetch). W stanie S2 jest dekodowany rozkaz oraz zwiększana o 1 zawartość licznika rozkazów. W kolejnych stanach wykonują się operacje wynikające z treści rozkazu. Jeżeli wykonanie rozkazu wymaga odczytania z pamięci programu np. argumentu lub adresu bezpośredniego, to odbywa się to w stanie S4 - w innym przypadku odczytanie w stanie S4 jest jałowe (nie wykorzystane).

Dzięki dwukrotnemu czytaniu z pamięci programu w każdym cyklu maszynowym, prawie wszystkie rozkazy (również trzybajtowe) są wykonywane w czasie jednego lub dwóch cykli. Wyjątek stanowią rozkazy mnożenia MUL i dzielenia DIV, wykonywane w czasie czterech cykli. Widać to na rys. 17, na którym pokazano schematy wykonania przykładowych rozkazów z różnych grup. Tylko sposób wykonania rozkazów MOVX jest nieco odmienny od pozostałych. W tym przypadku, w drugim cyklu maszynowym jest realizowany dostęp do zewnętrznej pamięci danych - nie ma więc pobierania z pamięci programu. Nie jest też wytwarzany sygnał ALE.

Podczas wykonywania cykli maszynowych są generowane sygnały sterujące do współpracy mikrokomputera z zewnętrznymi układami pamięci (rys. 2.8). Są to:

ALE - wspomniany już sygnał wysyłany dwukrotnie w każdym cyklu maszynowym, będący sygnałem strobującym adres wysłany do portu PO przy każdym odczytywaniu z zewnętrznej pamięci programu oraz przy komunikacji z zewnętrzną pamięcią danych (w czasie wykonywania rozkazów MOVX); w obu przypadkach w chwili opadającego zbocza

Wyszukiwarka

Podobne podstrony:

25 (46) 50 Zegar systemowy, cykl rozkazowy sygnału ALE adres jest obecny na porcie PO i dotyczj najb

Nowy 2 2 7. System wielodostępny to taki, który z zasady: a. Wymaga podziału czasu

lichtarski (24) 48 _1, Przedmiot 1 ewolucja nauki o pradiiębioratwic_ dzenie głosi

Zad. 4. Oblicz. Przedstaw wynik w najprostszej postaci. 4 1 a)7+r 13 37 b — + — = 24 48 c)

— 440 — Moyennes : C % : 65,24 H % 7,48. Calcule pour C23 H3207 : C 65,69 H : 7,67 %. Action de l’ac

Zagęszczone osady są wprowadzane do reaktora w cyklach 24-48 h. aby dobrze shigienizować osad Osady

44665 Slajd22 (48) Podział Systemów Ekspertowych ze względu sposób pozyskiwania wiedzy: PŁYTKIE - wi

E coli diagnostyka E. coli urynow & Przednamnażanie na bulionie z siarczanem laurynowym i pepto

- Okres połtrwania 24-48 godz. y - W 90%

60692 Untitled Scanned 24 - 48 - dowanych z elementów innych rodzajów, pełnią często rolę wzmacniacz

48 Le systeme social se reproduit par la communication. II est donc mouvement, ou, comme 1’enonce Lu

48 A.S. Jagiełło, Systemy elektromechaniczne dla elektryków Teraz wyrażenie (6.5) wynikające z drugi

więcej podobnych podstron