41 (34)

82 Inicjowanie lyitana

(+5 V) na wejściu zerującym RST/VPD. Do wyzerowania mikrokomputera podczas pracy sytemu (gdy normalnie pracuje generator) jest wymagane utrzymanie sygnału zerującego na RST/YPD przez czas trwania co najmniej 2 cykli maszynowych (12 okresów oscylatora). Natomiast po włączeniu zasilania konieczne jest, aby stan wysoki na wejściu RST/YPD trwał co najmniej 10 ms od chwili osiągnięcia przez napięcie zasilania wymaganego poziomu, tzn. przez czas potrzebny do ustabilizowania się generatora (plus dwa cykle maszynowe).

W wyniku zerowania systemu do rejestrów specjalnych (SFR) wpisują się następujące wartości'

|

PC |

0000H |

|

ACC |

OOH |

|

B |

00H |

|

PSW |

OOH |

|

SP |

07H |

|

DPTR |

0000H |

|

P0-P3 |

OFFH |

|

IP |

ntOOOOOOB |

|

IE |

0x00000GB |

|

TMOD |

OOH |

|

TCON |

OOH |

|

T2CON |

OOH |

|

THO |

OOH |

|

TLO |

OOH |

|

TH1 |

OOH |

|

TLI |

OOH |

|

TH2 |

OOH |

|

TL2 |

OOH |

|

RLD |

OOOOH |

|

SCON |

OOH |

|

SBUF |

nieokreślona |

|

PCON |

0xxx0000B |

|

W czasie zerowania systemu zawartość użytkowej częśd wewnętrz- | |

nęj pamięci danych nie ulega zmianie, więc po inicjowaniu w wyniku włączenia zasilania jest ona nieokreślona.

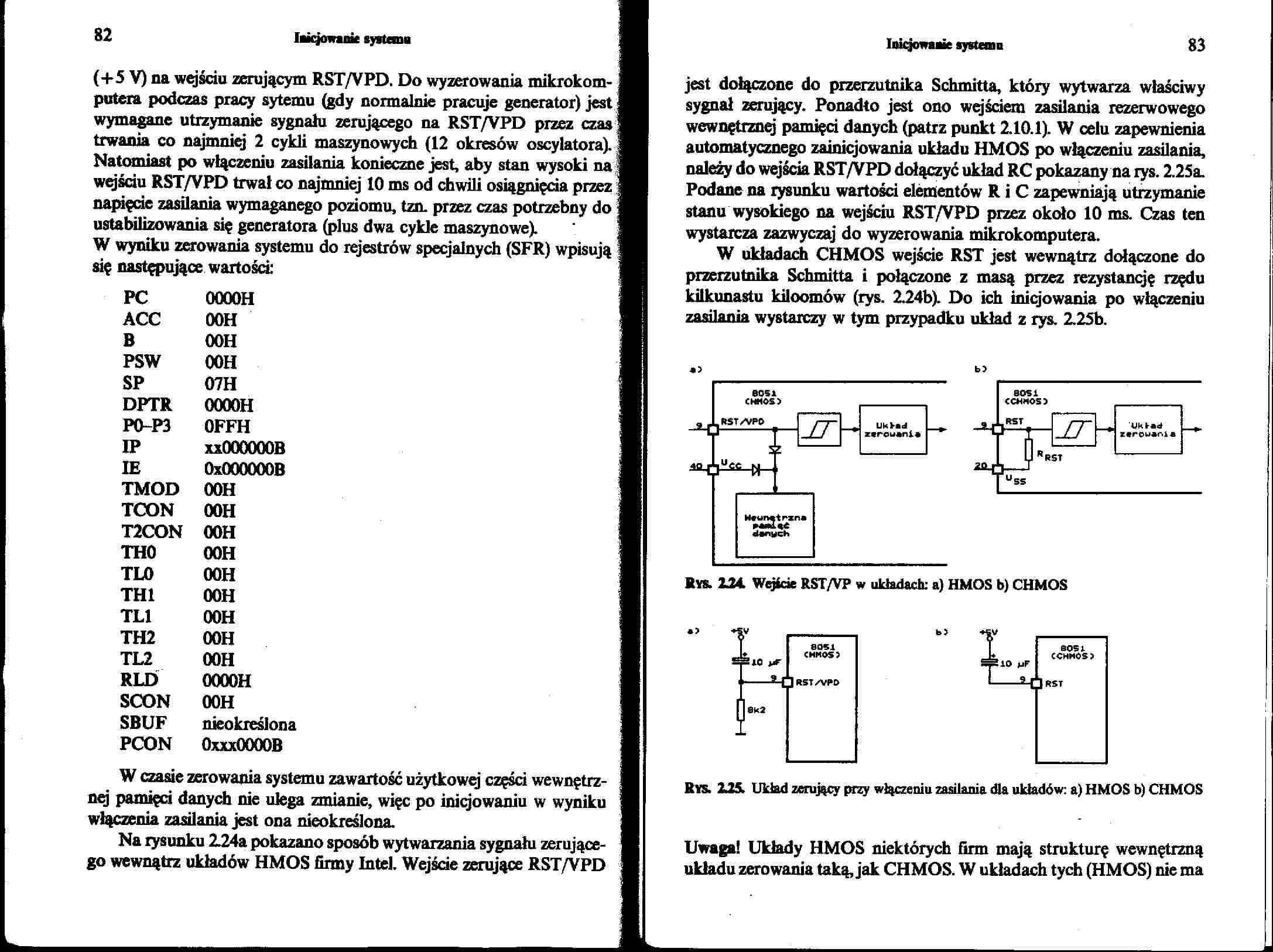

Na rysunku Z24a pokazano sposób wytwarzania sygnału zerującego wewnątrz układów HMOS firmy Intel. Wejście zerujące RST/YPD

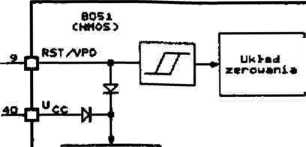

jest dołączone do przerzutnika Schmitta, który wytwarza właściwy sygnał zerujący. Ponadto jest ono wejściem zasilania rezerwowego wewnętrzną pamięci danych (patrz punkt 110.1). W celu zapewnienia automatycznego zainicjowania układu HMOS po włączeniu nasila niai należy do wejścia RST/VPD dołączyć układ RC pokazany na rys. 2.25a. Podane na rysunku wartości elementów R i C zapewniają utrzymanie stanu wysokiego na wejściu RST/VPD przez około 10 ms. Czas ten wystarcza zazwyczaj do wyzerowania mikrokomputera.

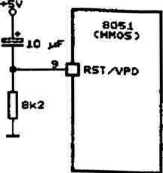

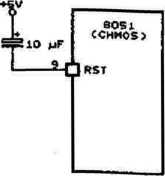

W układach CHMOS wejście RST jest wewnątrz dołączone do przerzutnika Schmitta i połączone z masą przez rezystancję rzędu kilkunastu kiloomów (rys. 124b)- Do ich inicjowania po włączeniu zasilania wystarczy w tym przypadku układ z rys. 125b.

«>

M«un«trzna

danweh

to

Rys. 124 Wejście RST/YP w układach: a) HMOS b) CHMOS

Rys. 215. Układ zerujący przy włączeniu zasilania dla układów: a) HMOS b) CHMOS

Uwaga! Układy HMOS niektórych firm mają strukturę wewnętrzną układu zerowania taką, jak CHMOS. W układach tych (HMOS) nie ma

Wyszukiwarka

Podobne podstrony:

page0092 82 Posadźmy magnetyzowanego na krześle i umocujmy mu ręce do krzesła, przyciśnięciem naszem

Czas, na który napięcie wzorcowe zostaje załączone na wejście integratora, jest proporcjonalny do wa

str16 (41) a 174 a. Cotte d armes przeszywana na wacie, zdobienie heraldyczne, należała do ks. Walii

Stan czytelnictwa w Polsce i na świecie. Metody, techniki i źródła do badań czytelniczych. Formy pra

IMAG0456 (2) Zadanie 8 Na wejście integratora w woltomierzu cyfrowym o podwójnym całkowaniu podano n

Image067 — na wejścia informacyjne podaje się, stosownie do tablicy stanów przerzu

Image113 G(s) - 1 G(s) Przeniesienie węzła sumacyjnego z wyjścia na wejście

Image115 r W układach praktycznych należy dążyć do tego, aby stan 1 na wejściu synchronizującym trwa

Image117 Załóżmy, że na wejście D podany jest stan 1 i wejście taktujące jest w stanie 0. W takim pr

Image118 lenia informacji na wejściu D (ts) przed zmianą stanu wejścia taktującego z 0 na 1 wynika z

Image162 Informacja zostaje wpisana pod wskazanym adresem w momencie zmiany stanu z 0 na 1 na wejści

Image249 — wejściem zerującym Zer, — wejściem sterującym wpisywa

Image317 Jeżeli liczba B nie zmienia się w trakcie podawania k impulsów na wejście taktujące, wówcza

Image319 W przypadku realizacji operacji odejmowania, na wejścia selekcjonujące powinny być podane s

Image321 układ, na wejścia którego są podawane jednocześnie wszystkie bity porównywanych liczb, podc

więcej podobnych podstron