DSCN5397 (3)

Pamięć podręczna - cache

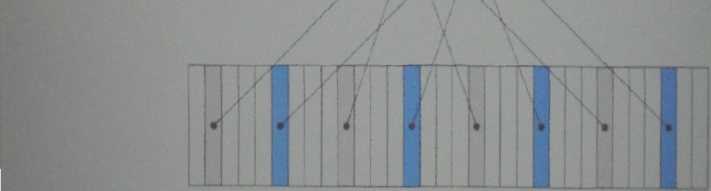

odwzorowanie bezpośrednie, direct mapped: a^res bloku cache I

młodsze bity adr. RAM

adres_bloku_RAM moduł o lic2ba_błoków__w__cache /

cache (oprócz danych) zawiera również tag - starszą część adresu RAM i vałid bit - info o aktualności danych

00001 00101 01001 01101 10001 10101 11001 11101

Memory

odwzorowanie 32 komórek pamięci RAM w 8 komórek pamięci cache

Wyszukiwarka

Podobne podstrony:

DSCN5393 (2) Pamięć podręczna - cache Organizacja: • bloki - linie pamięci (cache

DSCN5394 (3) Pamięć podręczna - cache Zasada działania: • CPU zgłasza chęć dostępu

DSCN5398 (2) Pamięć podręczna - cache przykład 256 bloków, w każdym 16 słów 32 bitowych Addrass {sho

DSCN5396 (2) Pamięć podręczna - cacheróżne metody odwzorowanie adresów bloków pamięci operacyjnej w

5.1.3 Pamięci podręczne Sposób odwzorowania adresów pamięci wyższego poziomu na adresy pamięci

Organizacja pamięci podręcznej Cache zorganizowana w Cache Lines o rozmiarach 16 lub 32 bajty (najmn

Pamięć podręczna Cache to podręczna pamięć procesora. Charakteryzuje się wyjątkowo krótkim czasem

DSCN5400 (3) Pamięć podręczna - cache spójność danych cache <-> RAM - różne strategie zapisu •

DSCN5404 (2) Pamięć podręczna - cache różne strategie wymiany bloków w cache sekcyjnoskojarzenicwych

DSCN5405 (3) Przykład: odczyt pamięci kolejno z adresów: 0,8.0,6.8 4 blokowy cache direct mapped A

74650 Slajd24 (113) Pamięć podręczna CPU M-► Cache «-► RAM CPU -T— RAM ► Cache

PAGE82 adres z CPU Organizacja dwukierunkowej pamięci podręcznej ze zbiorowym odwzorowaniem asocjacy

DSCN5411 Wielopoziomowa pamięć podręczna (muftilevel cache) L1 - mała (np. 2*32kB). małe bloki, prio

więcej podobnych podstron