DSCN5411

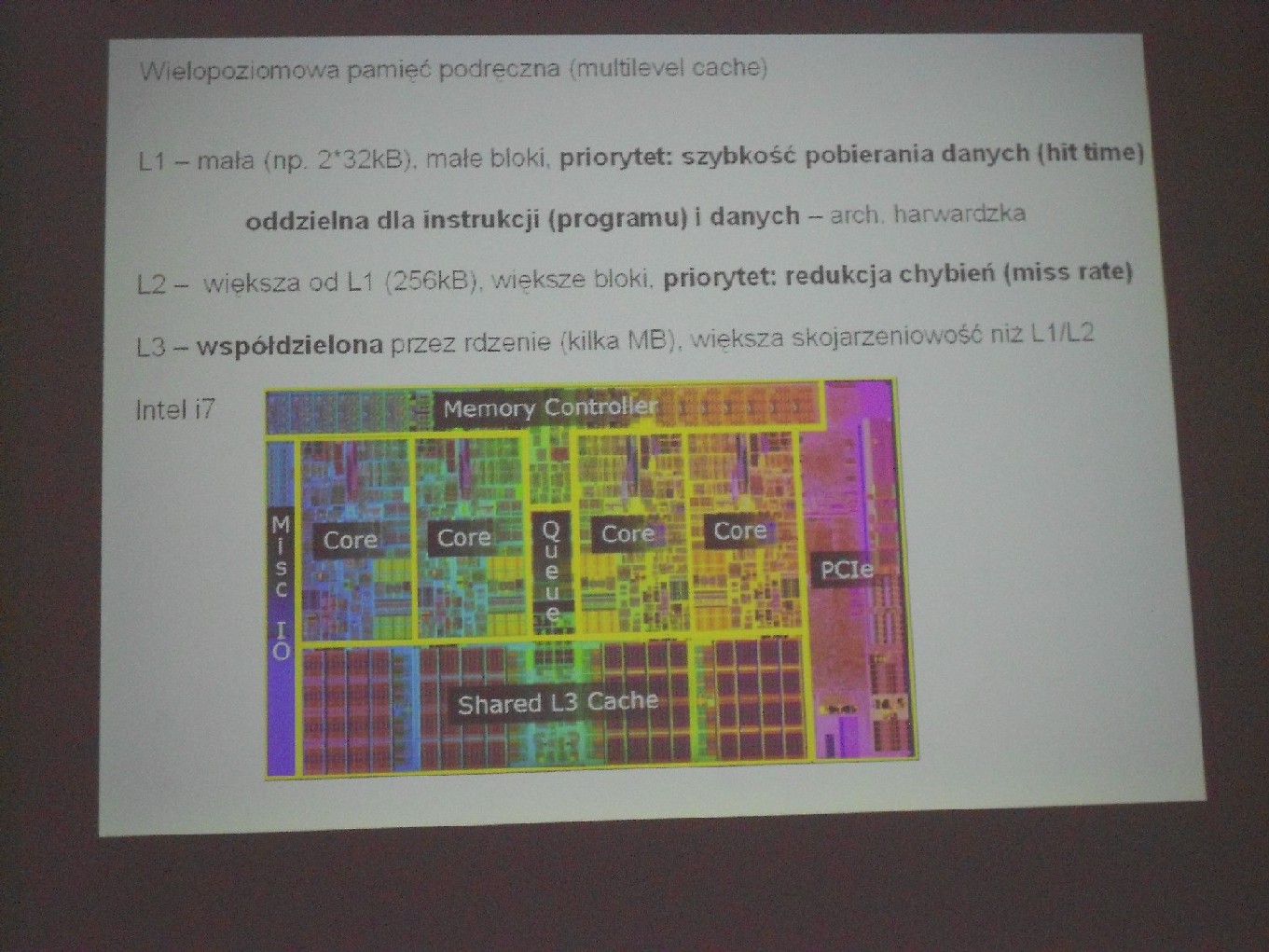

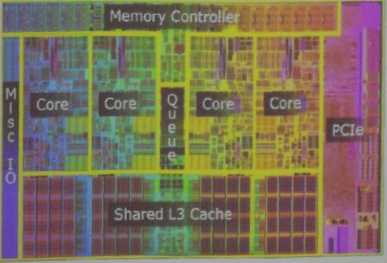

Wielopoziomowa pamięć podręczna (muftilevel cache)

L1 - mała (np. 2*32kB). małe bloki, priorytet: szybkość pobierania danych (hittime) oddzielna dla instrukcji (programu) i danych - arch. harwardzka L2 - większa od L1 (256kB), większe bloki, priorytet: redukcja chybień (miss ratę) L3 - współdzielona przez rdzenie (kilka MB), większa skojarzeniowość niz L1/L2

Wyszukiwarka

Podobne podstrony:

74650 Slajd24 (113) Pamięć podręczna CPU M-► Cache «-► RAM CPU -T— RAM ► Cache

DSCN5400 (3) Pamięć podręczna - cache spójność danych cache <-> RAM - różne strategie zapisu •

DSCN5404 (2) Pamięć podręczna - cache różne strategie wymiany bloków w cache sekcyjnoskojarzenicwych

41 P wieloportowa X Pamięć widoportowa (widościc/kowa) (Multi-Way Association CACHE) na przykładzi

cz3 str4 SyMeniy wieloprocesorowe z podziałem czasu Wiele jednostek centralnych z pamięcią podręczną

Organizacja pamięci podręcznej Cache zorganizowana w Cache Lines o rozmiarach 16 lub 32 bajty (najmn

Rys 1-3 Wieloprocesor z magistralą i pamięciami podręcznymi Złagodzenie problemu - zastosowanie pami

22 (477) Systemy wieloprocesorowe i. podziałem czosil Wiele jednostek centralnych z pamięcią podręcz

Pamięć podręczna Cache to podręczna pamięć procesora. Charakteryzuje się wyjątkowo krótkim czasem

DSCN5393 (2) Pamięć podręczna - cache Organizacja: • bloki - linie pamięci (cache

DSCN5394 (3) Pamięć podręczna - cache Zasada działania: • CPU zgłasza chęć dostępu

DSCN5397 (3) Pamięć podręczna - cache odwzorowanie bezpośrednie, direct mapped: a^

DSCN5398 (2) Pamięć podręczna - cache przykład 256 bloków, w każdym 16 słów 32 bitowych Addrass {sho

DSCN5401 (2) Pamięć podręczna - cacneodwzorowanie dynamiczne - skojarzeniowe (associative) 12mod8 =

DSCN5402 (2) Pamięć podręczna złożona z 8 bloków (linii) - w różnych konfiguracjach One-way set asso

więcej podobnych podstron