DSCN5401 (2)

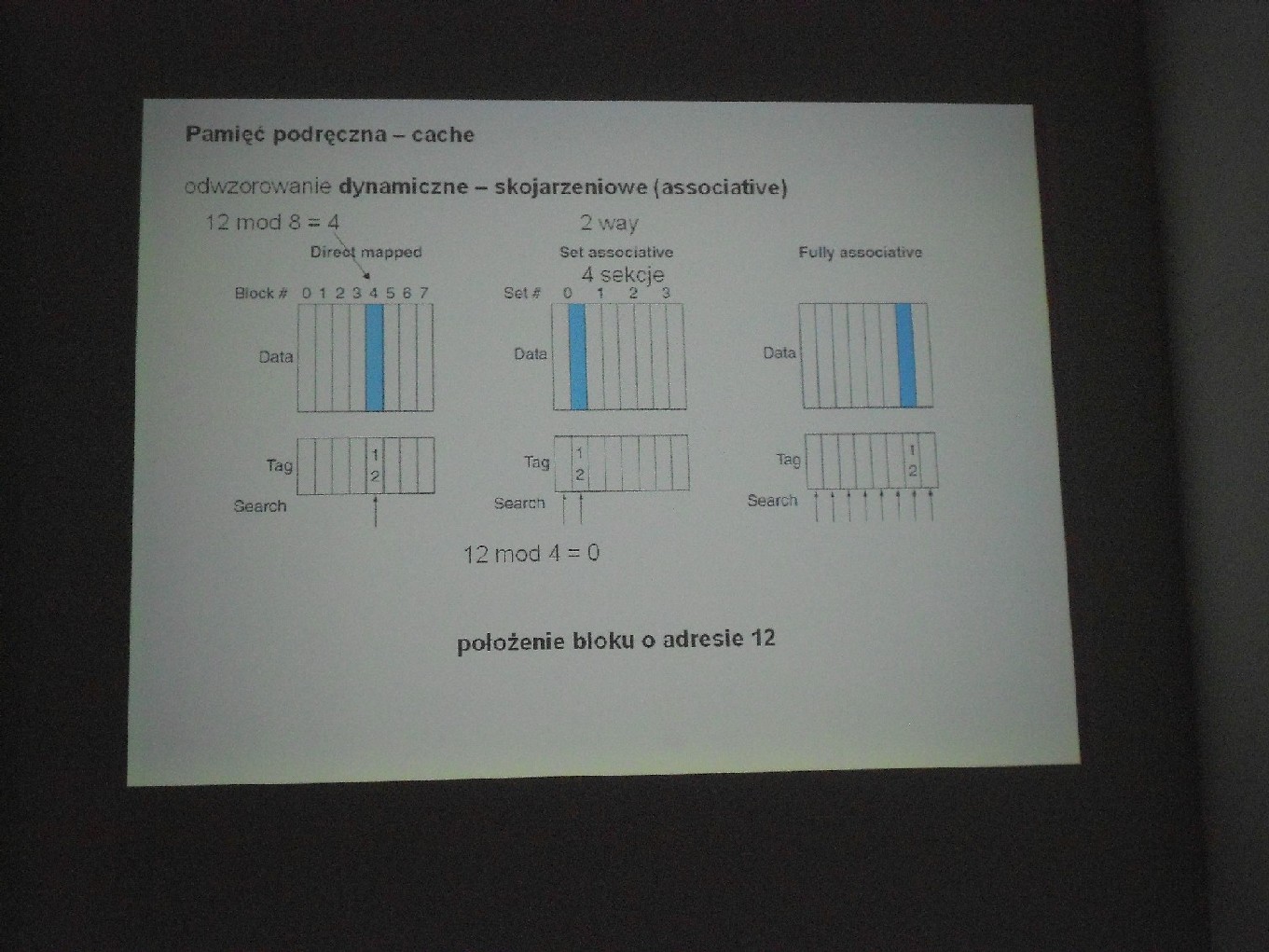

Pamięć podręczna - cacne

odwzorowanie dynamiczne - skojarzeniowe (associative)

2way

Set associative

4 sekcje

Set# 0 12 3

Tag

Search

Tag

Searcti f |

12mod4 = 0

Fuily associatńre

Data

Tag

Search

położenie bloku o adresie 12

Wyszukiwarka

Podobne podstrony:

DSCN5400 (3) Pamięć podręczna - cache spójność danych cache <-> RAM - różne strategie zapisu •

DSCN5402 (2) Pamięć podręczna złożona z 8 bloków (linii) - w różnych konfiguracjach One-way set asso

DSCN5404 (2) Pamięć podręczna - cache różne strategie wymiany bloków w cache sekcyjnoskojarzenicwych

DSCN5411 Wielopoziomowa pamięć podręczna (muftilevel cache) L1 - mała (np. 2*32kB). małe bloki, prio

Slajd18 (110) Sposób dostępu do pamięci Sekwencyjny Bezpośredni Swobodny Skojarzeniowy

Slajd16 Pamięć podręczna ARP Protokół ARP przechowuje tabelę zawierającą adresy 1P i odpowiadające i

cz3 str4 SyMeniy wieloprocesorowe z podziałem czasu Wiele jednostek centralnych z pamięcią podręczną

W języku „C” do dynamicznego przydzielania pamięci (tworzenia zmiennych dynamicznych) służyły

Slajd13 Magistrala lokalna PCIProcesor Pamięć podręczna ► Pamięć

Rysunek 1.4: Procesor wielordzeniowy - widoczne rdzenie, układy pamięci podręcznej oraz inne element

7 (206) 58. Wymień sposoby zapisu pamięci podręcznej : 1. Write

więcej podobnych podstron