8482348975

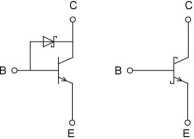

T2 jest zatkany , zatkany jest również T3. W tym przypadku T4 przewodzi i daje poziom “H na wyjściu. Tranzystor T4 pracujący jako wtórnik emiterowy może teraz dostarczać dużego prądu wyjściowego i dzięki temu szybko ładować pojemności obciążenia. Standardowe układy TTL tego rodzaju , jak pokazane na rysunku 3.1, są obecnie spotykane rzadko z powodu dużego czasu propagacji wywołanego nasyceniem tranzystorów. Nasyceniu można zapobiec przez dołączenie diody Schottky’ego równolegle do złącza kolektor-baza (rysunek 3.2). dzięki napięciowemu sprzężeniu zwrotnemu przy przewodzeniu tranzystora uniemożliwia ona spadek napięcia kolektor-emiter poniżej wartości ok. 0,3V.

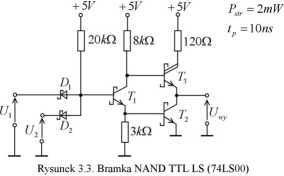

Rysunek 3.2.Tranzy stor z diodą Schottky'ego przeciwdziałającą nasyceniu i jego symbol graficzny Bramka TTL zbudowana z takich “tranzystorów Schottky'ego" (bramka TTL-S) jest przedstawiona na rys. 3.3. Jest to uproszczony schemat bramki TTL-S małej mocy, tzw. bramki TTL-LS (Iow power Schottky). Z porównania ze standardową bramką TTL z rys. 3.1 widać, że ma ona rezystancje kolektorowe pięć razy większe, dzięki czemu pobór mocy jest pięć razy mniejszy i wynosi tylko 2 mW. Mimo to czas propagacji bramki nie jest większy i wynosi 10 ns. Wejściowy zespół diod jest zbudowany tak, jak w układzie DTL, z oddzielnych diod. Dioda D (rys. 3.1) w stopniu wyjściowym, służąca do przesunięcia potencjału, została tu zastąpiona układem Darlingtona T3.

Charakterystykę przejściową inwertera TTL-S małej mocy przedstawiono na rys. 3.4. Nietrudno zauważyć, że poziom przełączania wynosi ok. 1,1 V. Charakterystyczne dla układów TTL tolerancje są tu zachowane z dużym zapasem. Przy najwyższym dopuszczalnym poziomie L na wejściu, równym 0,8 V, na wyjściu musi być poziom H wynoszący co najmniej 2,4 V. Przy najniższym poziomie H na wejściu, równym 2,0 V, poziom L na wyjściu może wynosić najwyżej 0,4 V.

14

Wyszukiwarka

Podobne podstrony:

Istotnym elementem w wyborze odpowiedniej kamery jest jej obudowa. W tym przypadku decydującą rolę o

Wnioski: Wygląd spirali zależny jest od kąta. W tym przypadku jest to kąt prosty (900) Aby uzyskać s

siecia . MAi.NA SZYBKOŚĆ REGUŁACH — Jest to największa zmiana poziomu sygnału na wyjściu regulatora

(zmęczenie) pacjenta. W tym przypadku nie przeprowadza się dekompozycji sygnału na poszczególne skła

img018 18 i skalę lokalną* S tym przypadku elementy kątowe, długościowa 1 powierzchniowa narysowano

49 (193) 96 W tym -przypadku, wyznaczmy najpierw ślad poziomy pionowy Vb prostej b, a metę pnie za p

87735 z15 (9) y Zauważmy, iż w tym przypadku (rama trójprzegubowa o podporach leżądy(ffl na różnych

IMG&96 Postać produktu W tym rozumieniu: usługa hotelarska jest również produktem - czyli służy zasp

więcej podobnych podstron