Laboratorium Elektroniki i Miernictwa Instytutu Fizyki PŁ

1

wiczenie EL2

Realizacja logicznych układów kombinacyjnych z bramek NAND

Przed zapoznaniem si z instrukcj i przyst pieniem do wykonywania wiczenia nale y opanowa

nast puj cy materiał teoretyczny:

1.

Czym zajmuje si algebra Boole’a i jakie s jej podstawowe prawa i to samo ci? [1-8]

2.

Minimalizacja funkcji logicznej przy u yciu tablicy Karnaugha. [1-8]

3.

Symbole graficzne funktorów realizuj cych podstawowe funkcje logiczne AND, OR, NOT, NAND, NOR,

EX-OR i EX-NOR. [1-3,5-8].

4.

Realizacja pozostałych funktorów logicznych przy u yciu samych funktorów NAND albo NOR. [1-4,8]

5.

Podział układów przeł czaj cych na układy kombinacyjne i sekwencyjne. [1,3,5-8]

Cel wiczenia

Celem wiczenia jest:

1. Zapoznanie si z funktorami realizuj cymi podstawowe funkcje logiczne.

2. Zaprojektowanie, wykonanie i przetestowanie kombinacyjnego układu logicznego realizuj cego postawione

zadanie w mo liwie najprostszy sposób.

Wst p teoretyczny

Technika cyfrowa posługuje si głównie algebr Boole’a okre lon dla zmiennych przyjmuj cych warto ci

ze zbioru dwóch elementów {0; 1}. Spotyka si równie układy dopuszczaj ce trzy stany, jednak e nie b d one

przedmiotem tego wiczenia. Na zmiennych dwustanowych definiuje si nast puj ce działania:

– iloczyn logiczny nazywany funkcj AND:

B

A

Y

⋅

=

,

– sum logiczn OR:

B

A

Y

+

=

,

– negacj argumentu NOT:

A

Y

= .

W praktyce wygodnie jest wprowadzi równie funkcje realizuj ce zło enie funkcji AND z NOT oraz OR z NOT

– negacja iloczynu NAND:

B

A

Y

⋅

=

,

– negacja sumy NOR:

B

A

Y

+

=

.

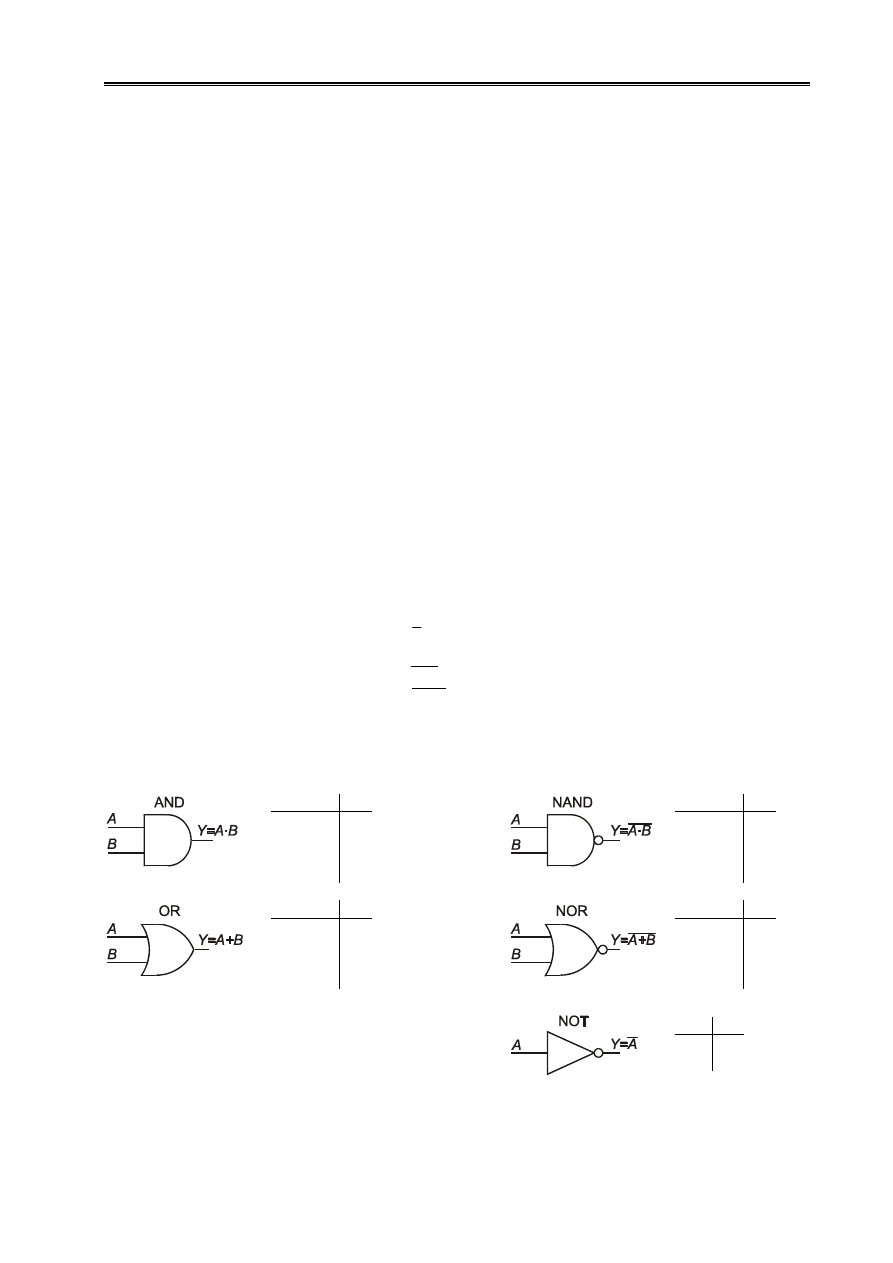

Symbole układów elektrycznych (zwanych dalej bramkami) realizuj cych wymienione powy ej funkcje zestawiono

na Rys. 1. Definicje funkcji AND, OR, NAND i NOR mo na łatwo rozszerzy na dowoln liczb argumentów

przez zło enie ich z funkcji dwuargumentowych, np.

A

·

B

·

C

= (

A

·

B

)·

C

.

A

B

Y

0

0

0

0

1

0

1

0

0

1

1

1

A

B

Y

0

0

0

0

1

1

1

0

1

1

1

1

A

B

Y

0

0

1

0

1

1

1

0

1

1

1

0

A

B

Y

0

0

1

0

1

0

1

0

0

1

1

0

A

Y

0

1

1

0

Rys. 1. Symbole podstawowych bramek logicznych i ich tablice stanów.

Laboratorium Elektroniki i Miernictwa Instytutu Fizyki PŁ

2

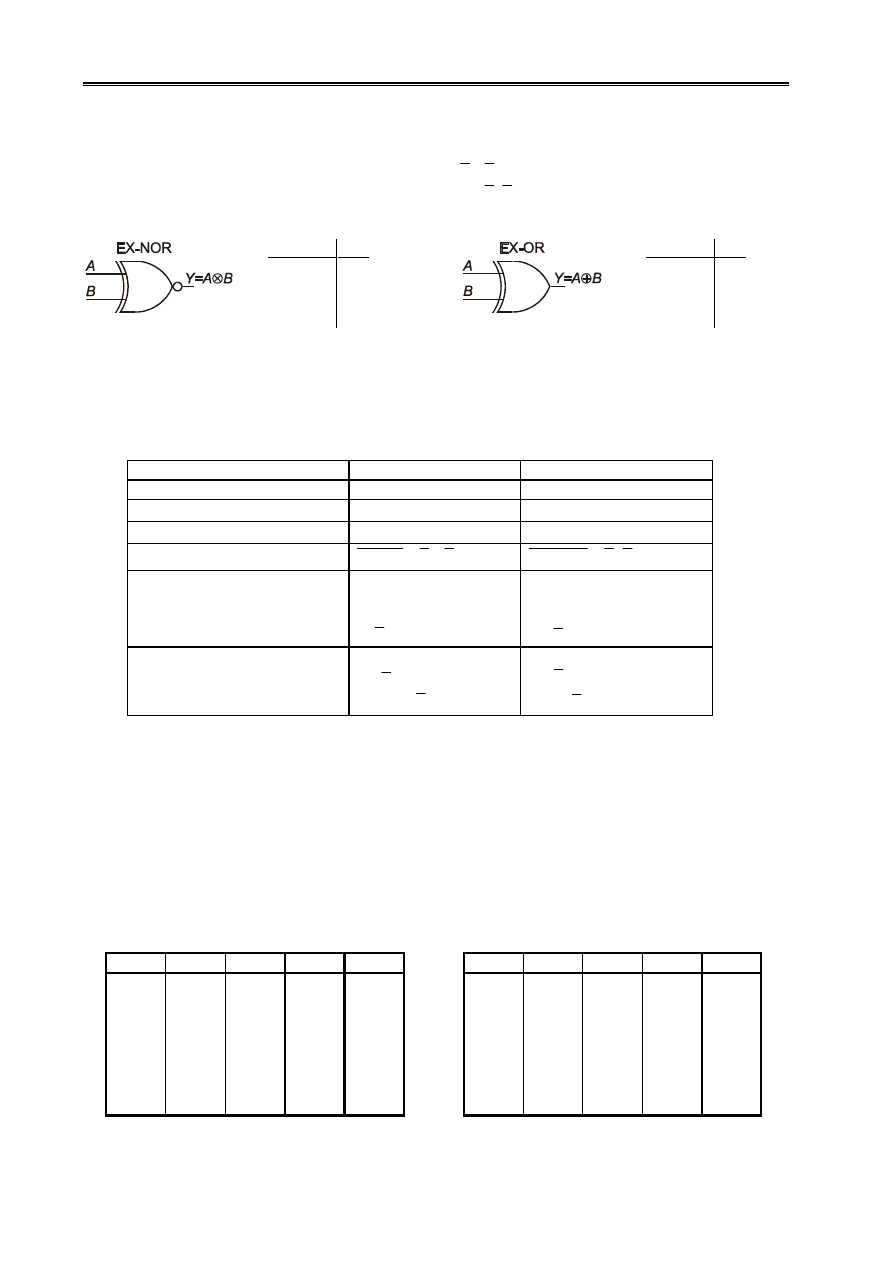

Ze wzgl du na du e znaczenie praktyczne definiuje si równie funkcj nierównowa no ci EX-OR (skrót od

EXCLUSIVE-OR) odpowiadaj c polskiemu operatorowi ALBO, czyli WYŁ CZNE LUB, a tak e funkcj

równowa no ci EX-NOR (pol. ALBO-NIE) okre lon jako zło enie EX-OR i NOT

– nierównowa no EX-OR:

B

A

B

A

B

A

Y

⋅

+

⋅

=

⊕

=

,

– równowa no EX-NOR:

B

A

B

A

B

A

Y

⋅

+

⋅

=

⊗

=

.

A

B

Y

0

0

1

0

1

0

1

0

0

1

1

1

A

B

Y

0

0

0

0

1

1

1

0

1

1

1

0

Rys. 2. Symbole dodatkowych bramek logicznych i ich tablice stanów.

Podczas projektowania układów logicznych najwi ksze znaczenie maj nast puj ce prawa algebry Boole’a:

przemienno ci, ł czno ci, rozdzielno ci i De Morgana. Zauwa my, e prawo rozdzielno ci sumy wzgl dem

iloczynu oraz obydwa prawa De Morgana nie maj swoich odpowiedników w algebrze liczb rzeczywistych.

Nazwa przekształcenia

Dla iloczynu logicznego

Dla sumy logicznej

Prawa przemienno ci

A

B

B

A

⋅

=

⋅

A

B

B

A

+

=

+

Prawa ł czno ci

C

B

A

C

B

A

⋅

⋅

=

⋅

⋅

)

(

)

(

C

B

A

C

B

A

+

+

=

+

+

)

(

)

(

Prawa rozdzielno ci

C

A

B

A

C

B

A

⋅

+

⋅

=

+

⋅

)

(

)

(

)

(

C

A

B

A

C

B

A

+

⋅

+

=

⋅

+

Prawa De Morgana

+

+

=

⋅

⋅

B

A

B

A

⋅

⋅

=

+

+

B

A

B

A

To samo ci podstawowe

0

0

=

⋅

A

A

A

=

⋅1

A

A

A

=

⋅

0

=

⋅ A

A

1

1

=

+

A

A

A

=

+ 0

A

A

A

=

+

1

=

+ A

A

To samo ci dodatkowe

A

B)

(A

A

=

+

⋅

B

A

B

A

A

+

=

⋅

+

B

B

A

B

A

=

+

⋅

+

)

(

)

(

A

B

A

A

=

⋅

+

B

A

B)

A

(

A

⋅

=

+

⋅

B

B

A

B

A

=

⋅

+

⋅

Tabela 1.

Podstawowe prawa i to samo ci algebry Boole’a.

Posługuj c si prawami De Morgana mo na stwierdzi , e spo ród funktorów realizuj cych podstawowe działania

logiczne jedynie funktory NAND i NOR s uniwersalne, tzn. ł cz c funktory tylko jednego z tych dwóch typów

mo na zrealizowa dowoln funkcj logiczn , w tym tak e pozostałe funkcje elementarne AND, OR, NOT, NAND,

NOR, EX-OR i EX-NOR. Ograniczenie zbioru funktorów stosowanych do realizacji dowolnej funkcji logicznej ma

wiele zalet i jest cz sto stosowane w praktyce.

Metoda minimalizacji i syntezy układu kombinacyjnego

Załó my, e w wyniku analizy tre ci zadania ustalono nast puj c tablic stanów układu o czterech

wej ciach A, B, C, D i jednym wyj ciu W.

A

B

C

D

W

A

B

C

D

W

0

0

0

0

1

1

0

0

0

0

0

0

0

1

0

1

0

0

1

0

0

0

1

0

0

1

0

1

0

1

0

0

1

1

0

1

0

1

1

1

0

1

0

0

1

1

1

0

0

0

0

1

0

1

0

1

1

0

1

0

0

1

1

0

1

1

1

1

0

1

0

1

1

1

–

1

1

1

1

–

Tabela 2.

Zapis funkcji logicznej w postaci tablicy prawdy. Kreskami (–) oznaczono przypadki, w których

stan logiczny wyj cia nie ma znaczenia.

Laboratorium Elektroniki i Miernictwa Instytutu Fizyki PŁ

3

Bezpo rednio na podstawie tablicy stanów funkcj mo na przedstawi np. w postaci kanonicznej sumy, czyli

sumy składników, z których ka dy stanowi iloczyn pełny wszystkich zmiennych wej ciowych lub ich negacji

i odpowiada innej linii w tabeli prawdy, dla której W = 1

D

C

B

A

D

C

B

A

D

C

B

A

D

C

B

A

D

C

B

A

D

C

B

A

W

+

+

+

+

+

=

.

(1)

Uproszczenie powy szej funkcji W = f(A, B, C, D) przy wykorzystaniu zasad algebry Boole’a jest zadaniem

mudnym a prostota ko cowej postaci zale y od intuicji i szcz cia projektanta. Znacznie efektywniejsza metoda

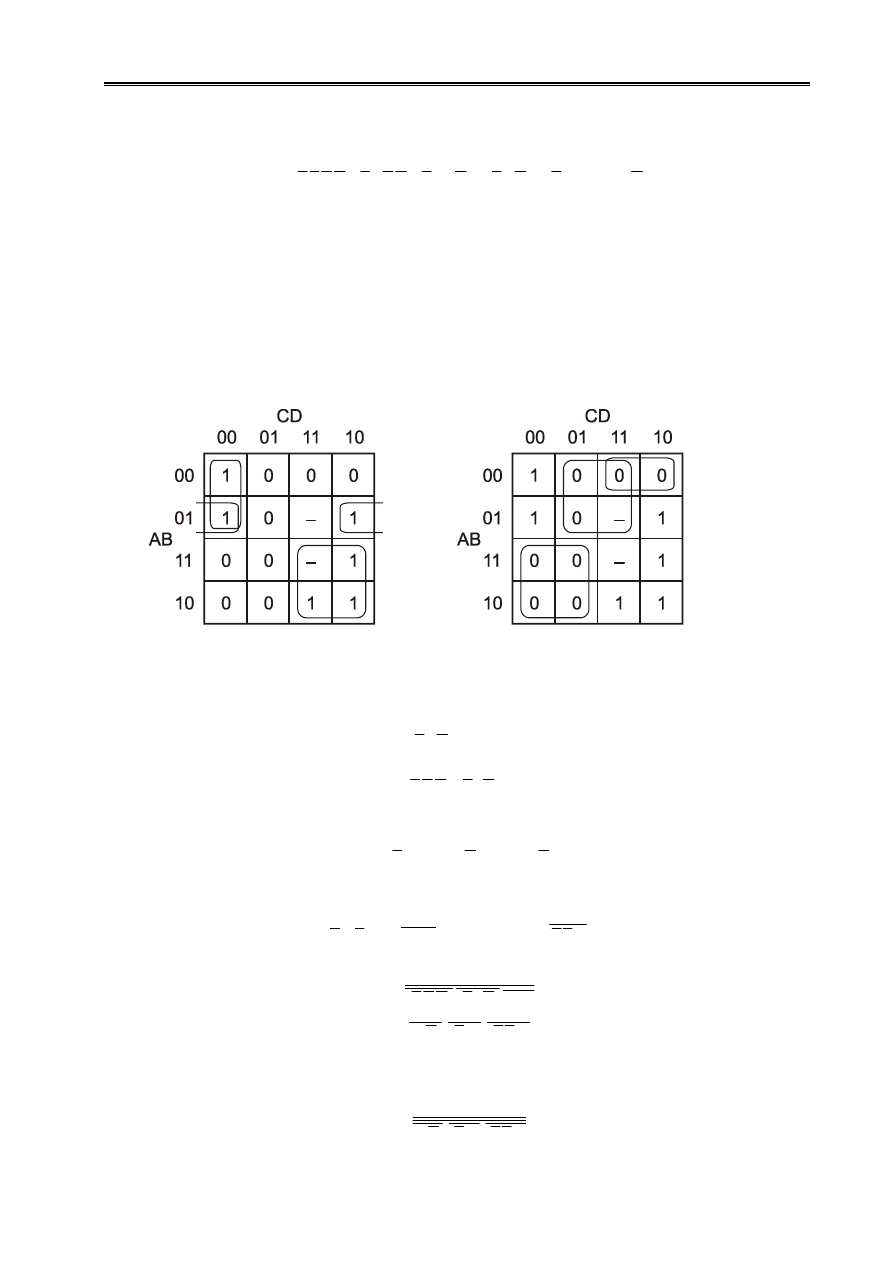

wykorzystuje zdolno ludzi do rozpoznawania geometrycznych wzorów w tablicy Karnaugha (Rys. 3), która jest

dwuwymiarow specyficznie uło on tablic stanów wyj ciowych. Stany wej ciowe podane s na zewn trz tablicy

i uporz dkowane zgodnie z kodem Graya, w którym dwa kolejne słowa ró ni si dokładnie jednym bitem.

W przypadku funkcji trzech zmiennych buduje si tablic o wymiarach 2

×

4, za dla dwóch zmiennych tablic

2

×

2. Minimalizacja funkcji sprowadza si do zgrupowaniu s siednich jedynek w prostok tne obszary (Rys. 3.a),

przy czym liczba pól w danych obszarze musi by pot g liczby 2. Przeciwległe kraw dzie tablicy traktuje si przy

tym jak sklejone ze sob . Aby otrzyma najprostsze rozwi zanie nale y zakre li wszystkie jedynki wybieraj c

mo liwie najmniejsz liczb obszarów o maksymalnie du ych rozmiarach. Alternatywnie mo na ł czy same zera

(Rys. 3.b). Wybrane pola zawieraj ce stan nieokre lony (–) mo na ł czy zarówno z jedynkami, jak i zerami.

a)

b)

Rys. 3.

Zapis funkcji logicznej danej Tabel 2 w postaci tablicy Karnaugha.

a)

minimalizacja funkcji przez

ł czenie jedynek,

b)

minimalizacja funkcji przez ł czenie zer.

Na podstawie tablicy na Rys. 3.a zminimalizowan funkcj logiczn tworzymy jako sum iloczynów, przy czym

ka dy iloczyn musi przyjmowa warto 1 dla wszystkich pół w danej grupie. Przykładowo, obszar zakre lony

poprzez kraw dzie tablicy odpowiada iloczynowi

D

B

A

, gdzie pomini te C nie zachowuje jednego stanu na całym

obszarze. Dla wszystkich grup otrzymujemy

AC

D

B

A

D

C

A

W

+

+

=

.

(2)

W przypadku, gdy na tablicy Karnaugha poł czono pola o stanach 0 (Rys. 3.b), funkcj logiczn tworzymy jako

iloczyn sum, z których ka da przyjmuje warto 0 w jednym zakre lonym obszarze

)

)(

(

)

(

C

B

A

D

A

C

A

W

+

+

+

+

=

.

(3)

Załó my, e funkcj trzeba zrealizowa przy u yciu samych funktorów NOT i NAND. Funkcj sumy

logicznej, wyst puj c we wzorach (2) i (3), przekształcamy zgodnie z prawami De Morgana

XY

Y

X

=

+

+

,

Y

X

Y

X

=

+

+

(4)

otrzymuj c ze wzorów (2) i (3) odpowiednio

)

(

)

(

)

(

AC

D

B

A

D

C

A

W

=

,

(5)

)

(

)

(

)

(

C

B

A

D

A

C

A

W

=

.

(6)

Wszystkie działania wyst puj c we wzorze (5) mo na zrealizowa bezpo rednio przy u yciu zało onych

funktorów. We wzorze (6) najbardziej zewn trzn funkcj iloczynu logicznego (AND) trzeba przedstawi jako

zło enie negacji (NOT) i zanegowanego iloczynu (NAND)

( ) ( ) (

)

C

B

A

D

A

C

A

W

=

.

(7)

Laboratorium Elektroniki i Miernictwa Instytutu Fizyki PŁ

4

Przebieg pomiaru

Pierwszym krokiem powinno by opisanie układu kombinacyjnego poprzez tablic prawdy oraz

zminimalizowan funkcj logiczn . Nast pnie mo na przyst pi do poł czenia zaprojektowanego układu i

testowania na stanowisku wyposa onym w nast puj ce moduły:

a) moduł zadawania stanów logicznych,

b) moduł zawieraj cy tablic bramek logicznych,

c) moduł testera stanów logicznych.

Odpowied na wyj ciach układu bada si testerem stanów kolejno dla wszystkich kombinacji stanów

zadawanych na wej ciach. Wyznaczon do wiadczalnie tablic stanów porównuje si z tablic teoretyczn .

Moduł zadawania stanów logicznych składa si z pi ciu przeł czników umo liwiaj cych wybór stanu

logicznego 0 albo 1 w gniazdach umieszczonych pod przeł cznikami. W przypadku gdy konieczne jest niezale ne

zadawanie stanów na wi cej ni pi ciu wej ciach układu kombinacyjnego, najrzadziej przeł czane wej cia nale y

podł czy do gniazd o ustalonym stanie 0 albo 1 umieszczonych w dolnej cz ci urz dzenia. Ponadto moduł

zawiera trzy generatory pojedynczego impulsu wykorzystywane tylko podczas badania układów sekwencyjnych,

które wykraczaj poza zakres wiczenia przewidzianego w niniejszej instrukcji.

Moduł bramek logicznych zawiera 4 bramki logiczne NOT, 8 dwuwej ciowych bramek NAND oraz 8

trzywej ciowych bramek NAND. Wszystkie pozostałe funkcje logiczne nale y realizowa przez poł czenia

dost pnych bramek NAND i NOT. Alternatywnie na stanowisku mo e znajdowa si zestaw bez bramek NOT

zło ony z 12 dwuwej ciowych bramek NAND oraz 8 trzywej ciowych bramek NAND.

Moduł testera stanów logicznych zawiera 10 niezale nych testerów. Ka dy tester zaopatrzony jest w jedno

wej cie pomiarowe oraz diody czerwon i zielon , których zapalenie symbolizuje stan logiczny odpowiednio 1 i 0.

Jednoczesne wiecenie diody czerwonej i zielonej oznacza wzbudzenie oscylacji w badanym układzie. Oscylacje

nie powinny wyst powa w poprawnie poł czonym układzie kombinacyjnym, zatem ich obecno wskazuje na bł d

w sieci poł cze . W przypadku gdy na wej ciu pomiarowym wyst puje stan wysokiej rezystancji lub

doprowadzone napi cie wzgl dem masy nie odpowiadaj ce adnemu stanowi logicznemu obie diody s zgaszone.

Wyst pienie takiego stanu przy wej ciu pomiarowym podł czonym do wyj cia bramki logicznej lub modułu

zadawania stanu wskazuje na brak kontaktu lub awari przyrz dów.

Kolejno czynno ci

A. Sprawdzenie prawa De Morgana

1. Wykorzystuj c zanegowane obustronnie prawo De Morgana dla sumy logicznej (Tabela 1) narysowa schemat

elektryczny układu realizuj cego funkcj bramki OR przy wykorzystaniu dost pnych bramek NAND i NOT.

2. Poł czy zaprojektowany układ, do wej układu doprowadzi sygnały z modułu zadawania stanów, za

wyj cie układu poł czy z próbnikiem stanów.

3. Poł czy z zasilaczem wszystkie moduły umieszczone na statywie. W tym celu w skrajnym prawym albo

lewym module poł czy przewodami lini masy (na dole modułu) i zasilania +5V (na górze) z wyj ciem

zasilacza. Zasilanie pozostałych modułów realizuje si poprzez poł czenie analogicznych linii w s siednich

modułach.

UWAGA:

a) wszystkie moduły powinny by zasilane z wyj cia zasilacza zapewniaj cego stałe napi cie +5V

(gniazda z prawej strony zasilacza). Nie u ywa wyj umo liwiaj cych płynn zmian napi cia,

b) nie wolno ł czy zasilania +5V do wyj bramek lub wyj zadajnika stanów logicznych.

Nieprzestrzeganie powy szych zalece grozi uszkodzeniem urz dze .

4. Po uzyskaniu zezwolenia wł czy zasilacz i sprawdzi czy wiec si czerwone diody umieszczone na linii

+5V. W module testera stanów logicznych wszystkie diody symbolizuj ce stan 0 lub 1 powinny by zgaszone

przy rozwartych wej ciach testerów.

5. Zadaj c ró ne kombinacje sygnałów wej ciowych sporz dzi tablic prawdy układu. Porówna tablic

otrzyman eksperymentalnie z tablic teoretyczn dla bramki OR umieszczon na Rys. 1. W przypadku

wyst pienia rozbie no ci sprawdzi ponownie układ. Je li próby usuni cia rozbie no ci nie powiod si

zawiadomi obsług pracowni.

Laboratorium Elektroniki i Miernictwa Instytutu Fizyki PŁ

5

B. Projektowanie i realizacja układu kombinacyjnego

1. W porozumieniu z prowadz cym zaj cia wybra zadania do realizacji. Przykładowe zadania zebrano w

nast pnym rozdziale.

2. Sporz dzi teoretyczn tablic prawdy (patrz przykład w Tabeli 2). Przypadki w których stan logiczny wyj cia

nie ma znaczenia oznaczy my lnikiem.

3. Podj prób minimalizacji funkcji logicznej posługuj c si tablic Karnaugha. Rozwa y przypadek ł czenia

jedynek (patrz przykład na Rys. 3.a) oraz przypadek ł czenia zer (Rys. 3.b).

4. Wykorzystuj c prawa algebry Boole’a przekształci zminimalizowan funkcj logiczn tak by wyrazi j

bezpo rednio przy u yciu funkcji logicznych realizowanych przez dost pn na stanowisku tablic bramek

logicznych (np. tablica zawieraj ca bramki NOT oraz dwu- i trzywej ciowe bramki NAND umo liwia

skorzystanie wył cznie z funkcji typu A ,

B

A

⋅ oraz

C

B

A

⋅

⋅

. W przypadku gdy rozwi zanie zadania wymaga

zbudowania układu kombinacyjnego o kilku wyj ciach porówna funkcje przeł czaj ce dla ka dego z wyj i

podj prób znalezienia wspólnych wyra e , które mo na wykorzysta do dalszego uproszczenia układu

przez u ycie tych samych bramek do realizacji wi cej ni jednej funkcji.

5. Wł czy zasilacz.

6. Poł czy układ kombinacyjny zgodnie z funkcjami zbudowanymi w punkcie 4. Nie zakłada , e

niepodł czone wej cia bramek posiadaj pewien ustalony stan logiczny. Najprostsz metod ustalenia stanu na

nadmiarowym wej ciu bramki jest poł czenie go zwork z s siednim u ywanym wej ciem. Alternatywnie

nadmiarowe wej cie mo na poł czy przewodem z modułem zadawania stanów logicznych. Zmiany w

układzie poł cze logicznych mog by bezpiecznie wykonywane przy wł czonym zasilaniu. Układy

elektroniczne s zabezpieczone przez przypadkowymi bł dnymi poł czeniami obejmuj cymi kilka wyj

bramek logicznych lub wyj modułu zadawania stanów logicznych.

7. Sporz dzi do wiadczaln tablic prawdy dla wszystkich wyj poł czonego układu.

8. Sprawdzi zgodno tablicy wykonanej w punkcie 7 z tablic z punktu 2. W przypadku stwierdzenia

rozbie no ci podj prób ich wyja nienia i usuni cia przez sprawdzenie luzów w poł czeniach realizowanych

przy u yciu przewodów i zworek, przeanalizowanie przekształce wykonanych w punktach 3 i 4 oraz

sprawdzenie poprawno ci poł cze wykonanych w punkcie 6. Po dokonaniu poprawek sporz dzi ponownie

tablic prawdy dla układu kombinacyjnego. Je li próby usuni cia rozbie no ci nie powiod si zawiadomi

obsług pracowni.

9. Wył czy zasilanie i narysowa schemat układu elektrycznego.

10. Rozł czy poł czenia.

Propozycje zada realizowanych przez układ kombinacyjny

Liczba gwiazdek w nawiasach opisuje stopie trudno ci zadania. Wybór najprostszych zada mo e uniemo liwi

otrzymanie maksymalnej oceny.

1.

(*) Zaprojektowa i poł czy układ sygnalizuj cy podzielno przez 3 liczby binarnej trzybitowej.

W rozwi zaniu zaznaczy czy liczb zero uznano za podzieln .

2.

(*) Zaprojektowa i poł czy układ realizuj cy funkcj czterowej ciowej bramki NOR przy u yciu bramek

NOT i NAND posiadaj cych co najwy ej trzy wej cia.

3.

(*) Zaprojektowa i poł czy układ, który na podstawie dwubitowej liczby binarnej steruje linijk zło on z

trzech diod wiec cych, w taki sposób, e liczba zał czonych kolejnych diod odpowiada warto ci liczby

binarnej na wej ciu układu.

4.

(**) Zaprojektowa i poł czy układ umo liwiaj cy wł czanie i wył czanie o wietlenia w du ym

pomieszczeniu z trzech ró nych miejsc, w których zamontowano pojedyncze wył czniki. Układ powinien

reagowa zmian stanu wyj ciowego na zmian stanu dowolnego pojedynczego wej cia, czyli powinien bada

parzysto bitów (ewentualnie nieparzysto ) trzybitowej liczby binarnej.

Wskazówka

: w prostszym przypadku

układu z dwoma wył cznikami zadanie realizuje pojedyncza bramka EX-OR lub EX-NOR przedstawiona na

Rys. 2.

5.

(**) Zaprojektowa i poł czy układ porównuj cy dwie liczby binarne dwubitowe

BA

oraz

DC

(gdzie

A

,

B

,

C

,

D

oznaczaj poszczególne bity). Układ powinien utrzymywa stan 1 na wyj ciu dla

DC

≥

BA

oraz stan 0 dla

DC

<

BA

.

6.

(**) Zaprojektowa i poł czy układ sygnalizuj cy stanem 1 na swoim wyj ciu awari termometru

kontaktowego wyposa onego w cztery kontakty

A

,

B

,

C

,

D

, które przy wzrastaj cej temperaturze powinny

zmienia swój stan z 0 na 1 w wymienionej kolejno ci. Za awari nale y uzna ka dy przypadek niekolejnego

zał czania kontaktów, tzn. sytuacj gdy poni ej zał czonego kontaktu pozostaje dowolny rozł czony kontakt.

Laboratorium Elektroniki i Miernictwa Instytutu Fizyki PŁ

6

7.

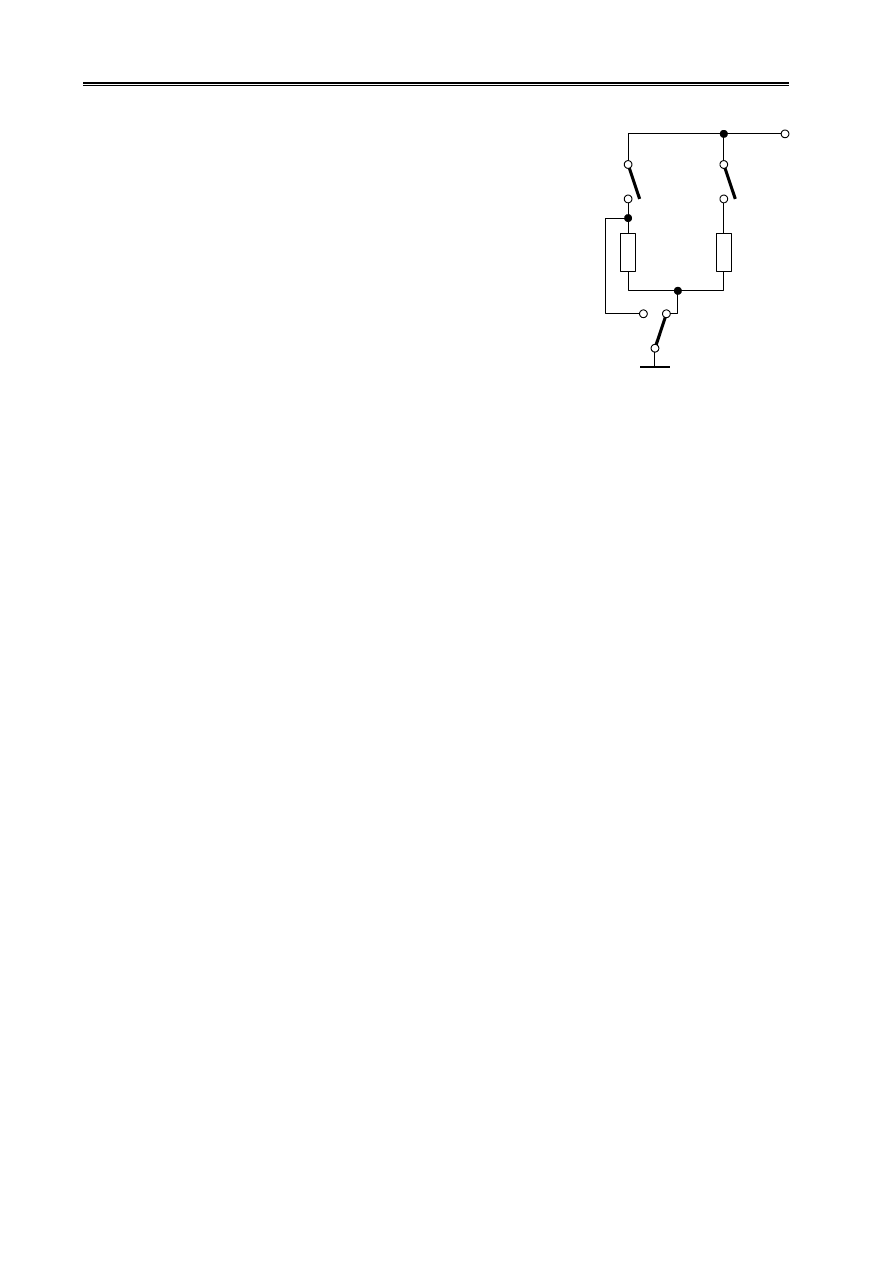

(***) Zaprojektowa i poł czy układ sterowania suszark zaopatrzon w dwa

grzejniki

G

1

i

G

2

o mocy odpowiednio 4 kW i 2 kW, które mo na sterowa

trzema wył cznikami

w

1

,

w

2

i

w

3

. Poło enia wył czników pokazane na

rysunku oznaczy symbolem 0, a poło enia przeciwne symbolem 1.

Temperatur w komorze suszarki mierzy termometr kontaktowy wytwarzaj cy

cztery sygnały

A

,

B

,

C

i

D

, które podczas wzrostu temperatury przechodz z 0

na 1 w wymienionej kolejno ci. Oznaczmy przez

t

i

temperatur , po osi gni ciu

której zmienia si sygnał na wyj ciu

i

-tego czujnika. Sposób działania układu

sterowania grzejnikami b dzie nast puj cy:

t

<

t

A

– oba grzejniki wł czone równolegle,

t

A

≤

t

<

t

B

– wł czony grzejnik

G

1

,

t

B

≤

t

<

t

C

– wł czony grzejnik

G

2

,

t

C

≤

t

<

t

D

– oba grzejniki wł czone szeregowo,

t

D

≤

t

– oba grzejniki wył czone.

8.

(***) Zaprojektowa i poł czy układ, który na podstawie czterobitowej liczby binarnej steruje linijk zło on

z czterech diod wiec cych. Dla warto ci binarnych od 0000 do 0100 (dziesi tnie od 0 do 4) układ powinien

zał cza kolejne diody w liczbie odpowiadaj cej warto ci na wej ciu układu, oraz utrzymywa wiecenie

wszystkich diod dla wszystkich warto ci wi kszych od 0100.

9.

(****) Zaprojektowa i poł czy układ jednego pełnego sumatora jednobitowego. Sumator oprócz wej

dodawanych bitów

A

i

i

B

i

powinien posiada wej cie

C

i-1

przyj cia przeniesienie z poprzedniego sumatora

dodaj cego bity na mniej znacz cej pozycji oraz generowa wynik sumowania

S

i

i przeniesienie

C

i

dla

sumatora dodaj cego cyfry na bardziej znacz cej pozycji.

Opracowanie sprawozdania

Sprawozdanie powinno zawiera :

1. Stron tytułow (wg wzoru).

2. Sformułowanie celu wiczenia.

3. Wyka u ytej aparatury. Dla modułu/modułów bramek logicznych poda tak e pełn specyfikacj dost pnego

zestawu bramek logicznych (typy bramek, liczba wej , liczba dost pnych bramek).

4. Opis przebiegu sprawdzenia prawa De Morgana.

5. Tre zadania, które powinien realizowa zbudowany układ kombinacyjny.

6. Teoretyczne tablice prawdy dla ka dego wyj cia wynikaj ce z analizy tre ci zadania.

7. Minimalizacj funkcji logicznej metod tablic Karnaugha.

8. Wynik przekształcenia zminimalizowanych funkcji logicznych do postaci mo liwej do bezpo redniego

zrealizowania przy u yciu dost pnych bramek.

9. Schemat poł cze elektrycznych układu kombinacyjnego.

10. Tablice stanu układu zbadane do wiadczalnie.

11. Dyskusj uzyskanych wyników. Przedstawi rezultat sprawdzenia zgodno ci zbudowanego układu

kombinacyjnego z teoretyczn tablic prawdy. W przypadku wyst pienia rozbie no ci opisa rodki podj te w

celu ich usuni cia, znalezione bł dy i uzyskany ostatecznie rezultat. Czy metoda tablic Karnaugha pomogła w

znalezieniu nieoczywistych mo liwo ci uproszczenia układu?

Literatura

[1] J. Kalisz,

Podstawy elektroniki cyfrowej

, WKiŁ, Warszawa 2002.

[2] P. Horowitz, W. Hill,

Sztuka elektroniki

, WKiŁ, Warszawa 2001,

[3] U. Tietze, Ch. Schenk,

Układy półprzewodnikowe

, WNT, Warszawa 1987.

[4] M. Molski,

Wst p do techniki cyfrowej

, WKiŁ, Warszawa 1989.

[5]

R. wirko, M. Rusek, W. Marciniak,

Układy scalone w pytaniach i odpowiedziach

, WNT, Warszawa, 1987.

[6] W. Traczyk,

Układy cyfrowe. Podstawy teoretyczne i metody syntezy

, WNT, Warszawa 1986.

[7] P. Misiurewicz,

Układy automatyki cyfrowej,

Wydawnictwa Szkolne i Pedagogiczne, Warszawa, 1984.

[8] A. Rusek,

Podstawy elektroniki

, cz

2, Wydawnictwa Szkolne i Pedagogiczne, Warszawa, 1983.

[9] B. Zbierzchowski, T. Łuba, K. Jasi ski, M. A. Markowski,

Synteza logiczna w układach programowalnych

,

Wydawnictwa Politechniki Warszawskiej, Warszawa, 1992.

w

1

G

1

4 kW

w

2

G

2

2 kW

w

3

Schemat

do zad. 7

Wyszukiwarka

Podobne podstrony:

EL2

Miernictwo el2 SPRAWOZDANIE cw 2

Miernictwo el2 SPRAWOZDANIE cw 3

El2 M wnski

El2 T wnski

sprawozdanie el2

el2, Studia, sprawozdania, sprawozdania z układów elektronicznych

Miernictwo el2 SPRAWOZDANIE cw 4

EL2

EL2

więcej podobnych podstron