POSK zminimalizowane jak się dało

MC_OMEN

1. Jaki cel przyświecał podziałowi jednostki centralnej na kilka działających współbieżnie jednostek

funkcjonalnych? Wyjaśnij na przykładzie.

Cel : Przyśpieszenie pracy procesora (wykonywanie czynności jednocześnie)

Koprocesor 8087:

- blok rozkazów sterujących i współpracy z magistralą (pobieranie rozkazów i argumentów, wysyłanie wyników stanu

układu do pamięci, odtwarzanie stanu układu; wykonuje rozkazy sterujące)

- blok rozkazów numerycznych. (operacje na argumentach umieszczonych w bloku rejestrów (stos))

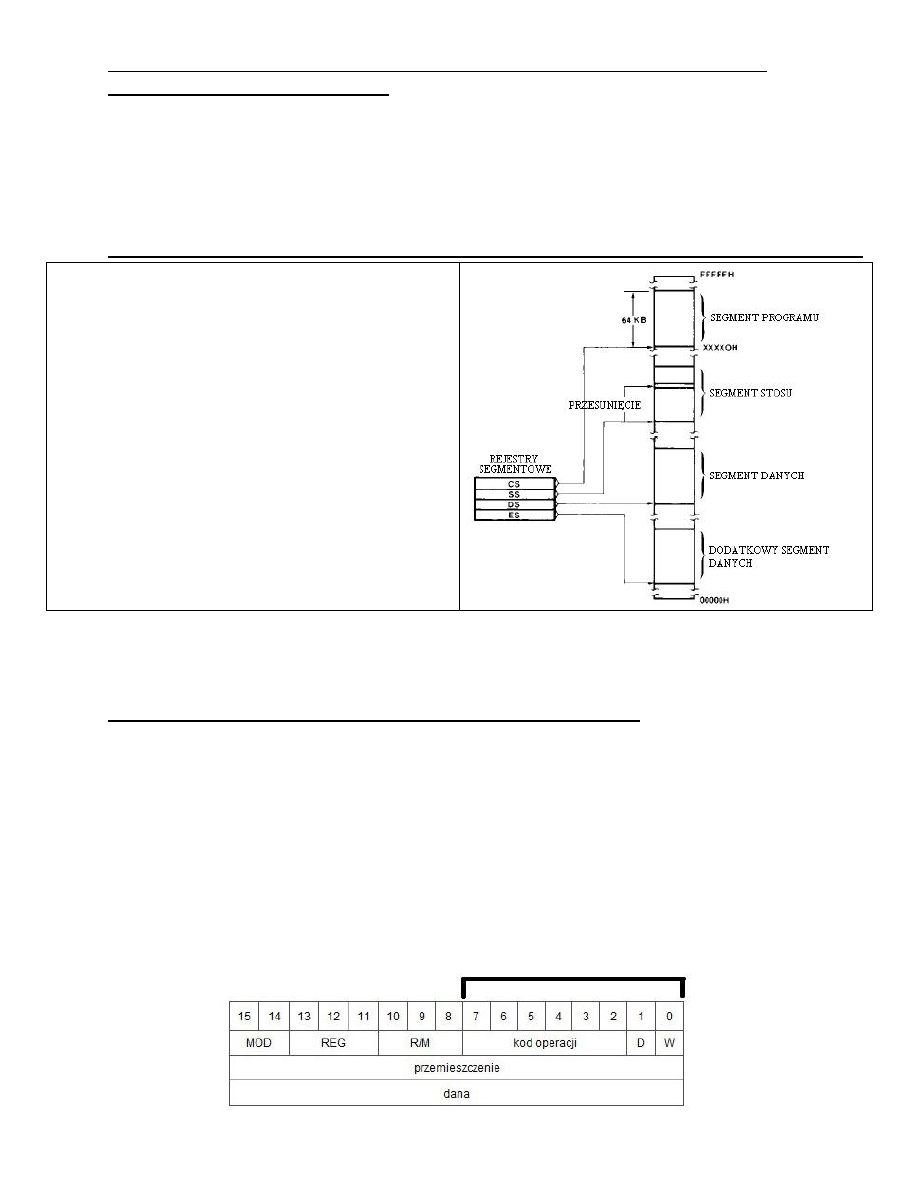

2. Przedstaw ideę i sposób realizacji podziału przestrzeni adresowej mikroprocesora na przykładzie I800 lub Ix86.

Idea: Segmentacja pamięci ->Każdy proces otrzymuje swój

własny obszar pamięci, realizowany poprzez rejestry

segmentowe. Segmentacja pamięci polega na podzieleniu

przez procesor pamięci fizycznej na fragmenty o

określonym początku, rozmiarze, atrybutach i

identyfikatorze. System tworzy takie segmenty na żądanie

aplikacji, przekazując jej jedynie identyfikatory nie

pozwalające na odczytanie parametrów segmentów.

Mikroprocesor 8086 posiada 20-bitową magistralę

adresową. Pozwala ona na zaadresowanie do 1MB pamięci

operacyjnej. Przestrzeo adresowa została podzielona na

segmenty o długości 64kB, rozpoczynające się co 16 bajtów

(kolejne segmenty pamięci mogą nakładad się na siebie).

CS – segment kodu programu, SS – segment stosu, DS –

segment danych, ES – dodatkowy segment danych

I8080

Dla tego przypadku jest 16 bitowa magistrala adresowa pozwalająca na zaadresowanej do 64 kB , 8 bitowa magistrala

danych. Przestrzeo adresowa jest podzielona na segmenty 8 bitowe.

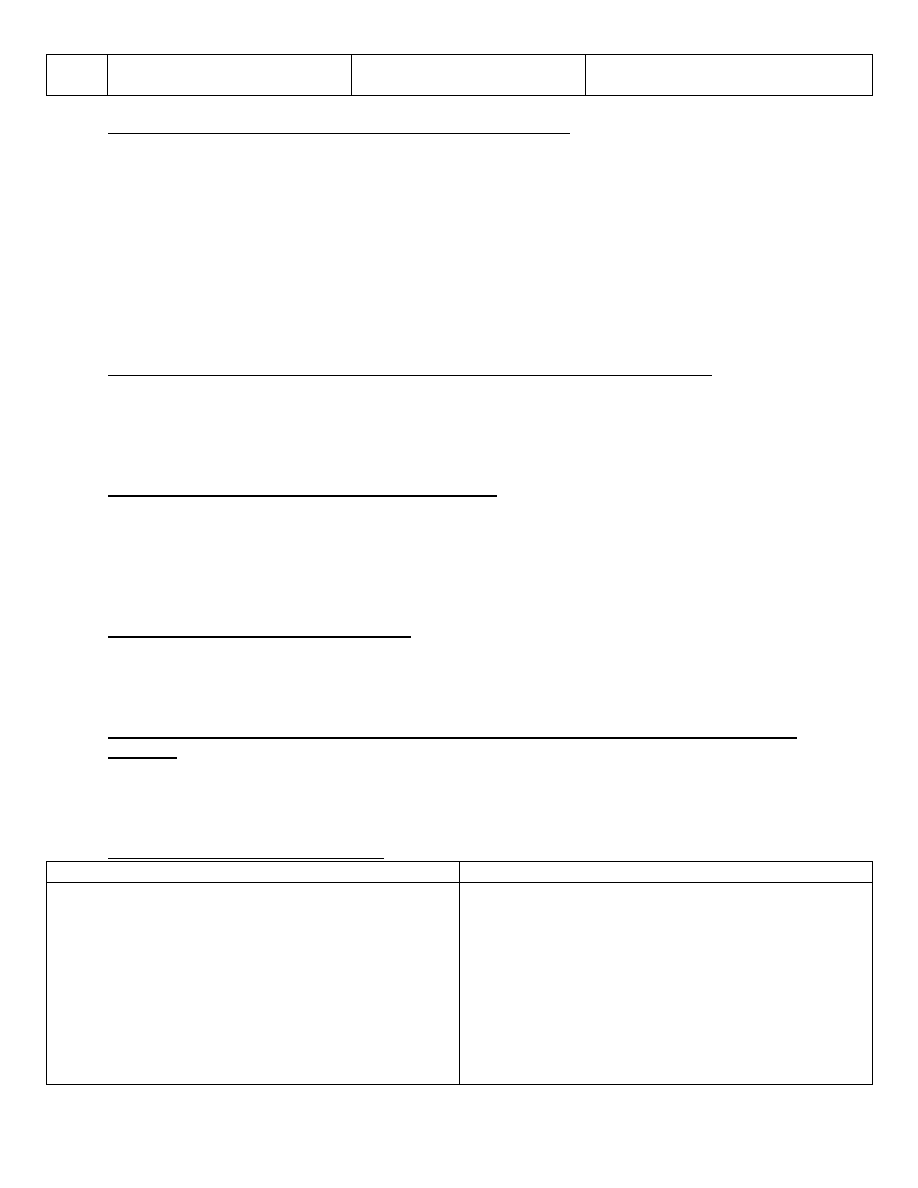

3. Opisz budowę i składnię rozkazu mikroprocesora na przykładzie I800 lub Ix86.

Rozkazy mikroprocesora 8086 są wielobajtowe. Ich liczba (bajtów) zależy od rodzaju rozkazu i może wynosid od jednego

do sześciu. Pierwszy bajt : kod operacji + D+W.

Bit D określa kierunek transmisji (0 - wynik operacji jest przesyłany z rejestru do pamięci, 1 - z pamięci do rejestru). W

zależności od wartości tego bitu w rozkazie rozróżniane są operandy źródłowe i operandy przeznaczenia. Bit W określa

długośd operandu danego rozkazu (0 - operacje bajtowe, 1 - operacje na słowie 16-bitowym).

Jeżeli rozkaz jest wielobajtowy, to drugi bajt rozkazu określa sposób adresowania argumentów. Zawiera on trzy grupy

bitów : MOD określa tryb adresowania, REG określa numer rejestru, w którym znajduje się operand, R/M określa sposób

wyznaczenia miejsca operandu. Trzeci i czwarty bajt to bajty przemieszczenia (jeden lub dwa – w zależności od MOD).

Piąty i szósty bajt to argumenty natychmiastowe.

4. Wymieo i opisz trzy dowolnie wybrane tryby adresowania. Podaj przykłady.

Nazwa

Adresowanie

natychmiastowe

Adresowanie rejestrowe

Adresowanie

bezpośrednie

Opis

Argument pobierany jest

bezpośrednio z rozkazu. W

tym trybie wskazywany jest

wyłącznie operand źródłowy

operandy znajdują się w rejestrach

wewnętrznych mikroprocesora. Jeżeli operand

znajduje się w pamięci, to zespół wykonawczy EY

oblicza jego 16-bitowy adres (przesunięcie)

wewnątrz segmentu. Zespół BIU oblicza adres

rzeczywisty na podstawie otrzymanego

przesunięcia (adresu efektywnego EA) i

zawartości wybranego rejestru segmentowego

adres operandu

znajduje się

bezpośrednio w

rozkazie

Przykład

MOV AX, 20

MOV AX, BX

MOV AX, [40]

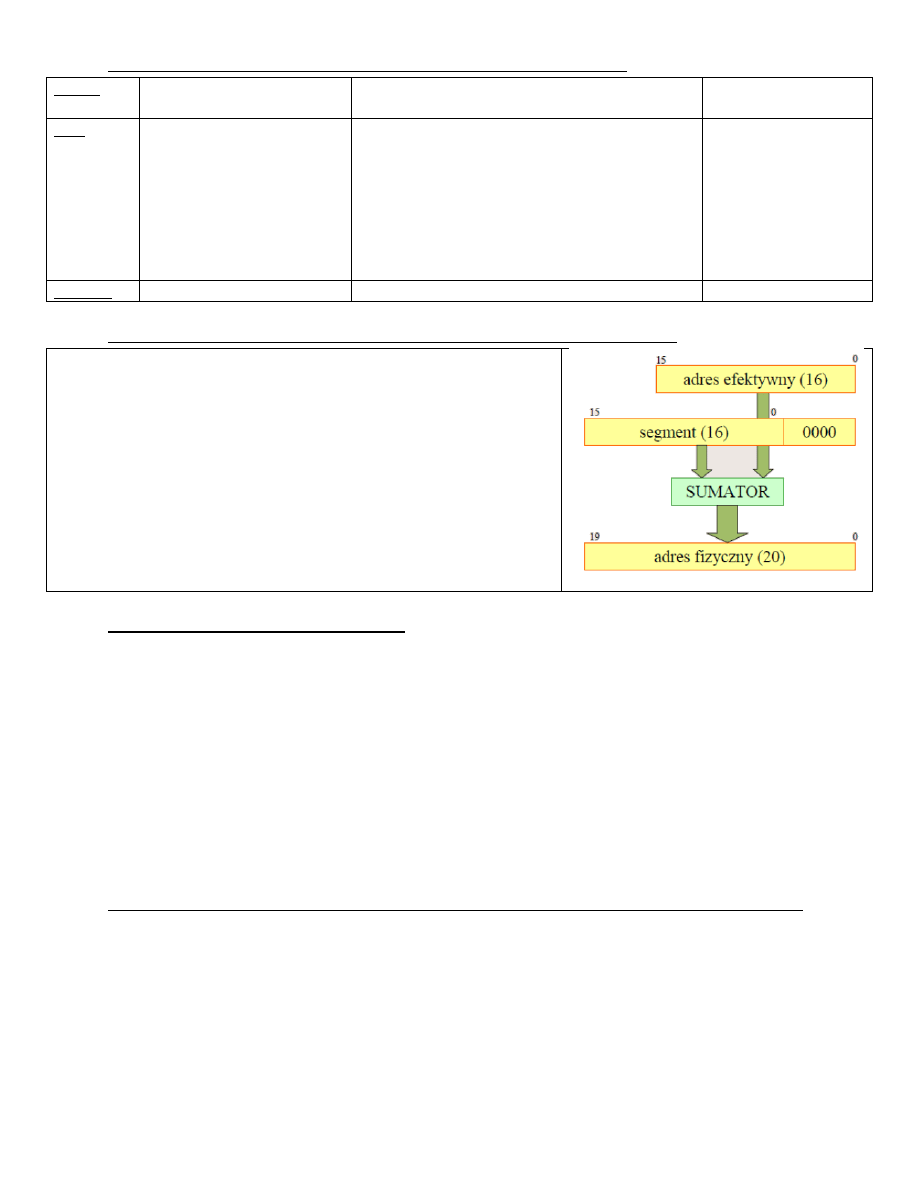

5. Jak przebiega translacja adresu logicznego segment-przesunięcie na adres fizyczny?

Operacja translacji adresu logicznego na fizyczny jest dokonywana przed

wykonaniem każdej instrukcji maszynowej przez procesor. Adres logiczny

składa się z dwóch części:

• 16 bitowej części segmentowej (zawartośd jednego z rejestrów

segmentowych )

• 16 bitowego przemieszczenia (adres efektywny)

co zapisujemy w postaci:

częśd segmentowa : przemieszczenie

adres fizyczny = częśd segmentowa*16 + przemieszczenie

Oznacza to, że przemieszczenie dodaje się do części segmentowej

przesuniętej o 4 bity w lewo, co daje adres 20 bitowy, którym można

zaadresowad 220 = 1048576 bitów = 1MB pamięci operacyjnej RAM.

6. Opisz przebieg cyklu pracy mikroprocesora.

Pobranie (fetch) – kod rozkazu zostaje pobrany z pamięci do zestawu rejestrów tworzących kolejkę rozkazów skąd

trafi do rejestru rozkazów IR procesora;

Dekodowanie (decode) – w tej fazie rozkaz jest dekodowany i ustalane są, jeśli wymaga tego typ rozkazu, połączenia

arytmometru z rejestrami, które mają dostarczyd argumentów operacji

Odczyt (read) – jeżeli rozkaz wymaga argumentu z pamięci operacyjnej, to zostaje obliczony jego adres, a następnie

argument jest odczytywany i wprowadzany do procesora

Wykonanie (execute) – w tej fazie operacja zdefiniowana rozkazem jest wykonywana;

Zapis (write) – jeżeli wynik operacji ma byd umieszczony w pamięci operacyjnej, to zostaje obliczony adres i

wykonany jest zapis do pamięci

Po zapisie modyfikowany jest licznik rozkazów o liczbę zależną od długości rozakzu i jego typu

7. Opisz ideę i podaj przykład wykorzystania mechanizmu oczekiwania mikroprocesora (READY – WAIT).

Wejście Ready – wejście sygnału wskazującego jednostce centralnej obecnośd danych na magistrali. Sygnał jest używany

do synchronizacji CPU z pamięcią lub urządzeniami we/wy, jeżeli po wysłaniu adresu jednostka centralna

mikroprocesora (I8080) nie otrzyma sygnału na wejściu READY wejdzie w stan oczekiwania (WAIT) i pozostanie w nim do

chwili pojawienia się stanu wysokiego na linii READY. Wyjście WAIT – wyjście sygnału potwierdzającego stan oczekiwania

jednostki centralnej na dane. Jeżeli WAIT = 1, to mikroprocesor oczekuje na zgłoszenie gotowości do obsługi układu

zewnętrznego (pamięd, układ we/wy).

8. Przedstaw budowę i objaśnij konstrukcję sprzętu portu wejściowego mikroprocesora pracującego z

potwierdzeniem.

Mikroprocesor 8255 może pracowad w trzech trybach: 0, 1 lub 2. Tryb 1 charakteryzuje:

• porty pracują jako wejście z potwierdzeniem lub wyjście z potwierdzeniem

• przesłanie danych następuje z potwierdzeniem;

• sygnały sterujące przepływem danych przesyłane są liniami szyny PC;

• przesyłane dane są pamiętane (porty A, B).

Natomiast dla trybu 2 jest to:

• przesyłanie danych odbywa się w obu kierunkach tylko poprzez port A;

• sygnały sterujące wysyłane są liniami portu C;

• przesyłane dane (w systemie z potwierdzeniem) są pamiętane;

• port A stanowi dwukierunkowy układ we/wy z potwierdzeniem.

W obu przypadkach stosuje się sygnał wejściowy ACK (acknowledge) – sygnał potwierdzenia odczytu, odebrania danych.

W trybie 1 niski poziom sygnału ACK informuje, że dane kanału A lub kanału B zostały odebrane przez urządzenia

zewnętrzne. W trybie 2 niski poziom na wejściu ACK odblokowuje trójstanowy bufor wyjściowy kanału A, aby wysłał

dane wyjściowe. W innym przypadku bufor wyjściowy znajduje się w stanie wysokiej impedancji.

9. Przedyskutuj wady i zalety trzech mechanizmów przekazania potwierdzenia operacji wejścia/wyjścia do

mikroprocesora.

Nazwa

A-programowe sterowanie I/O z odpytywaniem

(ang. polling):

B-obsługa I/O w przerwaniu:

C-bezpośredni dostęp

do pamięci przez kanał

DMA

Opis

przetwarzanie danych odbywa się całkowicie pod

kontrolą programu realizowanego przez procesor.

// Opis przerwania

Wady

ciężar współpracy przerzucony na procesor i

programistę, który musi znad protokół i

specyfikację techniczną urządzenia, zajętośd

procesora spowodowana okresowym

odpytywaniem urządzenia.

koniecznośd programowej i

sprzętowej obsługi przerwao

(zewnętrzny lub wewnętrzny

kontroler przerwao).

koniecznośd

programowej i

sprzętowej obsługi

transmisji DMA

(wymagany kontroler).

Zalety

przejrzystośd kodu.

obsługa urządzenia

(dodatkowe zadanie dla

procesora) tylko wtedy, gdy

jest zgłaszana taka potrzeba.

wymiana danych bez

udziału procesora. Daje

to odciążenie procesora

oraz możliwośd

efektywnego

przesyłania danych przy

dużych, podobnych

blokach danych.

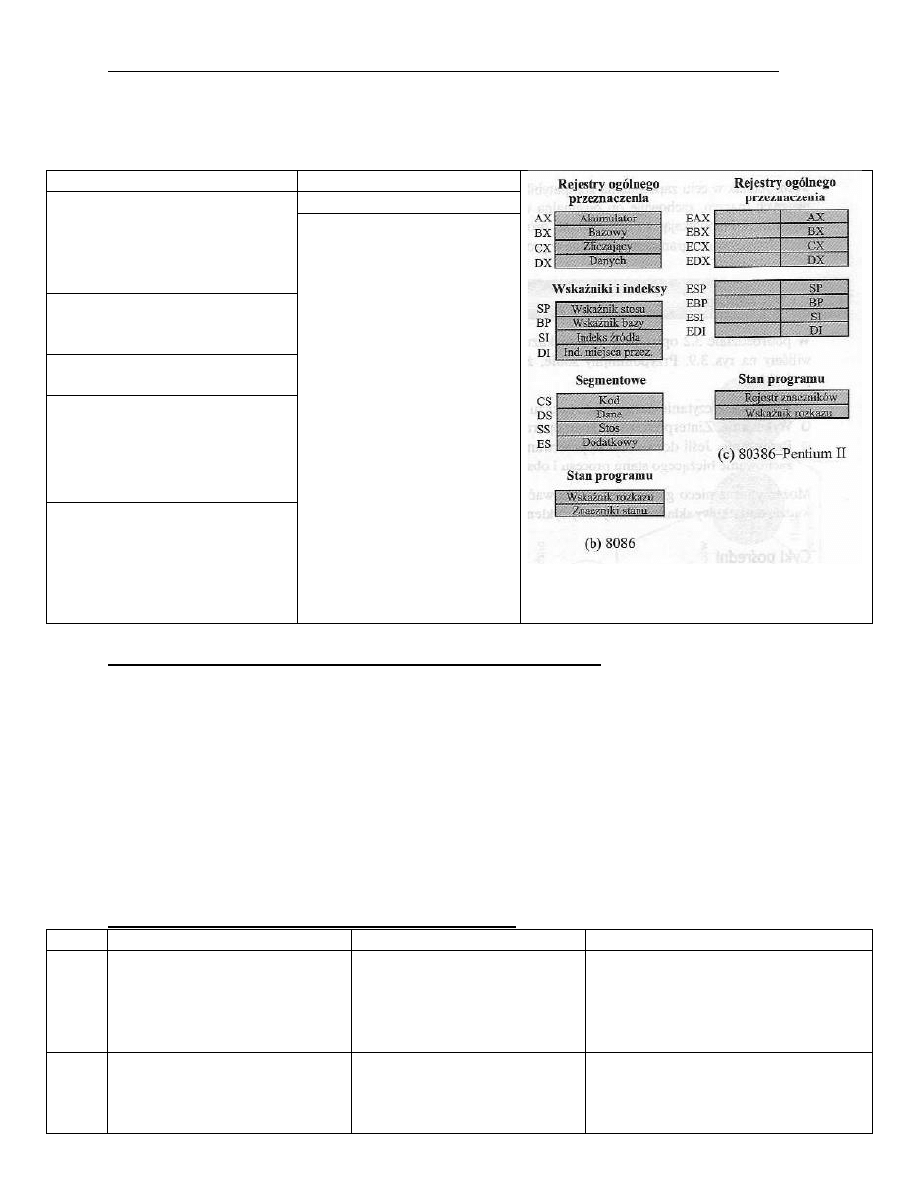

10. Opisz mechanizm kompatybilności w dół na przykładzie organizacji rejestrów mikroprocesora x86.

Kompatybilnośd wsteczna - cecha standardu, urządzenia lub oprogramowania, dzięki której - mimo zmiany

funkcjonalności - nowa wersja umożliwia współpracę z całym otoczeniem starej wersji i jej wszystkimi komponentami.

Mówi się wtedy o rozszerzeniu funkcjonalności. W przypadku mikroprocesora rodziny x86 organizację rejestrów można

przedstawid schematycznie:

8086

80386

Każdy rejestr jest

wyspecjalizowany, chociaż

niektóre z nich mogą również

służyd jako rejestry ogólnego

przeznaczenia.

Rejestry 32-bitowe

W celu zapewnienia

kompatybilności programów

napisanych dla wcześniejszych

maszyn procesor 80386

zachowuje oryginalną

organizację rejestrów

osadzoną w nowej organizacji.

Dla architektów procesorów

jest to znaczne ograniczenie

projektowe, które zmniejsza

swobodę w projektowaniu

organizacji rejestrów.

Podobną kompatybilnośd

zachowano dla trzeciej

generacji procesorów z

rodziny x86, czyli procesorów

64-bitowych.

4 16-bitowe rejestry danych,

adresowalne na podstawie 8- lub

16-bitowej,

4 16-bitowe rejestry wskaźnikowe

i indeksowe

W odniesieniu do niektórych

rozkazów rejestry danych mogą

służyd jako robocze. W odniesieniu

do pozostałych rozkazów są one

używane domyślnie

Specjalizacja rejestrów umożliwia

uzyskanie zwięzłego kodu kosztem

elastyczności.

Wskaźnik rozkazu i zespół 1-

bitowych znaczników stanu i

sterowania

11. Wymieo i opisz znaczenie dla mikroprocesora rejestrów segmentowych.

Rejestr segmentowy – rejestr procesora stworzony do przechowywania adresu początkowego obszaru pamięci, w

którym umieszczone są rozkazy, dane albo stos programu. Rejestry segmentowe są realizacją idei segmentacji pamięci i

lokalności danych. W trybie rzeczywistym adresy mają 20 bitów. Natomiast rejestry mają 16 bitów. Zatem by uzyskad

fizyczny adres komórki pamięci zawartośd rejestru segmentowego mnoży się razy 16 (aby uzyskad przesunięcie w prawo

w segmencie o 4 bity – 24, czyli brakujące 4 bity do 20 bitów adresu rzeczywistego wypełnia się zerami) i dodaje

przesunięcie (OFFSET) (odległośd od początku segmentu). W trybie chronionym rejestry segmentowe zawierają

selektory, które wskazują na pole w tablicy deskryptorów. Z wskazanego elementu tablicy deskryptorów procesor

pobiera 32-bitowy adres bazowy (w przypadku 80286 deskryptor zawiera jedynie 24-bitowy adres bazowy), który

sumowany jest z przesunięciem. Tak powstaje adres liniowy, który przy włączonym mechanizmie stronicowania zostaje

poddany transformacji na adres fizyczny. Uwaga: w tym trybie zawartośd rejestru segmentowego nazywana jest

selektorem!

12. Jaką rolę odgrywają flagi I, D oraz T w mikroprocesorze x86.

Nazwa IF (interrupt flag)

DF (direction flag)

TF (trap flag)

Opis

znacznik przerwao

znacznik kierunku, wskazuje, czy

zawartości rejestrów SI i DI mają

byd zwiększane lub zmniejszane

o jeden w czasie wykonywania

operacji łaocuchowych

znacznik pułapki umożliwiającej pracę

krokową

1

zezwolenie na przyjmowanie

przerwao

- rejestry są zmniejszane

praca krokowa włączona,

mikroprocesor po wykonaniu każdego

rozkazu wykona skok do odpowiedniego

podprogramu obsługi przerwania

0

brak zezwolenia na przyjmowanie

przerwao z wejścia INT

rejestry są zwiększane

praca krokowa wyłączona

13. Opisz czynności j.c. związane z przyjęciem przerwania sprzętowego.

Przerwania są sprzętowym mechanizmem służącym do zawiadamiania procesora o rozmaitych zdarzeniach. Procesor ma

tzw. linię zgłaszania przerwao, którą bada po wykonaniu każdej instrukcji.

Sygnał przerwania -> przerwanie aktualnego ciągu instrukcji -> zapamiętanie stanu na stosie -> wykonanie instrukcji

przerwania -> powrót do przerwanego ciągu instrukcji.

Rozróżnianie przerwao :

• odpytywanie - procedura obsługi przerwania pyta się kolejno wszystkich urządzeo, czy to nie one spowodowały

przerwanie; rozwiązanie to jest stosowane wówczas, gdy mamy tylko jeden rodzaj przerwao,

• wektor przerwao - w systemie może byd wiele rodzajów przerwao, a każdemu rodzajowi odpowiada osobna procedura

obsługi; adresy tych procedur są przechowywane w tablicy systemowej nazywanej wektorem przerwao; rozwiązanie to

jest bardziej efektywne niż odpytywanie.

14. Przedstaw algorytm wyznaczania adresu fizycznego operandy dla rozkazu MOV r, [SI+d].

W generatorze adresu fizycznego określony jest adres rozkazu MOV (w segmencie kodu programu). Następnie do

zawartości rejestru źródłowego SI (source index) dodawana jest wartośd d. Po raz kolejny w generatorze adresu

fizycznego wyznaczany jest adres argumentu w segmencie danych, na podstawie wartości SI + d. Ostatecznie do rejestru

r wpisywany jest znaleziony argument.

15. O czym decyduje przyjęcie określonego modelu pamięci?

Określenie modelu pamięci jest związane z jej podziałem. Operacje wykonywane w 1 segmencie nazywamy bliskimi,

wykonywane w wielu segmentach to operacje dalekie. Użycie modeli pamięci TINY, SMALL i COMPACT pozwala na

odwołania bliskie, LARGE i HUGE na odwołania dalekie. Wywołania bliskie są szybsze, prostsze i oszczędniej wykorzystują

pamięd i stos. Model pamięci trzeba dostosowad do programów wywołujących, modułów bibliotecznych i rozmiarów

programu.

16. Co to jest i do czego służy kolejka rozkazów?

Jest to 6-bajtowa pamięd zorganizowana w słowa (3x 2bajtowe komórki) wykorzystywane przez mikroprocesor do

przechowywania pobranych wcześniej rozkazów. Służy do przyspieszania pracy procesora poprzez pobieranie rozkazów

w czasie, w którym procesor nie wykorzystuje szyny danych.

17. Dlaczego liczby 16-bitowe powinny byd umieszczone w pamięci pod adresem parzystym? Odpowiedź

uzasadnij.

Wynika to ze sposobu dostępu do pamięci w zależności od wartości sygnału BHE i bitu adresu A0. Jeśli liczba 16-bitowa

jest umieszczona pod adresem parzystym, to jej transfer jest przeprowadzony w jednym cyklu maszynowym. W

przeciwnym razie do transferu liczby 16-bitowej potrzeba dwóch cykli maszynowych.

18. Porównaj cechy architektury CISC i RISC.

CISC

RISC

Zawierają ograniczony, prosty zbiór instrukcji.

Zawierają dużą liczbę uniwersalnych rejestrów.

Instrukcje arytmetyczno-logiczne wykonywane są na

rejestrach.

Kody instrukcji są stałej długości, typowo 16 bajtów, i

maja stałe rozmieszczenie pól, co ułatwia dekodowanie.

Posiadają mała liczbę trybów adresowania.

Występują skomplikowane instrukcje wspierające języki

wysokiego poziomu.

Zawierają mała liczba rejestrów i/lub rejestry

specjalizowane.

Instrukcje arytmetyczno-logiczne mogą pobierad

argumenty z pamięci i umieszczad wynik w pamięci.

Kody instrukcji maja zmienna długośd, typowo od jednego

do kilkunastu bajtów. Występuje prefiksowanie instrukcji

utrudniające dekodowanie.

Posiadają dużą liczbę trybów adresowania.

19. Na czym polega większa efektywnośd rozkazów operujących na łaocuchach (ciągach) w stosunku do ciągu

klasycznych rozkazów tworzących pętlę programową?

Rozkazy operujące na ciągach słów posługują się indeksami. Rejestry SI i DI zawierają adresy efektywne pierwszego

słowa odpowiednio w ciągu źródłowym i wynikowym. Po każdej transmisji wartości rejestrów indeksowych są

automatycznie inkrementowane lub dekrementowane w zależności od ustawienia bitu flagi D w rejestrze flag. Większa

efektywnośd polega na braku konieczności pobierania za każdym razem instrukcji.

20. Czym różni się skok zwykły od skoku ze śladem?

Instrukcja skoku ze śladem wykonuje skok po uprzednim zapamiętaniu wartości rejestru PC. Podczas wykonywania

instrukcji skoku ze śladem PC wskazuje następną instrukcję po instrukcji skoku, i taka właśnie wartośd PC podlega

zapamiętaniu. Instrukcja skoku ze śladem służy do przekazania sterowania do procedury (wywołania procedury).

Instrukcja powrotu według śladu jest instrukcją skoku, której adres docelowy jest uprzednio zapamiętanym adresem

śladu wywołania, czyli adresem wskazującym następną instrukcję po ostatnio wykonanej instrukcji skoku ze śladem.

Czyli generalnie: Zapamiętujemy adres miejsca, skąd został wykonany skok. I tak układamy kolejne adresy na stos

Możemy zatem, cofając się, wrócid aż do punktu wyjścia. Skok ze śladem - rozkaz CALL – zapisuje na stosie adres

powrotu do procedury (adres następnej instrukcji) – jest to albo IP albo CS:IP w zależności czy skok był wewnątrz

segmentu czy między segmentami. Wewnątrz procedury znajduje się rozkaz RET, który pobiera ze stosu adres powrotu ,

ustawiając się tym samym za instrukcją CALL, która oryginalnie spowodowała wykonanie procedury. W przypadku skoku

bez śladu – rozkaz JMP – nie zapisuje się nigdzie ślad powrotu do procedury wywołującej.

21. Porównaj konsekwencje wywołania podprogramu bliskiego oraz odległego.

ACALL wywołanie podprogramu (bliskie - adres 11 bitowy) ACALL PROCEDURA

LCALL wywołanie podprogramu (dalekie - adres 16 bitowy) LCALL PROCEDUR

Wywołanie podprogramowe dalekie wymaga modyfikacji przesunięcia i segmentu, a bliskie nie. W związku z tym,

zajmuje więcej czasu i pamięci.

22. Do czego może byd wykorzystany rozkaz NOP? Podaj przykład.

NOP - no operation - rozkaz pusty.

Umożliwia odliczanie czasu, gwarantuje,że żadne informacje zapisane w rejestrach nie ulegną zmianie, jedynie zajmuje

kilka jednostek czasowych. Jego wykonanie nie wywołuje żadnych efektów, zajmuje jedynie czas 1 cyklu maszynowego.

Często jest on wykorzystywany jako rezerwacja miejsca pamięci przeznaczonego na późniejszą rozbudowę programu

(daje szansę na przyszłe uzupełnienie programu o dodatkowe rozkazy, bez jego ponownej asemblacji), lub jako

niewielkie (1 cykl) opóźnienie w wykonywaniu programu.

23. Na czym polega wektorowy system przerwao?

Najbardziej zaawansowanym i często stosowanym jest system przerwao wektoryzowanych. W systemie tym na sygnał

potwierdzenia przyjęcia przerwania przez jc urządzenie, które zgłosiło przerwanie, podaje na szynę danych kod

identyfikacyjny, który jest traktowany jako numer elementu w wektorze przerwao. Zatem każdemu przerwaniu

przypisany jest adres obsługi przerwania w pamięci programu. W tym systemie każdemu przerwaniu jest przypisany na

stałe priorytet. Jeżeli pojawi się w tym samym czasie kilka przerwao to najpierw obsługiwane jest to o najwyższym

priorytecie, a następnie według ważności priorytetów kolejne przerwania. Często przerwanie o wyższym priorytecie

może przerwad obsługę przerwania o niższym (nigdy nie odwrotnie). Wymaga on użycia osobnego, programowalnego

kontrolera przerwao (ang. PIC). Ten kontroler połączony jest z procesorem. Jeśli urządzenie peryferyjne zgłosi

przerwanie, to kontroler je identyfikuje i przekazuje jego numer procesorowi. Numer ten jest indeksem w tablicy

wektorów przerwao (ang. ivt). Wartościami tej tablicy są adresy procedur obsługi przerwao. Każde przerwanie może

więc mied własną procedurę obsługi. Tablica ta umieszczana jest zazwyczaj na początku pamięci operacyjnej komputera

(rzadko na koocu) i wraz z procedurami obsługi przerwao stanowi częśd systemu operacyjnego.

24. Do czego służy mechanizm pracy krokowej mikroprocesora?

Praca krokowa polega na wykonywaniu pojedynczych cykli rozkazowych lub cykli procesora. Po wykonaniu kolejnego

kroku mikroprocesor zatrzymuje się bądź przechodzi do wykonywania programu sterującego zwanego monitorem.

Dzięki temu istnieje możliwośd kontroli stanu mikroprocesora i pamięci w trakcie wykonywania programu.

25. Jak działa przerwanie typu T (pułapka)?

Przerwanie, które następuje po wykonaniu jednej instrukcji, a przed wykonaniem nastepnej. Procedura obsługi takich

przerwao wraca do tej niewykonanej instrukcji i ją wykonuje. Zatem w działaniu programu nie ma żadnych

nieregularności - przepływ sterowania jest zwyczajny. Pułapka to sytuacja, która nie jest błędem, jej wystąpienie ma na

celu wykonanie określonego kodu; wykorzystywane przede wszystkim w debugerach; gdy procesor powraca do

wykonywania przerwanego kodu, wykonuje następną, po tej która wywołała wyjątek, instrukcję.

26. Do czego służą przerwania niemaskowalne?

Specjalny rodzaj przerwania występujący w większości architektur procesorów. Tym, co odróżnia je od zwykłego

przerwania, jest brak możliwości zignorowania go (zamaskowania maską przerwao). Obecnie przerwania te używa się

głównie do debugowania kodu programów, który może wyłączad zwykłe przerwania (np. kod systemu operacyjnego).

27. Czym różni się adresowanie jednolite od odrębnego pamięci i urządzeo we/wy?

Jednolite - jednakowe traktowanie przez sprzęt odwołao do pamięci operacyjnej i odwołao do urządzeo wejścia-wyjścia;

w adresowaniu jednolitym porty urządzeo zewnętrznych są odwzorowywane w pamięci operacyjnej; te same rozkazy są

używane do adresowania przestrzeni we/wy i pamięci, przestrzenie są rozdzielone tylko fizycznie. Odrębne – do

adresowania we/wy i do adresowania pamięci używane są różne rozkazy.

28. Czym różni się praca mikroprocesora w trybie rzeczywistym i chronionym?

Tryb rzeczywisty

Tryb chroniony

Wszystkie programy pracujące w trybie rzeczywistym

mogą korzystad tylko z instrukcji 16-bitowych i

współpracowad z 20-bitową architekturą pamięci (1 MB).

Tego typu oprogramowanie z reguły jest jednozadaniowe,

co oznacza, że jednocześnie może byd uruchomiony tylko

jeden program. Ponadto nie ma wbudowanej żadnego

ochrony zapobiegającej wykorzystaniu przez program

obszaru pamięci już przydzielonego innemu programowi

lub systemowi operacyjnemu. Jeśli zatem uruchomiono

więcej niż jeden program, dowolny z nich może

spowodowad zawieszenie całego systemu.

Tryb chroniony umożliwia adresowanie pamięci w

większym zakresie niż 1 MB (tryb rzeczywisty), wprowadza

wiele nowych udogodnieo wspierających

wielozadaniowośd, takich jak: sprzętowa ochrona pamięci

(układ MMU), wsparcie w przełączaniu kontekstu

procesora i wiele innych.

32-bitowy tryb pracy procesora został określony terminem

trybu chronionego (ang. protected mode). Nazwa wywodzi

się stąd, że programy działające w tym trybie otrzymują

własny obszar pamięci, przez co nie dochodzi między nimi

do konfliktów. Tego typu ochrona sprawia, że system jest o

wiele bardziej stabilny, ponieważ programy zawierające

błąd nie mogą w prosty sposób zaszkodzid innym

programom lub systemowi operacyjnemu. Poza tym

program, który się zawiesił, może byd usunięty z pamięci

bez szkody dla reszty systemu.

29. Na czym polega technologia MMX?

Technologia MMX (MultiMedia eXtension technology) operuje na ośmiu 64-bitowych rejestrach danych oznaczonych

mm0, ..., mm7, stanowiących części 80-bitowych rejestrów FPU. To wyklucza jednoczesne użycie FPU i MMX! Rejestry

64-bitowe mieszczą spakowane dane np. 2 słowa 32-bitowe, 4słowa 16-bitowe lub 8 słów 8-bitowych. Można

zatem wykonywad jedną instrukcje od razu na zbiorze danych! Technologia MMX wprowadza 57 nowych rozkazów i 4

typy danych ukierunkowanych na przetwarzanie danych multimedialnych. Wiele algorytmów obliczeniowych

wykorzystuje powtarzające się pętle obliczeniowe i obsługuje niewielkie ilości danych. Pętle stanowią poniżej 10% kodu

aplikacji niejednokrotnie zabierają nawet 90% czasu przetwarzania całego algorytmu. Nowe rozkazy MMX zwiększają

wydajnośd pracy tych najczęściej wykonywanych funkcji. Ich szczególną cechą jest możliwośd łączenia niewielkich ilości

danych w większy ciąg, co pozwala na szybsze równoległe wykonywanie obliczeo na wielu porcjach danych. Poprzednio

przetworzenie pewnego zbioru wymagało wielokrotnego wykonania pojedynczego rozkazu.

.Należy podkreślid, że technologia MMX to tylko rozszerzenie listy rozkazów procesora. Jeżeli program tych instrukcji nie

wykorzystuje, to nie mają one żadnego wpływu na wydajnośd.

Przykłady zastosowao:

• wyświetlanie grafiki trójwymiarowej: przekształcenia geometryczne, cieniowanie,

teksturowanie;

• dekodowanie obrazów JPEG i PNG;

• dekodowanie i kodowanie filmów MPEG (m.in. wyznaczanie transformat DCT i IDCT);

• filtrowanie sygnałów: obrazów statycznych, filmów, dźwięku;

• wyświetlanie grafiki dwuwymiarowej (blue box, maskowanie, przezroczystośd);

• wyznaczanie transformat: Haara, FFT.

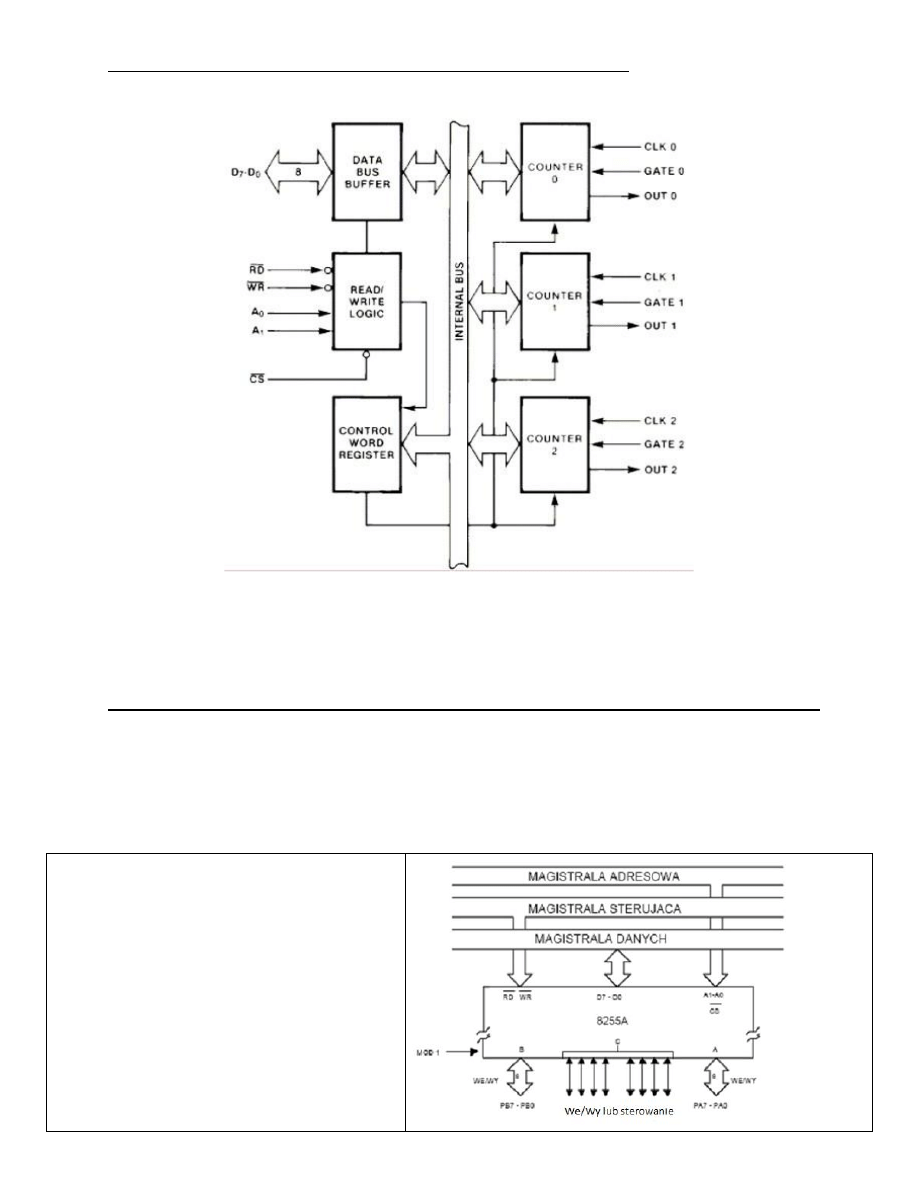

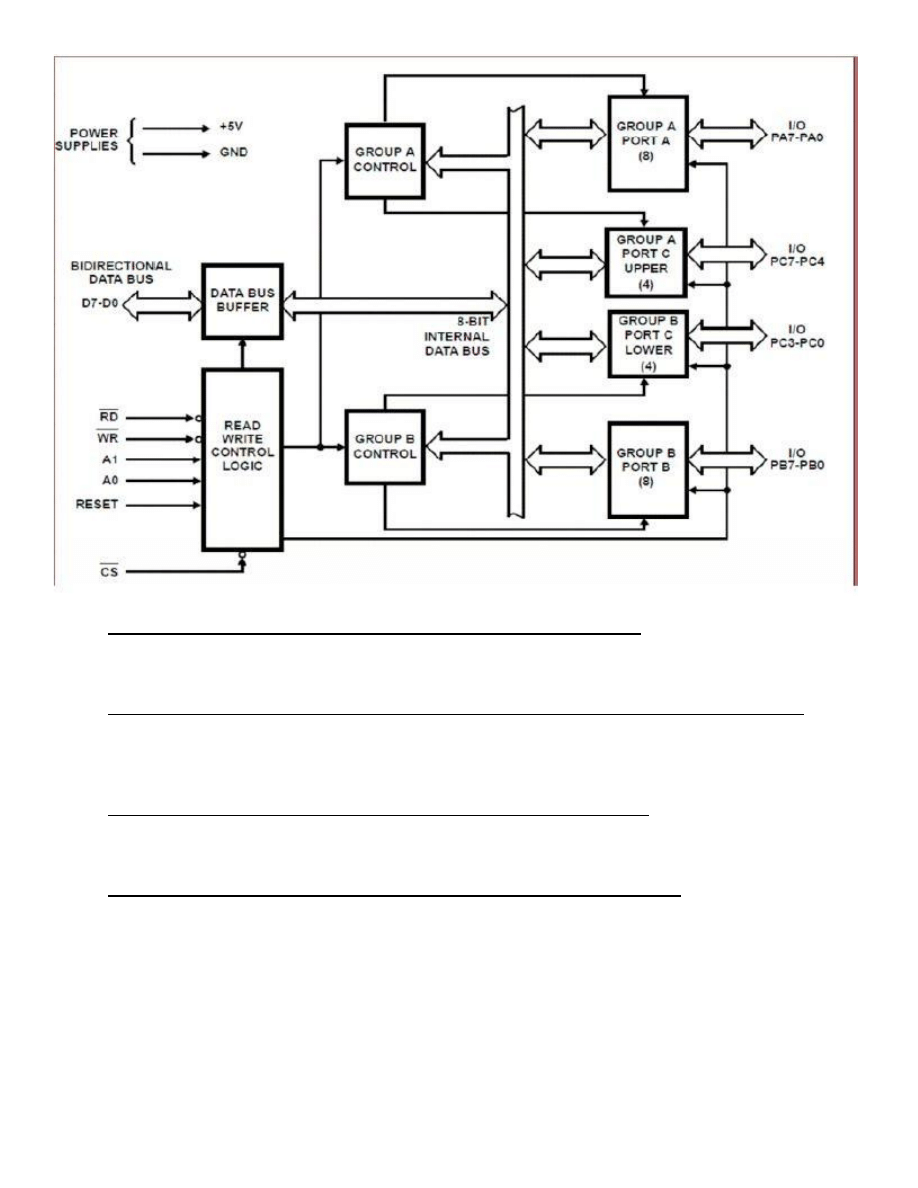

30. Opisz budowę i możliwości układu sprzęgu równoległego 8255.

Port 8255 jest programowalnym układem wejśd/wyjśd równoległych, zajmuje 4 komórki przestrzeni adresowej (trzy z

nich to adresy bram, czwarta to adres rejestru sterującego). Moduł został przystosowany do współpracy z magistralą

procesora 8080 z kontrolerem 8228. Na układ 8255 składają się:

• trzy 8-bitowe porty (bramy PA, PB, PC) mogące pracowad jako wejścia lub wyjścia

równoległe;

• bufor magistrali danych;

• rejestr sterujący RS (pozwala na określenie sposób działania bram).

Linie we/wy można łączyd w dwie, trzy lub cztery grupy w zależności od zaprogramowanego trybu pracy. Funkcje

spełniane przez poszczególne porty, programuje się poprzez przesłanie odpowiednio przygotowanego 8-bitowego słowa

sterującego z jednostki centralnej do rejestru sterującego (RS). Sam proces programowania modułu polega na wyborze

jego trybu pracy oraz określeniu statusu każdej z bram (tzn. czy ma pracowad jako wejście czy jako wyjście). Przesył

danych między CPU a układem 8255 odbywa się poprzez szynę danych. Standardowe sygnały przekazywane między

modułem sprzęgającym a procesorem to:

- 8-bitowa dwukierunkowa magistrala danych

- wejścia RD/WR - sterowanie kierunkiem przepływu danych;

- wejścia A0 oraz A1 adresują źródła danych lub miejsce przesłania (PA, PB, PC, RS);

- wejście wybierania układu

- RESET – zerowanie układu

31. Na czym polega idea układu programowalnego np. portu we/wy czy zestawu liczników?

Układ programowalny to taki układ, którego fizyczna struktura wewnętrzna może byd zmieniana pod wpływem róznych

czynników. W wyniku zmian struktury zmieniają się właściwości elektryczne tego układu, a co za tym idzie, także

realizowane funkcje. Istnieje kilka typów układów programowalnych:

jednokrotnie

programowalne

EPROM

EEPROM

w wewnętrznej

strukturze tych

układów

zmieniana jest struktura

ścieżek metalizacji

poprzez ich przepalanie

(niszczenie) lub

tworzenie przez

przepływ

odpowiedniego prądu.

Dzięki temu możemy

zaprojektowad

niemalże dowolną

ścieżkę połączeo

pomiędzy

poszczególnymi

elementami w układzie.

Układ taki można

zaprogramowad jedynie

raz.

zmiana struktury polega nie na przepalaniu

ścieżek połączeo

lecz na zmianach napięcia progowego

tranzystorów w bramkach. W tego typu

układach stosowane są tranzystory z podwójną

bramką (pływającą). Pomiędzy

kanałem a właściwą bramką jest odizolowany

obszar polikrzemu, który posiada

nieskompensowany ładunek, który wpływa na

napięcie progowe tranzystora. Jak

wiadomo napięcie progowe tranzystora

decyduje o tym, dla jakich wartości napięd

będzie on włączany. Manipulację ładunkiem

nieskompensowanym uzyskuje się

poprzez wstrzeliwanie wysokoenergetycznych

elektronów ze złącza dren-podłoże.

Kasowanie takie układu wykonuje się przez

naświetlanie struktury światłem

ultrafioletowym. Dzięki zachodzącemu zjawisku

fotoelektrycznemu elektrony mogą

opuścid bramkę izolowaną.

zasada działania jest identyczna jak

układów EPROM,

jednak to transportu elektronów do

pływającej bramki wykorzystywane jest

zjawisko

tunelowania nośników z kanału

tranzystora. Kasowanie układu odbywa się

elektrycznie, przez przyłożenie

odpowiedniego napięcia do bramki.

Najprostszą strukturą układu PLD

(Programable Logic Device) jest struktura

matrycy bramkowej AND-OR. Matryca taka

posiada programowalną macierz

bramek AND oraz stałą (w układach PAL -

Programable Array Logic) lub także

programowalną (w układach PLA -

Programable Logic Array) macierz bramek

OR.

Przewaga układu PLA nad PAL jest taka, że

każda bramka AND może byd

połączona z każdą bramką OR.

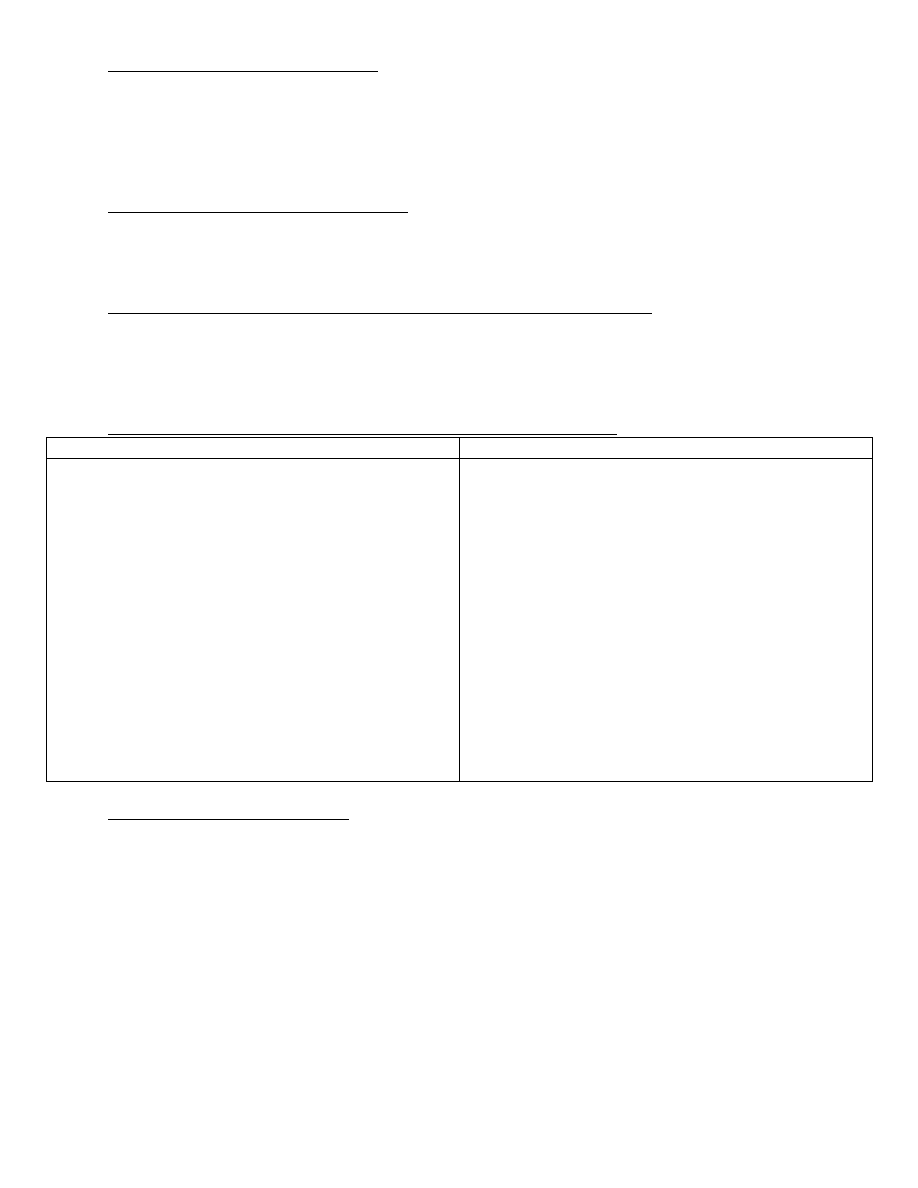

32. Czym różnią się słowa sterujące typu inicjującego i rozkazy wykonawcze? Jak są one odróżniane?

Słowo sterujące określa tryb pracy układu, oraz czy dany port ma pracowad jako wejście, czy jako wyjście. Rozkaz

wykonawczy natomiast ustawia pojedyncze bity na wyjściach układu. Słowa te rozróżnia się przy pomocy rejestru

flagowego.

33. Na czym polega tryb pracy bitowej portu C w układzie 8255?

Polega na ustawianiu pojedynczych bitów portu C za pomocą słowa wykonawczego. Możliwe jest selektywne ustawianie

bądź zerowanie poszczególnych bitów tego rejestru. Do tego celu służy zapis do rejestru kontrolnego słowa z

wyzerowanym najstarszym bitem D7.

Bit 7 – zawsze “0”.

Bity D6, D5, D4 – nie używane (dowolna wartośd, zazwyczaj “0”),

Kolejnośd Wybrany bit

Linia

Schemat

000

D0

PC0

001

D1

PC1

010

D2

PC2

011

D3

PC3

…

…

…

111

D7

PC7

Selektywna modyfikacja bitów rejestru C możliwa jest tylko w trybie 0 pracy rejestrów PA lub PB. Jeżeli np. rejestr PA

pracuje w trybie 1 lub 2, a rejestr PB w trybie 0 to można modyfikowad jedynie bity rejestru PCb (z grupy B) i odwrotnie,

dla PB pracującego w trybie 1, a PA w trybie 0, modyfikowalne są tylko bity PCa.

34. Przedstaw przebiegi czasowe ilustrujące proces wymiany informacji z potwierdzeniem.

INTR- żądanie przerwania,

~ACK- potwierdzenie,

~STB - wejściowy sygnał

strobujący,

IBF – wejściowy bufor pełny,

~OBF – wyjściowy bufor

pełny,

~WR – zapis,

~RD – odczyt.

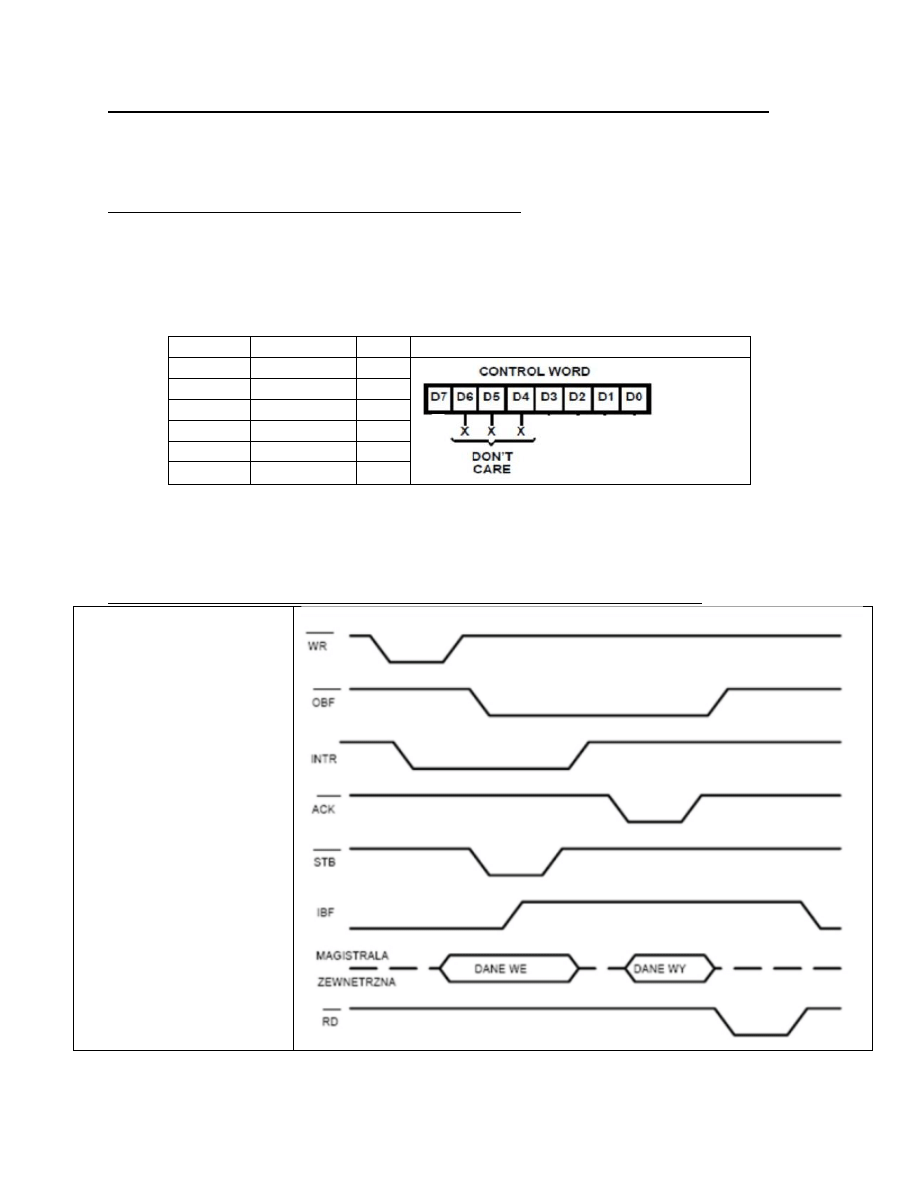

35. Przedstaw budowę i ideę działania układu programowanych liczników 8254.

Możliwośd działania w 6 trybach pracy, które ustawia się przy pomocy wejśd D7-D0. Za pomocą RD/WR odczytujemy,

bądź wpisujemy coś z/do liczników. Wybór licznika następuje poprzez A0,A1. Taktowanie liczników - CLK 0-2, wartości

liczników – OUT 0-2, GATE 0-2 startowanie, blokowanie, zatrzymywanie licznika. Dzięki różnym trybom pracy układ daje

nam możliwośd wygenerowania licznika zarówno w górę, jak i w dół lub sygnał cykliczny z opóźnieniem. By nie popełnid

błędu należy odczytywad wartośd z rejestru, w którym zapisaliśmy chwilową wartośd licznika, a nie z samego licznika.

36. Opisz ideę sprzęgania programowalnego układu z magistralą systemową (na przykładzie 8255 lub 8254).

Sprzęganie układu programowalnego z magistralą ma sens wtedy, gdy zależy nam na dużej prędkości działania. Łączy się

to ze złożonym hardwar'em, a z drugiej strony -nieskomplikowanym softwar'em. Najprościej rzecz mówiąc, układ 8255

zawiera trzy uniwersalne 8−bitowe porty (PA, PB i C), z których każdy może byd skonfigurowany jako wejście, wyjście a w

pewnych trybach spełniad rolę mieszaną, nawet z możliwością generowania przerwao do procesora.

Dodatkowo, oprócz wspomnianych rejestrów portów PA, PB i PC układ 8255 zawiera tzw. czwarty rejestr konfiguracyjny,

dzięki któremu możliwe jest ustalenie, jak ma pracowad cały układ, czy np. port PA ma byd ustawiony jako wejściowy, czy

wyjściowy itp.

-wejścia RD/WR - sterowanie kierunkiem

przepływu danych,

-wejścia A0 oraz A1 adresują źródła danych lub

miejsce przesłania (PA, PB, PC, RS),

- 8-bitowa dwukierunkowa magistrala danych (D0-

D7) – przesyła się przez nie słowa sterujące lub

wykonawcze, czyli programuje tryby pracy.

37. Opisz trzy wybrane tryby pracy programowanych liczników układu 8254.

Licznik 2 może byd programowany przez użytkownika w 6 różnych trybach. Typową wartością częstotliwości na

wejściach zegara jest 1,19 MHz, przetwarzane przez generator taktowania, znajdujący się na płycie głównej. Wejście

GATE licznika 2 sterowane jest przez bit 1 portu B układu PIO.

Tryb

Nazwa

Opis

0

interrupt on

terminal count

Wyjście licznika (Output Interrupt) określone zostaje po otrzymaniu Control Word w

odniesieniu do wartości Low. Liczenie rozpoczyna się po ustaleniu stanu licznika, a taktowane

jest przez wejście CLK. Przy tym wartośd wyjścia ustawiana jest na pozycji High, kiedy tylko stan

licznika osiągnie zero. W takiej sytuacji wyjście jest zamknięte do momentu, w którym

zdefiniowany zostanie kolejny stan licznika Licznik może byd zatrzymany, jeśli na wejściu GATE

ustalona zostanie wartośd Low. Stan licznika zostaje zachowany, po czym - przez ustawienie

wartości High - liczenie jest kontynuowane.

1

programmable

one - shot

Początkowo dla wyjścia (OUTPUT) określona jest wartośd High. Licznik uruchamia się przez

wzrastający sygnał na wejściu GATE (TRIGGER), natomiast wyjściu przypisana jest wartośd Low.

Po uzyskaniu stanu zero licznik zatrzymuje się, a wyjście ponownie ustawiane jest na High. Przy

pomocy wzrastającego sygnału GATE (TRIGGER) można ponownie ustalid stan licznika. Jeśli

impuls pojawi się na wejściu GATE, zanim stan licznika osiągnie wartośd "zero", to nie ma on

żadnego wpływu na aktualnie wyprowadzoną funkcję. Bowiem nowa wartośd jest uaktywniana

dopiero przez kolejny impuls, czyli po zakooczeniu operacji przeprowadzanych aktualnie przez

licznik.

2

rate generator

- dzielnik

częstotliwości)

Podczas występowania sygnału CLK, na wyjściu ustalona jest wartośd Low. Okres od jednego

pojawienia się sygnału na wyjściu do następnego odpowiada początkowemu stanowi licznika.

Jeśli rejestr licznika jest na nowo uruchamiany pomiędzy kolejnymi impulsami, wywołana przez

to zmiana zaczyna oddziaływad dopiero później. Podczas cyklu zerowego stan licznika określany

jest ponownie. Następnie - po jego uruchomieniu - rozpoczyna się liczenie. Wejście GATE może

byd wykorzystywane do synchronizacji licznika. Poprzez sygnał opadający (wcześniej

wzrastający) na wejściu GATE (Reset) przerywany jest proces liczenia, a na wyjściu pojawia się

wartośd High. Sygnał wzrastający na wejściu GATE uruchamia kolejny cykl.

3

generator z

symetrycznym

sygnałem

wyjścia

odpowiada w zasadzie trybowi 2, z tą tylko różnicą, że częstotliwośd dzielona jest przez dwa,

przez co osiągany jest niemal identyczny stosunek sygnałów High i Low. Wyjściu przeznaczona

jest tylko tak długo wartośd High, aż osiągnięta zostanie połowa wartości początkowej licznika.

Następnie na drugą połowę cyklu wyjściu przyporządkowana zostaje wartośd Low. Przy

nieparzystych wartościach początkowych na wyjściu, wartośd High pozostaje o jeden takt

dłużej, niż wartośd Low, po czym automatycznie uruchamiany jest następny cykl

38. Przedstaw architekturę programowalnego układu portów równoległych 8255.

39. Opisz znaczenie linii CLK, GATE i OUT w programowym liczniku z układu 8254?

CLK – wejście zegarowe (Podajemy zasilanie taktem), GATE – wejście bramkujące (Startuje, zatrzymuje, blokuje liczenie)

oraz OUT – wyjście.

40. Porównaj przeznaczenie rejestrów: rejestr rozkazów i wskaźnik (licznik) rozkazów w mikroprocesorze.

Wskaźnik (Licznik) rozkazów (instruction pointer) (program counter) - zawiera adresy komórki pamięci w której

przechowywany jest kod rozkazu przeznaczony do wykonania jako następny. Rejestr rozkazów (instruction register) -

zawiera kod aktualnie wykonywanego rozkazu.

41. Co ogranicza wielkośd przestrzeni adresowej mikroprocesora? Podaj przykłady.

Wielkośd przestrzeni adresowej ogranicza szerokośd magistrali adresowej mikroprocesora, która dla modelu 8086

wynosi 20bitów. To pozwala na zaadresowanie do 1MB pamięci operacyjnej i 4GB przy pomocy segmentacji.

42. Porównaj cykl pracy prostego mikroprocesora I8080 i mikroprocesora z rodziny x86.

Cykl pracy I8080

1. Pobranie z pamięci operacyjnej kodu rozkazu począwszy od adresu umieszczonego w

liczniku rozkazów IP.

2. Dekodowanie rozkazu i przygotowanie stanu procesora do wykonania rozkazu.

3. Wykonanie rozkazu, zmiana zawartości pamięci lub rejestrów procesora.

4. Modyfikacja licznika rozkazów o liczbę zależną od długości rozkazu i jego typu.

Podstawowa różnica w cyklu pracy mikroprocesora z rodziny x86 występuje w pierwszym kroku ze względu na kolejkę

rozkazów. Kod rozkazu zostaje pobrany z pamięci operacyjnej do kolejki rozkazów i dopiero stąd trafia do

rejestru rozkazów procesora.

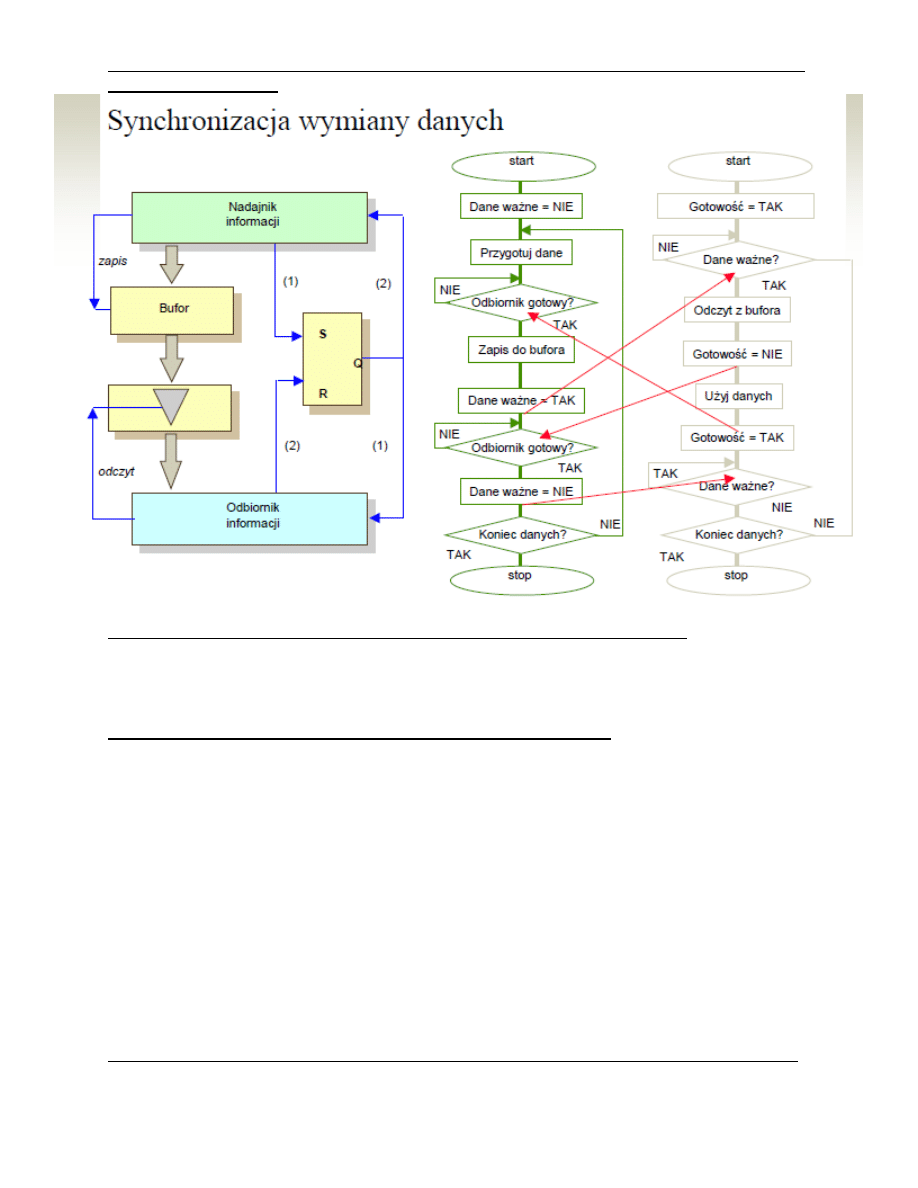

43. Podaj przykład algorytmu wymiany potwierdzeo podczas wymiany informacji pomiędzy nadajnikiem i

odbiornikiem informacji.

44. Do czego służą rejestry zatrzaskowe zawarte w układzie 8254? Odpowiedź uzasadnij.

Po wyzwoleniu odpowiedniego rozkazu zatrzaśnięcia, rejestry zatrzaskowe zapamiętują aktualny stan licznika, aż do

odczytania tego stanu przez procesor. Rejestry te są 8bitowe, zapamiętują 8 starszych i 8 młodszych bitów licznika

16bitowego. Dzięki temu procesor może odczytad stan 16bitowego licznika poprzez 8bitową szynę danych.

45. Na czym polega idea stronicowania pamięci w procesorach z rodziny x86?

Idea stronicowania pamięci w procesorach z rodziny x86 polega na tym, iż została ona wprowadzona przez coraz większe

zapotrzebowanie na pamięd, lecz by móc ją obsłużyd zaistniała potrzeba wprowadzenia nowszych technik zarządzania

pamięcią -> stronicowanie pamięci. Jeśli włączone jest stronicowanie, wówczas cała pamięd (4 GB) dzielona jest na bloki

– strony o rozmiarach np. 4 kB (w procesorach Pentium i nowszych możliwe jest także używanie stron o rozmiarach 4

MB). Gdy program odwołuje się do pamięci, podaje adres właściwej komórki pamięci. Adres ten jest 32-bitową liczbą,

która składa się z trzech części:

- indeks w katalogu stron (liczba 10-bitowa),

- indeks w tablicy stron (liczba 10-bitowa),

- przesunięcie w obrębie strony (liczba 12-bitowa).

Katalog stron zawiera wskaźniki do tablic stron, tablice stron przechowują adresy fizyczne stron. (System operacyjny

może zarządzad wieloma katalogami i tablicami stron). Zatem pierwsza częśd adresu wybiera z katalogu stron tablicę

stron. Druga częśd adresu wybiera pozycję z tablicy stron, która wyznacza fizyczny adres konkretnej strony. Przesunięcie

jest adresem lokalnym w obrębie wybranej strony. Ostatecznie adres fizyczny, na który zmapowano adres logiczny,

wyznaczany jest z dwóch składników: adresu fizycznego strony i przesunięcia.

46. Co jest przyczyną a co celem wprowadzenia segmentacji pamięci w systemach mikroprocesorowych?

Celem segmentacji pamięci jest rozdzielenie obszarów pamięci przeznaczonych dla programu, danych i stosu. Pozwala to

na sprzętową ochronę pamięci przy pracy wielozadaniowej.

Cel: przyspieszenie pracy komputera dzięki operowaniu krótszymi adresami

Przyczyna: Możliwośd operowania przez procesor jedynie na 16 bitach danych jednocześnie

( 16 bit = 1 segment)

47. Co to jest tablica wektorów przerwao i do czego służy?

Elementy tej tablicy zawierają właściwe adresy początków programów obsługi przerwao. Tablica wektorów przerwao

jest strukturą umieszczoną w pamięci operacyjnej komputera. Każda pozycja tej tablicy związana jest z dokładnie jednym

przerwaniem i zawiera adres komórki pamięci, w której znajduje się początek (kod pierwszej instrukcji) programu

obsługującego to przerwanie. Po dokonaniu arbitrażu sterownik przerwao podaje na swoim wyjściu danych numer

przerwania, które ma byd obsłużone. Mikroprocesor pobiera ten numer i następnie przy jego pomocy odczytuje adres

pocztu programu obsługi przerwania, który ma zostad wykonany. Adres ten, po zapamiętaniu informacji niezbędnych do

powrotu do przerwanego programu głównego, jest ładowany do określonych rejestrów procesora, w tym licznika

rozkazów. Powoduje to wykonanie skoku do programu obsługi przerwania umieszczonego pod adresem odczytanym z

tablicy wektorów przerwao. Po zrealizowaniu wymiany następuje powrót z programu obsługi przerwania do programu

głównego, który jest kontynuowany. Procesor obsługuje polecenie przerwania przy użyciu tablicy wektorów przerwao,

która znajduje się w początkowych 1024 bajtach pamięci . Każdy element tablicy jest 32-bitowym adresem typu

segment-przesunięcie, który wskazuje procedurę systemu operacyjnego. Rzeczywiste adresy w tablicy zmieniają się w

zależności od komputera. PS. Tablica zajmuje 1024B=32b*256, (1B=8b), czyli standardowych przerwao jest tylko

256 Na szczęście każde przerwanie ma wiele funkcji.

Przykład:

INT 10h to instrukcja żądania usługi grafiki, tak więc odnaleziony w wektorze przerwao dla numeru 10h adres to

F000:F065 pod którym rozpoczyna się obsługa przerwania zakooczona instrukcją RETI, która powoduje powrót do

wykonania kolejnego polecenia w bieżąco wykonywanym programie.

48. Wymieo i opisz przeznaczenie rejestrów jednostki centralnej procesora z rodziny x86.

Jednostka Centralna

Jednostka Wykonawcza

Jednostka Interfejsowa

Rejest

ry o

gól

n

ego

p

rz

ez

n

acze

n

ia

Rejestr znaczników - Bezpośrednio do jednostki

arytmetyczno-logicznej dołączony jest 16-bitowy

rejestr znaczników (rejestr flag). Znajdujące się w nim

flagi zostały podzielone na dwie grupy, tj. kontrolną i

arytmetyczną. Flagi arytmetyczne dostarczają

dodatkowych informacji na temat wyniku ostatniej

operacji wykonanej przez jednostkę arytmetyczno-

logiczną. Flagi kontrolne wpływają na sposób pracy

mikroprocesora. Mniej znaczący bajt rejestru

znaczników odpowiada rejestrowi znaczników

mikroprocesora 8080/8085. Cztery najbardziej

znaczące bity pozostają nieużywane. Przykładowe

znaczniki to: SF (sign flag) - znacznik znaku, ZF (zero

flag) - znacznik zera, PF (parity flag) - znacznik

parzystości, AF (auxiliary carry flag) - znacznik

przeniesienia połówkowego (pomocniczego), CF

(carry flag) - znacznik przeniesienia, OF (overflow flag)

- znacznik nadmiaru, IF (interrupt flag) - znacznik

przerwao, DF (direction flag) – znacznik kierunku, TF

(trap flag) - znacznik pułapki umożliwiającej pracę

krokową.

Licz

n

ik r

o

zkazó

w

(In

struc

ti

o

n

P

o

in

ter

–

IP)

16-bitowy rejestr, którego zawartośd służy do

obliczania adresu fizycznego następnego

słowa rozkazu do pobrania z pamięci. Stanowi on

rejestr indeksowy dla rejestru CS

wyznaczającego segment z kodem programu.

Jego zawartośd jest automatycznie

inkrementowana

po pobraniu każdego bajtu rozkazu (w przypadku

pobrania słowa jego wartośd wzrasta o 2).

Programista ma możliwośd zmiany zawartości

licznika rozkazów poprzez zastosowanie rozkazu

skoku.

Reje

stry

wsk

aź

n

ik

o

w

e

i in

d

ek

so

we

Rejestry arytmetyczne

Są to cztery 16-bitowe rejestry ogólnego

przeznaczenia: AX, BX, CX, DX. Każdy z tych rejestrów

może również działad jako dwa niezależne rejestry 8-

bitowe:

• AX lub AH, AL

• BX lub BH, BL

• CX lub CH, CL

• DX lub DH, DL

AX – Akumulator (Accumulator)

bezpośrednio współpracuje z jednostką

arytmetyczno-logiczną, przechowuje wartości

obliczeniowe

BX – Baza (Base)

używany do adresowania argumentu, znajdującego

się w pamięci, stanowiąc bazę do obliczania adresu

CX – Licznik (Counter)

używany jako licznik w operacjach łaocuchowych oraz

pętlach

DX – Dane (Data)

jest wykorzystywany w niektórych operacjach

arytmetycznych do przechowywania

części argumentu lub wyniku operacji (mnożenie i

dzielenie 16- bitowe). Zawiera on także adres

urządzenia w operacjach wejścia/wyjścia.

Rejestry wskaźnikowe i indeksowe

Są to 16-bitowe rejestry adresowe: SP, BP, SI, DI. Ich

głównym zadaniem jest wskazywanie miejsca

w pamięci, w którym znajdują się argumenty rozkazu.

Wykorzystywane są w adresowaniu

indeksowym, bazowym oraz indeksowo-bazowym.

Można ich również używad do przechowywania

argumentu bądź wyniku operacji. Podobnie jak w

przypadku rejestrów arytmetycznych, rejestry

adresowe mają nazwy zależne od funkcji jaką pełnią:

SP – wskaźnik stosu (Stack Pointer)

BP – wskaźnik bazy (Base Pointer)

SI – rejestr indeksowy źródła (Source Index)

DI – rejestr indeksowy przeznaczenia (Destination

Index)

Reje

stry

s

egm

ent

o

we

Są to 16-bitowe rejestry, dostępne dla programisty,

których zawartośd służy do obliczania adresu

fizycznego komórki pamięci. Rejestry te zawierają

adres początkowy danego segmentu pamięci.

Mikroprocesor w zależności od rodzaju segmentu

pamięci, do którego chce się odwoład, wykorzystuje

odpowiedni z rejestrów. Programista ma możliwośd

zmiany automatycznie wykorzystywanego rejestru

poprzez umieszczenie odpowiedniego prefiksu przed

rozkazem, dla którego zmiana ma zostad zastosowana.

• CS – rejestr segmentowy programu (Code Segment

register) Zawartośd tego rejestru wyznacza początek

aktualnie używanego segmentu programu. Wartośd ta

wykorzystywana jest do obliczania adresu fizycznego

kolejnego rozkazu do pobrania z pamięci.

• DS – rejestr segmentowy danych (Data Segment

register) Zawartośd tego rejestru wyznacza początek

aktualnie używanego segmentu danych. Wartośd ta

wykorzystywana jest do obliczania adresu fizycznego

argumentu lub wyniku aktualnie wykonywanego

rozkazu. Wyjątek stanowią rozkazy łaocuchowe, w

których zawartośd tego rejestru służy jedynie do

obliczania adresu źródła danych.

• SS – rejestr segmentowy stosu (Stack Segment

register) Zawartośd tego rejestru wyznacza początek

aktualnie używanego segmentu stosu. Wartośd ta

wykorzystywana jest do obliczania adresu fizycznego

komórki pamięci, na którą wskazuje wskaźnik stosu

(rejestr SP).

• ES – rejestr segmentowy dodatkowy (Extra Segment

register) Zawartośd tego rejestru wyznacza początek

aktualnie używanego dodatkowego segmentu danych.

Wartośd ta wykorzystywana jest do obliczania adresu

fizycznego przeznaczenia dla operacji łaocuchowych

(np. rozkazu przenoszenia bloku danych).

Wyszukiwarka

Podobne podstrony:

Opracowanie pytań MC OMEN 2

Opracowanie wykladow MC OMEN

Opracowanie pytań MC OMEN 3

Opracowanie projektu MC OMEN

Opracowanie pytań MC OMEN

Opracowanie pytań MC OMEN

Opracowanie pytań MC OMEN 2

Opracowanie wykladow MC OMEN

Opracowanie pytań MC OMEN 2

Opracowanie pytań MC OMEN

Opracowanie wykładów biofyzka 1 MC OMEN

Opracowanie pytań MC KULA MC OMEN 2

Opracowanie pytań RÓŻNE MC OMEN

więcej podobnych podstron