Pamięć systemu komputerowego

1/30

Pamięć komputera

1. Rodzaje pamięci

2/30

1

2

3

4

5

Rodzaje pamięci

Rejestry

RAM (Random Access memory)

SRAM (Static RAM)

DRAM : EDO, XDR

SDRAM (Synchronous Dynamic RAM): DDR (DDR2, DDR3), RDRAM (Rambus)

ROM (Read Only Memory) / WORM (Write Once Storage) / OTP (One Time Programmable )

PROM

EPROM

EEPROM = E2PROM

FLASH

Pamięć magnetyczna / optyczna / papierowa

1. Rodzaje pamięci

3/30

1

2

3

4

5

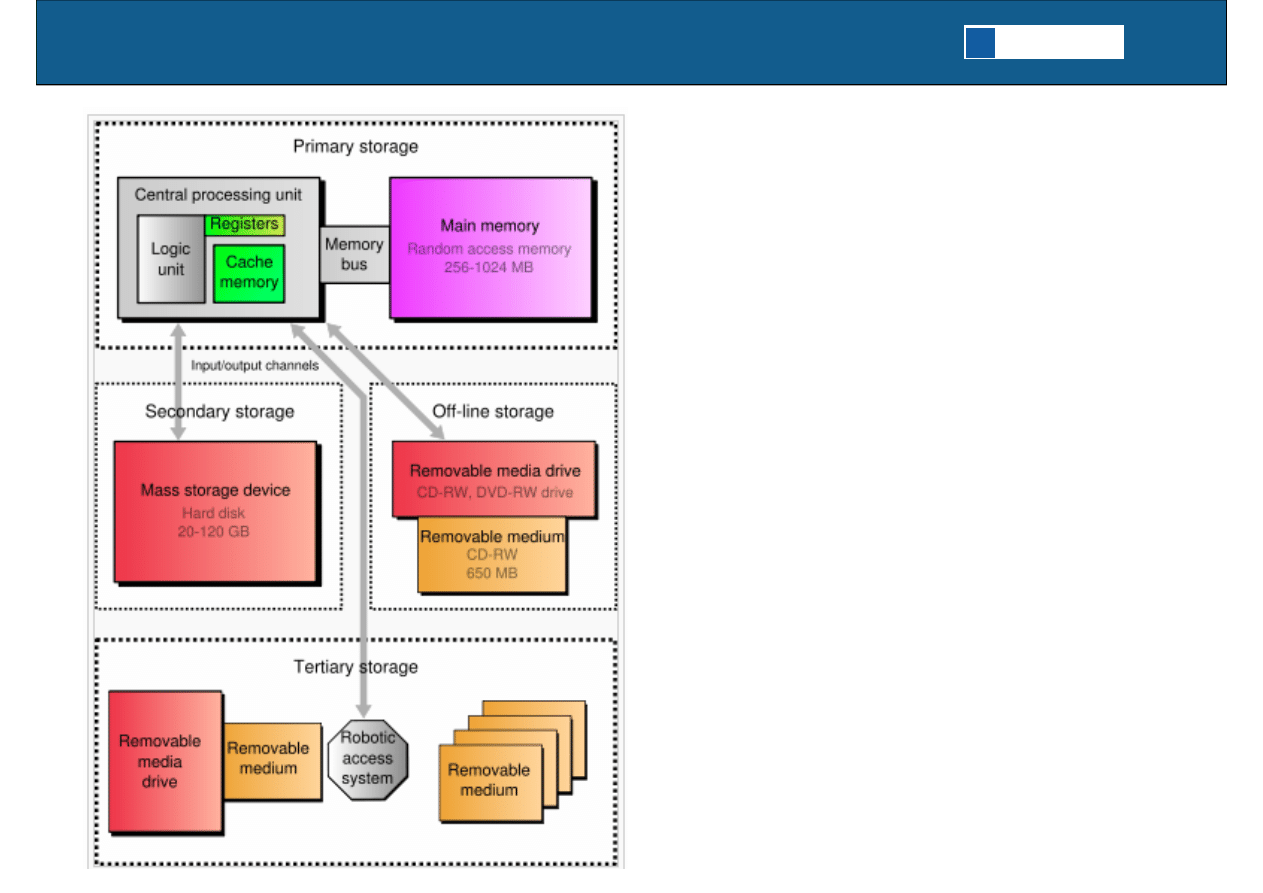

Hierarchia Pamięci

1. Rodzaje pamięci

4/30

1

2

3

4

5

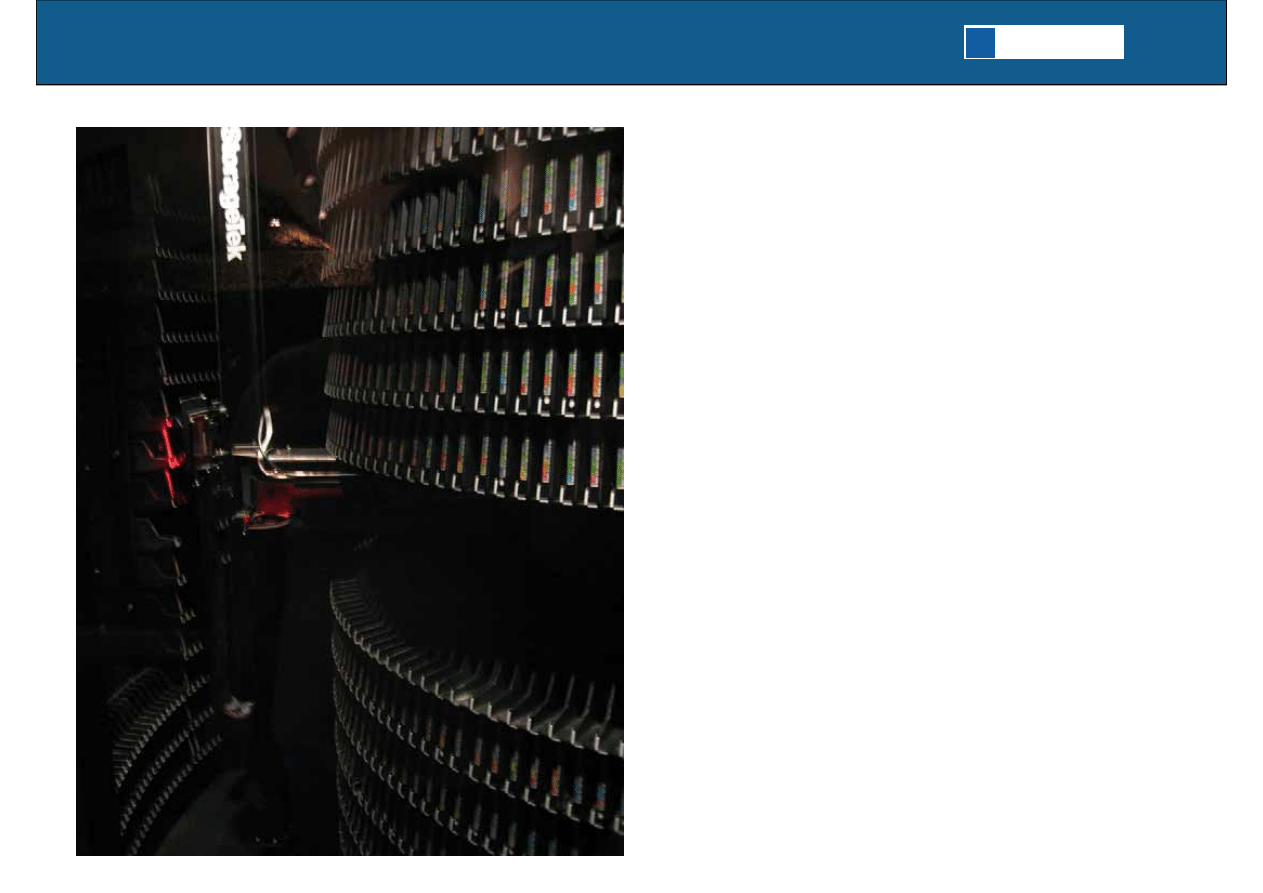

Pamięć trzeciego rzędu

2. S-RAM = Static RAM

5/30

1

2

3

4

5

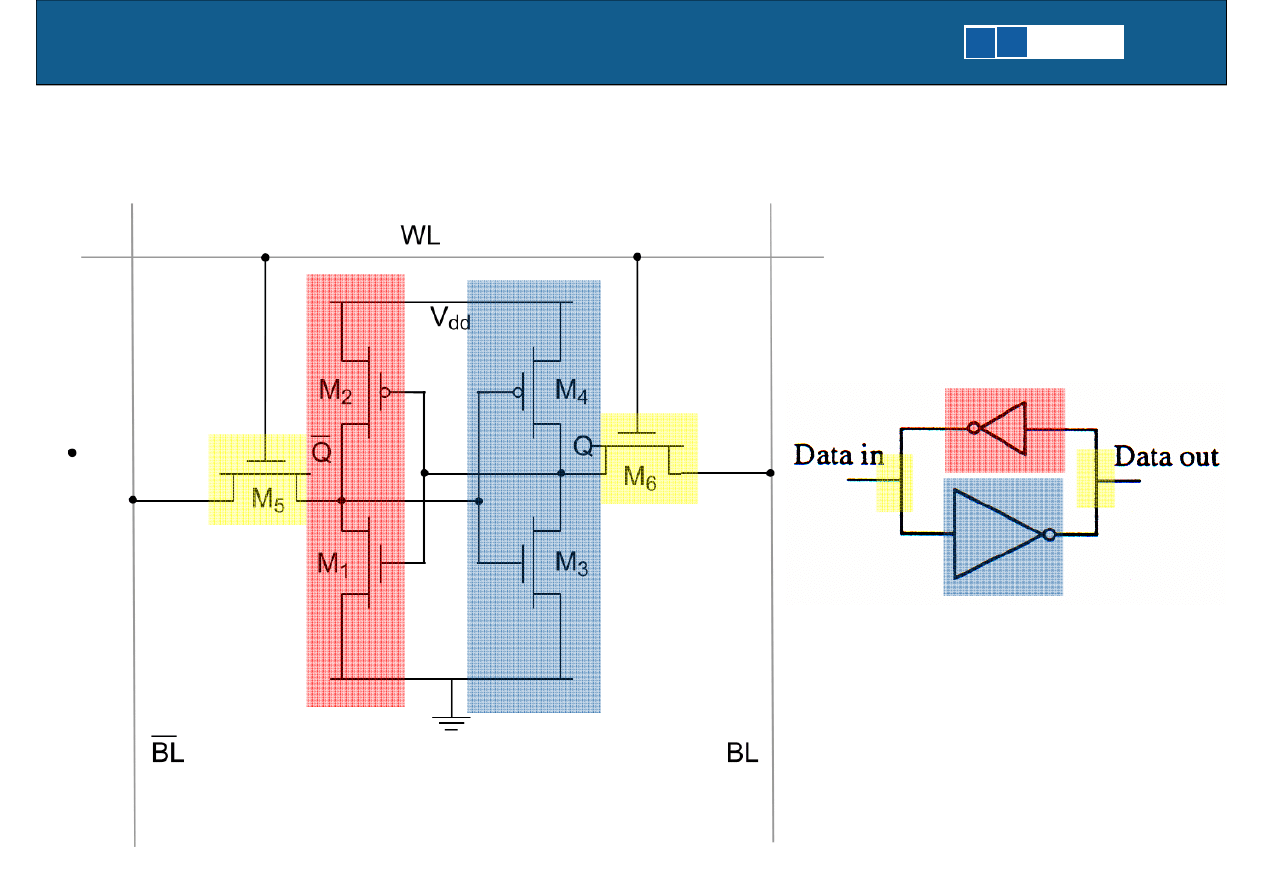

S-RAM od środka

2. S-RAM = Static RAM

6/30

1

2

3

4

5

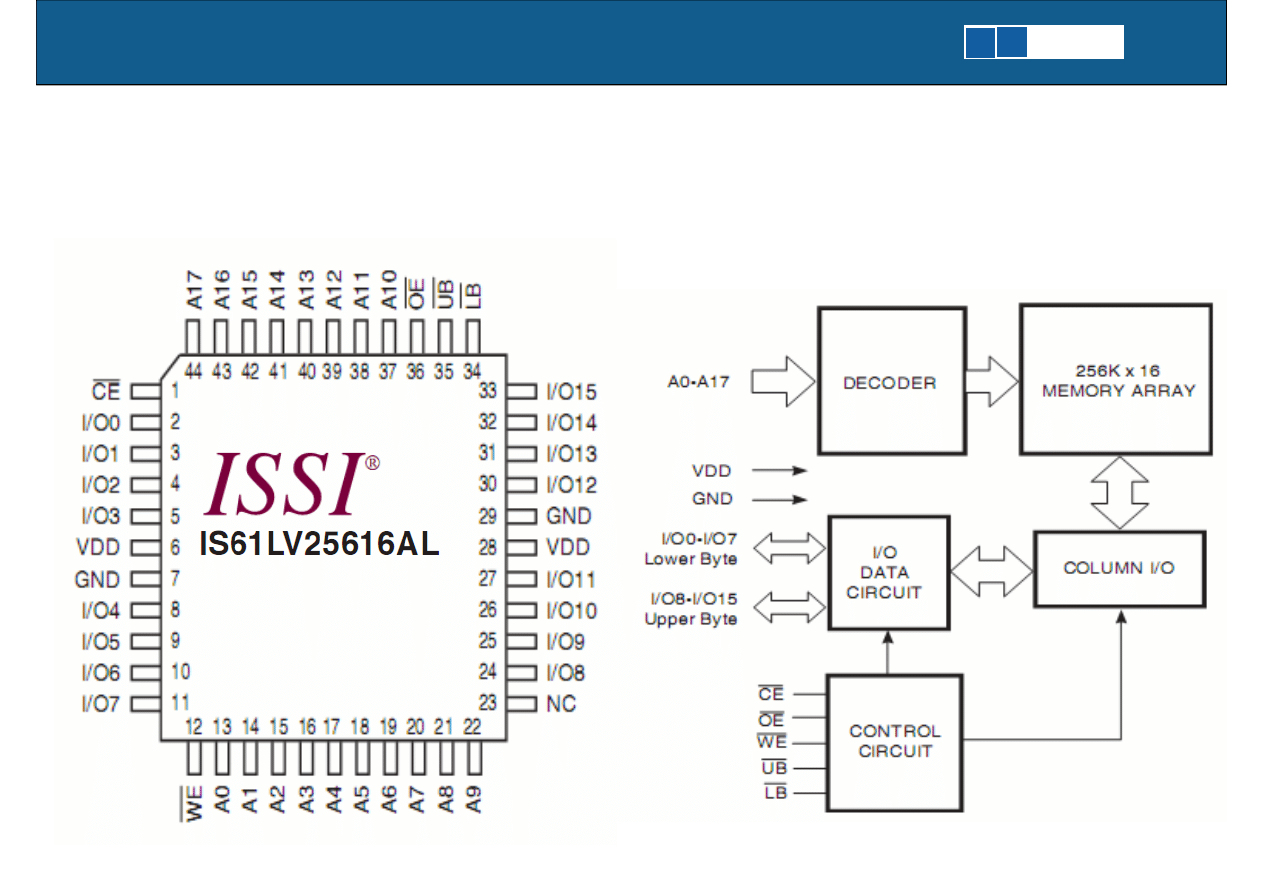

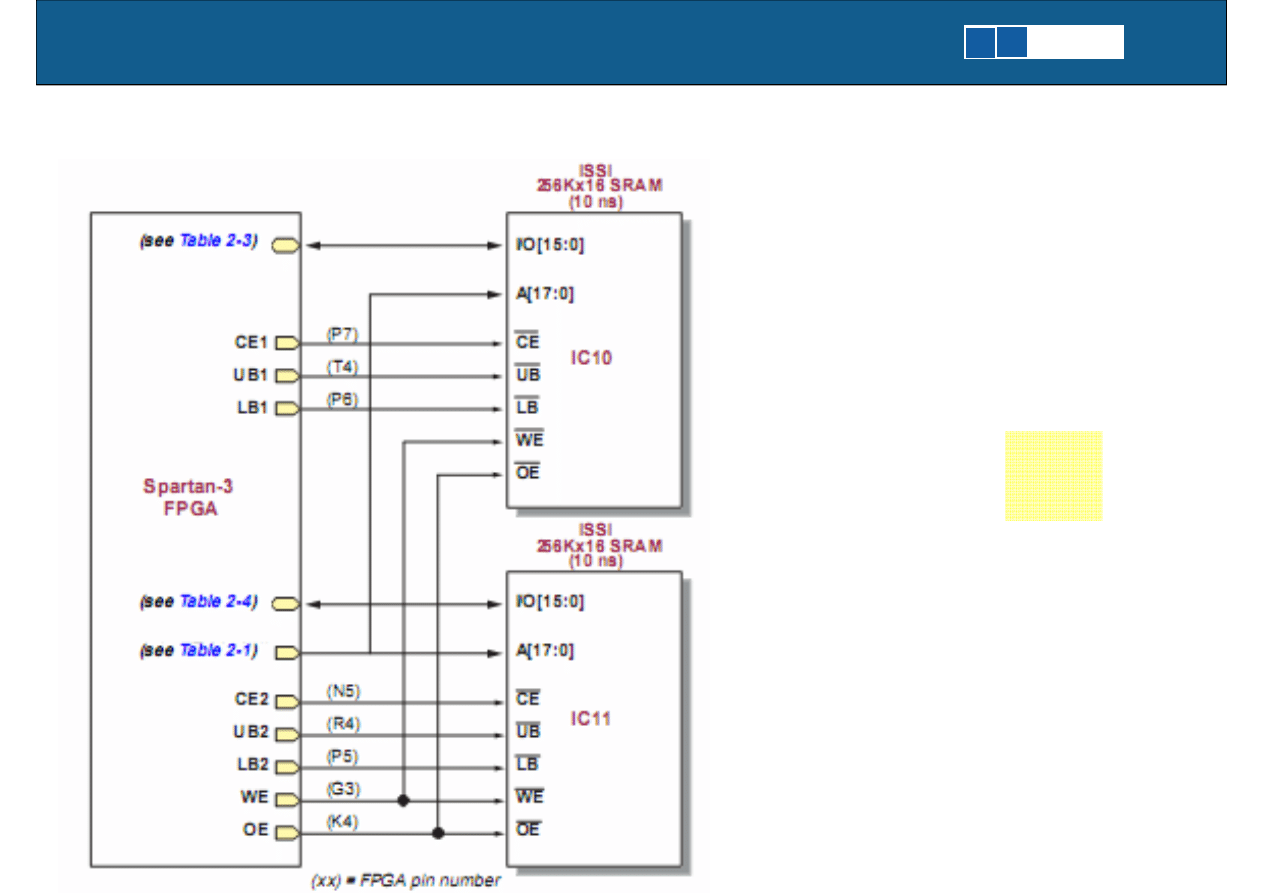

S-RAM, przykładowy układ

2. S-RAM = Static RAM

7/30

1

2

3

4

5

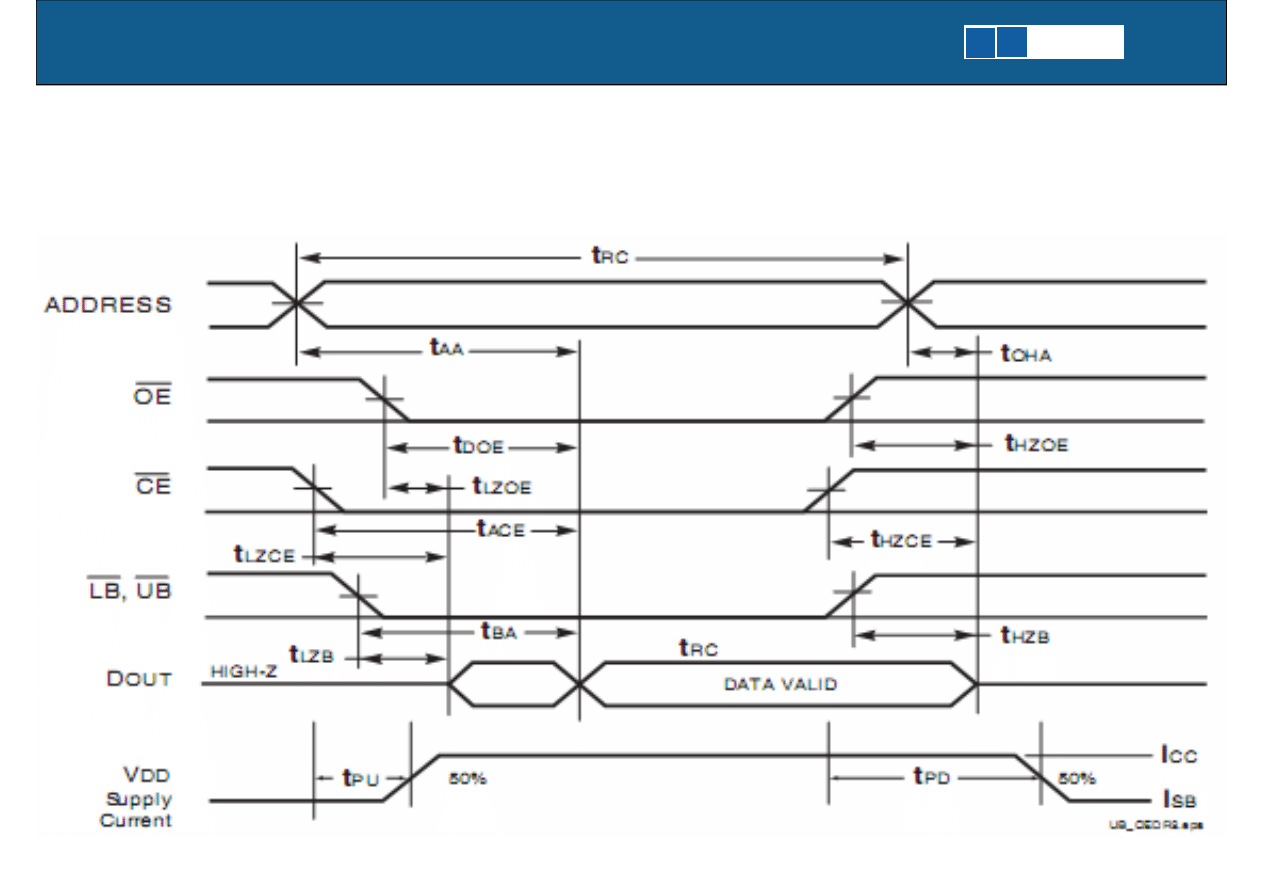

S-RAM, cykl odczytu

2. S-RAM = Static RAM

8/30

1

2

3

4

5

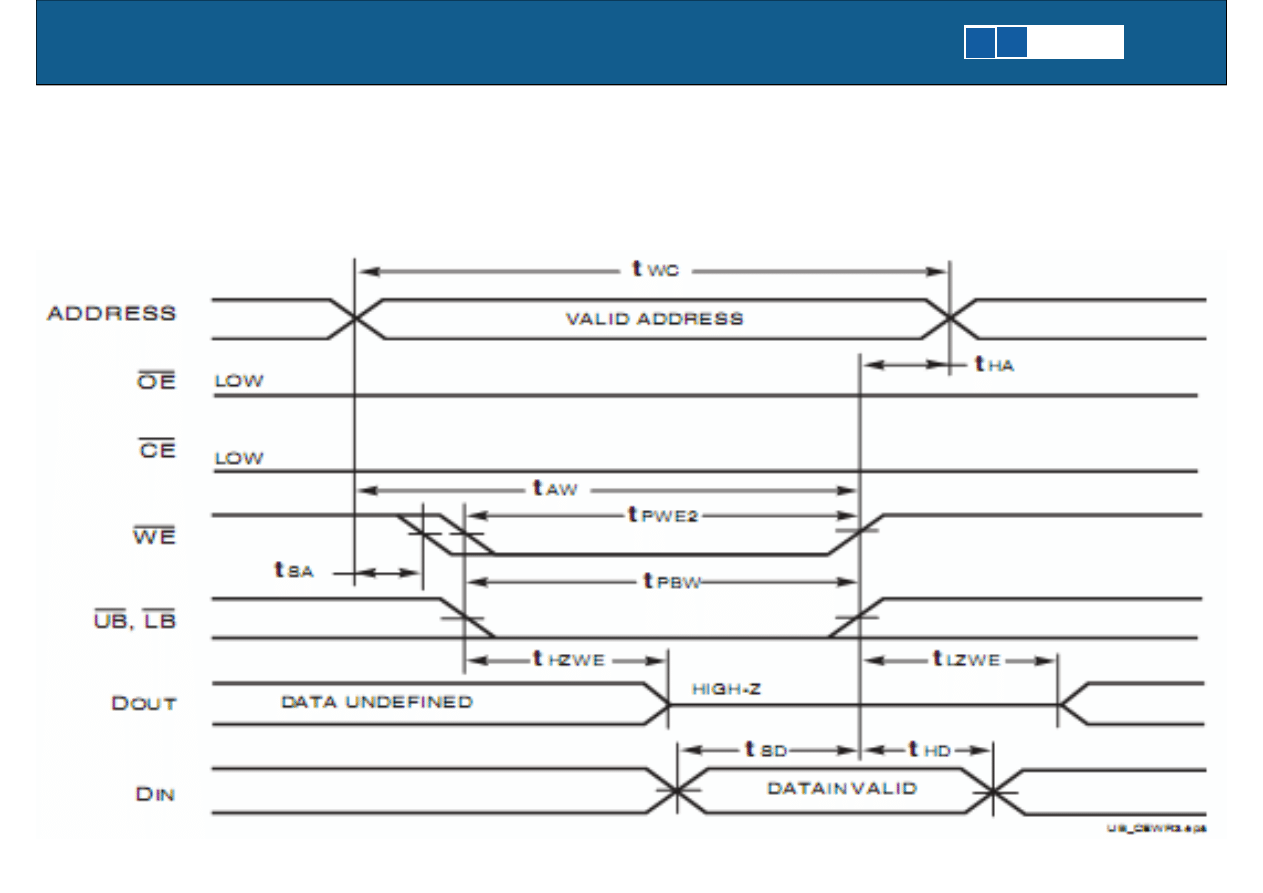

S-RAM, cykl zapisu

2. S-RAM = Static RAM

9/30

1

2

3

4

5

Obsługa pamięci S-RAM

Brak zegara taktującego pamięć

Brak konieczności odświeżania pamięci

Niskie zużycie mocy przy umiarkowanej

częstotliwości odwołań do pamięci

2. S-RAM = Static RAM

10/30

1

2

3

4

5

Parametry pamięci typu S-RAM

Pojemność : 262 144 x 16 bit (256K x 16 bit)

Czas cyklu odczytu (Read Cycle Time): 10 ns

Czas cyklu zapisu (Write Cycle Time): 10 ns

Zasilanie (Power Supply): 3.3V, stand-by 5mA, dynamic f = f

MAX

50mA

3. DRAM = Dynamic RAM

11/30

1

2

3

4

5

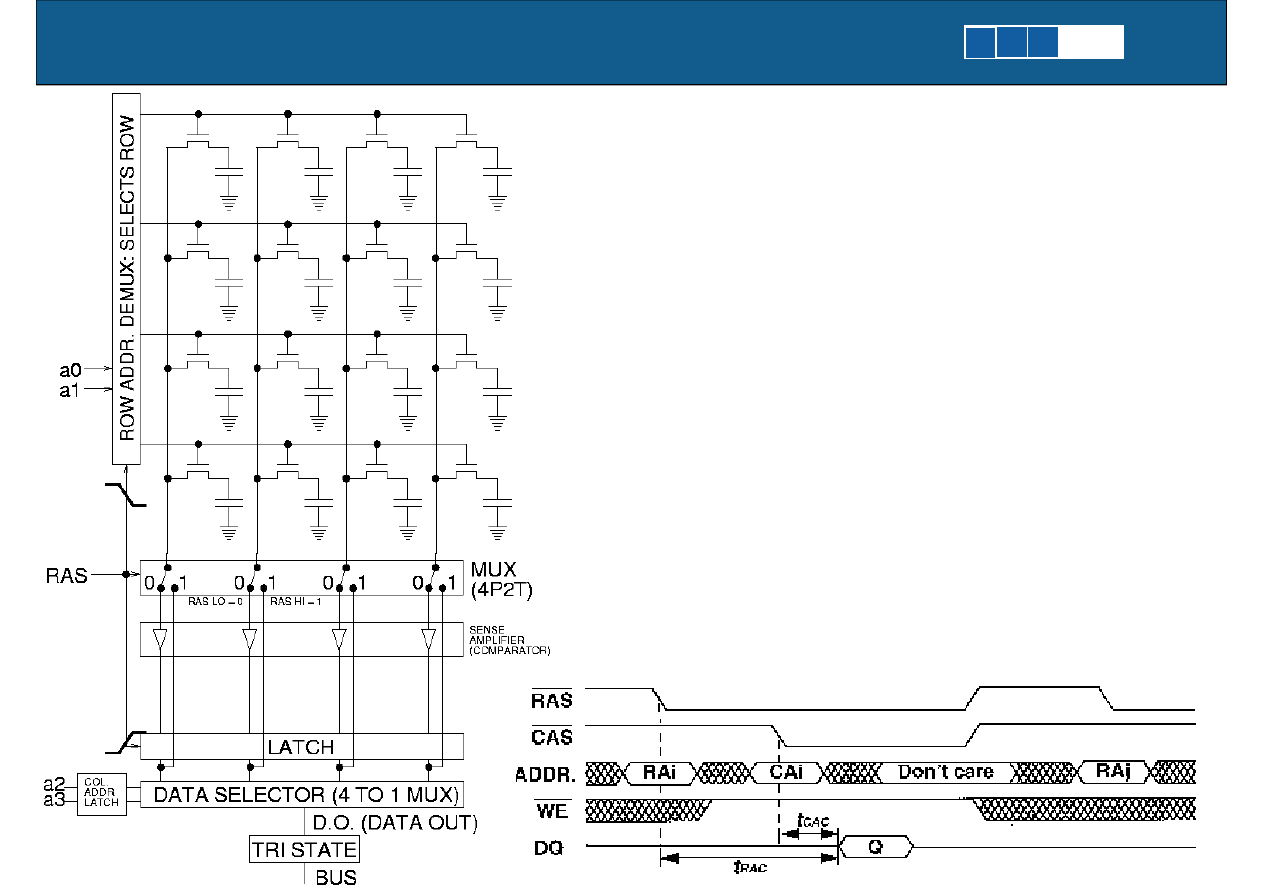

DRAM od środka, odczyt

1. Wiersz adresowanej komórki jest

aktywowany

2. Wybrany wiersz uaktywnia tranzystory,

podłączając kondensatory do linii

sygnałowych

3. Wzmacniacze linii sygnałowych

wzmacniają sygnał do poziomu 0 albo 1

4. Wyjścia z wzmacniaczy trafiają na

wyjście z pamięci

5. Wartości z linii sygnałowych ładują

kondensatory

3. DRAM = Dynamic RAM

12/30

1

2

3

4

5

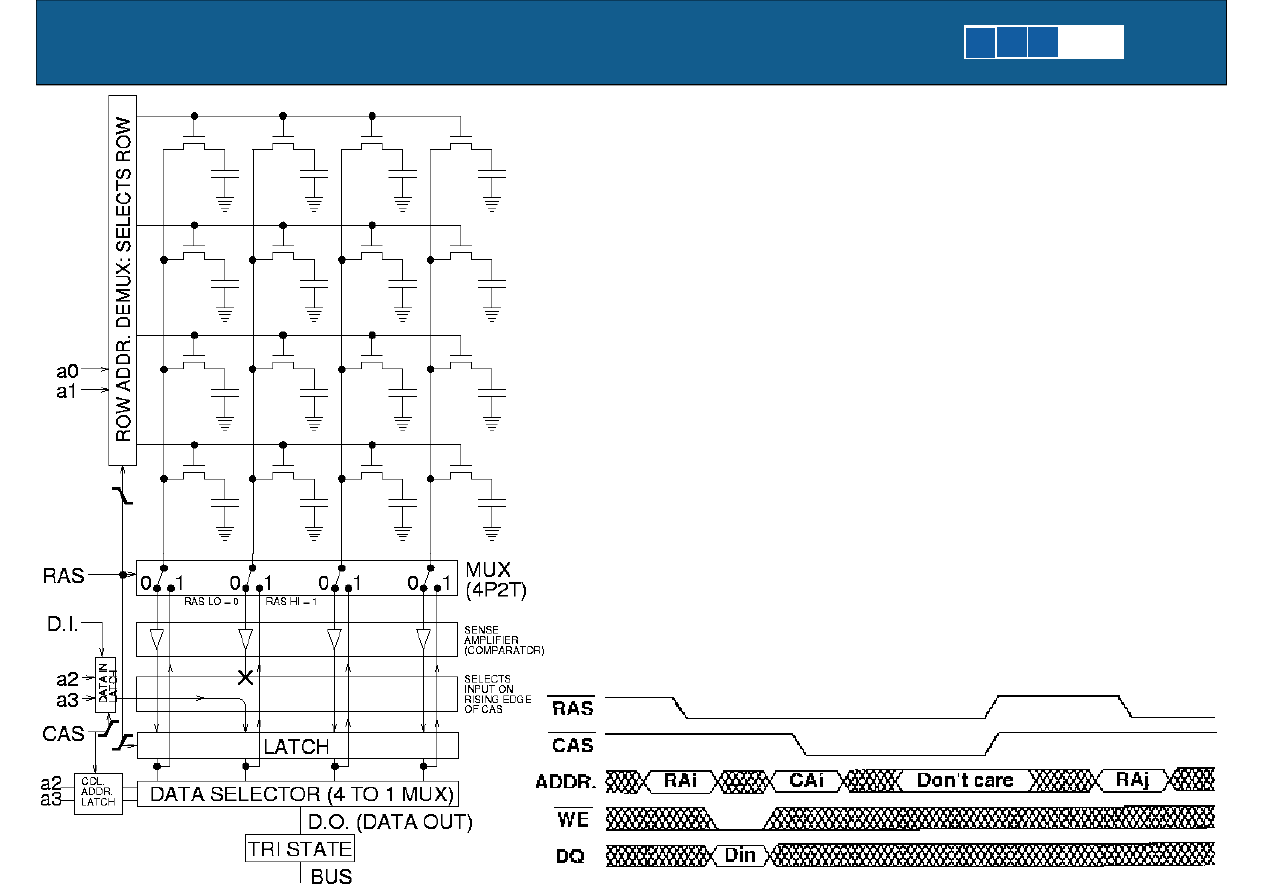

DRAM od środka, zapis

1. Wiersz adresowanej komórki jest

aktywowany

2. Wybrany wiersz uaktywnia tranzystory,

podłączając kondensatory do linii

sygnałowych

3. Wzmacniacze linii sygnałowych

wzmacniają sygnał do poziomu 0 albo 1

4. Dane wejściowe podłączane są do

odpowiednich linii sygnałowych

5. Wartości z linii sygnałowych ładują

kondensatory

3. DRAM = Dynamic RAM

13/30

1

2

3

4

5

http://www.cs.berkeley.edu/~pattrsn/294/LEC9/lec.html

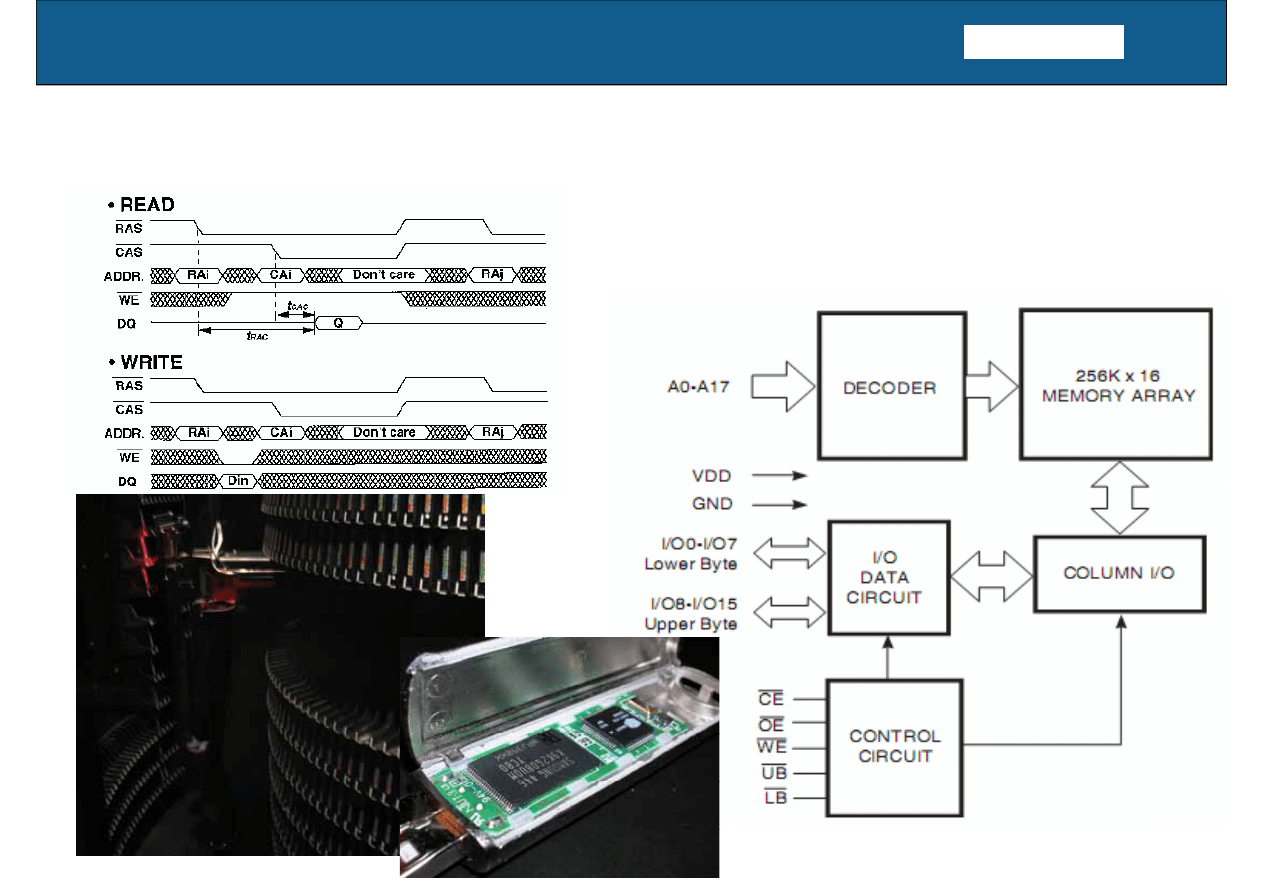

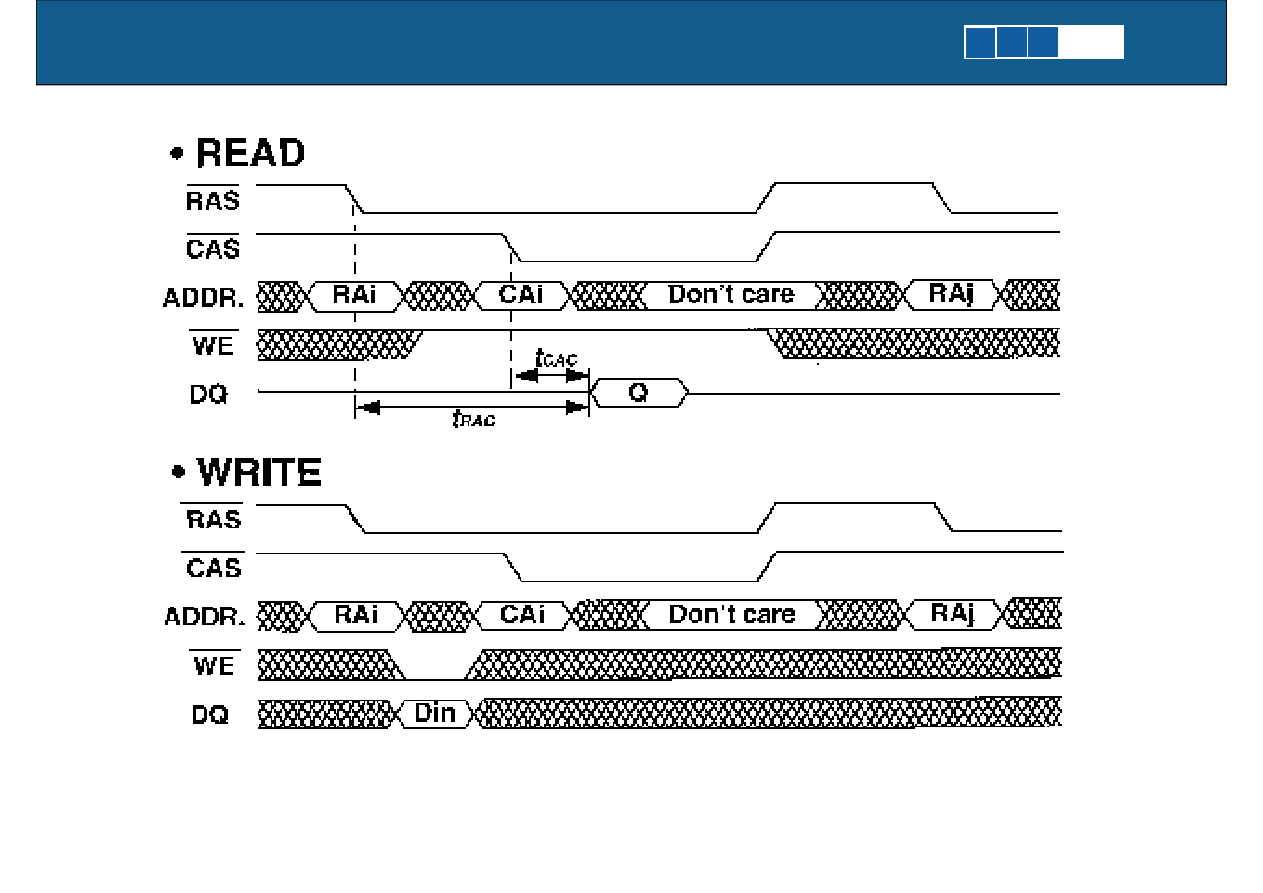

DRAM, cykl odczytu i zapisu

RAS – Row Access Strobe

CAS – Column Access Strobe

3. DRAM = Dynamic RAM

14/30

1

2

3

4

5

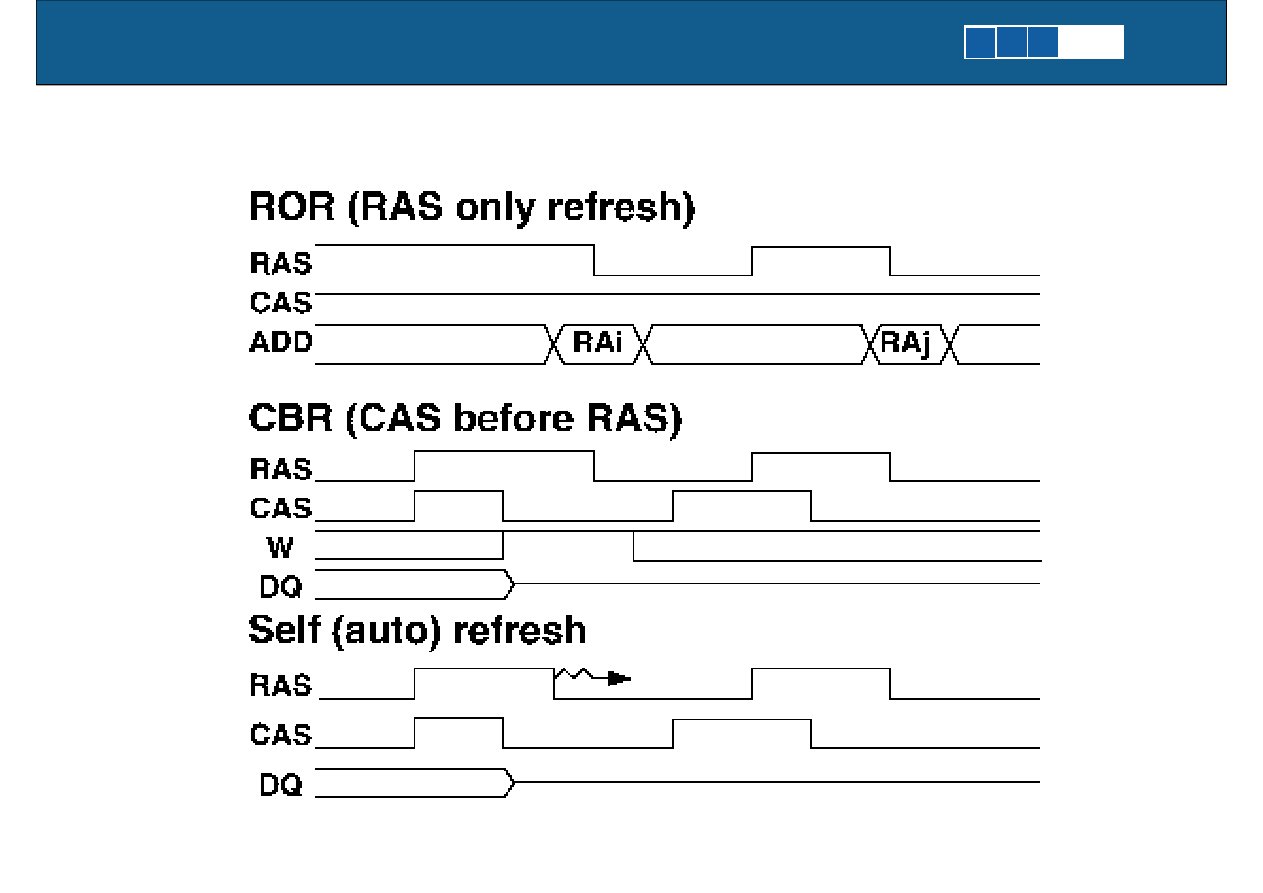

DRAM, odświeżanie

http://www.cs.berkeley.edu/~pattrsn/294/LEC9/lec.html

3. DRAM = Dynamic RAM

15/30

1

2

3

4

5

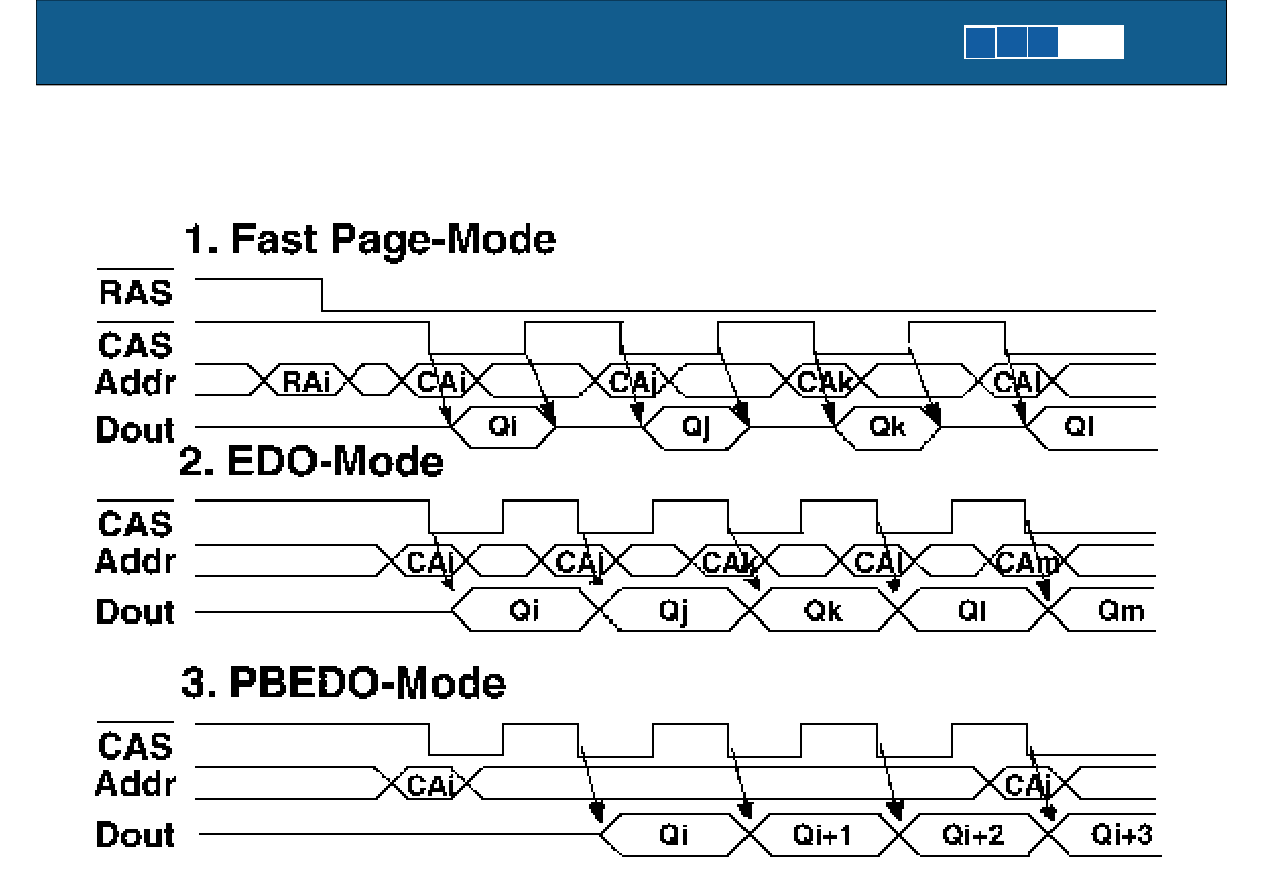

EDO DRAM – Extended Data Out

PBDRAM – Pipeline Burst EDO

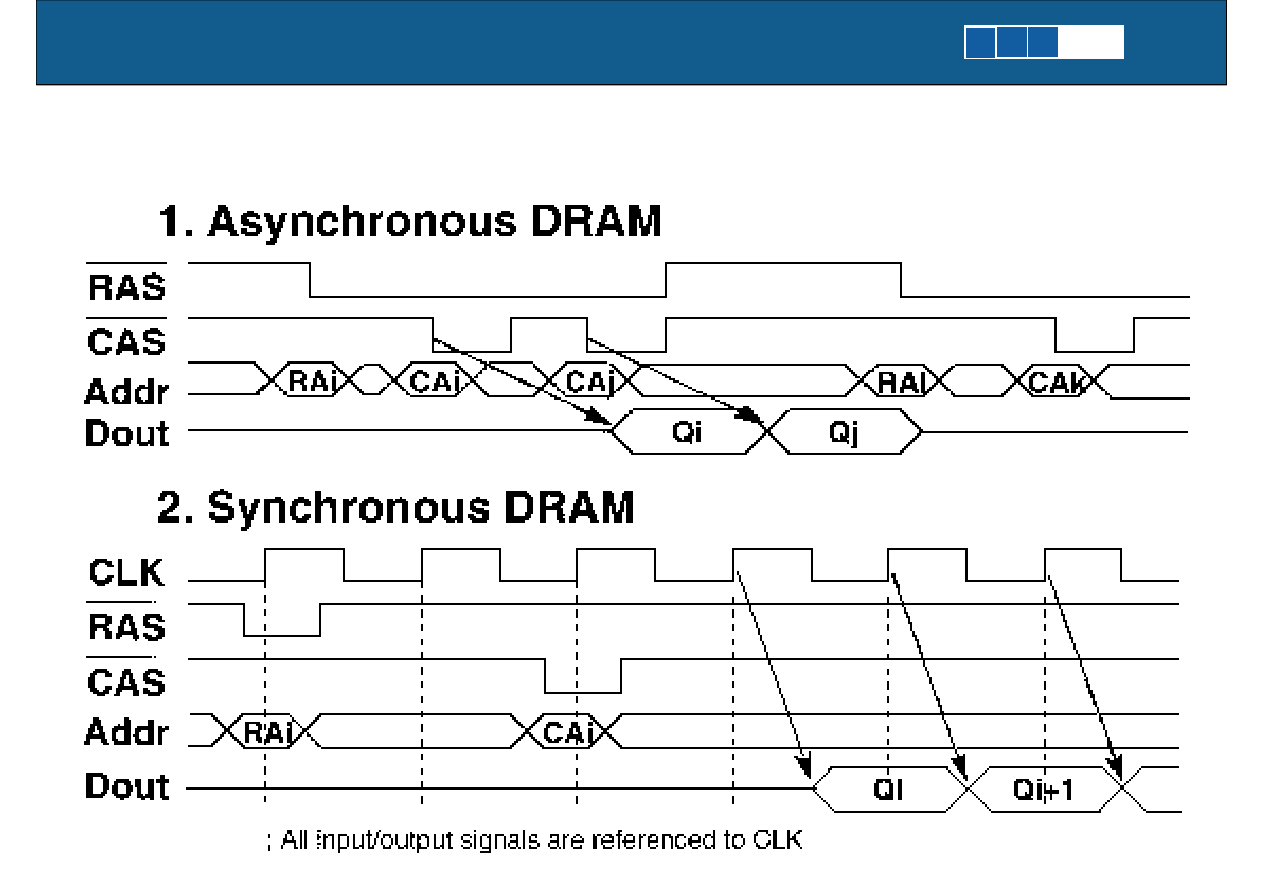

Asynchroniczne DRAM

3. DRAM = Dynamic RAM

16/30

1

2

3

4

5

Asynchroniczne/Synchroniczne DRAM

17/30

1

2

3

4

5

4. SDRAM – Synchronous DRAM

SDRAM

SDR SDRAM – Single Data Rate SDRAM – transmisja jednej danej na cykl

zegara. Typowe częstotliwości pomiędzy 66MHz a 133 MHz. Obudowa

najczęściej 168-pin DIMM.

DDR SDRAM – Double Data Rate SDRAM – transmisja danej na zboczu

rosnącym i opadającym zegara (dwie wartości na cykl zegara). Typowe

częstotliwości to 133MHz, 166 MHz oraz 200 MHz (DDR-266, DDR-333,

DDR-400). Obudowa najczęściej 184-pin DIMM (PC2100, PC2700,

PC3200).

DDR2 SDRAM – Szyna do pamięci pracuje na dwa razy większej

częstotliwości niż pamięć. Typowe częstotliwości to 200MHz, 333 MHz

oraz 400 MHz (DDR2-400, DDR2-667, DDR-800). Obudowa najczęściej

240-pin DIMM (PC2-3200, PC2-6400).

DDR3 SDRAM – Szyna do pamięci pracuje na cztery razy większej

częstotliwości niż pamięć. Typowe częstotliwości to 400MHz do 800 MHz

(DDR3-800, DDR3-1600).

18/30

1

2

3

4

5

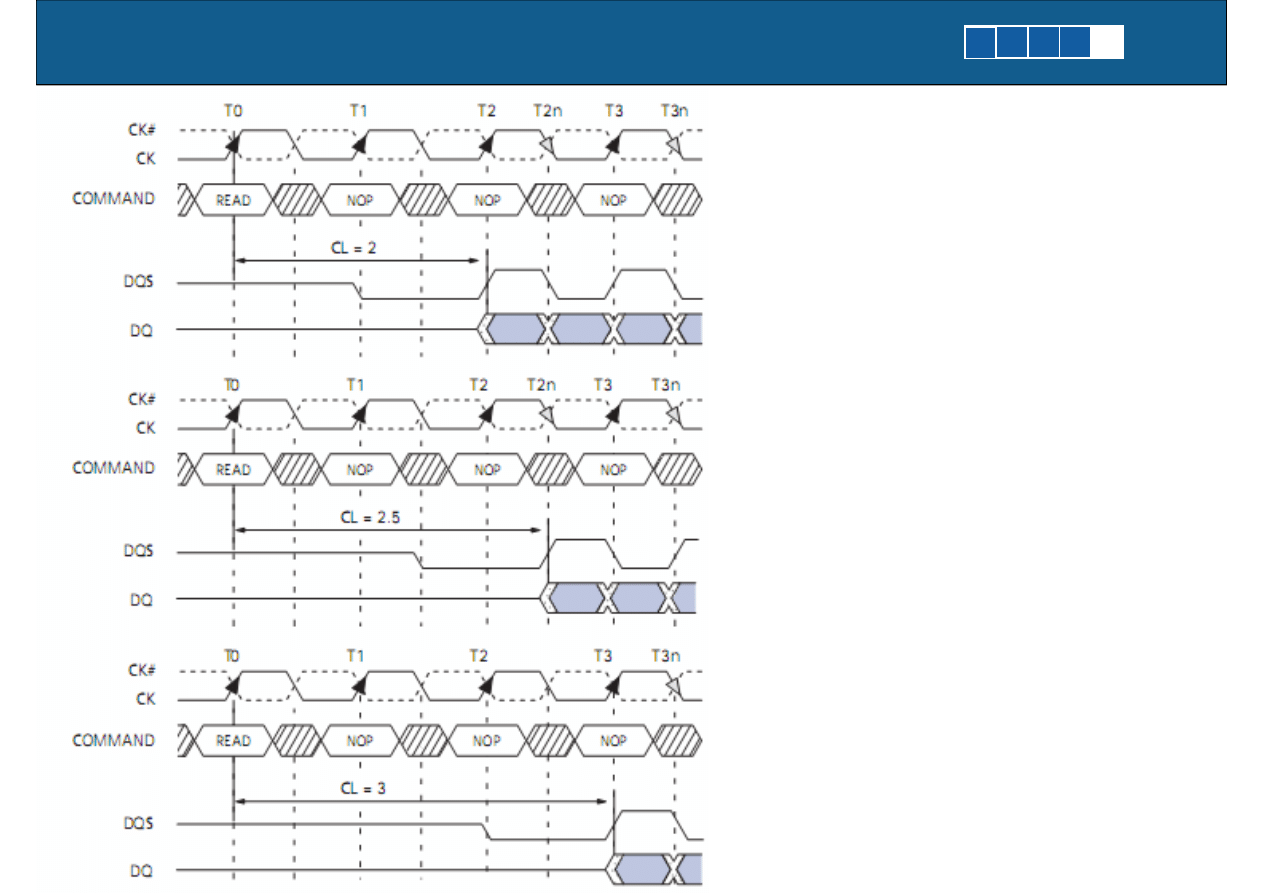

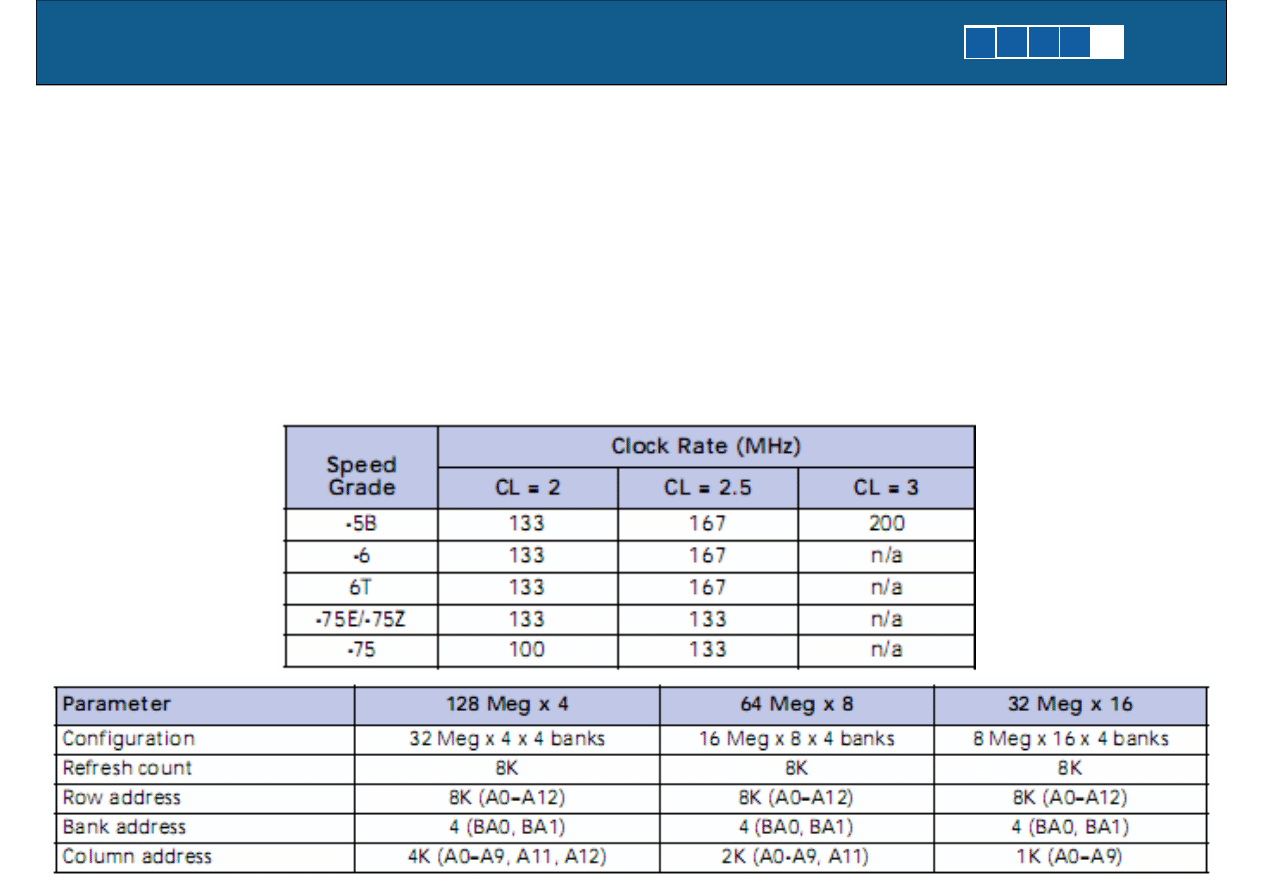

4. SDRAM – Synchronous DRAM

CL = CAS Latency

19/30

1

2

3

4

5

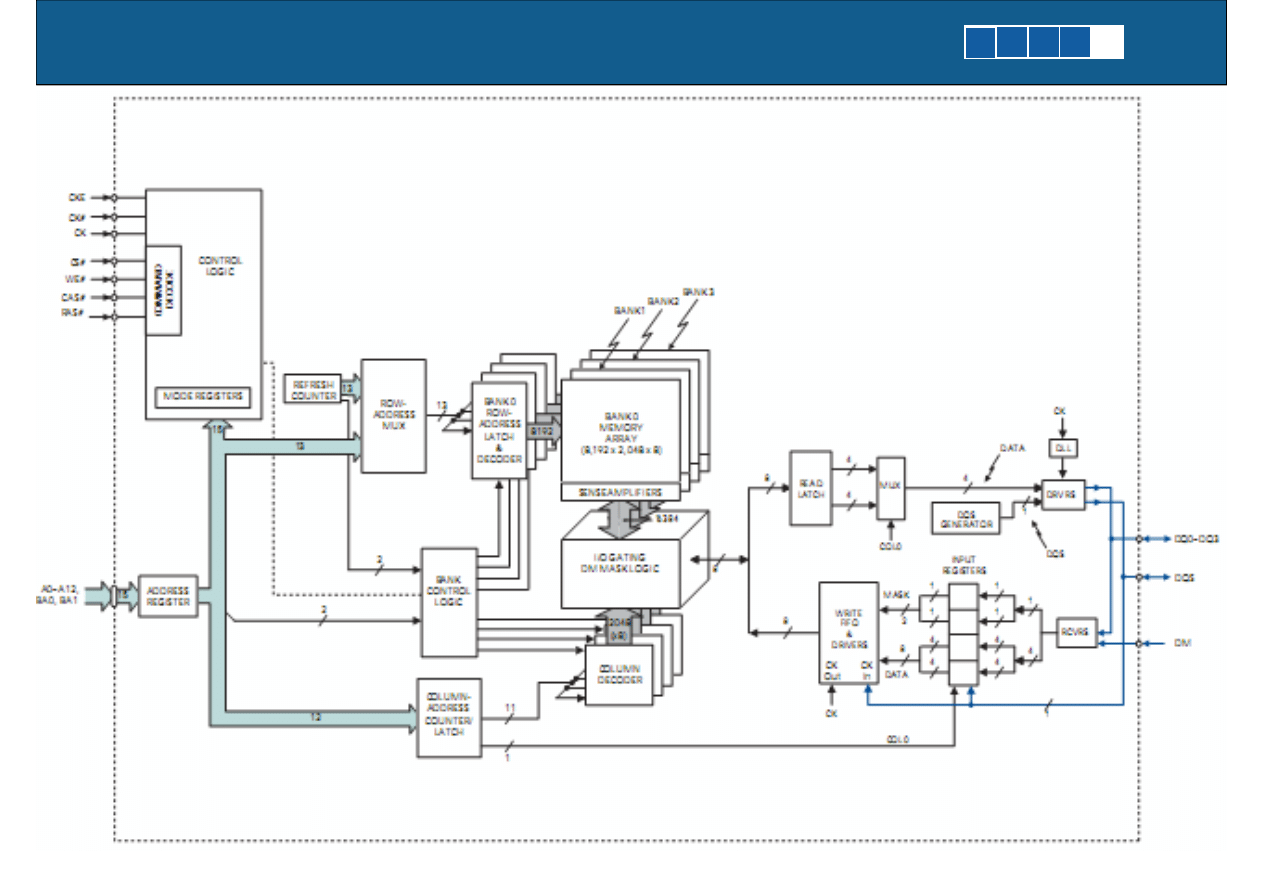

4. SDRAM – Synchronous DRAM

Micron MT46V128M4

Micron, DDR SDRAM MT46V128M

20/30

1

2

3

4

5

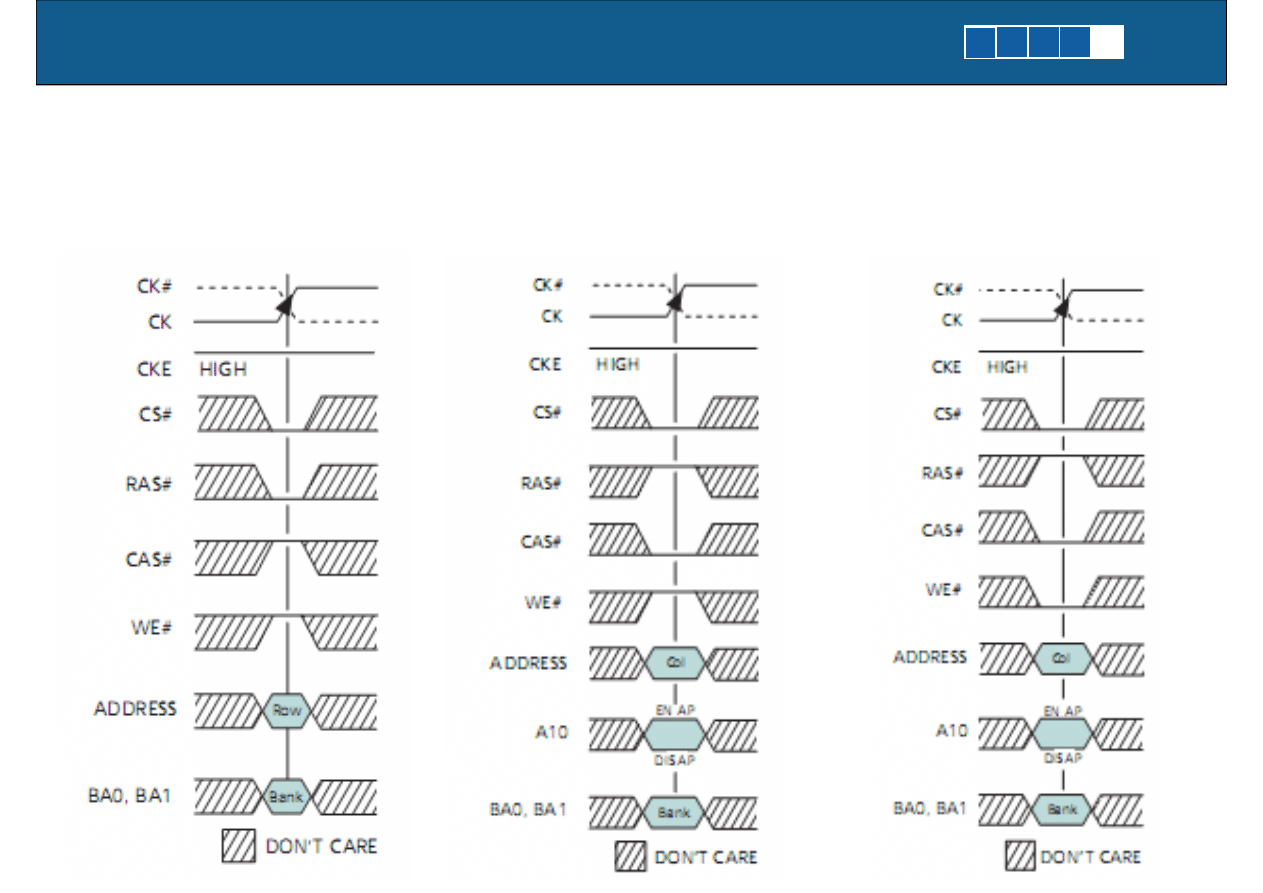

4. SDRAM – Synchronous DRAM

Aktywacja konkretnego

wiersza w konkretnym

banku

Komenda odczytu

Komenda zapisu

Komendy do pamięci

21/30

1

2

3

4

5

4. SDRAM – Synchronous DRAM

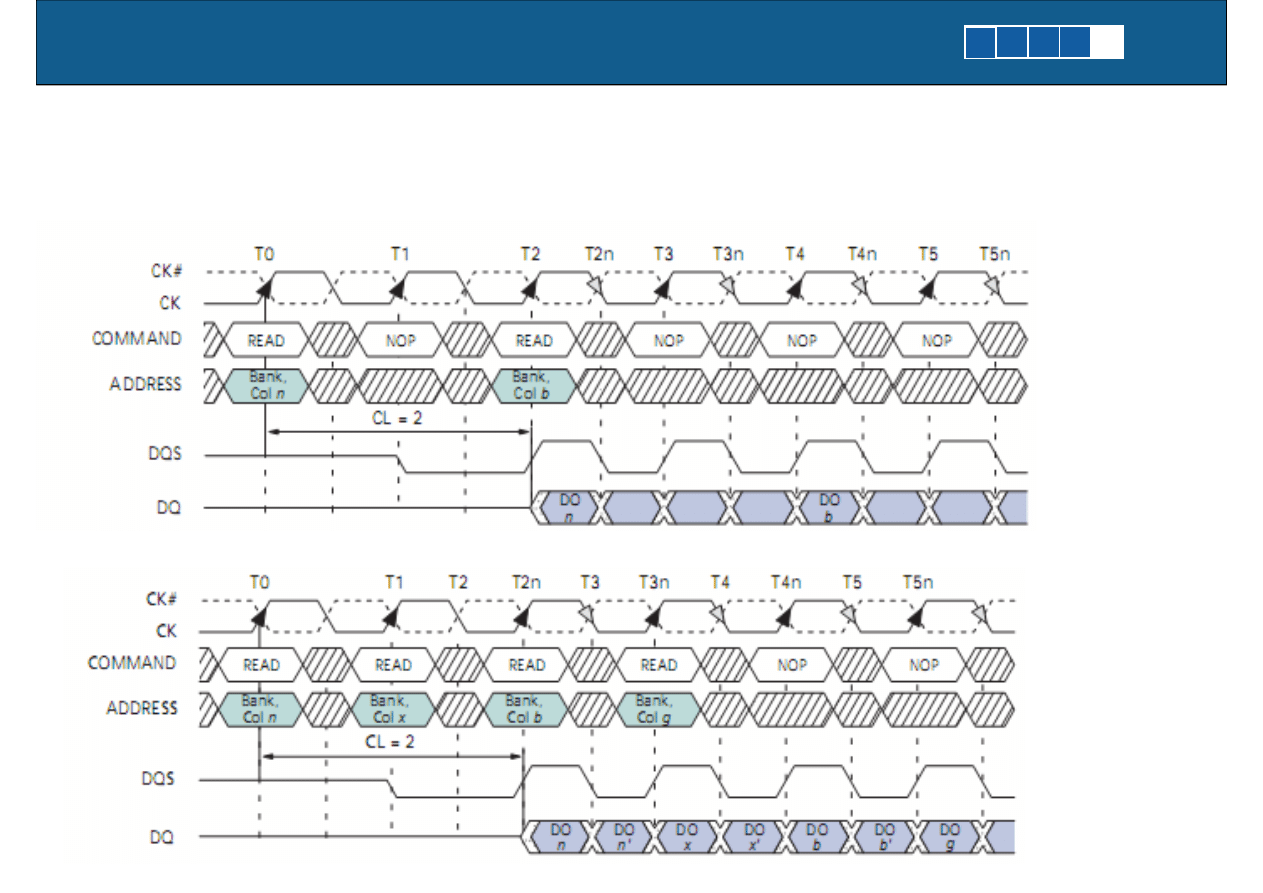

Odczyt w trybie BURST

Odczyt pamięci

22/30

1

2

3

4

5

4. SDRAM – Synchronous DRAM

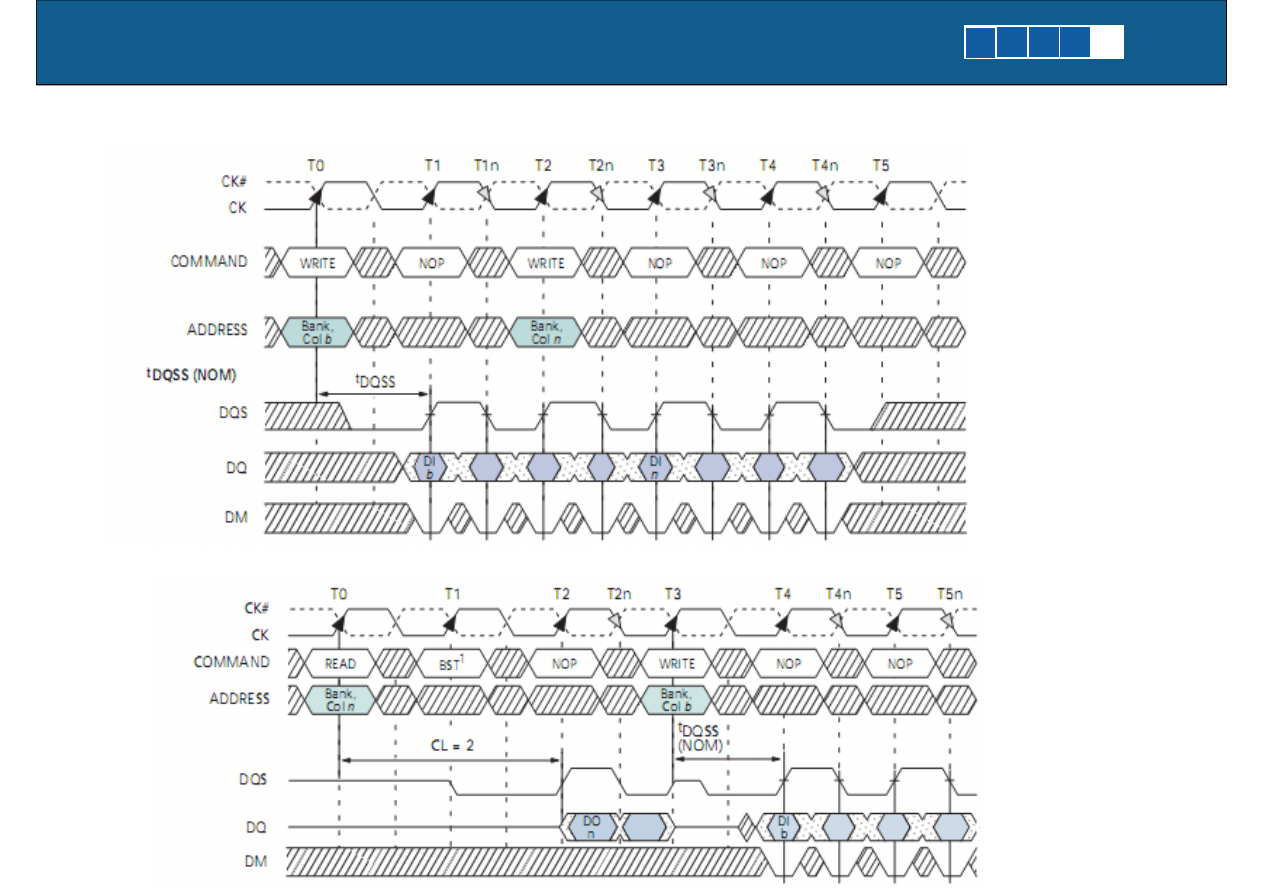

Zapis w trybie BURST

Przejście od trybu odczytu do trybu zapisu

Zapis pamięci

23/30

1

2

3

4

5

4. SDRAM – Synchronous DRAM

Parametry pamięci DDR SDRAM

Pojemność : 262 144 x 16 bit (256K x 16 bit)

Częstotliwość pracy (Read Cycle Time): 10 ns

CL (CAS Latency): 10 ns

Zasilanie (Power Supply): 3.3V, stand-by 5mA, dynamic f = f

MAX

50mA

24/30

1

2

3

4

5

4. SDRAM – Synchronous DRAM

Parametry pamięci SDRAM x-x-x-x

tCAS – tRCD – tRP – tRAS

np. 2-2-2-6 lub 2.5-3-3-8

tCAS = CL

tRCD – DRAM RAS# to CAS# delay – liczba cykli zegara pomiędzy

sygnałem RAS a CAS.

tRP – DRAM RAS# Precharge – liczba cykli zegara do zamknięcia

aktywnego wiersza pamięci i uaktywnienia innego wiersza.

tRAS – Precharge delay – min tRAS = tRCD + tCAS + 2

5. Pamięć nieulotna – PROM/EPROM/FLASH

25/30

1

2

3

4

5

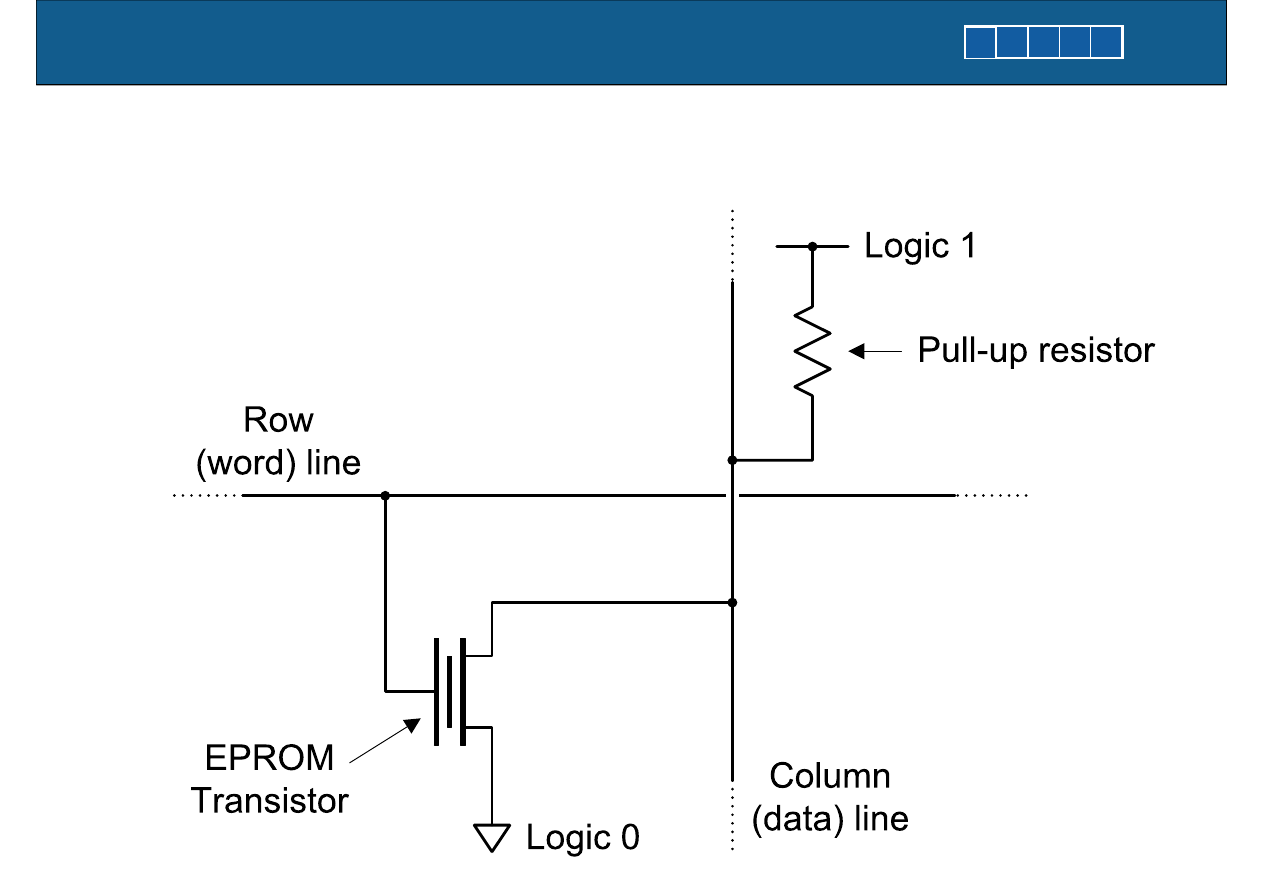

Pamięć nieulotna EPROM

5. Pamięć nieulotna – PROM/EPROM/FLASH

26/30

1

2

3

4

5

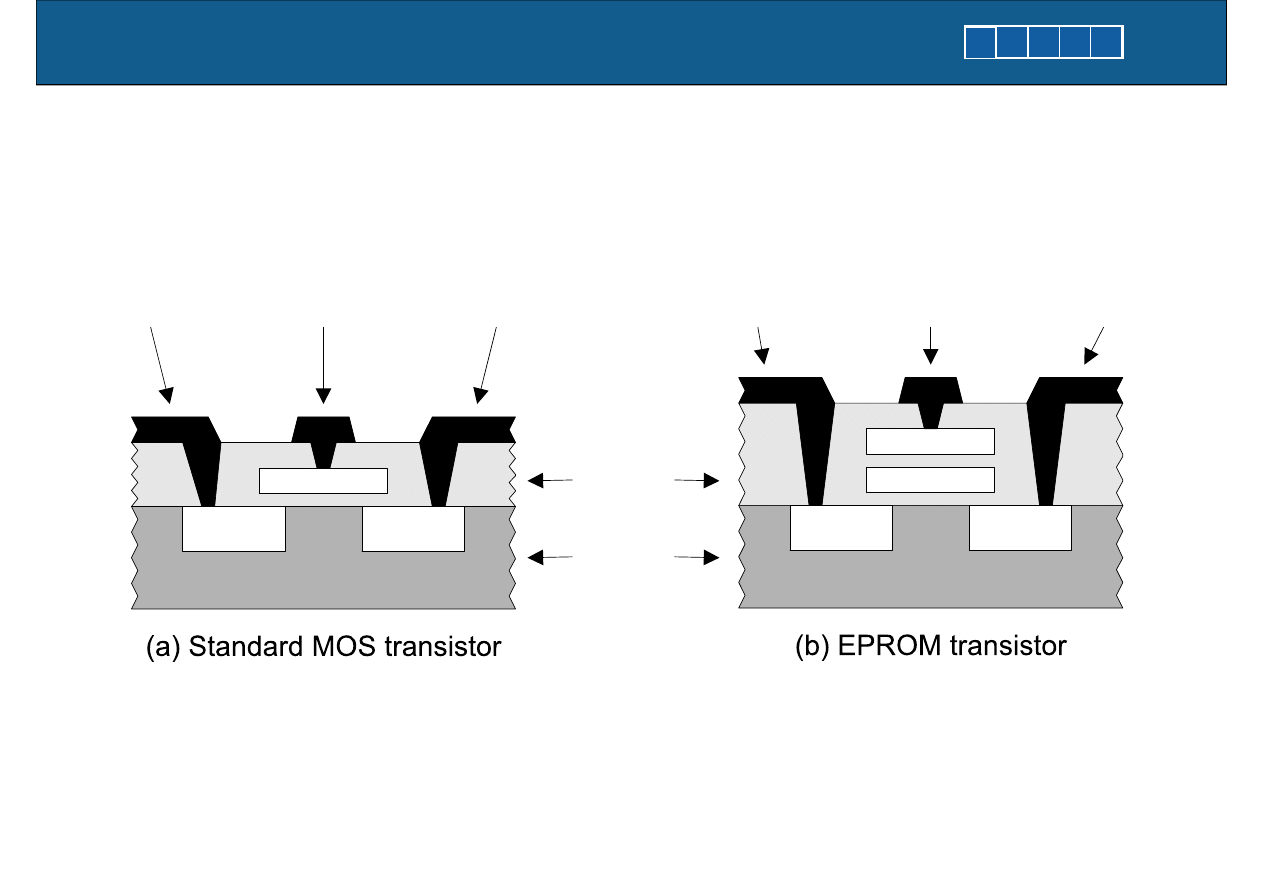

control gate

source

drain

control gate

floating gate

source

drain

Silicon

substrate

Silicon

dioxide

Source

terminal

Control gate

terminal

Drain

terminal

Source

terminal

Control gate

terminal

Drain

terminal

Pamięć nieulotna EEPROM

5. Pamięć nieulotna – PROM/EPROM/FLASH

27/30

1

2

3

4

5

Pamięć nieulotna FLASH

5. Pamięć nieulotna – PROM/EPROM/FLASH

28/30

1

2

3

4

5

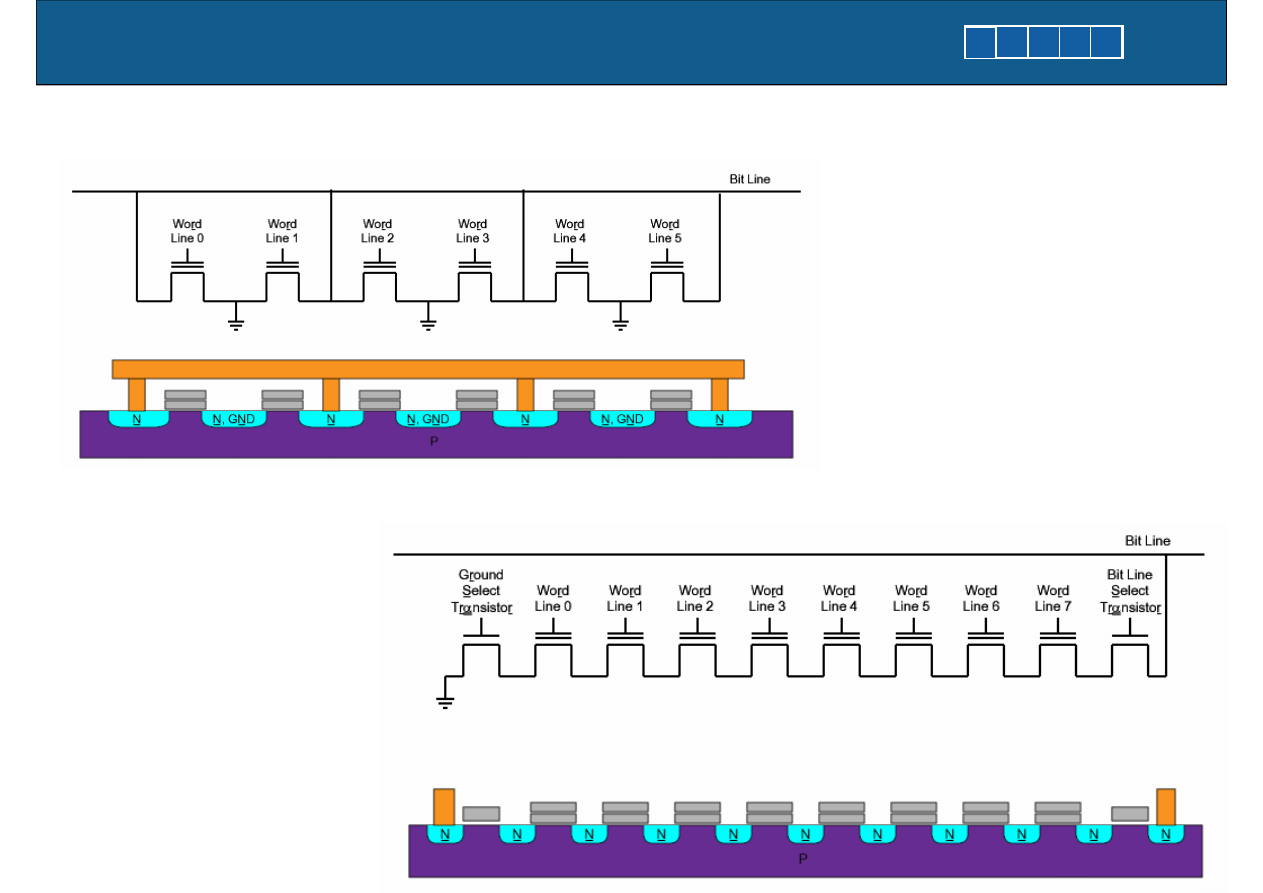

NOR FLASH

NAND FLASH

Pamięć nieulotna FLASH

● Zazwyczaj niewielkie rozmiary

pamięci

● Najczęściej do przechowywania

kodu w syst. wbudowanych

● RAM

● Szybki odczyt pamięci (wolny

zapis)

● Wysoka niezawodność

● Wysoka pojemność

● Najczęściej w zastępstwie dysków

magnetycznych/optycznych

● Dostęp sekwencyjny

● Szybszy niż w NOR Flash zapis i

kasowanie pamięci

● Duża liczba cykli kasowania-

zapisania

● Niska cena

Pamięć systemu komputerowego

29/30

Polecana literatura

1) K. Kaspersky, Optymalizacja kodu, Efektywne wykorzystanie pamięci, RM 2003

Rozdział 2,3

2) W. Stallings, Organizacja i architektura systemu komputerowego, WNT 2003

Rozdział 4

3) P. Metzger, Anatomia PC, Helion 2001

Rozdział 3

Pamięć systemu komputerowego

30/30

KONIEC

dr inż. Mariusz Kapruziak

mkapruziak@wi.ps.pl

pok. 107, tel. 449 55 44

Wyszukiwarka

Podobne podstrony:

ASK 08 PiotrGębala MateuszMacięga

ASK 08 Bacula

ASK 08 Bacula

FP w 08

08 Elektrownie jądrowe obiegi

archkomp 08

02a URAZY CZASZKOWO MÓZGOWE OGÓLNIE 2008 11 08

ankieta 07 08

08 Kości cz Iid 7262 ppt

08 Stany nieustalone w obwodach RLCid 7512 ppt

2009 04 08 POZ 06id 26791 ppt

08 BIOCHEMIA mechanizmy adaptac mikroor ANG 2id 7389 ppt

depresja 08 09

W15 08 II

więcej podobnych podstron