1.Rodzaje bramek – opis i symbole, realizacja funkcji(wejścia, wyjścia).

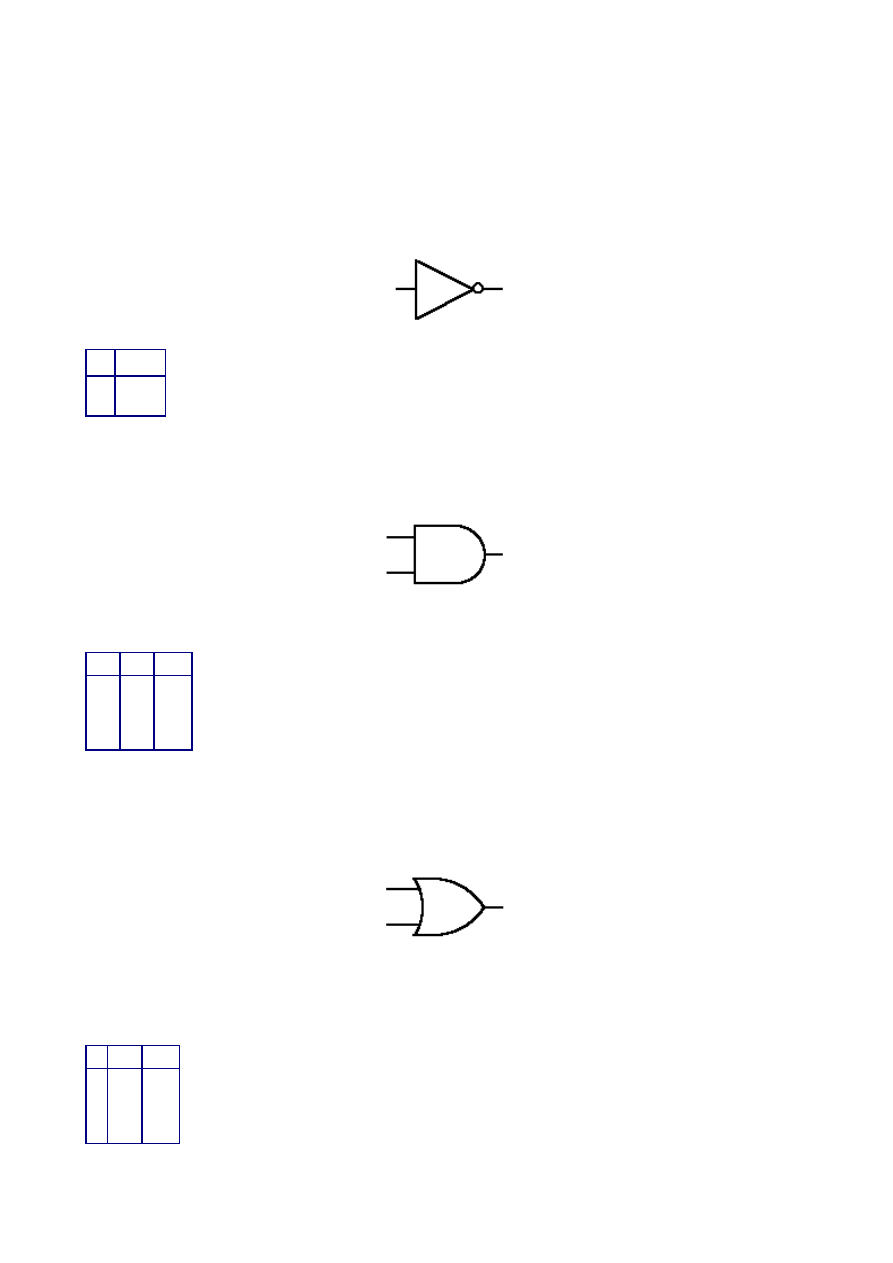

Bramka realizuje funkcje logiczną: NOT, NIE – negacja.

Bramka ma tylko jedno wejście. Neguje, czyli zmienia sygnał wejściowy na przeciwny.

Jest to najprostsza bramka. Gdy na wejściu ustawimy sygnał "1" to na wyjściu otrzymamy "0", a

gdy na wejściu ustawimy "0" to na wyjściu pojawi się "1". Bramka ta zawsze ma tylko jedno

wejście i wyjście.

Tablica prawdy:

IN OUT

0

1

1

0

Bramka realizuje funkcje logiczną: AND, I - iloczyn

Jeśli na wszystkich wejściach bramki są podane "1" to na wyjściu jest "1". W spoczynku na wyjściu

jest "0".

Bramka ta posiada conajmniej dwa do ośmiu wejścia i tylko jedno wyjście.

Tablica prawdy:

IN 1 IN 2 OUT

0

0

1

1

0

1

0

1

0

0

0

1

Bramka realizuje funkcje logiczną: OR, LUB - suma

Jeśli na przynajmniej jednym wejściu bramki jest podana "1" to na wyjściu jest "1". W spoczynku

na wyjściu jest "0".

W przypadku tej bramki wystarczy aby choć na jednym z jej wejść pojawił się stan "1" i wtedy na

wyjściu również pojawi się "1".

Tablica prawdy:

IN IN 2 OUT

0

0

1

1

0

1

0

1

0

1

1

1

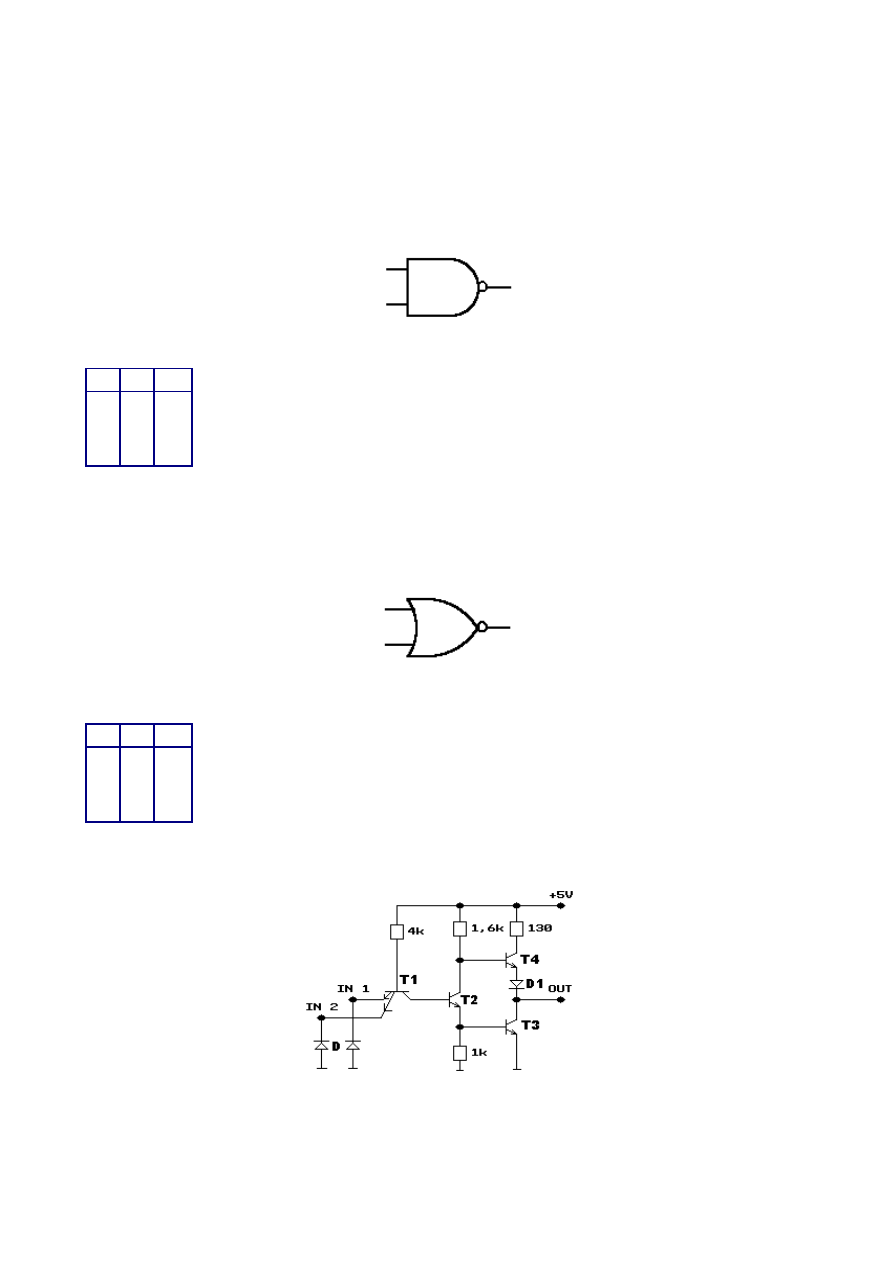

Bramka realizuje funkcje logiczną: NAND, NIE I - negacja iloczynu

Bramka jest złożona z bramki NOT i AND. Zasada działania jest taka sama jak bramki AND z tą

różnicą, że sygnał wyjściowy jest jeszcze negowany. Bramka ta stanowi SYSTEM

FUNKCJONALNIE PEŁNY, czyli za jej pomocą można przedstawić każdą złożoną funkcję

logiczną.

Jest to połączenie bramki AND z inwerterem. Zero logiczne "0" na wyjściu jest ustawiane tylko

wtedy gdy na obu wejściach jest jedynka logiczna "1". W pozostałych przypadkach na wyjściu

zawsze jest stan "1".

Tablica prawdy:

IN 1 IN 2 OUT

0

0

1

1

0

1

0

1

1

1

1

0

Bramka realizuje funkcje logiczną: NOR, NIE SUMA - negacja sumy

Bramka jest złożona z bramki NOT i OR. Zasada działania jest taka sama jak bramki OR z tą

różnicą, że sygnał wyjściowy jest jeszcze negowany. Bramka ta stanowi SYSTEM

FUNKCJONALNIE PEŁNY, czyli za jej pomocą można przedstawić każdą złożoną funkcję

logiczną.

Tablica prawdy:

IN 1 IN 2 OUT

0

0

1

1

0

1

0

1

1

0

0

2. Schemat ideowy bramki NAND – ukł. UCY 7400.

3. Opis działania bramki NAND w oparciu o ukł. UCY 7400.

Wszystkie tranzystory układu, z wyjątkiem T3, znajdują się w stanie nasycenia lub odcięcia,

zależnie od poziomów logicznych na wejściach (dla stanu statycznego). Tranzystor T2 działa jako

wtórnik emi-terowy (stan wysoki na wyjściu) lub inwerter (stan niski). Dioda D1 zapewnia odcięcie

tranzystora T3, gdy tranzystory T2 i T4 są w stanie nasycenia. Tranzy-story T3 i T4 tworzą układ

wyjściowy (ang. – totem pole), zapewniający małą impedancję wyjścio-wą zarówno przy poziomie

L, jak i H na wyjściu. Rezystor R3 ogranicza prąd wyjściowy w przy-padku zbyt dużego obciążenia

na poziomie H (np. przy zwarciu do masy) oraz w procesie przełą-czania. Diody ograniczające D2 i

D3 ułatwiają realizację dłuższych połączeń między układami, tłumiąc oscylacje powstające w

procesie przełączania bramki i zapobiegając powstawaniu ujemnego napię-cia większego niż

~0,7V.

4.Sposób postępowania z niewykorzystanymi wejściami bramki NAND.

Nie wykorzystane wejścia podłączamy w następujący sposób:

Nieużywane wejścia bramek AND, NAND i przerzutników należy dołączyć do szyny napięcia

zasilania Ucc przez rezystancję 15k. Przez jedną rezystancję 1k można dołączyć 1- 25 wolnych

wejść. Jeżeli można zagwarantować, że napięcie zasilania Ucc nie przekracza wartości 5,5 V, to

nieużywane wejścia można dołączyć wprost do napięcia zasilania Ucc.

Nieużywane wejścia bramek AND, NAND, OR oraz NOR można dołączyć do wejść używanych

tych samych bramek, jeżeli dopuszczalna obciążalność układu sterującego w stanie wysokim (1) nie

zostanie w ten sposób przekroczona.

Wolne wejścia bramek AND, NAND oraz przerzutników można dołączyć do wyjścia nieużywanej

bramki, na wejście której należy przyłożyć napięcie ustawiające wyjście w stanie wysokim (1).

Wolne wejścia bramek AND, NAND oraz przerzutników można dołączyć do niezależnego źródła

napięcia zasilania o napięciu wynoszącym 2,4-3,5 V.

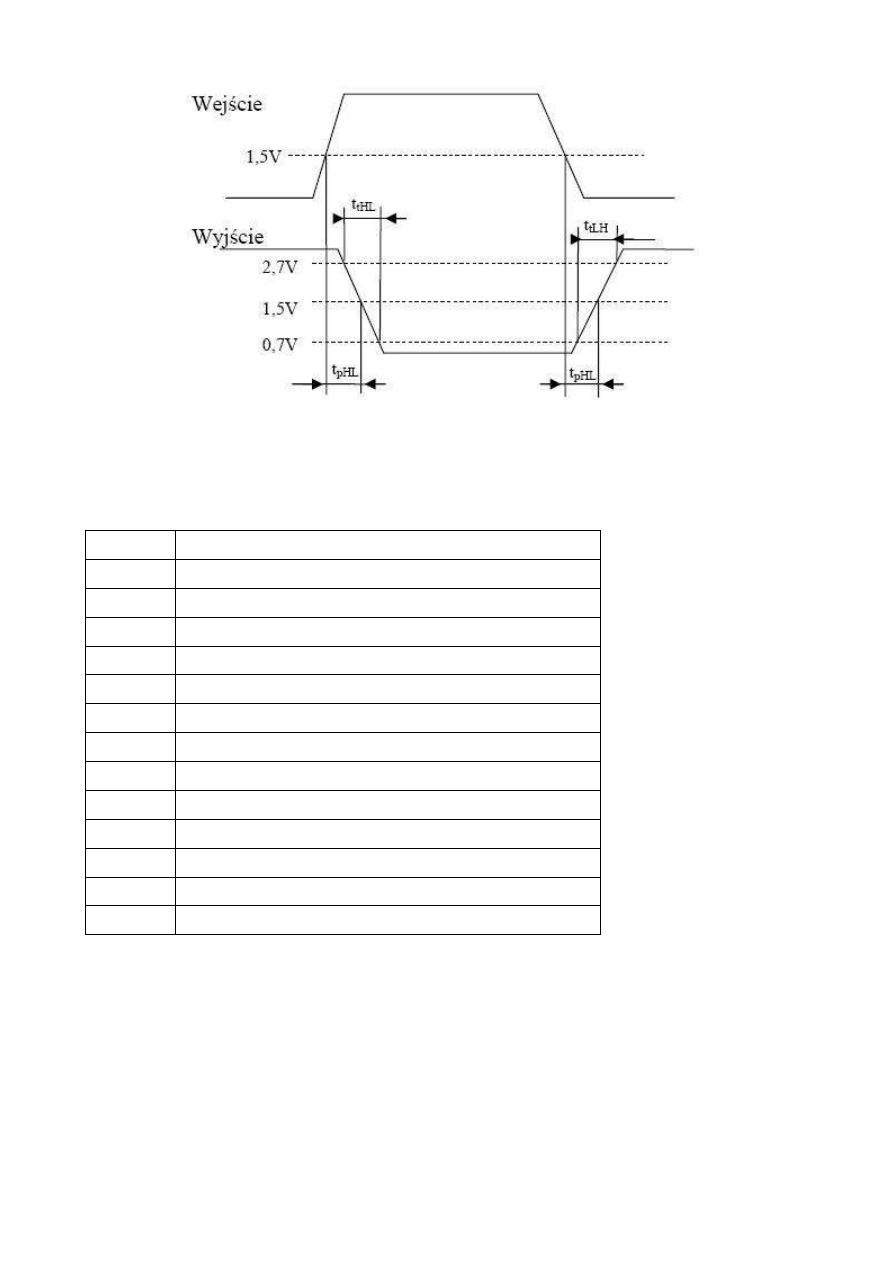

5. Parametry dynamiczne – rysunek.

tpLH – czas propagacji do stanu 1 na wyjsciu, jest to czas mierzony od chwili osiągnięcia przez

zbocze przebiegu wejściowego wartości 1,5V do chwili, kiedy napięcie na wyjściu wzrośnie od

poziomu L do 1,5V.

tpHL– czas propagacji do stanu 0 na wyjsciu, jest to czas mierzony od chwili osiągnięcia przez

zbocze przebiegu wejściowego wartości 1,5V do chwili, kiedy napięcie na wyjściu zmniejszy się od

poziomu H do wartości 1,5V.

tp – średni czas propagacji.

ttLH – czas narastania impulsu wyjściowego

ttHL – czas opadania impulsu wyjściowego

6.Parametry statyczne bramek TTL.

U

CC

napięcie zasilania

U

IH

napięcie wejściowe w satnie 1

U

IL

napięcie wejściowe w satnie 0

U

OH

napięcie wyjściowe w stanie 1

U

OL

napięcie wyjściowe w stanie 0

I

IH

prąd wejściowy w stanie 1

I

IL

prąd wejściowy w stanie 0

I

OH

prąd wyjściowy w stanie 1

I

OL

prąd wyjściowy w stanie 0

I

OS

prąd wyjściowy zwarcia

I

CCL

prąd zasilania w stanie 0 na wyjściu

I

CCH

prąd zasilania w stanie 1 na wyjściu

N

obciążalność bramki

P

S

straty mocy w bramce

7. Podział przerzutników – opis podstawowych grup.

Przerzutniki są elementarnymi układami logicznymi z pamięcią, czyli fizycznymi reprezentantami

ukłdów elementarnych. Podobnie jak wszystkie układy z pamięcią, przerzutniki można podzielić na

dwie zasadnicze grupy: przerzutniki asynchronicze i synchroniczne.

Przerzutniki asynchronicze mają tylko jeden typ wejść, tzw. wejścia informacyjne, podczas gdy

przerzutniki synchroniczne mają dodatkowo tzw wejścia zegarowe. Wejściami w sensie teorii

automatów są tylko wejścia informacyjne tzn. że tylko stan tych wejść wraz z aktualnym stanem

zewnętrznym, określa następny stan przerzutnika. W przerzutnikach asynchronicznych stan

wewnętrzny zmiena się równocześnie (z dokładnością do stanu propagacji) ze stanem wejść

informacyjnych. W przerzutnikach asynchronicznych chwile zmian stanów wyznaczone są przez

sygnały obecne na wejściach zegarowych.

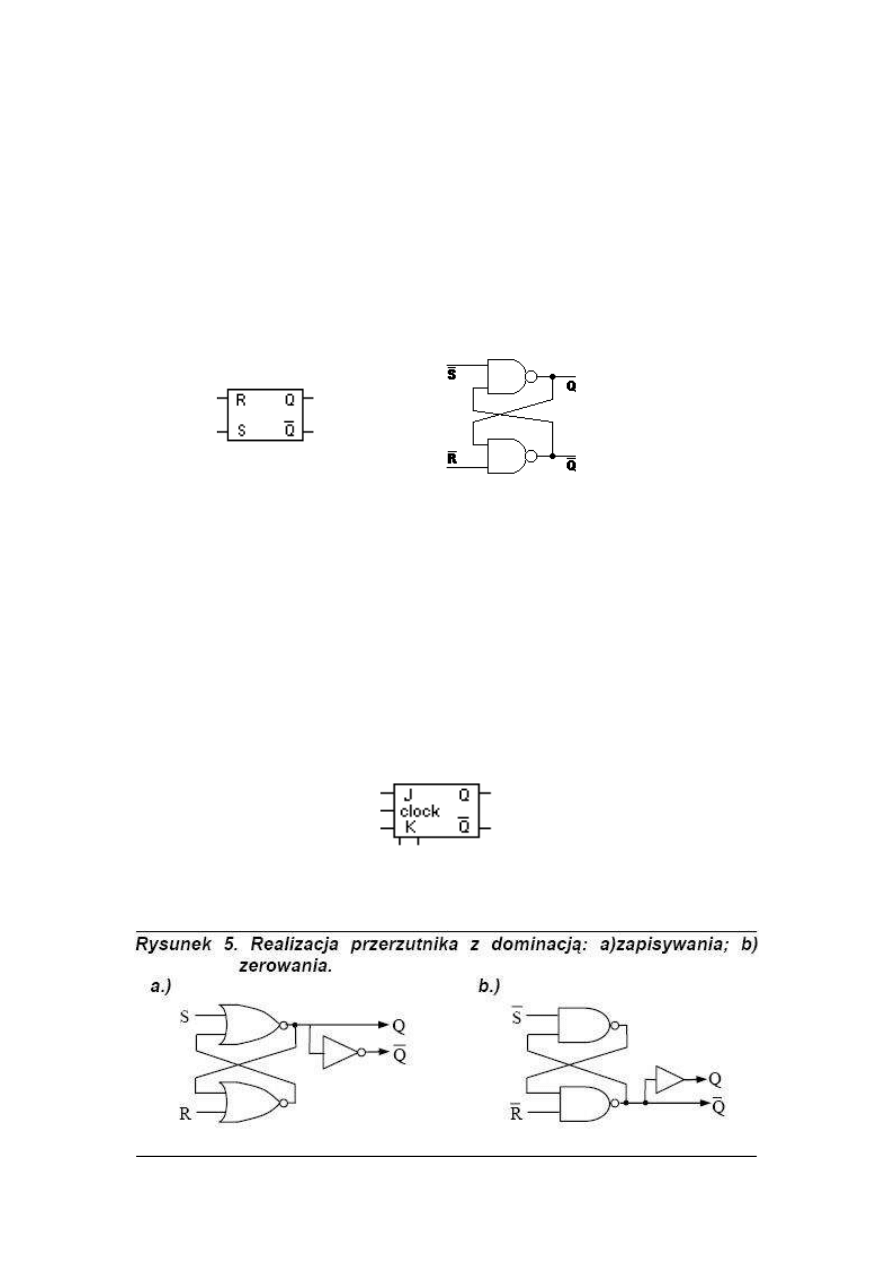

8. Schemat i opis działania przerzutnika RS.

Dla przerzutnika zbudowanego na bramkach NAND sygnałem sterującym jest "0", natomiast dla

NOR "1". Jeśli na wejście SET zostanie podany sygnał sterujący na wyjściu Q będzie "1" -

przerzutnik będzie ustawiony, jeśli na wejście RESET zostanie podany sygnał sterujący na wyjściu

Q będzie "0" - przerzutnik będzie zresetowany. Sygnał sterujący może być impulsem. Jeśli na

wejściach są narysowane kółeczka to przerzutnik jest sterowany "0". Wyjścia są komplementarne,

tzn. na ich stany logiczne są przeciwne. Jest to przerzutnik asynchroniczny, czyli bez zegara

taktującego.

9. Schemat i opis działania przerzutnika JK.

Przerzutnik zachowuje się w zależności od kombinacji stanów wejściowych na J i K. Przerzutnik

jest wyzwalany dwuzboczowo, tzn. gdy jest zbocze narastające układ przepisuje dane wejściowe do

wewnętrznego przerzutnika Master a przy opadającym z przerzutnika Master do przerzutnika Slave.

Przerzutnik zachowuje się w następujący sposób:

0 0 - stan na wyjścia nie ulega zmianie

1 0 - stan na Q jest ustawiany na "1"

0 1 - stan na Q jest ustawiany na "0"

1 1 - stan na wyjściu zmienia się na przeciwny

Z przerzutników buduje się różnego rodzaju pamięci, liczniki i rejestry i dzielniki.

10.Realizacja przerzutnika zapisywanie – wymazywanie.

Jeśli sygnał S dominuje nad sygnałem R, mówi się o dominacji zapisywania, w przeciwnym

wypadku o dominacji zerowania.

11.Znajomość podstawowych układów pomiarowych do wyznaczania charakterystyk.

12.Hazard statyczny i dynamiczny.

W układach cyfrowych ma miejsce niekorzystne zjawisko, nazwane hazardem, którego

podłożem jest niezerowy czas propagacji (przenoszenia) sygnałów. Rozróżnia się dwa rodzaje

hazardu:

•

hazard statyczny

•

hazard dynamiczny

Hazard statyczny jest związany z niezerowym czasem przełączania sygnałów wyjściowych w

bramkach, zaś hazard dynamiczny wynika z niezerowego czasu propagacji sygnału w większych

partiach układu. Hazard statyczny można wyeliminować już na etapie projektowanie układu, dzieje

się to kosztem skomplikowania układu. Eliminacja hazardu statycznego powoduje równoczesną

eliminację hazardu dynamicznego.

Wyszukiwarka

Podobne podstrony:

Ćw. 10- Przerzutniki TTL, Politechnika Lubelska, Studia, Teoria obwodów, Laboratorium, Sprawozdania,

Laborki z elektroniki, ED 4 - Bramki logiczne TTL, POLITECHNIKA

Bramki logiczne TTL 3, Politechnika Lubelska

Bramki logiczne TTL 2, Laborka z elektroniki

Bramki logiczne TTL

Bramki TTL

bramki TTL

Objaśnienie zasady działania bramki NAND na podstawie struktury wewnętrznej wykonanej w technologii

Instr nr 7 bramki TTL[1]

119,120,121 parametryTTL i CMOS,charakterystyka przejściowa TTL, obciążalnosc bramki

Bramki TTL i CMOS mają na wyjściu wzmacniacz przeciwsobny

bramki TTL

PA2 8 przerzutniki synchron

PA2 5 przerzutniki asynchr

Koordynacja ze strzałem na dwie bramki cz 3

Bramki Logiczne

więcej podobnych podstron