55 12212-01

MASTER

A3

Sven-Ake Larsson

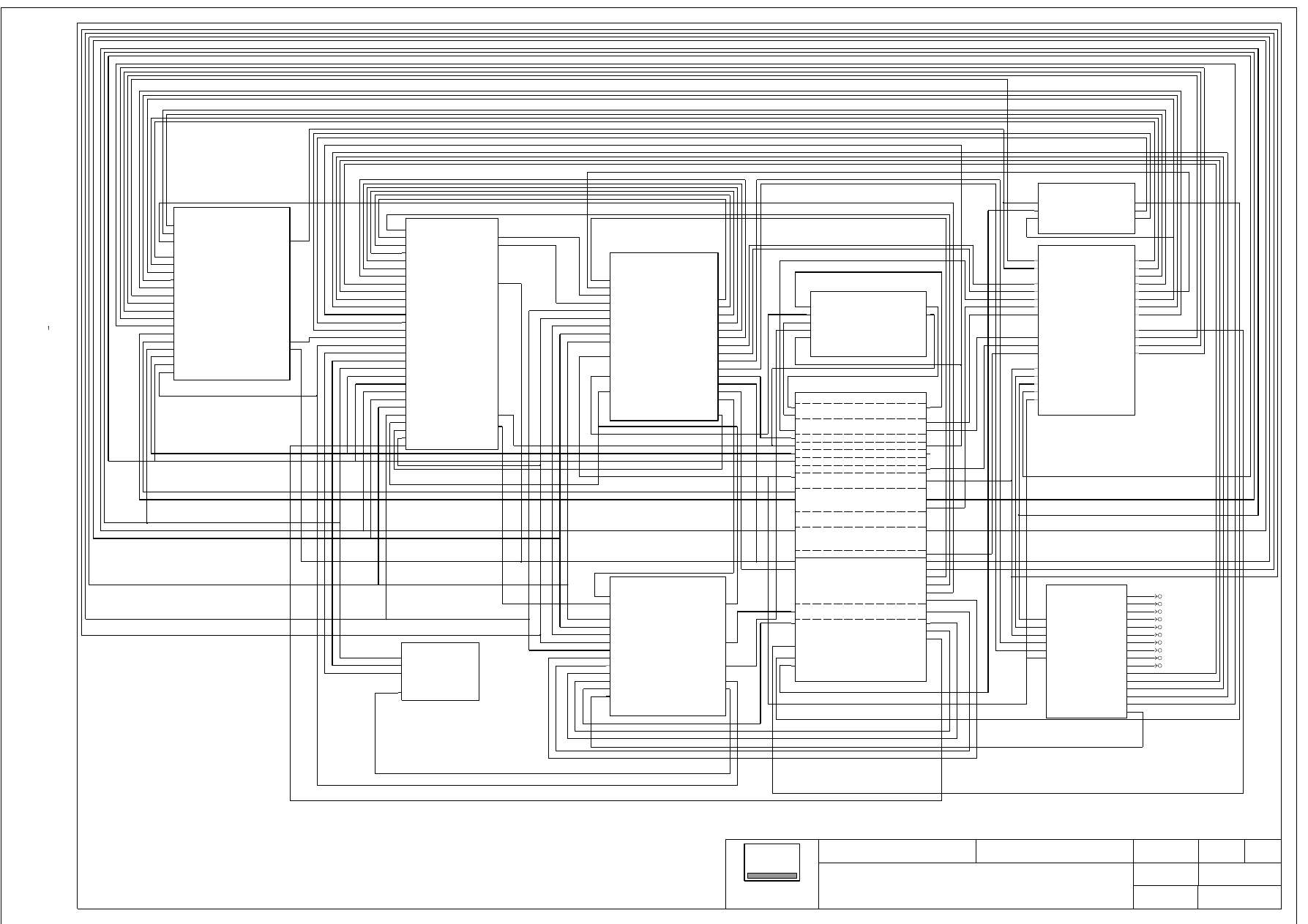

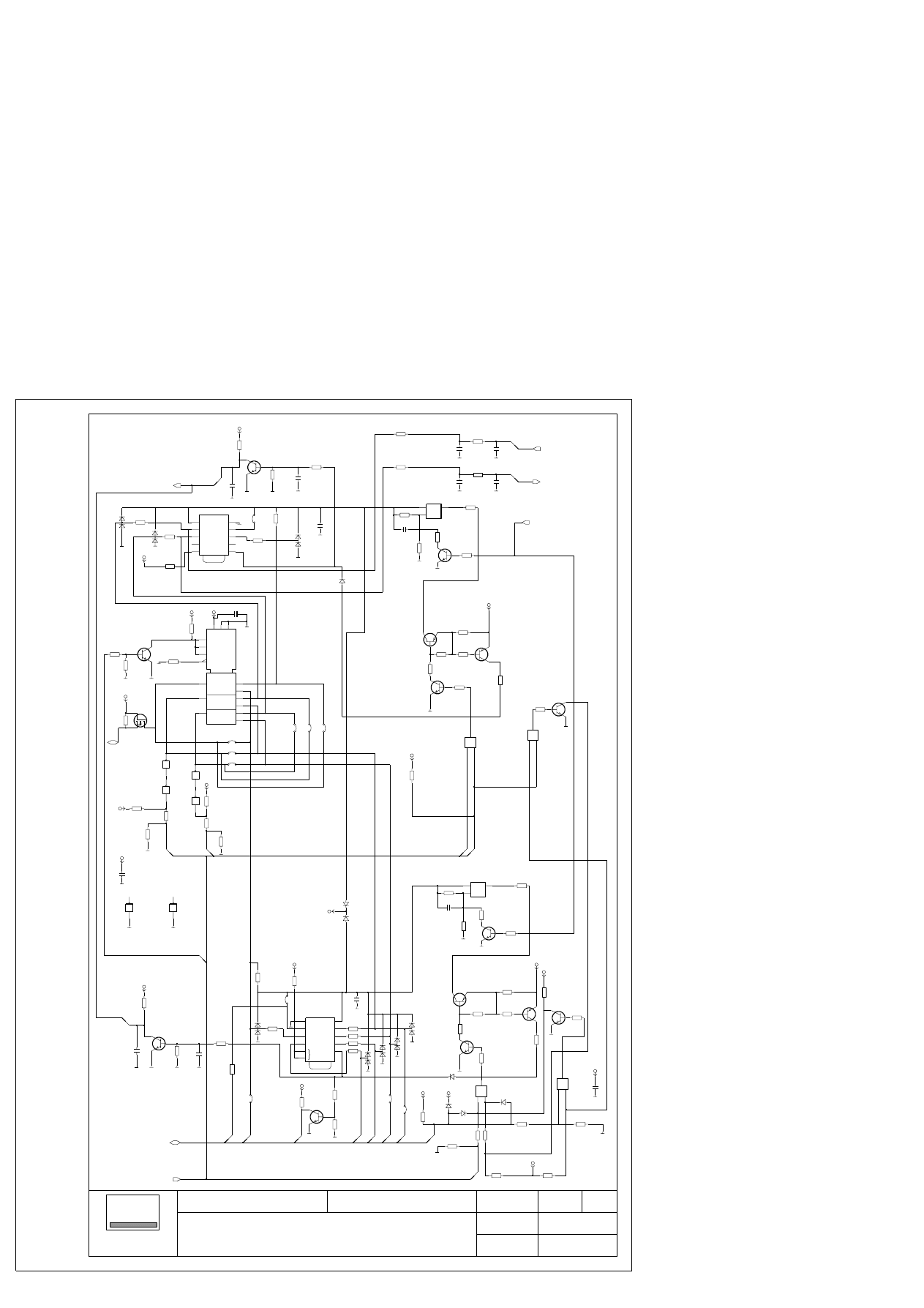

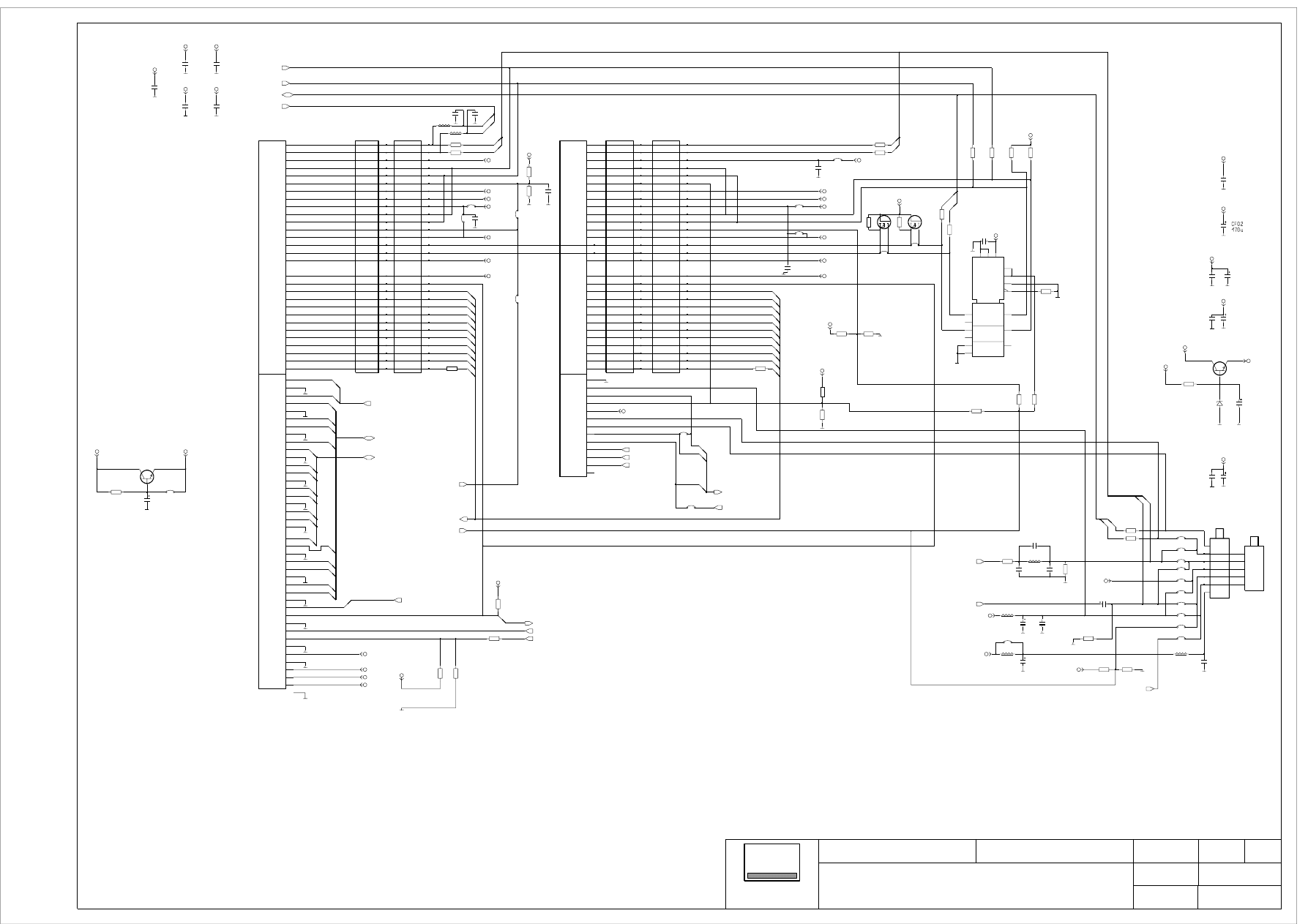

Block overview

11

MAIN BOARD

THIS DRAWING IS PROPERTY OF SCI DESIGN CENTER AND MUST NOT BE COPIED

OR SHOWN OR GIVEN TO THIRD PERSON. VIOLATION OF THESE STIPULATIONS

WILL BE SUBJECT TO LEGAL MEASURES ACCORDING TO EXISTING LAW.

SCI

Design Center

Motala Sweden

ENGINEER

DRAWN BY

SHEET

DATE

TIME

PCB

VARIANT

BLOCK ID

SIZE

of

Sheet 11 (G)

OSD PAL SYNC BLOCK

1

HVSYNC(0:1)

INT_VER

O_E

PAL_A_V(0:2)

2

PAL_DVB

VCO_CNT

Sheet 8 (E)

1284 BLOCK

1284_LEVEL

HSDI_DATA(0:7)

HSDI_SIG(0:8)

HSDI_STATUS(0:1)

2001-03-07

11:57:14

1

Palm Nils Erik

SMARTCARD_IN(0:2)

SMARTCARD_OUT(0:4)

SMARTCARD_SCDATAIO

UART1_CK16

UARTDI(0:5)

UARTDO(0:5)

VCO_CNT

VREF_TRIM

Sheet 6 (B)

SMARTCARD BLOCK

SC_CONTROL(0:7)

1,2

SMARTCARD_IN(0:2)

SMARTCARD_OUT(0:4)

SMARTCARD_SCDATAIO

SMART_C_3.3_5V

UARTDI(0:5)

UARTDO(0:5)

HSDI_SIG(0:8)

HSDI_STATUS(0:1)

HVSYNC(0:1)

IIC(0:1)

IIC_2(0:1)

JTAG_S_IN(0:3)

JTAG_S_TDO_S

MDO(0:10)

PCMCLK

REMOTECONTROL_SIRCSO

RESET

RGB_OUT(0:2)

SADDR(0:11)

SDATA(0:15)

SDRAM_CONTROL(0:8)

PROCESSOR BLOCK

AUDIO_OUT(0:4)

CHIP_SELECT(0:6)

CLK_27

COMPOUT_CVBS

EB_CLK401

EB_CLK402

EB_CLK403

EB_DRAMOUT(0:4)

EB_EXTINT(0:2)

EB_IN(0:3)

EB_OUT(0:2)

EXTADDR(0:24)

EXTDATA(0:31)

FBLK_IN

GENERAL_IO(0:5)

HSDI_DATA(0:7)

IRQ-RDY1

IRQ-RDY2

1,2

JTAG_M_OUT(0:2)

JTAG_M_TDO_M

LNB_LARM

MDI_EC(0:10)

MDO_EC(0:10)

MOD_RESET_A

MOD_RESET_B

O_E

READ_STROBE

RESET

TDO

UARTDI(0:5)

UARTDO(0:5)

Sheet 2 (P)

DISEQ

EB_CLK402

0

EB_EXTINT(0:2)

0-1

EB_OUT(0:2)

EXTADDR(0:24)

16-31

EXTDATA(0:31)

EXTWAIT1

3-5

GENERAL_IO(0:5)

GND_SEP

HSDI_DATA(0:7)

HSDI_SIG(0:8)

HSDI_STATUS(0:1)

IIC(0:1)

INT_VER

IIC(0:1)

LNB_IN(0:1)

MDO_EC(0:10)

MOD_RESET_B

PAL_A_V(0:2)

PAL_DVB

RESET_DMA

RF_A_MONO

RF_CVBS

TUNE_IN

Sheet 4 (D)

HOST2 BLOCK

+3.3V_SEP

CD1

CD2

4,6

CHIP_SELECT(0:6)

CLK_27

+2.5V

FRONTEND BLOCK

Sheet 10 (F)

BG_L-NORM

CH3:4

EB_CLK403

EB_EXTINT(0:2)

FRONTEND_C1

FRONTEND_C2

FRONTEND_SCL

FRONTEND_SDA

3

GENERAL_IO(0:5)

HSDI_DATA(0:7)

HSDI_SIG(0:8)

HSDI_STATUS(0:1)

JTAG_S_TDO_S

LATCH_CONTROL

LIGHT_DISPLAY

MOD_RESET_B

RESET

SADDR(0:11)

SDATA(0:15)

SDRAM_CONTROL(0:8)

SMART_C_3.3_5V

+3.3V_OP

+12V

+23V

+5V_OP

+12V_OP

TDO

+6V

+33V

+3.3V

HOST CONTROL BLOCK

Sheet 3 (H)

1284_LEVEL

1,3

CHIP_SELECT(0:6)

EB_DRAMOUT(0:4)

EB_OUT(0:2)

EXTADDR(0:24)

EXTDATA(0:31)

JTAG_M_OUT(0:2)

JTAG_M_TDO_M

JTAG_S_IN(0:3)

EXTWAIT1

IIC_2(0:1)

IRQ_RDY1

IRQ_RDY2

0

JTAG_M_OUT(0:2)

LATCH_CONTROL

LATCH_CONTROL2

LATCH_CONTROL3

MDI_EC(0:10)

MDO(0:10)

MOD_RESET_A

READ_STROBE

RESET

SAT_SW_WR

SC_CONTROL(0:7)

STD_BY

VREF_TRIM

+5V

DESCRAMBLER BLOCK

Sheet 5 (C)

CA_5V_CTRL

CD1

CD2

1,2

CHIP_SELECT(0:6)

EB_CLK401

2

EB_EXTINT(0:2)

0

EB_IN(0:3)

1

EB_OUT(0:2)

EXTADDR(0:24)

24-31

EXTDATA(0:31)

FRONTEND_SCL

FRONTEND_SDA

IIC(0:1)

IIC_2(0:1)

LATCH_CONTROL2

LATCH_CONTROL3

PAL_A_V(0:2)

PAL_DVB

PCMCLK

REMOTECONTROL_SIRCSO

RESET

RESET_DMA

RF_A_MONO

RF_CVBS

RGB_OUT(0:2)

TUNE_IN

RESET

SAT_SW_WR

STD_BY

Sheet 7 (A)

AUDIO/VIDEO BLOCK

AUDIO_OUT(0:4)

BG_L-NORM

CA_5V_CTRL

CH3:4

COMPOUT_CVBS

1,2,3

EXTADDR(0:24)

24-31

EXTDATA(0:31)

FBLK_IN

FRONTEND_C1

FRONTEND_C2

+3,3V

+3,3V_OP

+3.3V_SEP

+33V

+5V

+5V_OP

+6V

DISEQ

0-2

EXTADDR(0:24)

24

EXTDATA(0:31)

GND_SEP

1

IIC_2(0:1)

LIGHT_DISPLAY

LNB_IN(0:1)

LNB_LARM

JTAG_S_IN(0:3)

EXTDATA(0:31)

EXTADDR(0:24)

EB_OUT(0:2)

EB_DRAMOUT(0:4)

EB_IN(0:3)

SC_CONTROL(0:7)

CHIP_SELECT(0:6)

HSDI_STATUS(0:1)

HSDI_SIG(0:8)

HSDI_DATA(0:7)

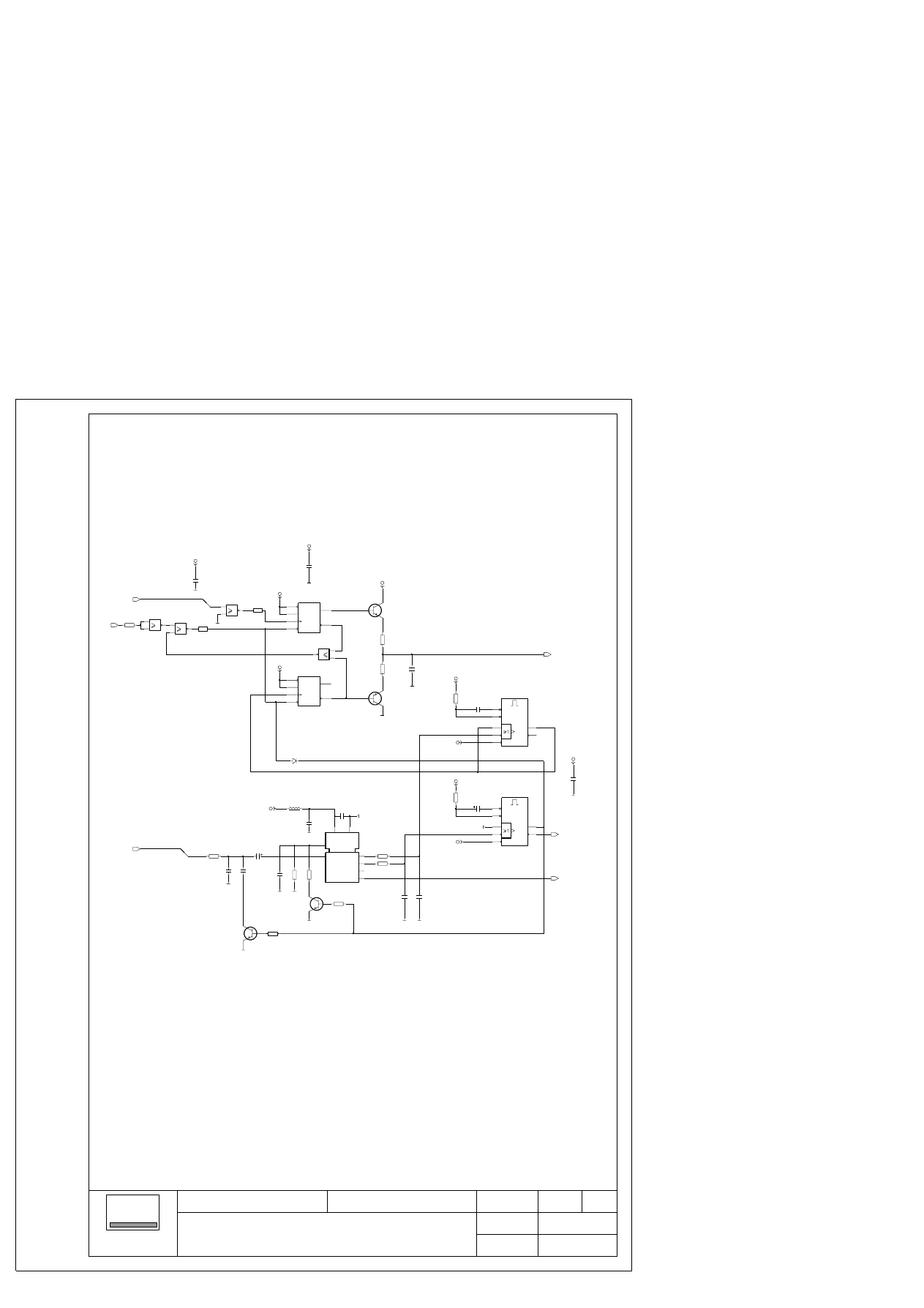

Sheet 9 (S)

POWER BLOCK

+12V

+12V_OP

+2,5V

+23V

SDRAMCONTROL(0:8)

SDATA(0:15)

SADDR(0:11)

RESET

GND_SEP

+3.3V_SEP

LNB_IN(0:1)

LNB_LARM

PAL_A_V(0:2)

RGB_OUT(0:2)

AUDIO_OUT(0:4)

IIC(0:1)

STDBY

DISEQ

HVSYNC(0:1)

SMARTCARD_OUT(0:4)

MDO_EC(0:10)

MDI_EC(0:10)

EB_EXTINT(0:2)

MDO(0:10)

UARTDI(0:5)

GENERAL_IO(0:5)

UARTDO(0:5)

SHEET

DATE

TIME

PCB

VARIANT

BLOCK ID

SIZE

of

THIS DRAWING IS PROPERTY OF SCI DESIGN CENTER AND MUST NOT BE COPIED

1

29

2001-03-07

11:57:14

2

Palm Nils Erik

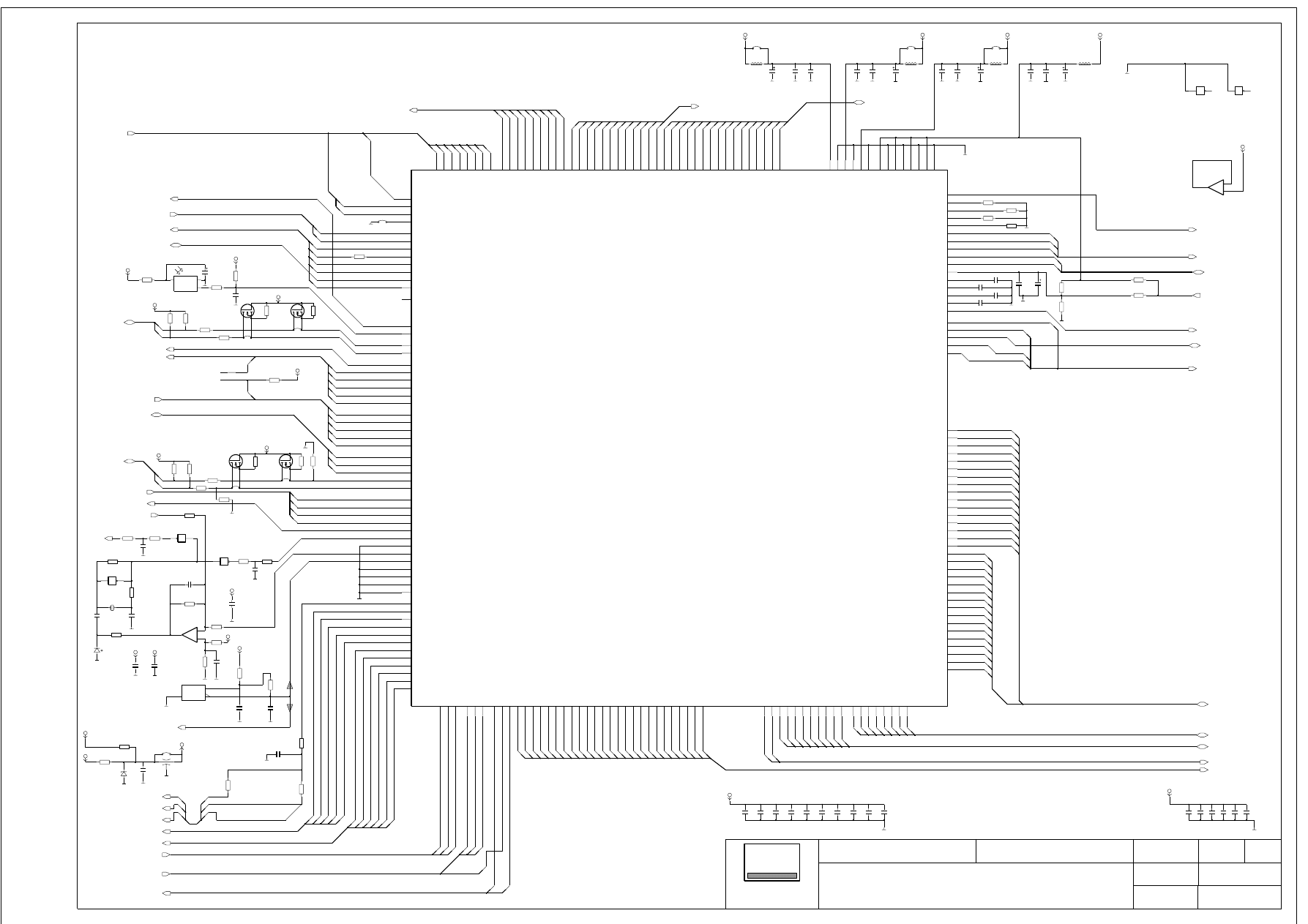

55 12212-01

MASTER

A3

P

Sven-Ake Larsson

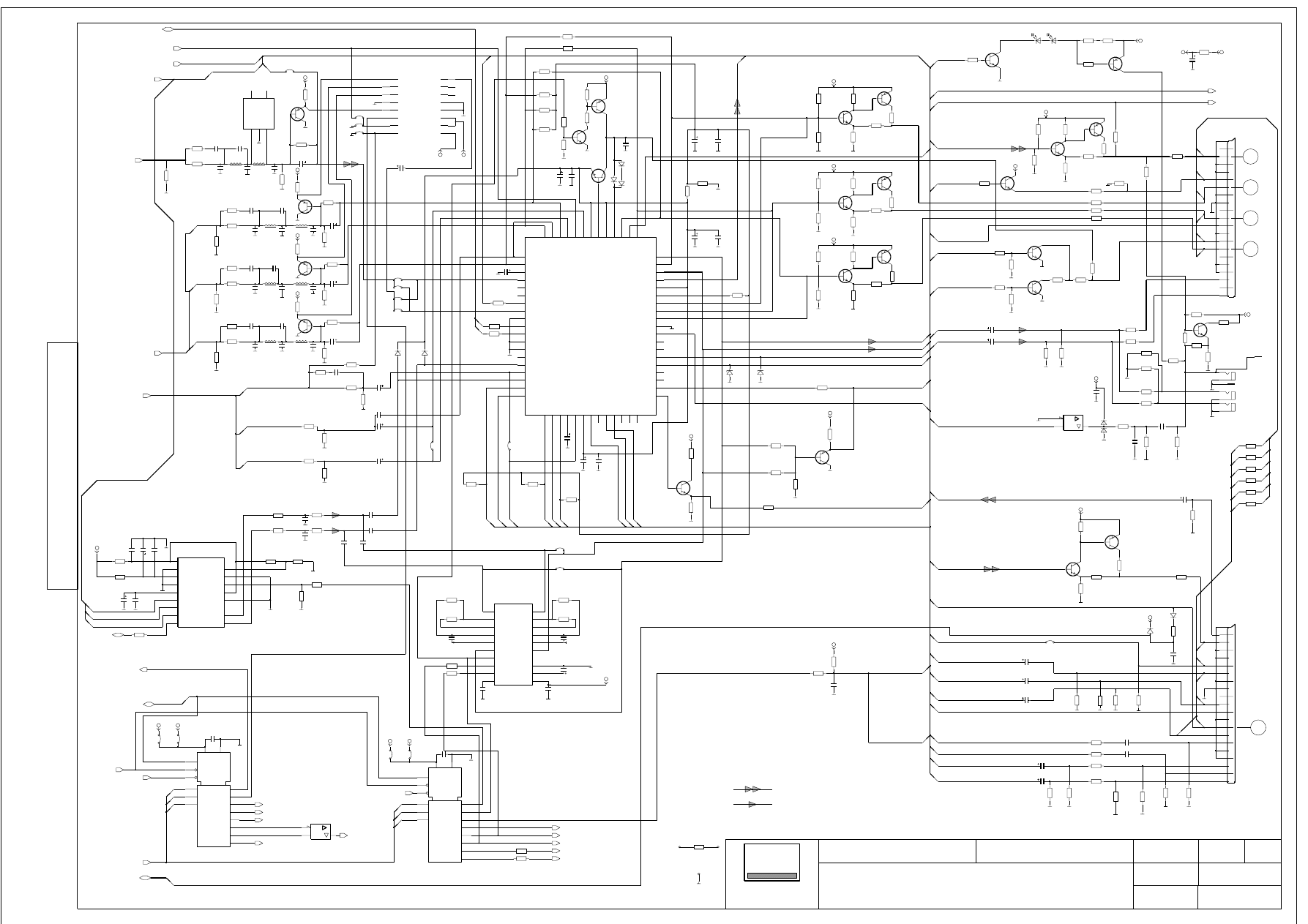

Processor block

11

MAIN BOARD

OR SHOWN OR GIVEN TO THIRD PERSON. VIOLATION OF THESE STIPULATIONS

WILL BE SUBJECT TO LEGAL MEASURES ACCORDING TO EXISTING LAW.

SCI

Design Center

Motala Sweden

ENGINEER

DRAWN BY

17

19

5

1

CP18

22n

0

31

RP21

2k7

8

RP79

39k

5

+3V

6k8

RP80

5

3

2

15

1

0

+3.3V

C10

UART_DI1

C14

UART_DI2

C16

UART_DI3

D10

UART_DO1

D14

UART_DO2

D16

UART_DO3

C11

UART_RTS1

C13

UART_RTS2

L4 UCAS

V12

VCXO_CTRL

A7

VREF

G4

VSYNC

4

4

K3

SDOMU

R18

SPDIF

C3

SRAS

J3

SWE

E18

TCK

H18

TDI

G18

TDO

U20

TEST0

V20

TEST1

W20

TEST2

Y20

TEST3

F18

TMS

D18

TRST

C15

UART_CK16

C12

UART_CTS1

D12

UART_CTS2

B2

SDATA1

G1

SDATA10

G2

SDATA11

H1

SDATA12

H2

SDATA13

J1

SDATA14

J2

SDATA15

C1

SDATA2

C2

SDATA3

D1

SDATA4

D2

SDATA5

E1

SDATA6

E2

SDATA7

F1

SDATA8

F2

SDATA9

L3

SDOML

P1

SADDR8

P2

SADDR9

D3

SCAS

V16 SCCLK

T18 SCDATAIO

V17 SCDET1

V18 SCDET2

E3

SCKE

F3

SCLK

U18 SCRESET

G3

SCS1

H3

SCS2

SCSEL

V15

U16 SCVCCEN

T17 SCVPPEN

B1

SDATA0

R19

PCMDATA

M3 RAS1

RAS2

N3

P3 RAS3

A6

RC_OUT

C18 RESET

K1

SADDR0

K2

SADDR1

R1

SADDR10

R2

SADDR11

L1

SADDR2

L2

SADDR3

M1

SADDR4

M2

SADDR5

N1

SADDR6

N2

SADDR7

HSDI_STATUS1

K18

E4

HSYNC

P18

IICS_SCL

IICS_SDA

N18

G17

IO1

J17

IO2

K17

IO3

M17

IO4

P17

IO5

A18

IRIN

IROUT

B18

M4 LCAS

T20

LRCLK

OSD_ACTIVE

A2

N20

PACCLK

R20

PCMCLK

HSDIF_DATA1

H19

HSDIF_DATA2

G20

HSDIF_DATA3

G19

HSDIF_DATA4

F20

HSDIF_DATA5

F19

HSDIF_DATA6

E20

HSDIF_DATA7

E19

HSDIF_STATUS0

L18

M19

HSDI_SIG2

L20

HSDI_SIG3

L19

HSDI_SIG4

K20

HSDI_SIG5

K19

HSDI_SIG6

J20

HSDI_SIG7

J19

HSDI_SIG8

J18

HSDI_SIG9

W5

EXTDATA31

A11

EXTDATA4

B11

EXTDATA5

A12

EXTDATA6

B12

EXTDATA7

A13

EXTDATA8

B13

EXTDATA9

R3

EXTINT0

T3

EXTINT1

U3

EXTINT2

U14

EXTOE

V13

EXTRW

V14

EXTWAIT

C6

GY_OUT

M20

HSDIF_1

HSDIF_DATA0

H20

T2

EXTDATA17

U1

EXTDATA18

U2

EXTDATA19

A10

EXTDATA2

V1

EXTDATA20

V2

EXTDATA21

W1

EXTDATA22

W2

EXTDATA23

Y1

EXTDATA24

Y2

EXTDATA25

Y3

EXTDATA26

W3

EXTDATA27

Y4

EXTDATA28

W4

EXTDATA29

B10

EXTDATA3

Y5

EXTDATA30

W7

EXTADDR3

Y8

EXTADDR4

W8

EXTADDR5

Y9

EXTADDR6

W9

EXTADDR7

Y10

EXTADDR8

W10

EXTADDR9

A9

EXTDATA0

B9

EXTDATA1

A14

EXTDATA10

B14

EXTDATA11

A15

EXTDATA12

B15

EXTDATA13

A16

EXTDATA14

B16

EXTDATA15

T1

EXTDATA16

Y11

EXTADDR10

W11

EXTADDR11

Y12

EXTADDR12

W12

EXTADDR13

Y13

EXTADDR14

W13

EXTADDR15

Y14

EXTADDR16

W14

EXTADDR17

Y15

EXTADDR18

W15

EXTADDR19

Y7

EXTADDR2

Y16

EXTADDR20

W16

EXTADDR21

Y17

EXTADDR22

EXTADDR23

W17

Y18

EXTADDR24

V9 CS6

D20

DATAIN0

D19

DATAIN1

C20

DATAIN2

C19

DATAIN3

B20

DATAIN4

B19

DATAIN5

A20

DATAIN6

A19

DATAIN7

N19

DCLK

P20

DERROR

EXTACK0

U5

EXTACK1

U7

EXTACK2

U9

EXTADDR0

Y6

W6

EXTADDR1

A5

BIAS_RC

P19

BYTE_START

A3

B_OUT

U12

CLK27

T4 CLK40

V10

CLK_SEL

B8

COMP0

B6

COMP1

A4

COMP2

C4

COMP3

COMP_OUT

D9

V4 CS1

V5 CS2

V6 CS3

V7 CS4

V8 CS5

A8

AGND_COMP

AGND_CPLL

V11

B5

AGND_GY

C7

AGND_RC

W19

APLL_LOCK

ASCLK

T19

B17

AVCC_APLL1

U19

AVCC_APLL2

B4

AVCC_B

C9

AVCC_COMP

AVCC_CPLL

U11

D7

AVCC_GY

B7

AVCC_RC

B3

BIAS_B

C8

BIAS_COMP

C5

BIAS_GY

220R

RP13

SIMBA

IP01

+2.5V

+3.3V

GND

C17

AGND_APLL1

V19

AGND_APLL2

D5

AGND_B

BZT55C3V0

DP02

5

15 14

100n

CP31

26

220R

RP01

OPT

0

4

CP72

100n

0

27

22n

CP16

OPT

CP34

22n

1

4

74AC04

11

10

33R

RP33

JP03

220n

CP03

IP03-5

GND

+3V

1

1

3

1n0

CP76

1k0

RP89

9

20

10

CP66

220u

6u8

LP02

RP71

0R0

10u

CP68

CP61

22n

1

1k82

RP72

1

OPT

XP01-2

2

22n

CP11

4

17

0

2

OPT

14

100n

CP69

1

11

2

5

1

24

7

30

0

2

4

8

16

22

2

3

33R

RP36

BSH111

IP09

5k6

RP87

0

23

OPT

JP07

13

5

11

6

CP70

100n

100n

CP71

3

5

33R

RP69

+3.3V

4

GND

1

2

1

OPT

JP05

432R

RP74

20

IP03-1

74AC04

1

+3V

RP67

2k2

4

JP02

2

0

8

CP20

22n

CP08

220n

6

1

15

21

16

0

RP51

33R

3

3k3

RP08

OPT

6u8

LP04

7

1

10

OPT

22u

CP63

4n7

CP09

1

+3.3V

JP09

1

4

RP09

3k3

1

OPT

22n

CP32

3

1

OPT

LP03

6u8

+3V

10

5

7

3

+3V

CP67

2k2

RP68

CP58

22n

4

RP22

47R

3

7

100n

5

OPT

JP08

8

1

5

2

25

CP22

22n

CP14

22n

2

3

47p

CP39

6

7

+3.3V

18

BSH111

IP08

6

OPTCP02

68p

GND

+3V

1

74AC04

IP03-3

5

22n

CP60

1

100n

CP38

3

220n

CP06

+3.3V

18

9

+3.3V

R12C222

FP01

0

RP18

100k

RP86

10k

22n

CP62

2

RP82

5k6

CP04

68p

+23V

+3.3V

10

JP01

11

5k6

RP81

+5V

3

OPT

100R

RP19

+2.5V

CP15

22n

3

8

3

22u

CP65

2

33R

RP02

6

12

0

4

2

6

4

7

0

OPT

8

RP73

1k00

+3.3V

8

3

LP01

6u8

10

14

IP06

MC34164P-3

GND

3

IN

2

RES

1

RP83

5k6

+3.3V

JP04

CP17

22n

CP75

100n

BB640

DP01

6

CP19

22n

12k

RP85

12k

RP88

7

OPT

CP36

22n

OUT

VCC

1

2

OPT

RP03

47R

RP16

47k

IP05

IR

TSOP1836SI3V

GND

RP78

47k

CP74

18p

5

470R

RP76

2

1M0

RP10

CP07

22n

CP12

OPT

22n

CP30

3

21

2

22R

RP35

100n

JP06

+5V

RP52

33R

9

ZP01

27MHz

4

OPT

OPT CP64

22u

1

33R

RP70

22n

+3.3V

+3.3V

0

1

100k

RP14

12

+3.3V

RP20

470R

CP37

0

4

6

RP75

470R

1

+3.3V

22R

RP62

22n

CP21

CP35

0

3

0

6

2

+5V

IP07

BSH111

4

100n

+3.3V

2

1

22n

CP13

CP33

100n

3

9

28

6

0

7

3

10k

RP17

180k

RP15

8

0

13

23

1

3

2

9

3

74AC04

1

GND

+3V

IP03-4

9

22p

CP05

IP04-2

TL082CD

+23V

GND

+

5

-

6

7

RP77

470R

1

11

13

2

2

5

2

19

0

3

GND

+23V

IP04-1

TL082CD

+

3

-

2

IP10

BSH111

22u

CP01

RP60

22R

5k6

RP84

XP01-1

CP73

100n

1

12

IP03-6

74AC04

1

+3V

GND

13

12

OPT

CLK_27

0

24

22

EB_CLK402

EB_CLK403

TEMP(0:3)

EB_CLK401

FBLK_IN

VCO_CNT

VREF_TRIM

EB_OUT(0:2)

RESET

COMPOUT_CVBS

GENERAL_IO(0:5)

HSDI_STATUS(0:1)

HSDI_SIG(0:8)

JTAG_S_TDO_S

IIC_2(0:1)

EXTDATA(0:31)

AUDIO_OUT(0:4)

HSDI_DATA(0:7)

SDRAM_CONTROL(0:8)

SMARTCARD_IN(0:2)

SMARTCARD_OUT(0:4)

MDO(0:10)

REMOTECONTROL_SIRCSO

EB_IN(0:3)

EB_DRAMOUT(0:4)

EB_DRAMOUT(0:4)

EB_EXTINT(0:2)

UARTDI(0:5)

JTAG_S_IN(0:3)

PCMCLK

SMARTCARD_SCDATAIO

UART1_CK16

CHIP_SELECT(0:6)

EXTADDR(0:24)

SADDR(0:11)

SDATA(0:15)

HVSYNC(0:1)

RGB_OUT(0:2)

UARTDO(0:5)

IIC(0:1)

ARM/JTAG

JTAG_TDO

DISPLAY CONN ALT

THIS DRAWING IS PROPERTY OF SCI DESIGN CENTER AND MUST NOT BE COPIED

OR SHOWN OR GIVEN TO THIRD PERSON. VIOLATION OF THESE STIPULATIONS

WILL BE SUBJECT TO LEGAL MEASURES ACCORDING TO EXISTING LAW.

SCI

Design Center

Motala Sweden

ENGINEER

DRAWN BY

SHEET

DATE

TIME

PCB

RAS

14

UCAS

30

WE

13

10

28

2001-03-07

11:57:14

3

Palm Nils Erik

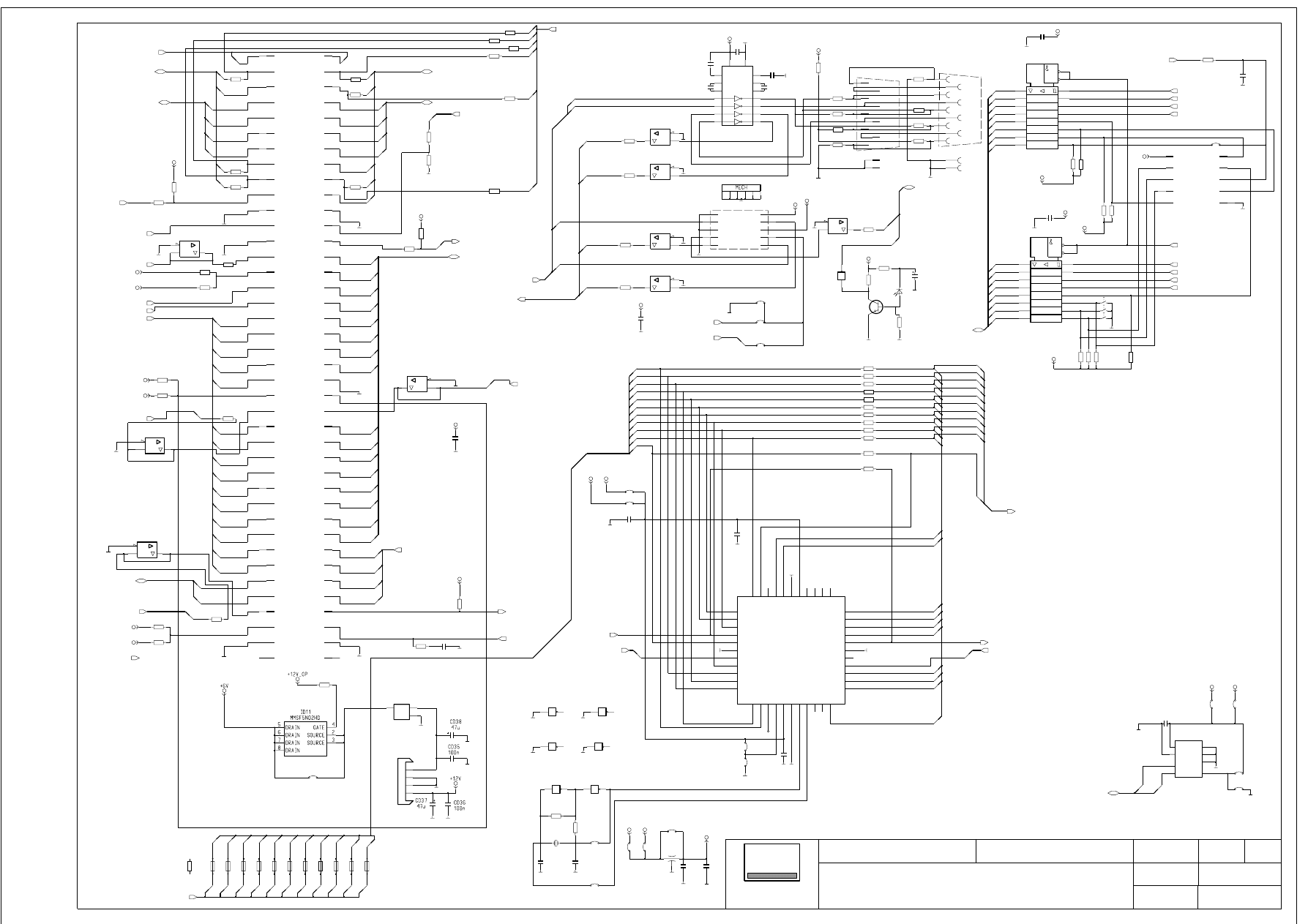

55 12212-01

MASTER

A3

H

Sven-Ake Larsson

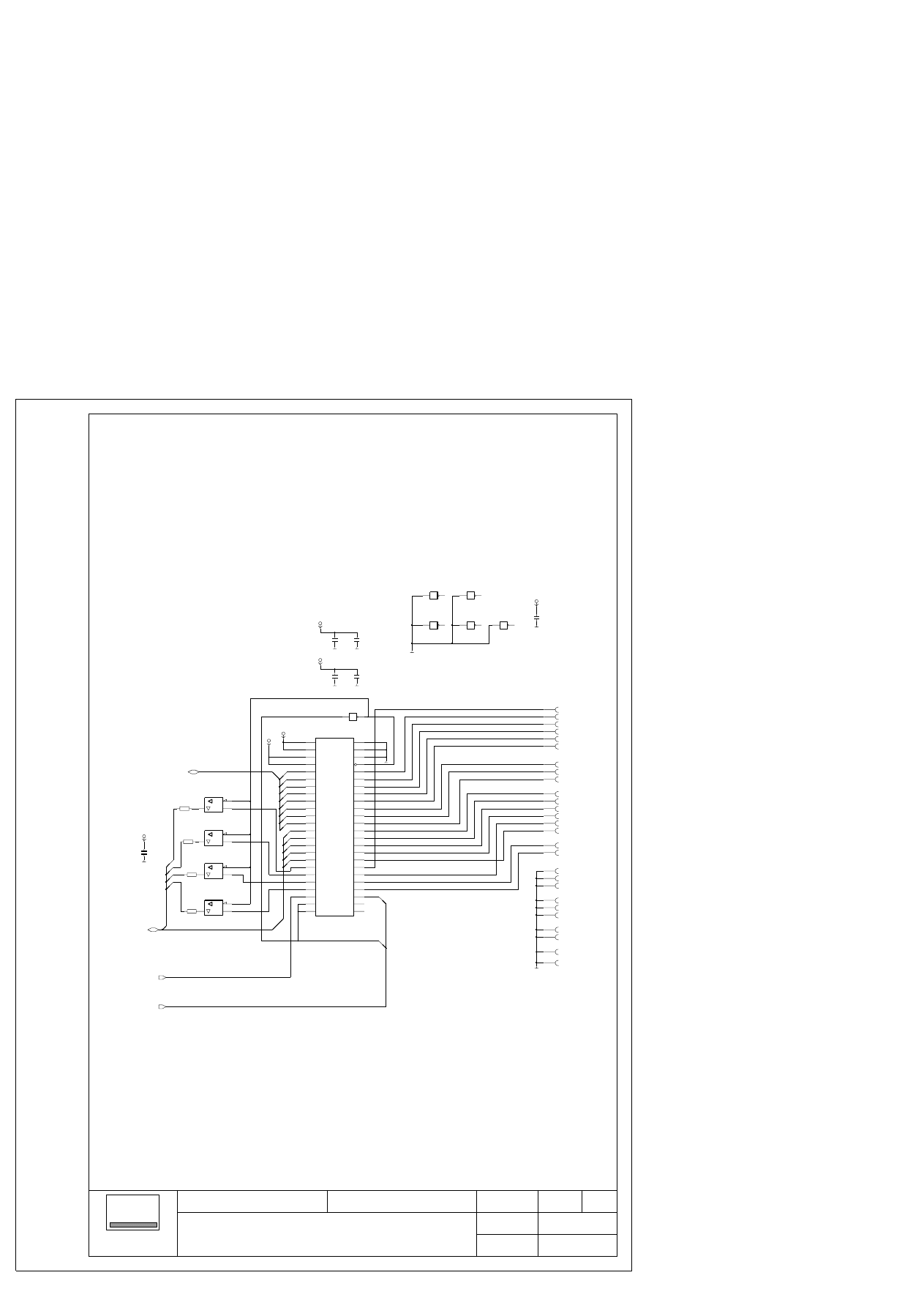

Host control block

11

MAIN BOARD

VARIANT

BLOCK ID

SIZE

of

D11

35

D12

36

D13

38

D14

39

D15

40

D16

41

D2

3

D3

4

D4

5

D5

7

D6

8

D7

9

D8

10

D9

33

LCAS

31

OE

29

17

A0

A1

18

A10

16

A11

15

19

A2

20

A3

23

A4

24

A5

25

A6

26

A7

27

A8

A9

28

D1

2

D10

34

29

1k8

RH88

SOCKEL

IH10

+3.3V

GND

100R

RH19

390R

RH86

OPT

22

31

5

16

1

0

RH60

100R

14

XH02-6

27

12

12

6R8

RH91

+3.3V

OPT

+3.3V

5

6R8

RH94

26

100p

CH43

OPT

20

18

68R

RH32

16

17

1

12

3

22n

CH32

4

13

19

21

28

18

5

31

20

T19

JH08

28

0

21

22n

CH18

XH02-12

3

CH63

22n

4

8

1

10

20

0

XH05-7

11

18

RH20

100R

RH04

47k

15

XH02-4

12

8

1

T08

4

+3.3V

RH07

0R0

11

1

29

6

21

30

11

JH02

OPT

XH02-13

14

1k0

RH89

RH30

1k2

100n

CH69

25

56k

RH10

CH41

22n

OPT

2

22n

CH45

0

2

31

4k7

RH82

OPT

22n

CH77

13

RH58

100R

DQML

14

36

DQMU

RAS

17

1

VCC

50

VSS

WE

15

25

VCC

26

VSS

13

6

DQ0

2

3

DQ1

DQ10

42

43

DQ11

DQ12

45

DQ13

46

DQ14

48

DQ15

49

DQ2

5

DQ3

6

DQ4

8

DQ5

9

DQ6

11

DQ7

12

DQ8

39

40

DQ9

A0

21

22

A1

A10

20

19

A11

A2

23

A3

24

A4

27

A5

28

A6

29

30

A7

A8

31

A9

32

CAS

16

CKE

34

CLK

35

18

CS

29

4

20

4

Driver power: +3.3V

Driver ground:

TMS626162

IH18

GND

OE

28

12

RESET

VCC

37

VSS

27

46

WE

11

14

WP

ACC

0

31

1

D0

29

D1

31

D10

34

D11

36

D12

39

D13

41

D14

43

D15

45

D2

33

D3

35

D4

38

D5

40

42

D6

D7

44

D8

30

D9

32

48

A17

17

16

A18

A19

9

A2

23

10

A20

A3

22

A4

21

A5

20

A6

19

A7

18

A8

8

A9

7

RY

BY

15

BYTE

47

CE

26

OPT

IH09

AM29LV160

A0

25

A1

24

A10

6

A11

5

A12

4

A13

3

2

A14

A15

1

A16

4

22n

CH42

CH38

22n

XH05-5

18

23

7

RH12

47k

4

RH27

100R

5

21

11

1

10

22n

CH54

OPT

19

19

DQ7

12

DQ8

39

DQ9

40

DQML

14

DQMU

36

RAS

17

1

VCC

VSS

50

WE

15

25

VCC

26

VSS

8

CKE

34

CLK

35

CS

18

DQ0

2

DQ1

3

DQ10

42

43

DQ11

DQ12

45

46

DQ13

DQ14

48

DQ15

49

DQ2

5

DQ3

6

DQ4

8

DQ5

9

DQ6

11

Driver ground:

TMS626162

IH19

A0

21

A1

22

A10

20

19

A11

A2

23

24

A3

A4

27

A5

28

A6

29

A7

30

A8

31

A9

32

CAS

16

5

3

1

0

GND

Driver power: +3.3V

25

RH83

4k7

OPT

XH05-9

13

1

IH20-2

74F32

+5V

GND

4

5

6

T09

BC847B

TH06

OPT

CH51

22n

26

XH02-9

7

RH41

100R

0

10

+3.3V

3

17

1

20

CH48

22n

0

4

19

4

5

6

7

8

9

EN

1

GND

10

19

18

17

16

15

14

13

12

VCC

24

17

9

IH11

74HCT574

CLK

11

2

D

3

7

24

16

100R

RH42

4

2

DH02

LS4148

20

8

6

XH02-8

28

22n

CH37

16

6

2

0

4

6

220R

RH03

17

100R

RH16

1

CH52

22n

RH65

18

25

15

15

30

7

28

10

0

23

220R

+3.3V

7

XH01-5

OPT

0

+3.3V

25

7

9

7

CH66

22n

100R

RH57

OPT

0

XH01-3

OPT

22n

CH57

OPT

20

20

T16

T23

LH01

1u0

5

CH27

22n

24

100n

CH67

25

1

10

TH08

BC857B

26

LCAS

38

OE

36

RAS

14

UCAS

37

WE

13

GND

50

GND

45

GND

39

26

GND

1

VCC

6

VCC

12

VCC

VCC

D1

2

D10

42

D11

43

D12

44

D13

46

D14

47

D15

48

D16

49

D2

3

D3

4

D4

5

D5

7

D6

8

D7

9

D8

10

D9

41

19

A0

A1

20

A10

31

A11

32

33

A12 /NC

21

A2

22

A3

23

A4

24

A5

27

A6

28

A7

29

A8

A9

30

RH68

100R

9

31

+3.3V

uPD4265165

IH16

7

XH02-14

CH70

100n

18

CH44

22n

XH02-7

8

RH26

220R

0

17

OPT

2

1

7

XH02-2

3

9

CH16

100n

BC817-25

TH07

4

0

3

+5V

5

9

22

8

28

6

2

CH76

47u

5

22

7

+3.3V

0

11

6

+3.3V

+3.3V

9

6

28

+3.3V

31

LCAS

29

OE

14

RAS

30

UCAS

13

WE

+3.3V

CH68

22n

4

2

D1

34

D10

35

D11

36

D12

38

D13

39

D14

40

D15

41

D16

3

D2

4

D3

5

D4

7

D5

8

D6

9

D7

10

D8

33

D9

GND

+3.3V

IH24

uPD4218165

A0

17

18

A1

16

A10

15

A11

A2

19

A3

20

A4

23

A5

24

A6

25

A7

26

A8

27

28

A9

4

D3

5

D4

7

D5

8

D6

9

D7

10

D8

33

D9

31

LCAS

29

OE

14

RAS

30

UCAS

13

WE

+3.3V

A3

20

A4

23

A5

24

A6

25

A7

26

A8

27

28

A9

2

D1

34

D10

35

D11

36

D12

38

D13

39

D14

40

D15

41

D16

3

D2

10

9

GND

+3.3V

IH13

SOCKEL

A0

17

18

A1

16

A10

15

A11

A2

19

GND

+5V

74F32

IH20-1

1

1

2

3

2

100R

RH79

XH05-8

8

22n

CH50

26

4

23

T18

CH36

22n

5

12

25

100R

RH39

1

12

CH56

22n

8

22

22n

CH55

8

14

CH61

22n

OPT

XH05-13

19

T14

16

14

4

4

26

XH05-6

2

+3.3V

7

+3.3V

11

0

5

2

XH05-11

6

RH81

4k7

OPT

24

1

7

3

21

15

12

10k

RH06

20

0

22

8

22

31

100n

CH72

56k

RH08

1

16

6

OPT

1

1

CH58

22n

26

14

2

9

CH17

100u

Q7

VCC

16

9

T17

24

T15

A0

1

A1

2

A2

3

D

13

GND

8

LE

14

MR

15

4

Q0

5

Q1

Q2

6

7

Q3

9

Q4

10

Q5

11

Q6

12

10

6

0

3

4

3

IH01

74HCT259

1k2

9

12

7

0

+3.3V

RH18

100R

RH29

17

G

18

ISET

12

LOAD

19

V+

4

GND

9

GND

RH02

10k

21

20

C

CLK

13

23

D

2

DIG0

11

DIG1

6

DIG2

7

DIG3

3

DIG4

10

DIG5

5

DIG6

8

DIG7

1

DIN

24

DOUT

22

DP

21

E

15

F

4

11

47k

RH87

MAX7219

IH25

14

A

16

B

4k7

RH80

OPT

6

8

+3.3V

D4

40

D5

D6

42

44

D7

30

D8

32

D9

28

OE

RESET

12

37

VCC

27

VSS

46

11

WE

14

WP

ACC

17

8

A8

7

A9

15

BY

RY

47

BYTE

26

CE

29

D0

31

D1

34

D10

36

D11

39

D12

41

D13

43

D14

45

D15

33

D2

35

D3

38

5

A11

4

A12

3

A13

A14

2

1

A15

48

A16

17

A17

A18

16

9

A19

23

A2

A20

10

22

A3

21

A4

20

A5

19

A6

18

A7

1

IH20-3

74F32

+5V

GND

9

10

8

AM29LV160

IH22

25

A0

24

A1

6

A10

22n

CH62

OPT

11

+5V

VCC

1

VCC

6

VCC

12

25

VCC

21

+12V

13

0

7

D5

8

D6

9

D7

10

D8

41

D9

38

LCAS

36

OE

14

RAS

37

UCAS

13

WE

50

GND

45

GND

39

GND

GND

26

A5

24

A6

27

A7

28

A8

29

30

A9

2

D1

42

D10

43

D11

44

D12

46

D13

47

D14

48

D15

49

D16

3

D2

4

D3

5

D4

6

IH17

uPD4265165

A0

19

20

A1

31

A10

32

A11

/NC

A12

33

A2

21

A3

22

A4

23

D3

35

D4

38

D5

40

42

D6

D7

44

D8

30

D9

32

OE

28

12

RESET

VCC

37

27

VSS

46

WE

11

14

WP

ACC

14

19

A7

18

A8

8

A9

7

RY

BY

15

BYTE

47

CE

26

D0

29

D1

31

D10

34

36

D11

D12

39

D13

41

D14

43

D15

45

D2

33

24

A10

6

A11

5

A12

4

A13

3

A14

2

A15

1

A16

48

A17

17

16

A18

A19

9

A2

23

10

A20

A3

22

A4

21

A5

20

A6

5

100R

RH17

IH03

AM29LV160

A0

25

A1

8

XH05-14

24

22

11

OPT

XH05-1

23

8

12

5

RH72

100R

3

JH19

0

XH05-3

11

10

+3.3V

1

0

RH63

10k

8

24

29

9

CH73

22n

OPT

4

9

1

5

9

+3.3V

15

2

7

0

T20

27

+5V

1

13

JH05

OPT

10

8

100R

RH61

27

+3.3V

12

4

3

30

6

+3.3V

22n

CH53

23

XH05-15

25

TH02

BC807-25

3

100R

RH21

9

1

15

10

7

RH78

100R

CH33

22n

CH49

+3.3V

14

56k

RH09

39

GND

GND

26

VCC

1

VCC

6

VCC

12

25

VCC

2

7

22n

3

D2

4

D3

5

D4

7

D5

8

D6

9

D7

10

D8

41

D9

38

LCAS

36

OE

14

RAS

37

UCAS

13

WE

50

GND

45

GND

A2

21

A3

22

A4

23

A5

24

A6

27

A7

28

A8

29

30

A9

2

D1

42

D10

43

D11

44

D12

46

D13

47

D14

48

D15

49

D16

7

11

9

IH23

uPD4265165

A0

19

20

A1

31

A10

32

A11

/NC

A12

33

29

JH01

25

+5V

13

18

+3.3V

20

27

JH12

4

4

XH05-2

20

10

10

3

BC807-25

TH04

12

RH01

OPT

JH03

OPT

2

+5V

74F32

IH20-4

1

12

13

11

0

28

19

1R5

21

T21

XH05-12

GND

XH05-16

2

6

14

5

20

22n

CH65

OPT

2

16

0

100R

RH50

11

100R

RH52

22n

CH34

1

23

JH04

OPT

18

16

0

JH16

4

1

30

5

31

5

8

30

1

30

11

45

D2

33

D3

35

D4

38

D5

40

42

D6

D7

44

D8

30

D9

32

OE

28

12

RESET

VCC

37

VSS

27

46

WE

11

14

WP

ACC

A5

20

A6

19

A7

18

A8

8

A9

7

RY

BY

15

BYTE

47

CE

26

D0

29

D1

31

D10

34

D11

36

D12

39

D13

41

D14

43

D15

A0

25

A1

24

A10

6

A11

5

A12

4

A13

3

2

A14

A15

1

A16

48

A17

17

16

A18

A19

9

A2

23

10

A20

A3

22

A4

21

19

0

30

13

IH14

AM29LV160

2

+12V

5

T10

RH28

1k2

5

1

RH11

56k

3

11

10

21

10

6

1k2

RH55

23

4

3

16

29

22

8

XH01-6

OPT

1

XH05-10

XH02-5

3

3

5

27

17

2

4

CH64

22n

21

18

0

XH05-4

CH59

22n

OPT

8

+3.3V

RH22

100R

100R

RH76

14

+3.3V

22n

CH46

29

3

2

CH75

22n

OPT

15

4

6

XH02-10

17

21

JH13

OPT

1

0

16

4

10

19

8

13

4

3

12

RH56

1k2

1

3

10k

RH25

9

15

22

+3.3V

26

2

22n

CH71

OPT

470R

RH84

OPT

XH01-1

OPT

XH01-2

OPT

XH01-4

OPT

27

6

XH02-1

27

7

BC807-25

TH01

26

19

17

1

RH46

0R0

22n

CH60

OPT

RH90

220R

CH47

100n

27

RH92

6R8

11

3

29

JH17

RH53

100R

BC807-25

TH03

7

0

2

24

0

15

2

+5V

9

30

17

XH02-3

19

+12V_OP

T11

CH28

+3.3V

LS4148

DH01

2

TH05

BC807-25

100n

BC327-25

TH09

T12

17

31

19

2

11

24

11

25

3

10

3

T13

XH02-11

RH85

470R

OPT

RH51

100R

22n

CH74

OPT

16

18

1

6

4

c

2

d

3

dp

1

e

10

f

5

g

RH49

100R

18

RH93

6R8

IH12

LTC45454G

13

COLON

12

DIG1

9

DIG2

8

DIG3

6

DIG4

11

a

7

b

EB_DRAMOUT(0:4)

LIGHT_DISPLAY

JTAG_S_IN(0:3)

SECTOR_WP

EXTADDR(0:24)

EXTADDR(0:24)

EB_OUT(0:2)

EB_OUT(0:2)

EXTDATA(0:31)

EB_OUT(0:2)

EB_DRAMOUT(0:4)

EXTADDR(0:24)

EXTDATA(0:31)

EB_OUT(0:2)

SADDR(0:11)

SADDR(0:11)

SDRAM_CONTROL(0:8)

CHIP_SELECT(0:6)

LOAD1

RESET

SDATA(0:15)

SDATA(0:15)

SMART_C_3.3_5V

MOD_RESET_B

TMS_M

TDI_M

SPU

TDI_S

JTAG_M_TDO_M

TMS_S

TCK_M

JTAG_M_OUT(0:2)

JTAG_S_TDO_S

JTAG_S_TDO_S

ICE_RST

TRST_S

TCK_S

1284_LEVEL

LATCH_CONTROL

11

MAIN BOARD

DCE CONN

DTE CONN

TELCO CONN

THIS DRAWING IS PROPERTY OF SCI DESIGN CENTER AND MUST NOT BE COPIED

OR SHOWN OR GIVEN TO THIRD PERSON. VIOLATION OF THESE STIPULATIONS

WILL BE SUBJECT TO LEGAL MEASURES ACCORDING TO EXISTING LAW.

SCI

Design Center

Motala Sweden

ENGINEER

DRAWN BY

SHEET

DATE

TIME

PCB

VARIANT

BLOCK ID

SIZE

of

3

RD26

10k

2001-03-07

11:57:14

4

Palm Nils Erik

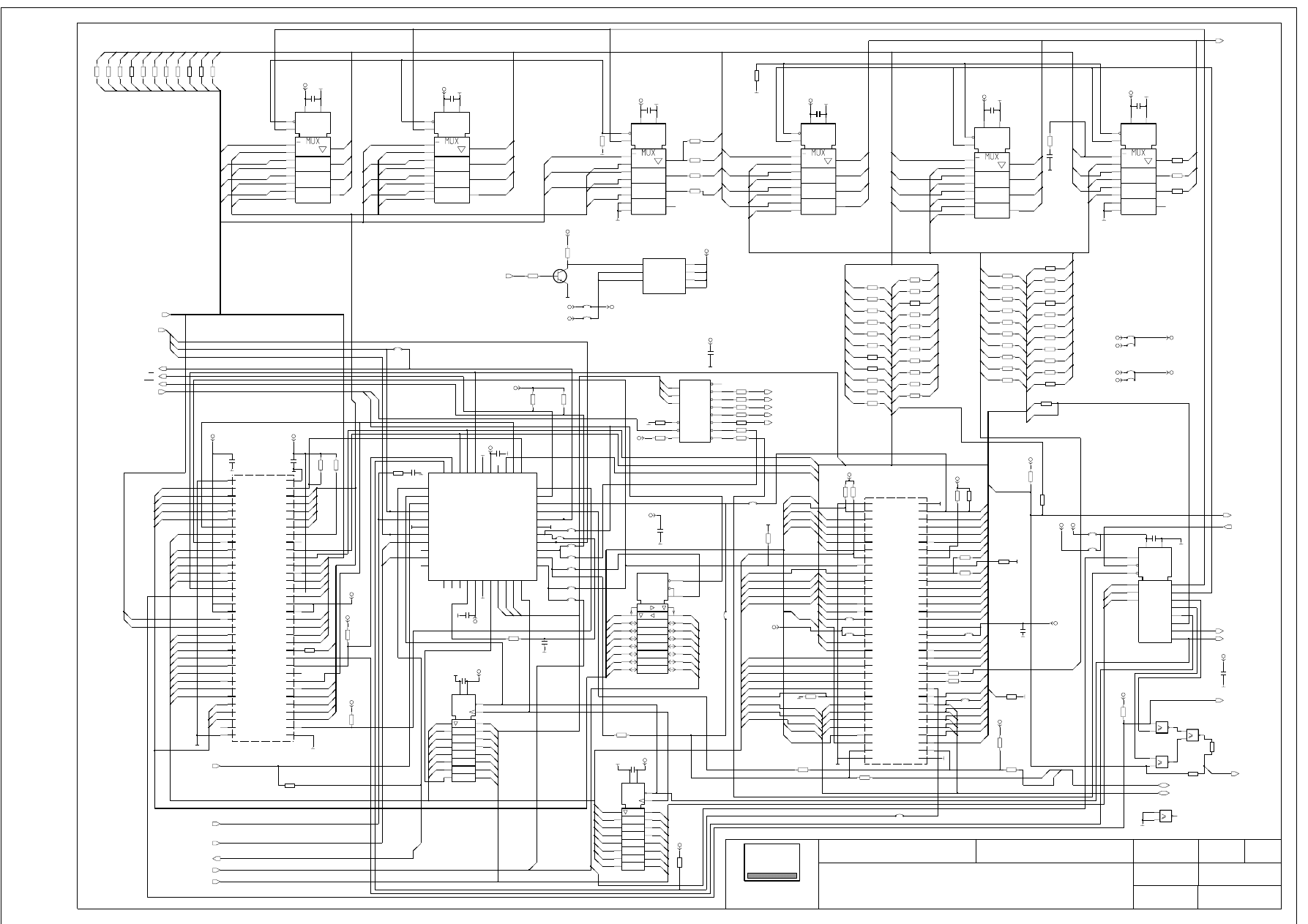

55 12212-01

MASTER

A3

D

Sven-Ake Larsson

Host2 block

74LVT125

OPTION

10

EN

9

8

XD15-6

XD15-59

XD15-4

XD15-26

GND

+3.3V

ID09-3

XD16-9

5

XD15-71

12

18

RD02-2

0

R

0R

RD54-1

XD15-46

0

OPT

JD03

0R

RD54-2

RD04-3

0R

XD15-48

0

RD02-1

0R

RD03-2

0R

30

22n

CD12

0R

RD02-3

XD9-6

0R

XD9-9

3

+3.3V

1

74LV04

ID02-5

+V_D2

GND

11

10

21

RD71-1

+5V

8

0R

RD55-1

100R

RD52

7

XD10-2

0R

RD04-4

3

XD16-4

XD15-24

24

16

RD02-4

0R

9

XD08-1

5

C2-

15

GND

13

12

8

9

11

14

10

7

2

V+

6

V-

16

VCC

9

RD55-2

0R

ID06

MAX202

1

C1+

3

C1-

4

C2+

JD14

6

4

8

17

0R0

RD17

OPTION

RD45-1

0R

OPTION

29

16

0

1

XD08-4

JD08

4

6

18

+12V

0R

RD45-2

OPTION

XD15-2

28

+5V

XD10-3

XD15-51

RD18

0R0

OPTION

XD15-23

GND

+V_D2

ID02-6

74LV04

1

13

12

JD02

1

XD08-8

XD15-16

DD01

S186P

OPT

XD15-41

1

XD15-44

10k

RD27

0R

RD03-4

+3.3V

9

2

+5V

XD15-42

0R0

RD75

CD21

100n

+5V

1

10

22n

CD31

20

XD9-8

GND

+3.3V

IA07-3

74LVT125

10

EN

9

8

XD15-13

JD04

0R0

RD60

XD9-4

CD11

22n

8

XD9-5

XD15-14

5

11

2

5

RD51

1M0

RD01

4k7

+3.3V

XD08-7

15

14

13

12

11

+3.3V

25

7

G1

1

EN

G2

19

2

3

4

5

6

7

8

9

18

17

16

5

22n

CD13

+12V

0

ID04

74LVC541A

+3.3V

GND

ID05

24LC64

E0

1

E1

2

E2

3

MODE

7

6

5

VCC

8

VSS

4

30

7

XD15-80

RD53-4

0R

XD15-64

XD15-10

+3.3V_OP

2

XD15-60

CD32

100n

RD23

10k

XD15-32

33p

CD24

22u

CD14

14

3

GND

17

28

GND

39

GND

16

VCC

38

VCC

+3.3V

R12C222

FD01

IO28

35

IO29

43

IO3

36

IO30

37

IO31

44

IO4

1

IO5

2

IO6

IO7

3

8

IO8

9

IO9

7

TCK

4

TDI

29

TDO

26

TMS

6

GND

IO13

14

IO14

15

IO15

18

IO16

19

IO17

20

IO18

21

IO19

42

IO2

22

IO20

23

IO21

24

IO22

25

IO23

IO24

30

31

IO25

32

IO26

33

IO27

34

ID07

MACH4-64/32

5

CLK0

27

CLK1

40

IO0

41

IO1

10

IO10

IO11

11

12

IO12

13

0R0

RD19

OPTION

0R

RD45-4

OPTION

TD01

BC847B

9

XD15-79

4

XD15-53

OPTION

3k3

RD30

9

1

MD01

5

RD03-1

0R

47p

CD10

22k

RD29

+5V

XD15-1

+3.3V

0R0

RD49

OPTION

RD69

0R0

2

4

XD15-3

XD08-3

XD16-11

24

RD47

0R0

OPTION

RD20

0R0

OPTION

1

4

10

18

+3.3V

XD9-10

0R

RD03-3

ZD01

17.734475MHz

0R

RD54-3

GND

+V_D2

ID02-3

74LV04

1

5

6

XD15-50

RD14

10k

3

3

XD15-62

XD15-35

0R0

OPTION

100n

CD25

XD10-5

GND

EN

4

5

6

3

XD15-74

RD48

GND

+3.3V

ID08-3

74LVT125

10

EN

9

8

74LVT125

ID08-2

+3.3V

XD15-17

6

28

1

XD15-76

RD55-3

0R

0R

OPTION

XD16-2

RD57

0R0

OPTION

XD08-5

XD10-1

RD46-3

1

0

7

5

1

0R

RD53-2

XD15-47

1

XD16-5

XD15-5

7

7

20

2

+3.3V

10

3

0R

RD46-2

OPTION

0

XD15-39

0R

RD70-4

26

10k

RD13

XD15-40

10

JD17

XD16-8

9

+V_D2

6

7

+3.3V

XD15-49

+5V_OP

15

14

13

12

11

XD15-20

100n

CD18

+3.3V

GND

1

G1

19

G2

EN

2

3

4

5

6

7

8

9

18

17

16

11

RD61

0R0

OPTION

2

3

74LVC541A

ID03

XD15-27

74LVT125

ID09-4

+3.3V

GND

OPTION

EN

13

12

16

OPT

JD18

0

XD15-77

27

13

XD10-4

5

100n

CD16

21

X3

XD10-8

0R

RD70-1

0R

XD15-73

1

5

0R0

RD22

RD53-3

GND

+3.3V

ID08-1

74LVT125

1

EN

2

3

1k0

RD62

0

RD55-4

0R

2

1n0

CD26

XD15-25

+3.3V

5

XD15-56

2

XD15-75

XD15-45

330p

CD22

XD16-1

XD15-28

XD15-33

XD15-31

X1

2

1

24

XD15-68

XD15-43

CD15

100n

15

+3.3V_OP

6

23

23

XD9-3

6

5

RD31

220R

26

31

+5V

6

5

OPTION

2

0R

RD04-1

XD10-6

RD50

0R0

7

XD15-70

XD15-37

22

0R

RD46-1

OPTION

XD15-7

XD15-61

ID02-4

+V_D2

GND

9

8

XD15-58

6

1

74LV04

XD15-8

CD19

100n

10k

RD15

25

4

XD08-6

RD25

10k

XD15-54

4

19

XD15-22

0

XD15-15

XD15-78

CD17

100n

1

RD45-3

0R

OPTION

CD27

100n

10

5

GND

+V_D2

ID02-2

74LV04

1

3

4

RD67

68R

OPT

JD10

XD9-11

1

RD58

0R0

OPTION

OPT

JD15

XD08-9

22

XD15-63

4

4

XD15-19

+3.3V

4

10

68R

RD64

RD63

68R

2

XD9-2

RD04-2

0R

8

XD15-29

XD15-55

XD10-7

JD12

X2

6

4

100n

CD20

T22

19

8

1

XD15-38

XD15-69

0R

RD53-1

1

74LV04

ID02-1

+V_D2

GND

1

2

19

JD06

DV normal

JD13

XD16-3

OPT

JD16

XD15-9

RD71-4

0R

OPT

JD01

OPT

JD09

XD10-9

1

ID10

L4941BDT

1

IN

3

OUT

2

REF

0

4

XD16-6

68R

RD66

10

3

5

0R

RD71-2

9

0

XD15-11

XD15-12

OPTION

EN

4

5

6

6

17

XD10-10

0R

RD71-3

74LVT125

ID09-2

+3.3V

GND

7

CD23

33p

100R

RD05

OPTION

RD16

XD15-36

0R

RD46-4

OPTION

OPTION

8

XD15-34

4k7

RD68

0R0

0R0

RD59

22

+3.3V

+3.3V_OP

+3.3V

0

RD65

68R

+3.3V

XD16-7

XD15-57

OPTJD05

DV inverted

+5V

27

XD15-67

EN

13

12

11

+3.3V

PIN

XD17

1

2

3

4

XD9-7

74LVT125

ID08-4

+3.3V

GND

IP03-2

74AC04

1

34

RD70-2

0R

XD15-30

JD11

2

RD54-4

0R

GND

+3V

0

10k

RD24

OPT

3

XD15-65

0

XD08-2

XD15-21

GND

+3.3V

ID09-1

74LVT125

OPTION

1

EN

2

1k0

RD76

RD28

10k

XD15-72

2

29

JD19

XD08-10

20

23

RD70-3

0R

XD15-52

21

31

17

0R0

RD56

XD15-18

0

XD15-66

XD16-10

EXTWAIT1

+3.3V_SEP

MOD_RESET_A

MOD_RESET_B

CLK_27

TS(0:10)

IIC(0:1)

MDO_EC(0:10)

MD_EC(0:10)

MDO_EC(0:10)

EB_CLK402

EB_OUT(0:2)

MDI_EC(0:10)

EXTDATA(0:31)

EXTADDR(0:24)

EXTADDR(0:24)

IIC(0:1)

EB_OUT(0:2)

TDO

JTAG_M_TDO_M

JTAG_M_OUT(0:2)

JTAG_M_OUT(0:2)

UARTDI(0:5)

MOD_RESET_A

EXTDATA(0:31)

GENERAL_IO(0:5)

DTR

CHIP_SELECT(0:6)

DO2

GENERAL_IO(0:5)

EB_EXTINT(0:2)

CTS2

READ_STROBE

DCD

LNB_LARM

RTS2

DISEQ

CD2

UARTDO(0:5)

IRQ-RDY2

DI2

RXD_DTE

HSDI_DATA(0:7)

HSDI_DATA(0:7)

CTS_DTE

HSDI_SIG(0:8)

EXTADDR(0:24)

HSDI_SIG(0:8)

GND_SEP

HSDI_STATUS(0:1)

RESET

O_E

INT_VER

TXD_DTE

CD1

RTS_DTE

IRQ-RDY1

GENERAL_IO(0:5)

VARIANT

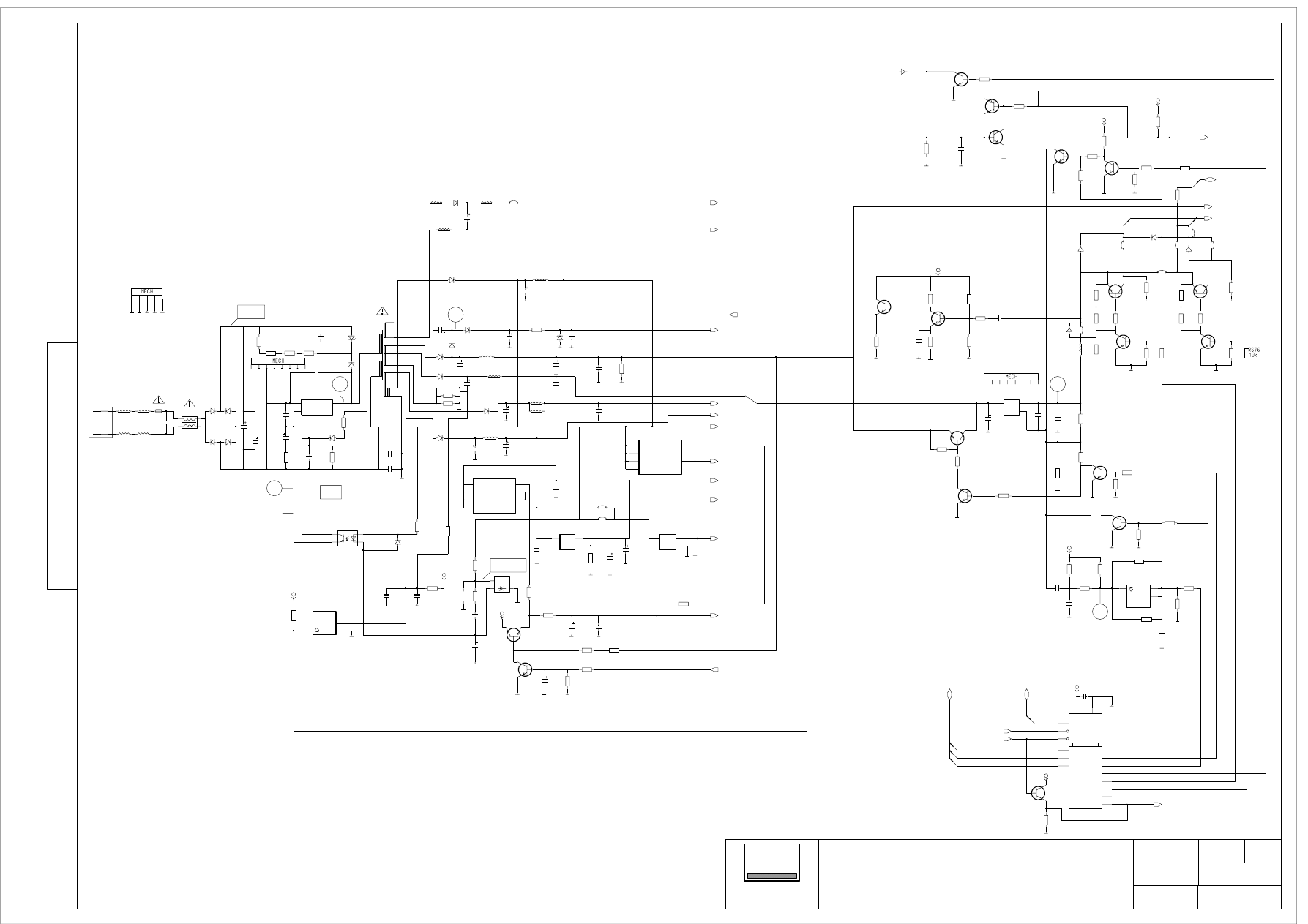

MASTER

A3

C

Sven-Ake Larsson

Descrambler block

11

MAIN BOARD

BLOCK ID

SIZE

of

THIS DRAWING IS PROPERTY OF SCI DESIGN CENTER AND MUST NOT BE COPIED

OR SHOWN OR GIVEN TO THIRD PERSON. VIOLATION OF THESE STIPULATIONS

WILL BE SUBJECT TO LEGAL MEASURES ACCORDING TO EXISTING LAW.

SCI

Design Center

CAM CONN

CAM CONN

IRDETO

LOWER

UPPER

CI

CI

IRDETO

IRDETO/CI

CI

Motala Sweden

ENGINEER

DRAWN BY

SHEET

DATE

TIME

PCB

5

XC02-T15

15

2001-03-07

11:57:14

5

Palm Nils Erik

55 12212-01

XC02-B7

XC02-T11

RC147

0R0

10k

RC158

RC146-4

0R

JC11

6

4

1

12

3

JC32

9

XC02-T17

RC82-4 0R

8

GND

2

1

5

11

14

3

1

6

10

13

16

VCC

YA

4

7 YB

9 YC

12 YD

8

IC02 74LVC257

OPT

EN

15

1

G1

37

5

RC81-4 0R

47R

RC129

2

21

XC02-B65

7

0

7

D7

4

E1

5

E2

6

E3

4

33R

RC123

GND

+3.3V

IC17

74LVC138

1

A0

2

A1

3

A2

15

D0

14

D1

13

D2

12

D3

11

D4

10

D5

9

D6

10

XC02-B52

0

15

18

0R

RC81-3

2

2

T01

1

+3.3V

XC02-T9

RC128

47R

9

4

XC02-T24

28

RC175

68R

OPT

0

13

14

XC02-T18

5

CC20

22n

+3.3V_CA

4

0R0

RC150

JC23

XC02-T13

XC02-T33

7

JC25

6

XC02-B57

+5V

+5V

+5V_CI

OPT

XC02-B1

GND1=GND

4

0

+5V

1

+5V_CI

XC02-B54

22

100R

RC172

5

11

XC02-T38

36

7

XC02-T66

XC02-B6

3

XC02-B43

2

XC02-B22

26

RC155

0R0

3

1

6

10

13

16

VCC

4

YA

7

YB

9

YC

12 YD

XC02-T34

IC12

74LVC257

15

EN

1

G1

8

GND

2

1

5

11

14

VCC

16

YA

4

YB

7

9

YC

YD

12

RC180

10k

RC181

1k0

IC11

74LVC257

EN

15

G1

1

GND

8

1

2

5

11

14

1

3

6

10

13

0

JC29

TC1

BC847B

10k

1

+5V_CI

3

17

9

+3.3V

7

RC171

47R

RC132

XC02-T65

47R

RC127

XC02-B33

3

JC28

7

21

23

9

5

5

23

XC02-B8

0R

RC82-1

0

XC02-B50

+12V

0

RC79 0R0

XC02-B64

+5V

JC19

15

1

XC02-B36

7

RC82-2 0R

XC02-B40

5

2

27

9

6

XC02-T54

JC27

0R

RC146-3

26

9

12

0R0

RC138

13

XC02-B42

4

GATE

5

DRAIN

6

DRAIN

7

DRAIN

8

DRAIN

2

SOURCE

3

SOURCE

17

0

8

15

TC2

MMSF5N02HD

1

6

CC16

22n

2

0

JC31

28

XC02-B32

0R

RC95-1

20

3

30

5

11

14

1

3

6

10

13

16

VCC

YA

4

YB

7

YC

9

YD

12

2

1

+3.3V_CA

4

IC03

74LVC257

OPT

15

EN

G1

1

GND

8

1

2

1

9

33

10

0

5

XC02-B13

1

IC18-1

74LVC02

+3.3V GND

2

3

9

XC02-B5

8

VCC_MAC

16

11

0

1

12

4

8

68R

RC121

8

T04

RC80 0R0

RC157 0R0

XC02-B3

11

5

XC02-B41

RC169

0R0

10

10k

RC57

+3.3V_CA

0

RC145-1

0R

4

8

14

XC02-T55

32

6

XC02-T14

JC12

29

7

10

7

XC02-T45

4

14

JC30

2

1

RC167

68R

XC02-B60

6

10

13

VCC

16

YA

4

YB

7

YC

9

YD

12

0R

RC87-4

74LVC257

IC01

OPT

EN

15

G1

1

GND

8

1

2

5

11

14

1

3

XC02-B12

6

RC151-1

0R

RC144

0R0

0R0

RC170

4

1

XC02-B24

XC02-B46

5

CC28

16

38

XC02-B27

4

30

XC02-B51

22n

7

0R

RC71-3

RC56

10k

OPT

RC06OPT

+3.3V_CA

2

37

25

7

0R0

RC64

21

3

10k

RC70-1 0R

3

+5V

RC58

10k

JC24

XC02-B9

RC780R0

3

+3.3V_CA

XC02-T4

6

13

RC146-2

0R

8

+3.3V

2

5

47R

RC173

OPT

1

T02

22

0R

RC146-1

0R

RC91-2

10

XC02-T53

+5V_OP

RC71-2 0R

6

1

RC20

OPT

RC145-3

0R

RC95-3 0R

XC02-T1

GND1=GND

0R0

RC159

100R

RC125

8

XC02-T29

2

XC02-B26

9

1

47R

20

+3.3V_OP

+5V

8

4

1

12

1

100n

CC23

XC02-T28

28

XC02-B62

XC02-T42

IC18-2

1

5

6

4

9

9

3

0R

RC70-4

RC122

33R

GND

+3.3V

74LVC02

XC02-T35

XC02-T57

25

VCC_MAC

0

5

+5V

14

0R

RC71-4

XC02-T3

OPTION

JC10

0R0

RC99

1

XC02-T44

XC02-B34

5

3

13

6

6

11

RC166 0R0

8

VCC_MAC

XC02-B59

2

0

24

9

100n

CC14

RC87-3 0R

+3.3V

9

XC02-T25

RC82-3

10

XC02-B37

0

0

13

4

3

6

0R

3

XC02-T58

10

XC02-B58

JC07

+5V_CI

XC02-T67

1

XC02-T51

6

4

XC02-T63

6

11

23

3

3

RC43

10k

1

JC22

6

2

9

RC70-3 0R

XC02-B4

OPT

XC02-B28

XC02-B29

XC02-T37

20

4

22n

CC05

XC02-T10

10

14

5

10

10

4

12p

CC33

OPT

4

7

4

RC151-3

0R

4

17

27

4

10

7

XC02-T39

10

6

4

25

11

2

5

XC02-B25

JC26

47n

CC08

22n

CC19

10

15

+3.3V

25

RC149

0R0

XC02-T26

3

8

XC02-B63

XC02-B45

100R

RC112

18

+5V

3

10

14

XC02-B38

1

CC27

22n

OE

19

JC15

1

6

4

2

3

4

5

6

7

8

9

2

18

17

16

15

14

13

12

11

0

16

9

GND

+3.3V

74LVC245A

IC14

3EN2

3EN1

1

1

XC02-T8

33

XC02-B23

22

0

0

5

XC02-B15

GND

8

LE

14

MR

15

Q0

4

Q1

5

Q2

6

Q3

7

Q4

9

Q5

10

Q6

11

Q7

12

VCC

16

3

CC15

100n

7

IC19

74LV259

A0

1

A1

2

A2

3

D

13

+3.3V

XC02-B67

29

1

RC87-1 0R

RC81-2 0R

12

22n

CC25

2

0R

RC145-2

3

XC02-B66

XC02-B16

5

XC02-B2

7

31

0R0

RC86

XC02-B17

7

4

RC164

47R

10

13

0R

RC87-2

5

24

7

RC30

100R

XC02-T59

RC177

68R

XC02-T60

3

0

XC02-T56

9

5

+3.3V_CA

XC02-B31

XC02-T2

3

8

0R

RC70-2

47R

RC119

5

XC02-B19

7

13

12

20

VCC

XC02-B55

XC02-B53

2

3

4

5

6

7

8

9

1

EN

10

GND

19

18

17

16

15

14

6

6

+3.3V

74LV574

IC15

11

CLK

D

16

6

5

11

RC174

390R

17

11

2

7

19

22n

CC06

OPT

+5V

XC02-B61

1

36

RC61

100R

XC02-T22

3

68R

RC108

22n

CC04

OPT

17

28

GND

39

GND

16

VCC

38

VCC

XC02-T6

35

IO29

43

IO3

36

IO30

37

IO31

44

IO4

1

IO5

2

IO6

3

IO7

8

IO8

9

IO9

7

TCK

4

TDI

29

TDO

26

TMS

6

GND

GND

14

IO14

15

IO15

18

IO16

19

IO17

20

IO18

21

IO19

42

IO2

22

IO20

23

IO21

24

IO22

25

IO23

30

IO24

31

IO25

32

IO26

33

IO27

34

IO28

IC20

MACH4-32/32-15VC

5

CLK0

27

CLK1

40

IO0

41

IO1

10

IO10

11

IO11

12

IO12

13

IO13

XC02-B20

2

XC02-B11

10k

RC41

OPT

XC02-T19

XC02-B14

4

JC21

8

RC65

0R0

XC02-T21

XC02-T27

XC02-B48

8

4

T03

1

7

1

RC179

47R

XC02-B10

XC02-B56

5

29

+5V

4

6

19

0

XC02-T50

6

XC02-T32

1

OPT

8

5

5

CC35

10n

OPT

0

8

JC14

XC02-T49

XC02-T61

18p

CC34

0

16

3

14

XC02-T23

XC02-T31

32

XC02-T40

24

XC02-B49

1

6

10

24

XC02-B21

8

9

10

RC71-1 0R

XC02-T47

+5V

27

3

1

IC18-3

74LVC02

+3.3V

GND

2

+5V

7

7

31

10k

RC60

2

0R

RC151-2

CC24

22n

1

CC18

22n

22n

CC17OPT

0

7

XC02-T46

7

9

RC114

33R

OPT

XC02-T62

5

RC62

100R

31

3

0R

RC145-4

+5V

9

2

10

0R0

RC101

OPT

68R

RC178

12

10k

RC39

OPT

2

XC02-B68

XC02-T36

OPT

19

0

68R

RC176

OPT

XC02-T43

8

10k

RC42

18

17

16

15

14

13

12

VCC

20

3

RC29

100R

IC07

74LV574

CLK

11

2

D

3

4

5

6

7

8

9

EN

1

GND

10

19

35

35

2

RC100 0R0

OPT

RC151-4

24

XC02-T5

+3.3V

6

2

XC02-T48

0R

0R

RC91-1

+3.3V

+5V_CI

10

1

XC02-T64

XC02-T20

XC02-B47

XC02-B39

0R

RC81-1

34

2

XC02-B44

6

XC02-B35

8

XC02-T12

2

30

7

RC85 0R0

RC113

100R

XC02-B30

11

0

JC08

OPT

13

2

0R

RC91-4

4

18

JC13

0R0

RC77

XC02-T52

0R0

RC156

JC09

1

IC18-4

74LVC02

+3.3V GND

11

12

13

JC20

+3.3V

0R

RC95-4

3

8

XC02-T16

17

10k

RC133

9

XC02-T41

XC02-B18

XC02-T68

XC02-T30

9

RC66

0R0

2

XC02-T7

10

2

RC95-2 0R

9

YD

12

9

0

34

0R0

RC67

EN

15

G1

1

GND

8

1

2

5

11

14

1

3

6

10

13

VCC

16

YA

4

YB

7

YC

5

RC40

10k

OPT

0

IC13

74LVC257

7

RC91-3 0R

CC32

100n

4

11

6

2

26

+3.3V_CA

0

0

6

2

RC59

10k

TDO

TDI_M

TCK_M

JTAG_M_OUT(0:2)

TMS_M

EXTWAIT1

CA_5V_CTRL

10

38

SDA2_R

SCL2

SDA2

STD_BY

EXTWAIT

SDA2_OE

MDI_EC(0:10)

LATCH_CONTROL3

CHIP_SELECT(0:6)

EXTADDR(0:24)

LATCH_CONTROL2

EB_CLK401

CD1

CD2

MDO1(0:10)

IRQ_RDY2

MDO(0:10)

LATCH_CONTROL

EB_EXTINT(0:2)

SAT_SW_WR

READ_STROBE

RESET

MOD_RESET_A

RESET_CA2

EXTDATA(0:31)

CA_BYPASS2

MDO2(0:10)

CA_D(0:7)

EB_OUT(0:2)

EB_IN(0:3)

IRQ_RDY1

MDI2(0:11)

CA_A(0:14)

CA(0:38)

SC_CONTROL(0:7)

IIC_2(0:1)

CA_BYPASS1

VARIANT

BLOCK ID

SIZE

of

LOWER

UPPER

OPT

2001-03-07

11:57:14

6

Palm Nils Erik

55 12212-01

MASTER

A4P

B

Sven-Ake Larsson

Smartcard block

11

MAIN BOARD

THIS DRAWING IS PROPERTY OF SCI DESIGN CENTER AND MUST NOT BE COPIED

OR SHOWN OR GIVEN TO THIRD PERSON. VIOLATION OF THESE STIPULATIONS

WILL BE SUBJECT TO LEGAL MEASURES ACCORDING TO EXISTING LAW.

SCI

Design Center

Motala Sweden

ENGINEER

DRAWN BY

SHEET

DATE

TIME

PCB

GND

+3.3V_OP

74HC08T

IB03-2

&

4

5

6

100n

CB15

RB41

100R

10k

RB52

4k7

RB76

+3.3V_OP

100R

RB46

JB08

OPT

TB01

BC847B

9

10

8

CB07

22n

+12V_OP

10k

RB100

OPT

IB03-3

74HC08T

+3.3V_OP

GND

&

RB104

33R

CB13

100n

OPT

RB03

33k

5

2

DB08

BAV99

OPT

OPTION

CB08

1n0

1n0

CB09

OPT

4k7

RB30

TB18

BC847B

OPT

RB31

4k7

RB77

4k7

LS4148

DB12

1

74AC04

IB08-2

Vcc12

GND

34

RB53

10k

3k3

RB39

634R

RB97 OPT

RST

S1U

S1

S2U

S2

C1U

VCC

C6U

VPP

C4U

RFU

C8U

RFU

OPTION

JB06

RB95

732R

BB01-2

CARD_READER

UPPER

C3U

CLK

C5U

GND

C7U

IO

C2U

C8 RFU

GND

Vcc12

IB08-1

74AC04

1

12

3

BB01-1

CARD_READER

CLK

C3

GND

C5

IO

C7

RST

C2

VCC

C1

VPP

C6

S2A

S2

S1

S1

S2B

C4

RFU

RB51

10k

10n

CB01

4k7

RB58

100R

RB09

DB16

LL103C

TB16

BC847B

DB01

BAV99

0

10k

RB88

100n

CB12

4k7

RB42

OPT

+5V_OP

3

10k

RB74

OPT

RB11

10k

100R

RB06

RB101

0R0

IB05

LM317LZ

3

IN

2

OUT

1

REF

100R

RB48

OPT

GND

+3.3V_OP

74HC08T

IB03-4

&

12

13

11

OPT

RB98

243R

TB02

BC847B

Vcc12

GND

13

12

2k2

RB29

OPT

RB89

10k

1k0

10k

RB24

1

74AC04

IB08-6

2

2

Y0

3

3

Z1

4

4

Z

5

5

Z0

6

6

INH

7

7

VEE

8

8

VSS

9

9

C

RB28

IB06

4053

MUX/DX

1

1

Y1

10

10

B

11

11

A

12

12

X0

13

13

X1

14

14

X

15

15

Y

16

16

VDD

+3.3V_OP

4

DB10

BAV99

1

+12V_OP

RB61

10k

3

+5V_OP

+3.3V_OP

Vcc12

TB21

BC847B

OPT

100R

BC847B

TB08

6

JB14

100n

CB11

4k7

RB04

RB45

GND

Vcc12

IB08-5

74AC04

1

11

10

RB50

2k2

RB26

6R8

CB04

10n

TB14

BC807-25

LS4148

DB14

0R0

RB102

DB09

BAV99

OPT

33R

RB105

3

+5V_OP

10k

RB87

+3.3V_OP

RB106

33R

CB14

100n

TB15

BC857B

33R

RB103

OPTION

JB05

4

+3.3V_OP

RB90

RB10

100R

JB04

4k7

RB59

1k5

18R

RB23

0

+12V_OP

OPTION

RB15

2

RB84

100R

RB12

10k

BAV99

DB06

5k6

LM317LZ

IB10

IN

3

OUT

2

REF

1

JB01

OPT

RB40

4R7

OPT

2

732R

RB94

+3.3V_OP

BC847B

TB03

BC847B

TB17

LL103C

DB15

TB07

DB03

BAV99

JB03

IB03-1

74HC08T

+3.3V_OP

GND

&

1

2

3

BC807-25

BC847B

TB19

OPT

BAV99

DB11

JB07

OPT

LS4148

DB18

OPT

CB10

100n

CB06

22n

BC847B

TB20

RB85

12k

OPT

1

74AC04

IB08-3

Vcc12

GND

56

OPT

Vcc12

RB91

1k5

RB93

10k

DB17

LS4148

OPT

7

DB19

LS4148

4

BC857B

TB09

BAV99

DB02

RB92

OPT

RB47 100R

OPT

18R

RB49

1k0

RB57

10k

OPT

CB02

47n

243R

RB99

2

3k3

RB07

RB96

634R

10k

OPT

GND

Vcc12

IB08-4

74AC04

1

98

Vcc12

+12V_OP

5k6

12k

RB86

RB43

RB01

4k7

JB02

RB16

OPT

+5V_OP

+3.3V

JB15

RB55

RB05

10k

RB44

4k7

CB03

47n

100k

RB54

6R8

2k2

RB25

10k

RB13

RB38

10k

JB09

OPT

BSH111

IB09

10k

RB02

RB73

10k

Vcc12

+3.3V_OP

CB05

22n

SC_VCC2

SC_PWREN

UARTDI(0:5)

UARTDO(0:5)

1

SC_RST

VCC2

SC_CLKS

SMARTCARD_OUT(0:4)

SMART_C_3.3_5V

SC_VCC1

SC_SEL

SC_SEL

SMARTCARD_SCDATAIO

VCC1

SC_RESET

SC_IO1

SMARTCARD_IN(0:2)

SC_RSRVD

SC_SENSE

SC_PROGV

SC_IO2

SC_CONTROL(0:7)

SC_CONTROL(0:7)

SC_CLK

THIS DRAWING IS PROPERTY OF SCI DESIGN CENTER AND MUST NOT BE COPIED

OR SHOWN OR GIVEN TO THIRD PERSON. VIOLATION OF THESE STIPULATIONS

WILL BE SUBJECT TO LEGAL MEASURES ACCORDING TO EXISTING LAW.

SCI

Design Center

Motala Sweden

ENGINEER

DRAWN BY

SHEET

DATE

TIME

PCB

(C)

A_R_in

Audio Right ch

Audio Left ch

Audio

TV SCART

AUX SCART

CVBS out

(Y)

Composite video

CVBS_IN

A_L_in

SPDIF

VARIANT

BLOCK ID

SIZE

of

1

JA23

2001-03-07

11:57:14

7

Palm Nils Erik

55 12212-01

MASTER

A3

A

Sven-Ake Larsson

Audio/video block

11

MAIN BOARD

4

100k

RA111

3u9

LA05

1u0

CA61

1

2

CA15

33p

RA198

0R0

100R

RA35

RA194

0R0

0R0

RA195

10u

CA54

BC847B

TA04

0

RA187

82R

RA103

6k8

OPTRA133

39k

RA164

2k2

+12V_A

RA162

4k7

5

OPT

JA16

180k

RA71

10k

RA87

RA86

22

+12V_A

GND

+3.3V

IA07-2

74LVT125

4

EN

5

6

2k2

RA163

OPTRA101

100R

2k7

RA112

100k

100k

RA91

JA19

1

OPT

BAV21

DA12

CA83

1n0

5

0

OPT

CA33

47u

XA05-4

XA05-10

OPT

RA192

2k2

2

17

CA41

47u

2

0

OPT 0R0

RA123

XA05-14

OPT

RA38

100R

BC337-25

TA13

24

BC847B

TA14

BC807-25

TA26

1k0

RA166

33p

CA09

2

3n3

CA25

CA69

10u

0R0

RA197

OPT

150p

CA20

RA127

33R

RA84

2k7

RA196

0R0

CA60

1u0

LA06

RA157

22k

RA93

470R

10u

CA65

19

10u

10u

0R0

RA75

XA02-1

1k5

RA199

220p

CA90

LA08

470p

+12V_OP

GND

2k2

RA36

OPT

TA03

BC857B

CA87

0R0

RA193

OPT

68R

RA182

RA49

0R0

CA16

220p

15k

RA114

12

2k2

RA48

47R

+12V

11

XA02-3

2k2

RA190

BC857B

TA10

RA170

33R

RA128

75R

RA81

OPT

JA17

XA05-2

1u0

CA27

RA12

82R

RA07

820R

OPT

CA14

150p

82R

RA08

RA05

A4

20

2

+3.3V

OPT

180R

RA153

+12V_A

OPT

RA25

100R

100R

33R

RA118

10k

7

A6

4k7

RA161

RA130

2k2

RA191

CA56

1u0

0R0

RA175

4

47u

CA40

OPT

RA125

47k

RA74

2k2

RA155

100k

RA142

10k

XA05-6

12

VCT

18

VCT1

3

VCT2

16

VRIN1

5

VRIN2

CA50

10u

CXA1846

IA06

7

CE

9

CLK

8

DATA

13

GND

17

INAO1

4

INAO2

10

INIT

19

INN1

2

INN2

20

INP1

1

INP2

15

OUT1

6

OUT2

11

VCC

10

Q6

11

Q7

12

VCC

16

1

OPT

RA24

4k7

A0

1

A1

2

A2

3

D

13

GND

8

LE

14

MR

15

Q0

4

Q1

5

Q2

6

Q3

7

Q4

9

Q5

RA41

100R

75R

RA83

IA04

74LV259

CA86

1u0

RA17

0R0

1u0

CA57

1R0

RA172

68p

CA17

1k0

RA167

33R

RA129

74LVT125

IA07-1

+3.3V

GND

EN

1

2

3

33p

CA21

10u

CA51

220R

RA178

10

OPT

RA168

1k0

31

VOUT5

29

VOUT6

27

VOUT7

33

VOUT8

56

VREG_9V

57

VREG_BASE

LA01

3u9

62

VIN1

8

VIN10

16

VIN11

24

VIN12

18

VIN2

64

VIN3

20

VIN4

2

VIN5

6

VIN6

14

VIN7

22

VIN8

4

VIN9

54

VOUT1