8 bitowe mikrokontrolery rodziny AVR

Dariusz Chaberski

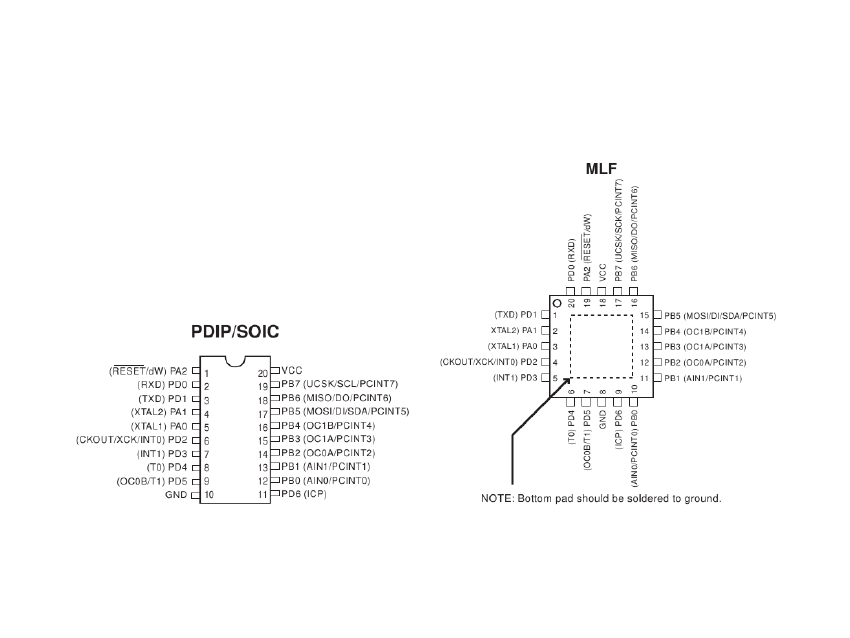

ATtiny 2313

2

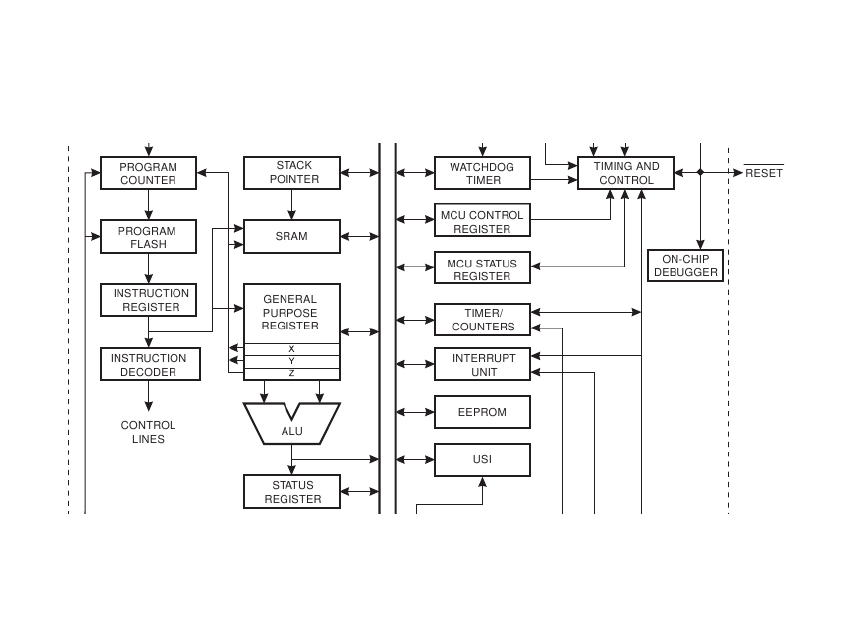

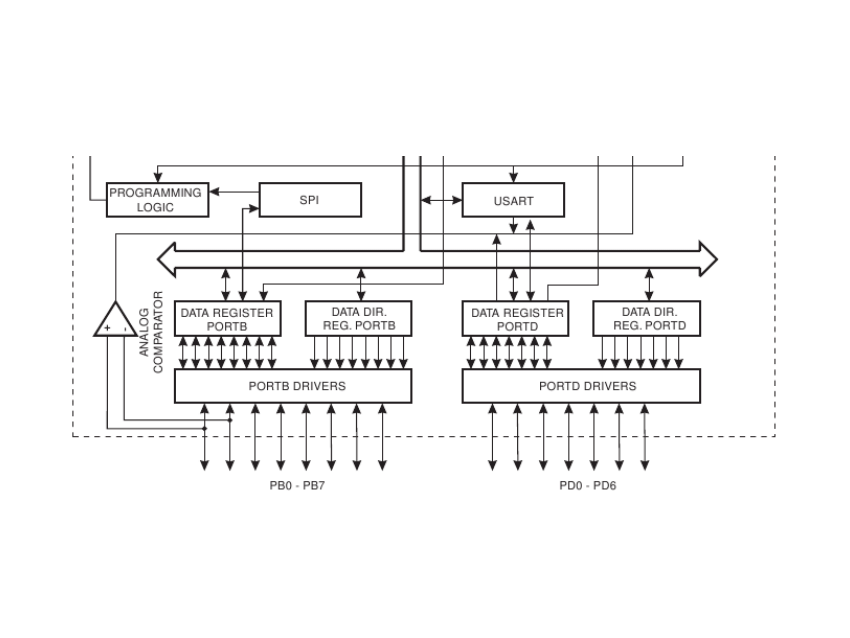

§ Block Diagram

3

4

5

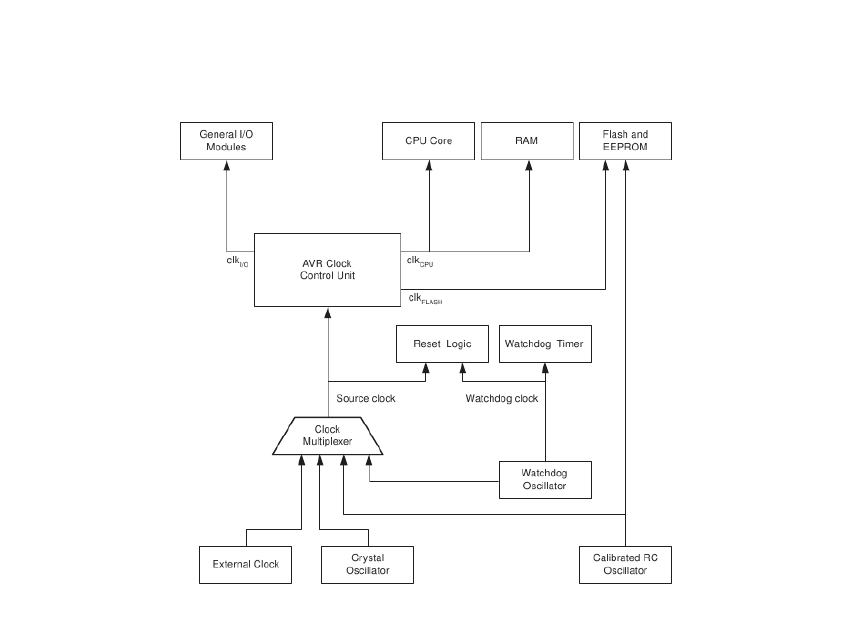

§ System Clock and Clock Options

6

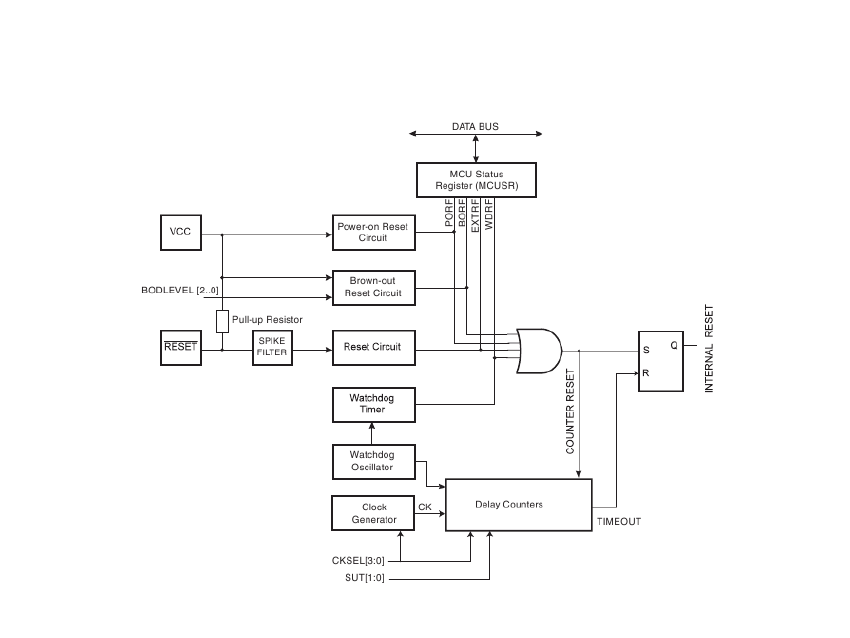

§ Reset Sources

7

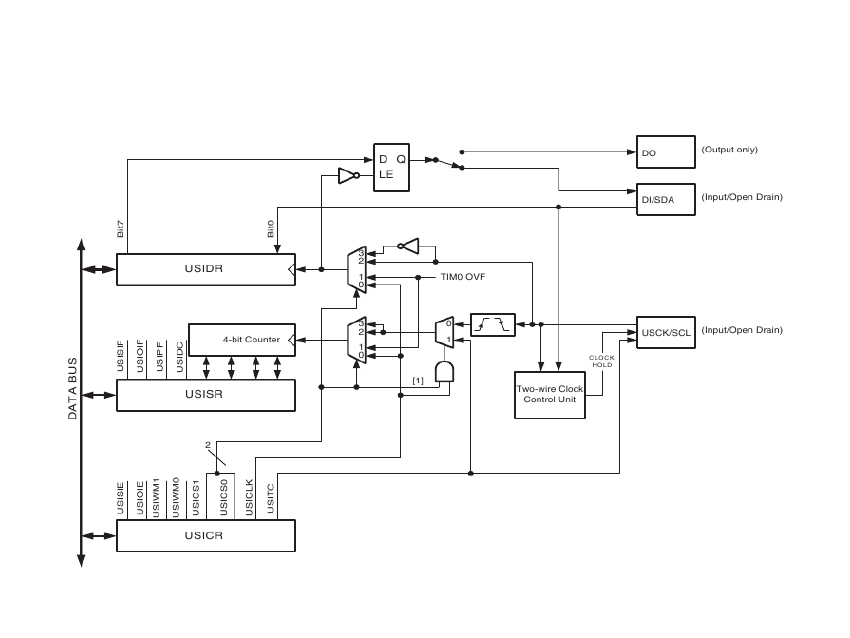

§ Universal Serial Interface

8

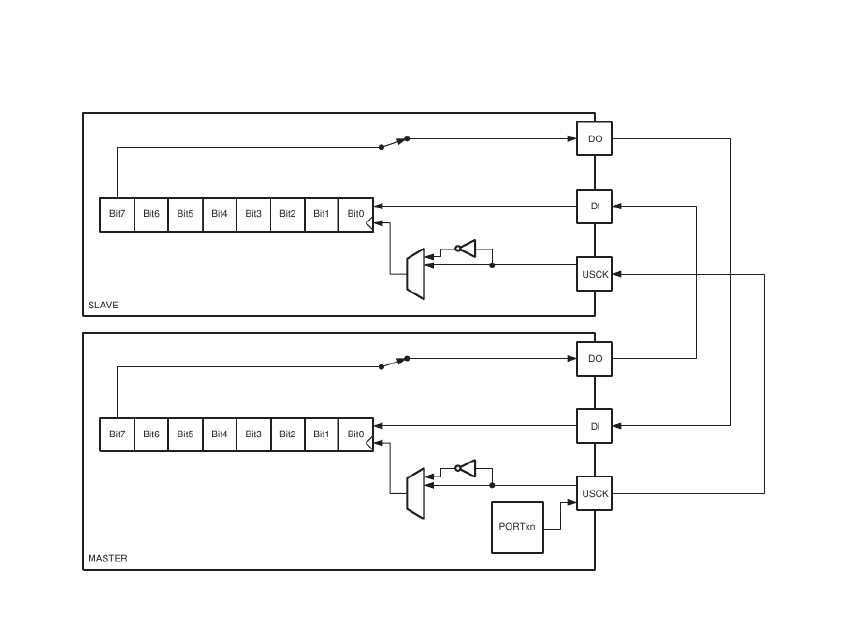

Three-wire Mode

9

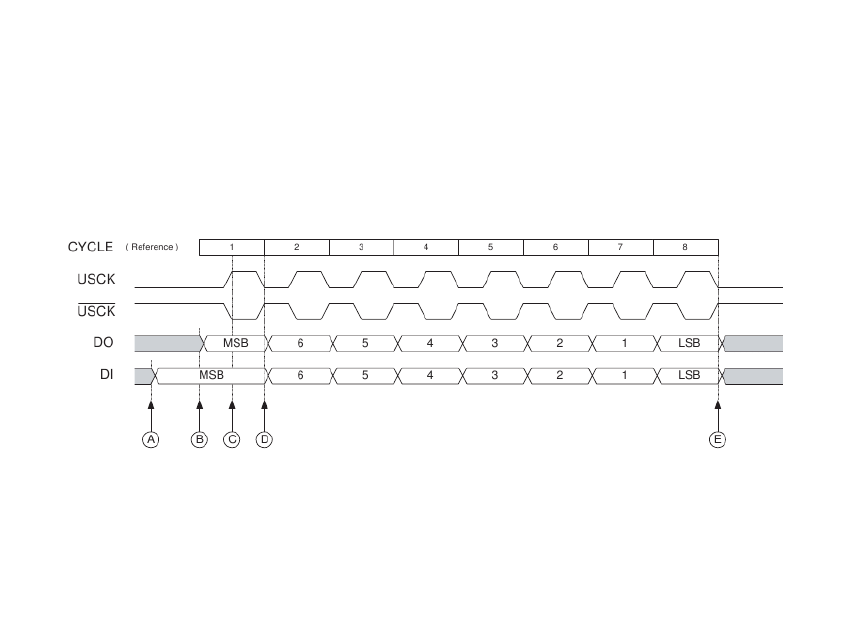

Three-wire Mode, Timing Diagram

10

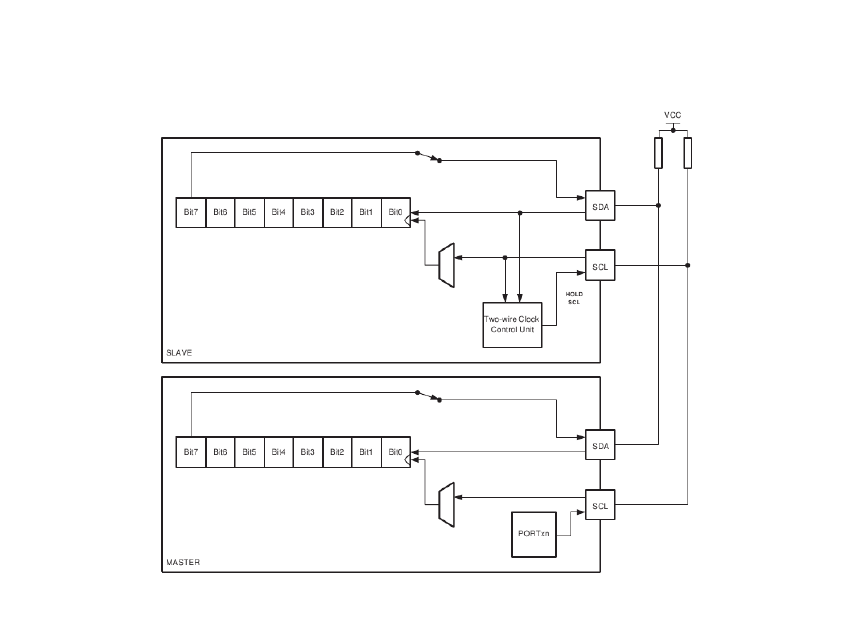

Two-wire Mode

11

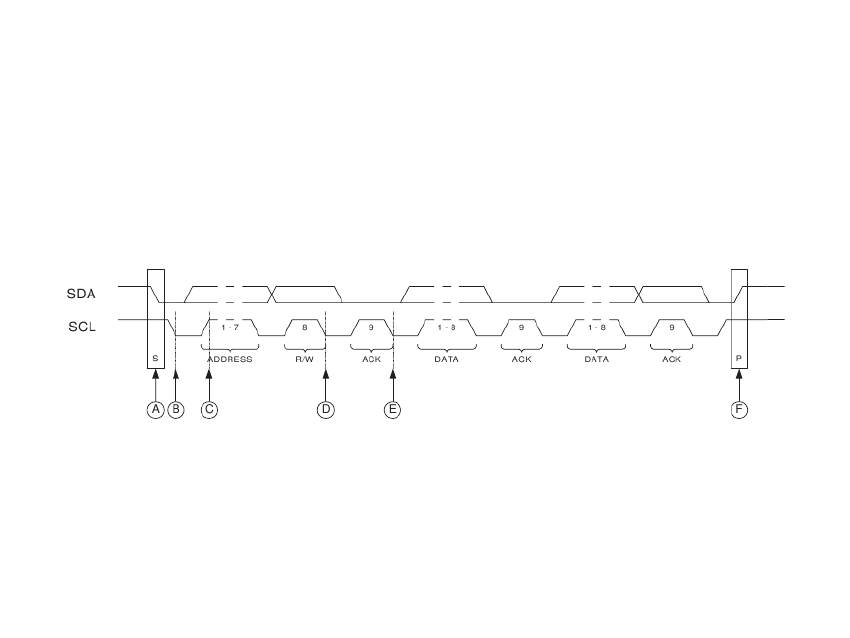

Two-wire Mode, Typical Timing Diagram

12

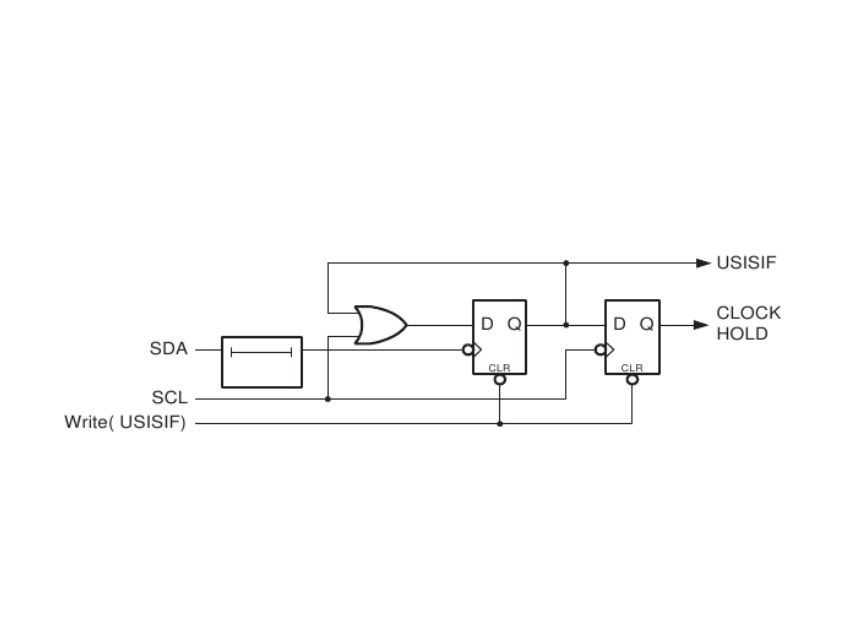

Start Condition Detector, Logic Diagram

13

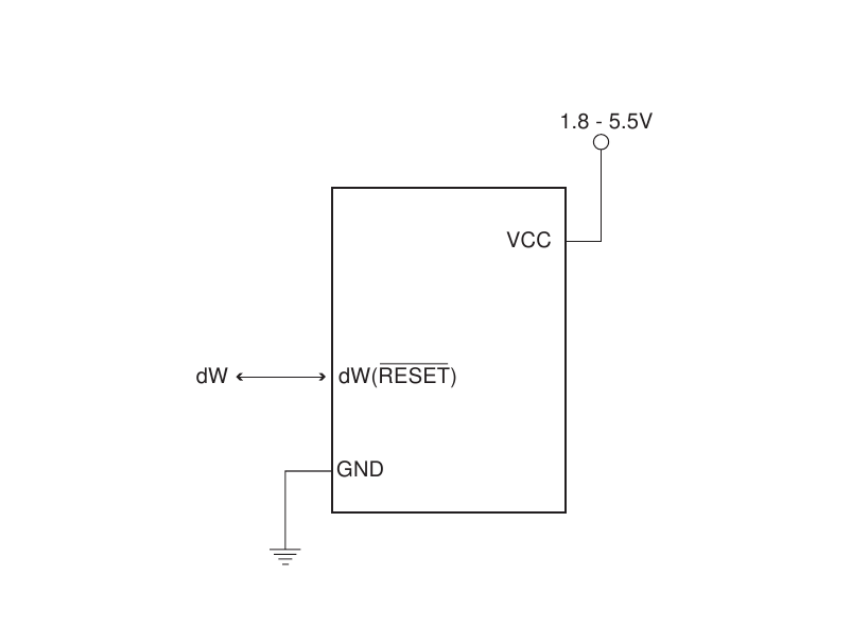

§ debugWIRE On-chip Debug System

14

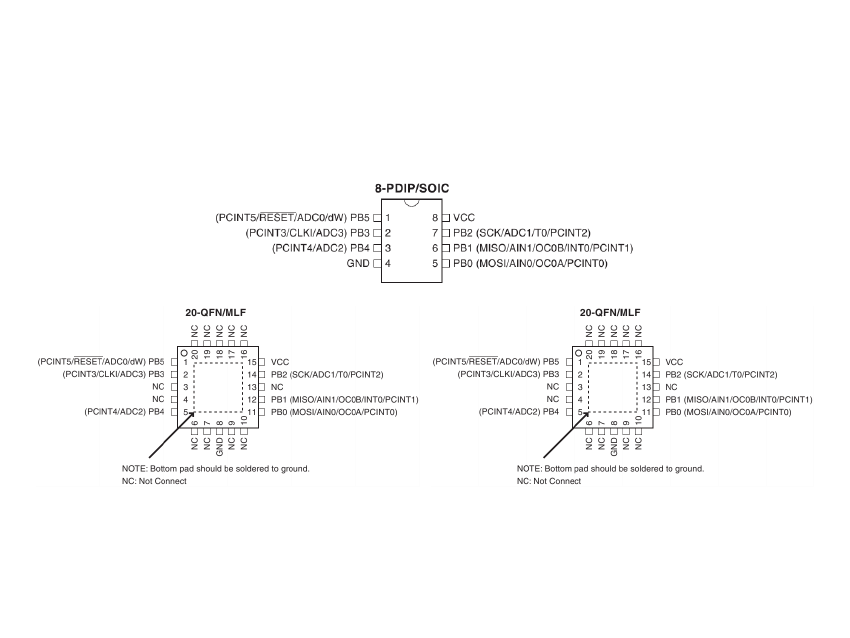

ATtiny 13

15

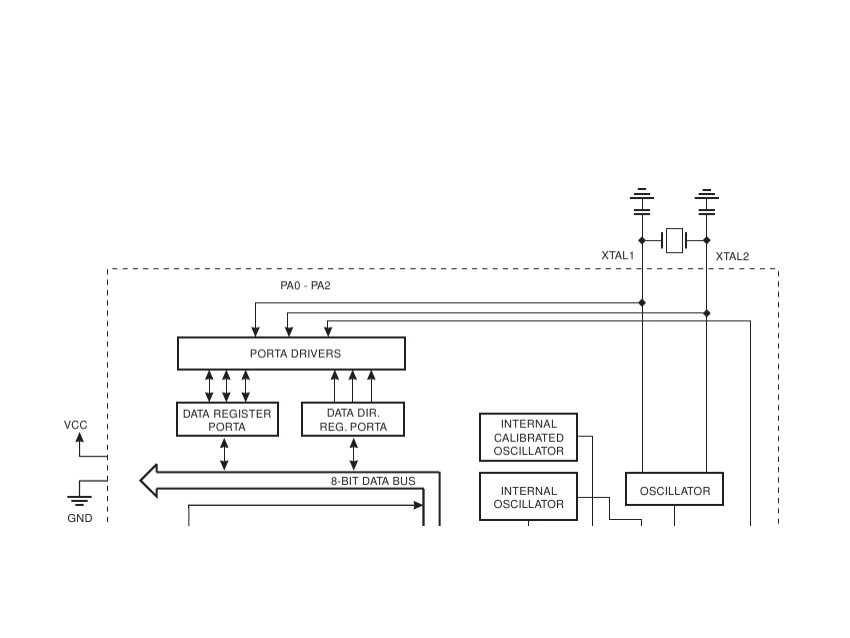

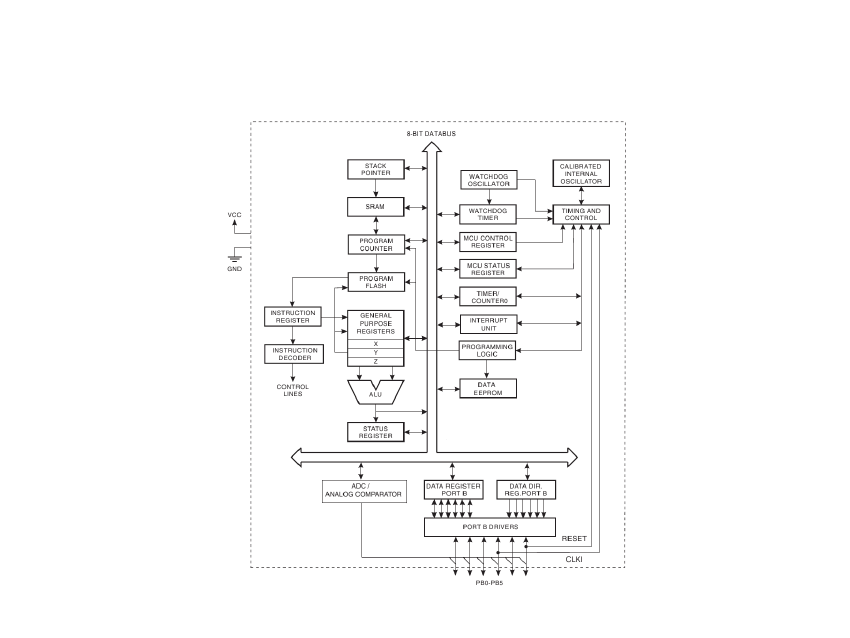

§ Block Diagram

16

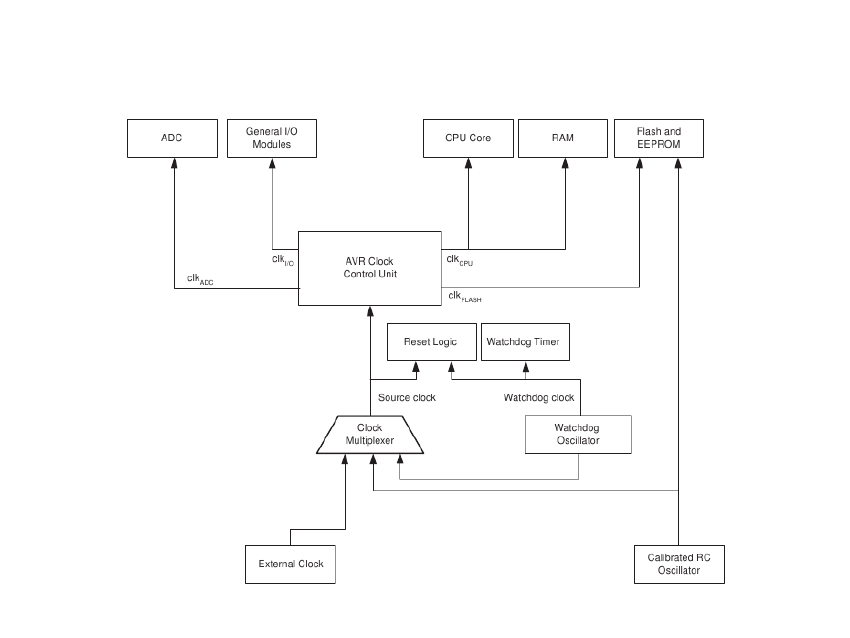

§ Clock Distribution

17

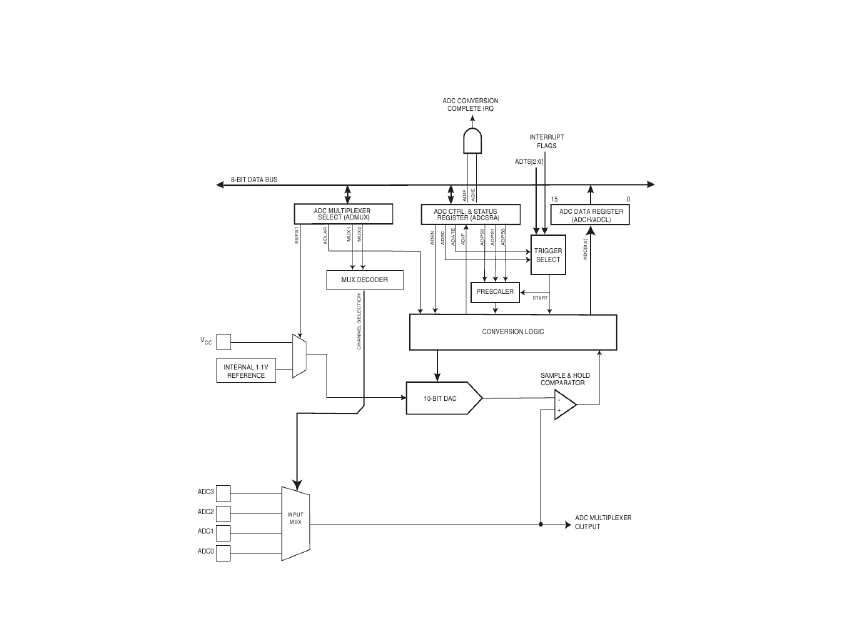

§ Analog to Digital Converter

18

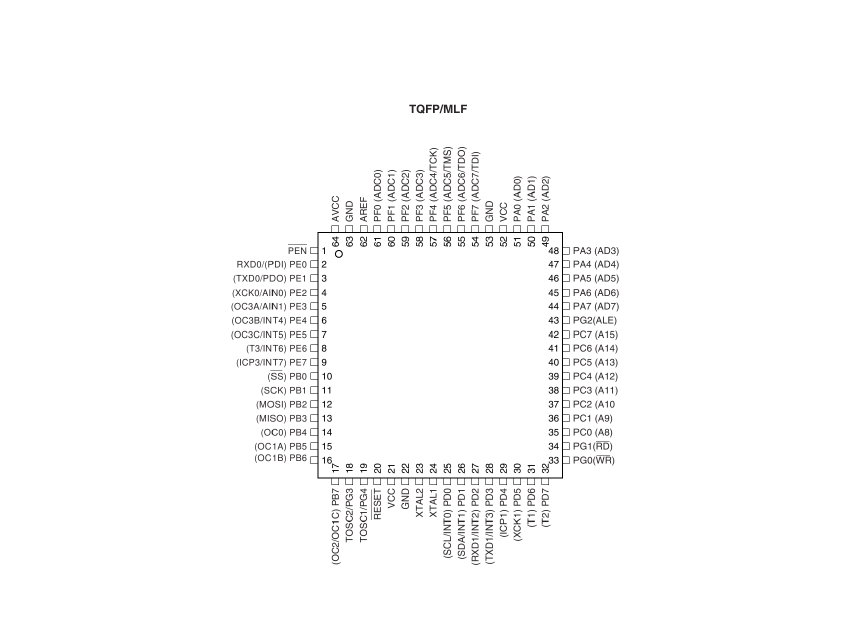

ATmega 64

19

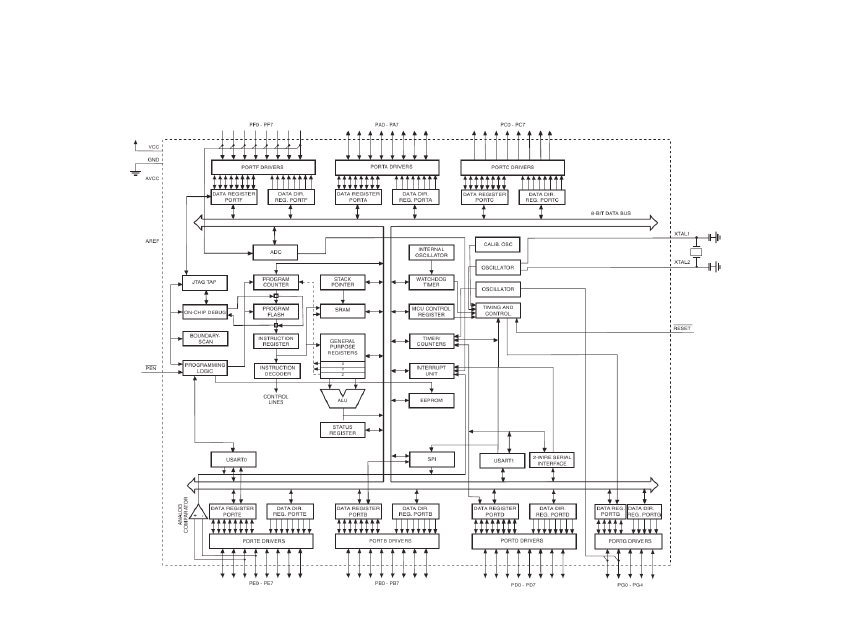

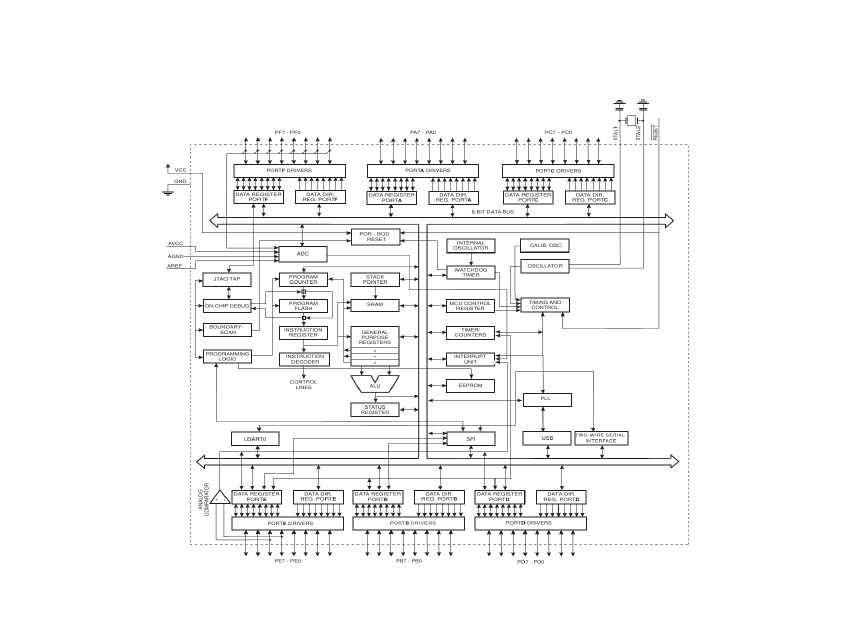

§ Block Diagram

20

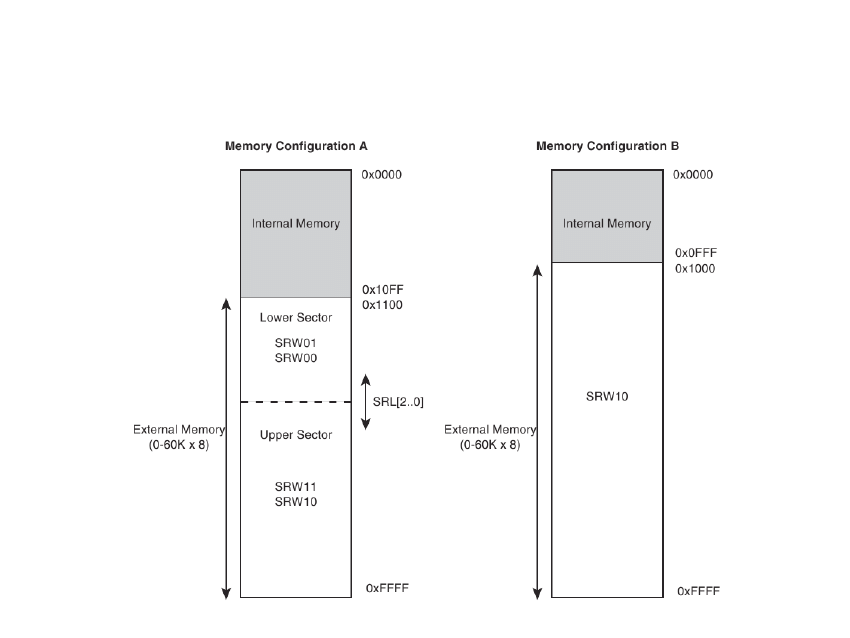

§ External Memory Interface

External Memory with Sector Select

21

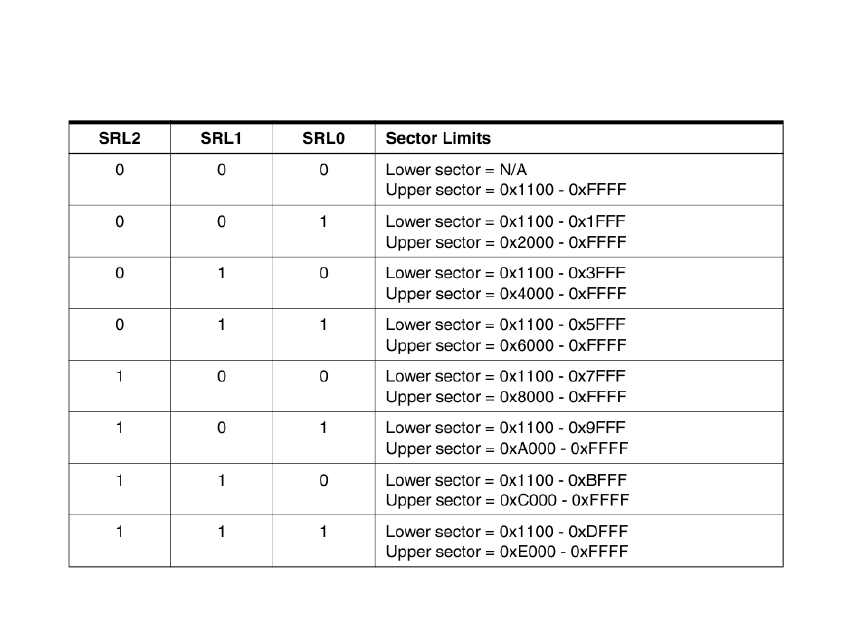

Sector Limits with Different Settings of SRL2..0

22

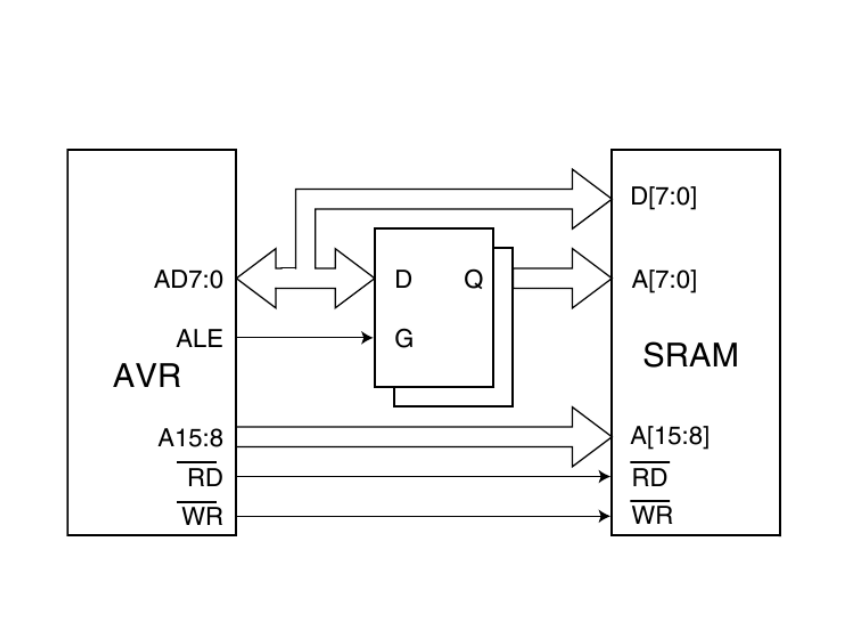

External SRAM Connected to the AVR

23

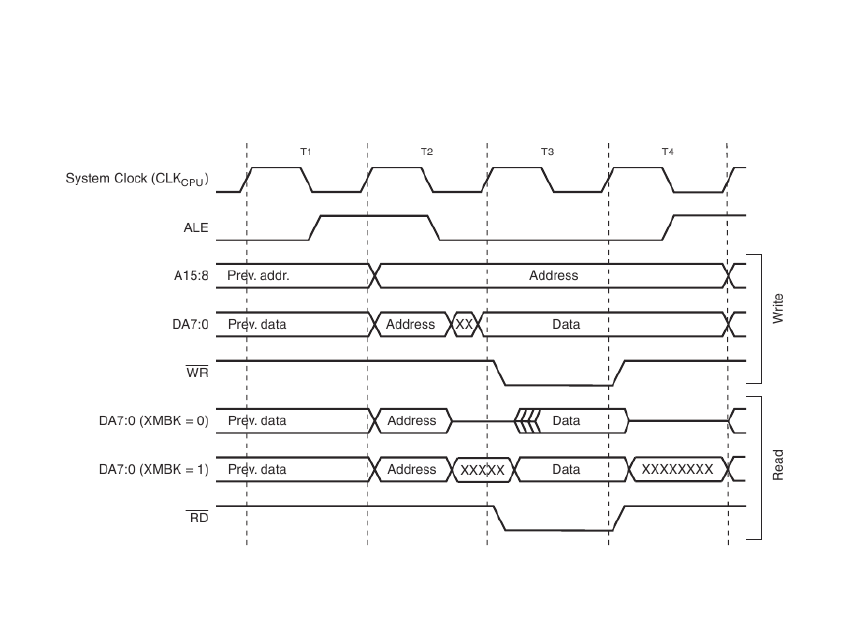

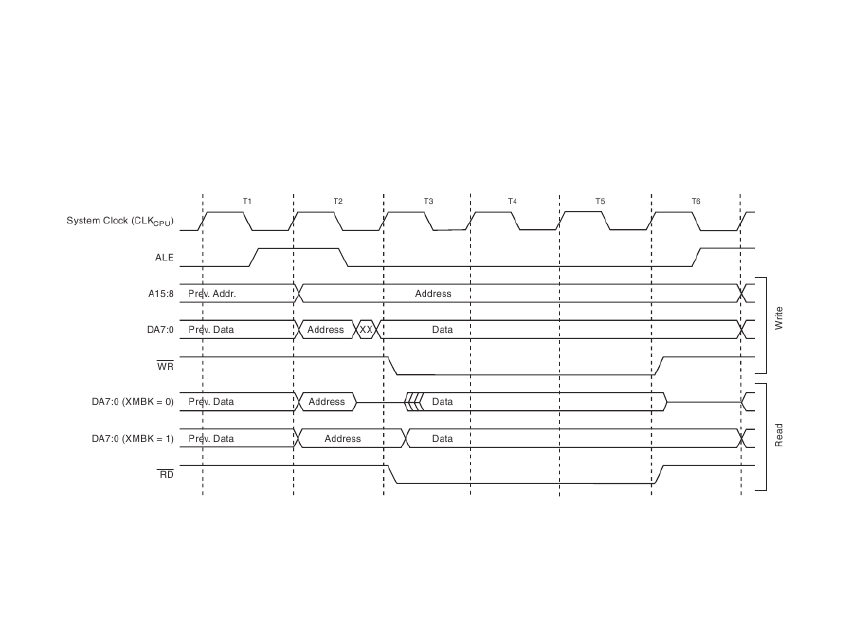

External Data Memory Cycles without Wait State (SRWn1 = 0 and SRWn0 =0)

24

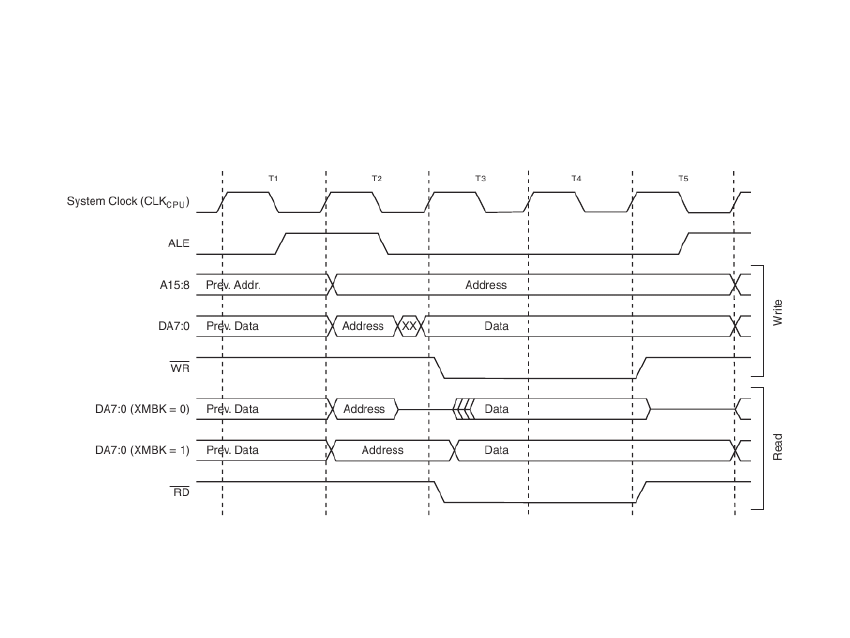

External Data Memory Cycles with SRWn1 = 0 and SRWn0 = 1

25

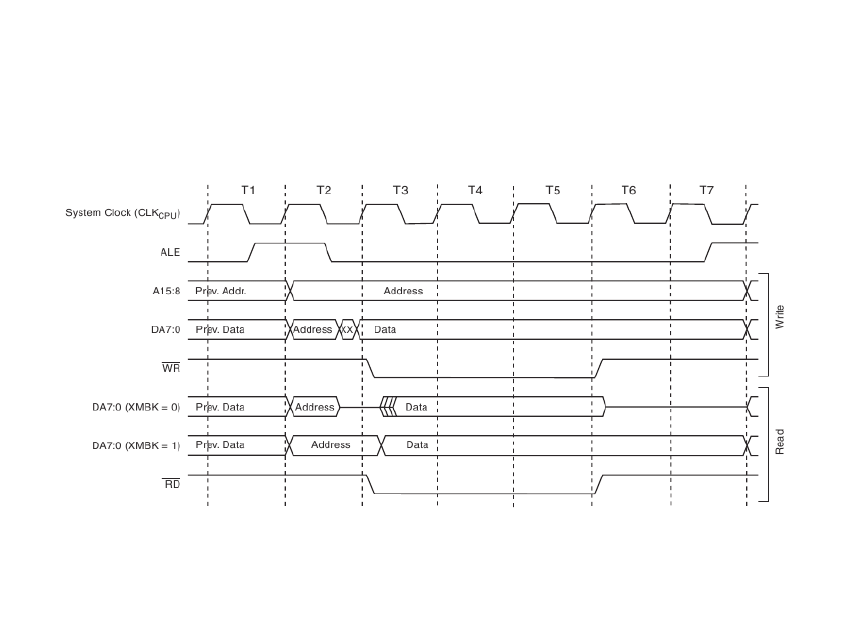

External Data Memory Cycles with SRWn1 = 1 and SRWn0 = 0

26

External Data Memory Cycles with SRWn1 = 1 and SRWn0 = 1

27

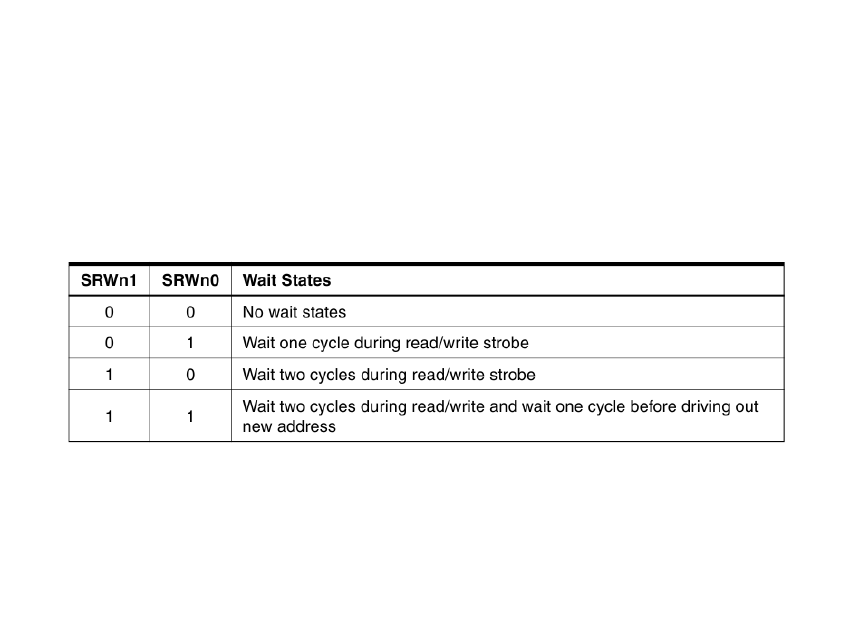

§ Wait States

28

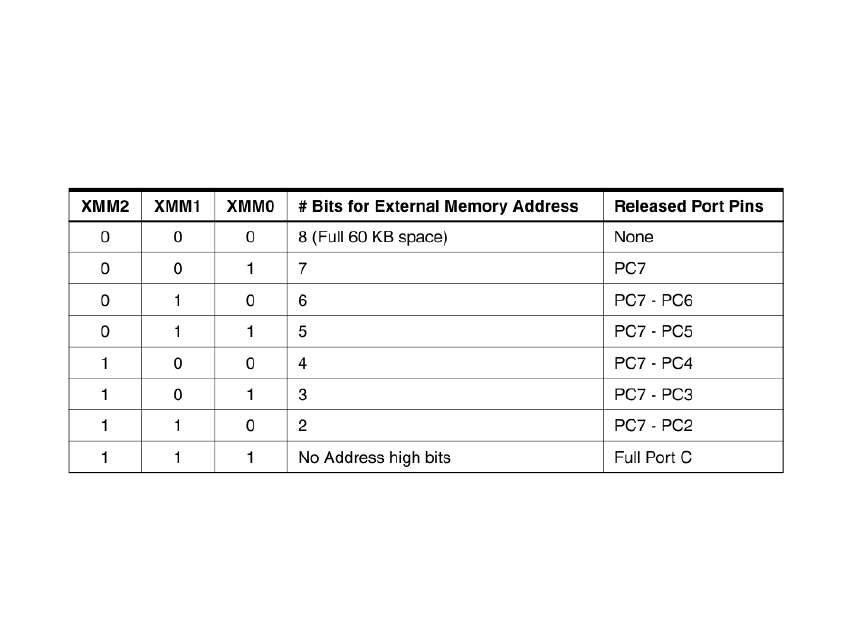

§ Port C Pins Released as Normal Port Pins when the External Memory is Enabled

29

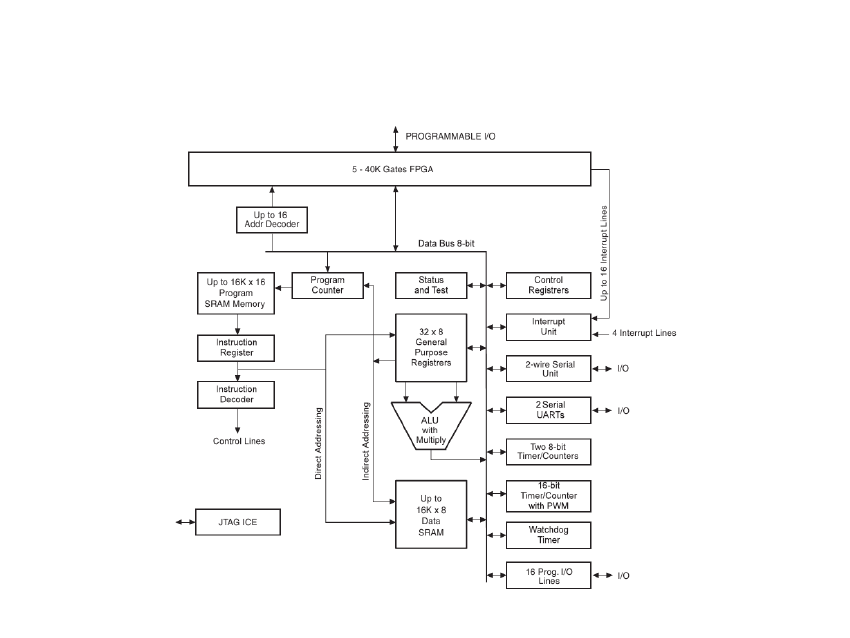

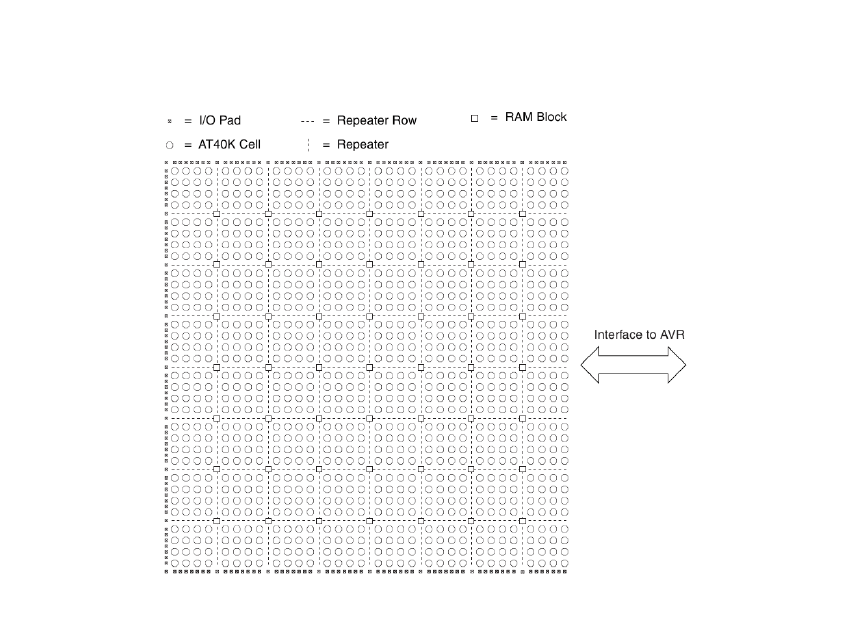

AT94KAL Series Field Programmable

System Level Integrated Circuit

30

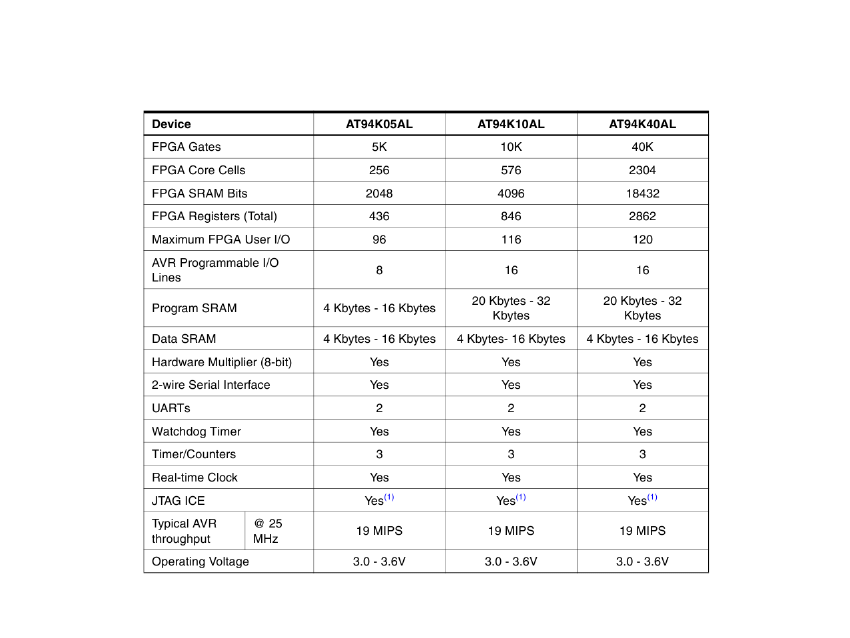

The AT94K Series Characteristics

31

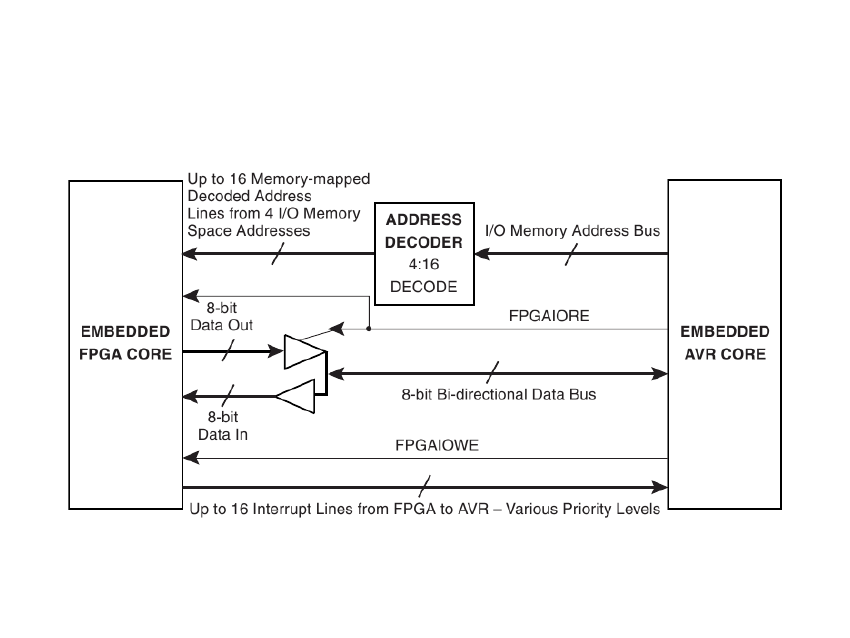

FPGA/AVR Interface: Interrupts and Addressing

32

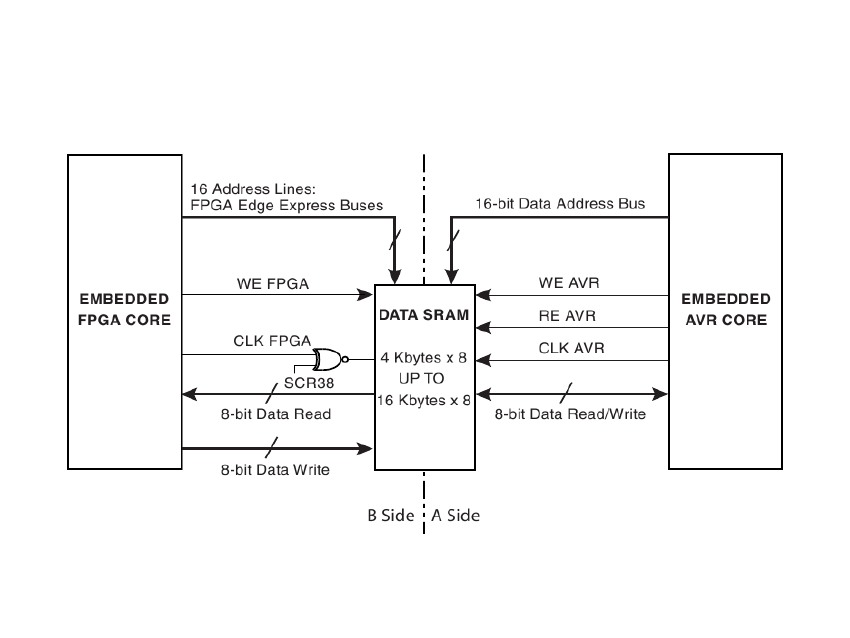

Internal SRAM Access - Normal Use

33

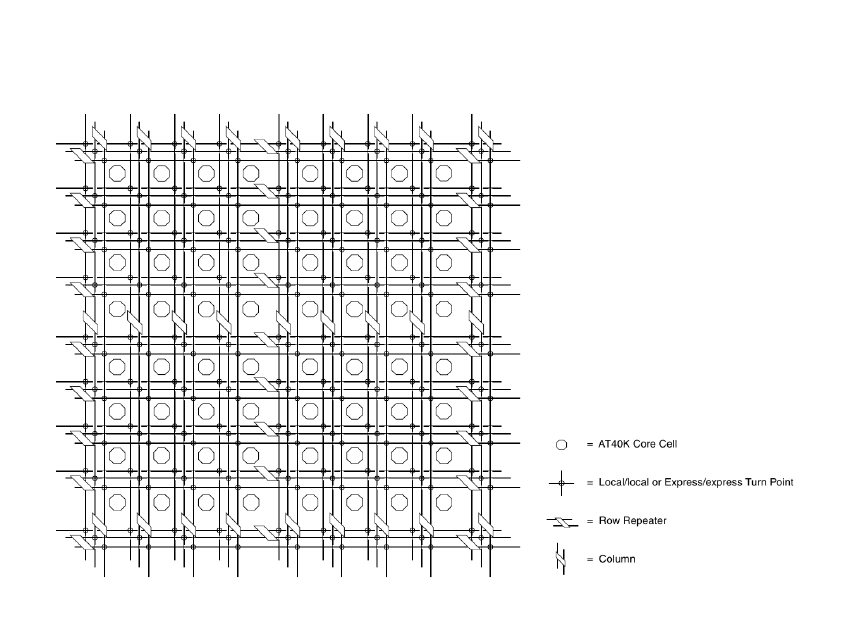

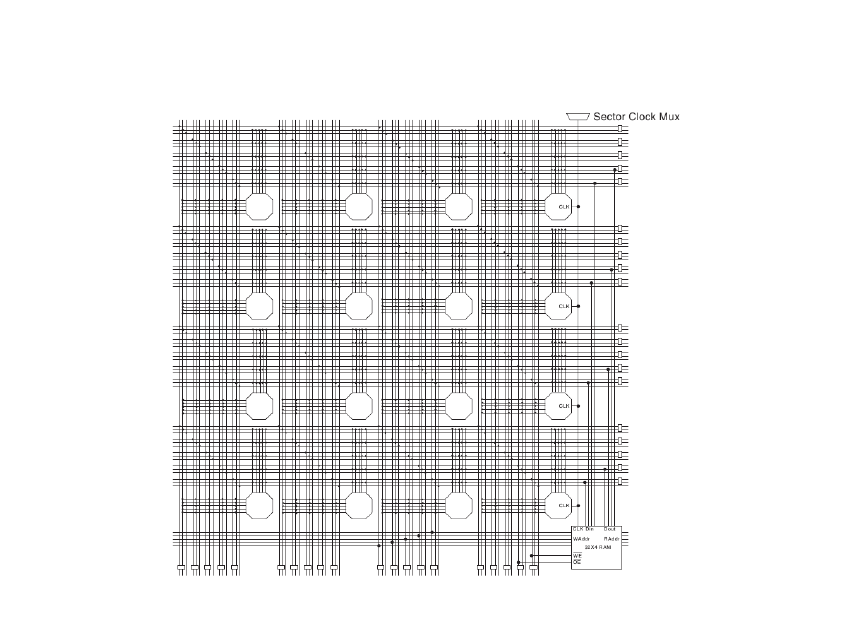

Busing Network

34

Busing Plane (One of Five)

35

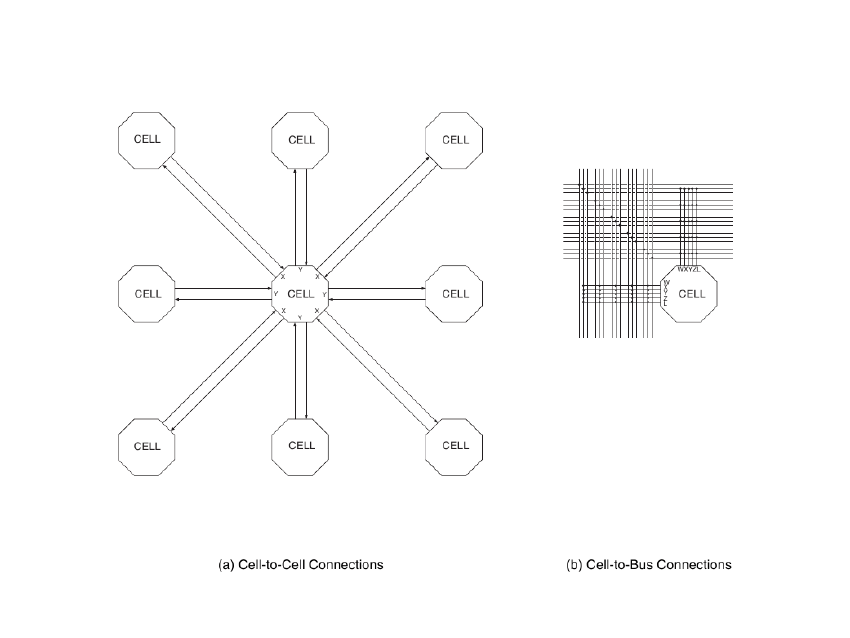

Cell Connections

36

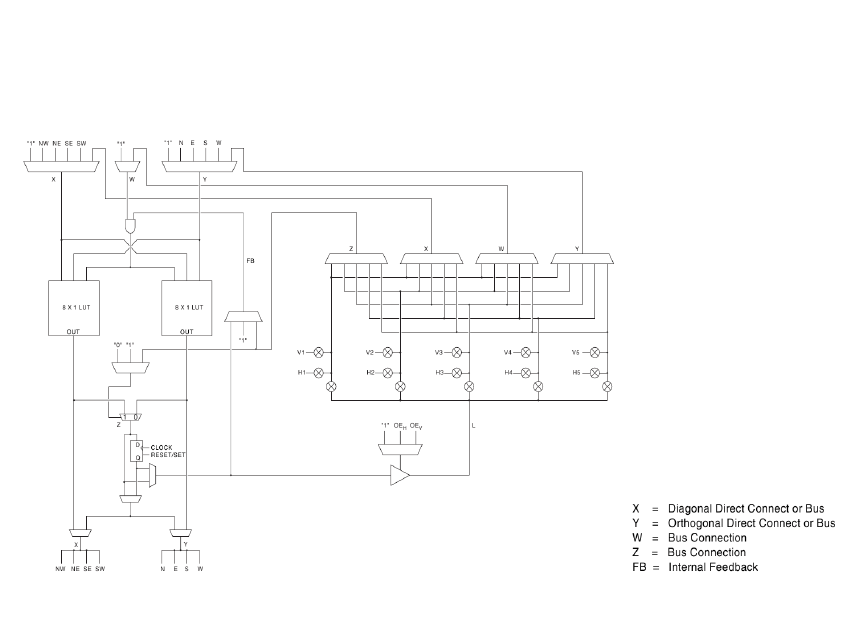

The Cell

37

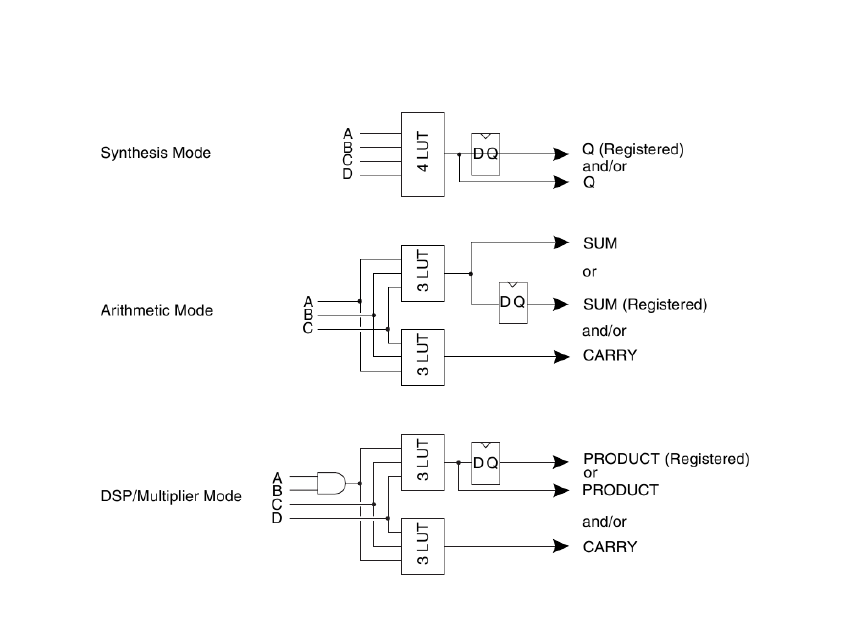

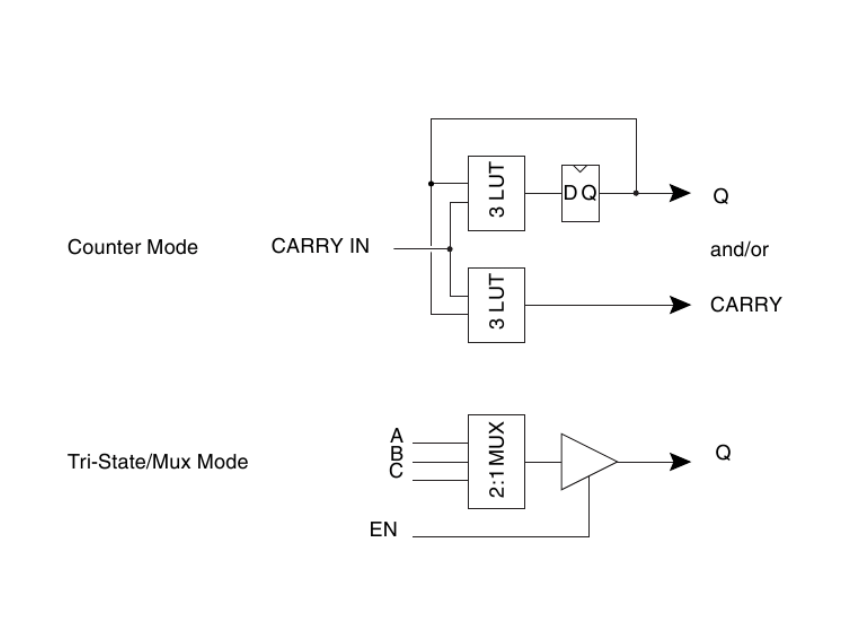

Some Single Cell Modes

38

39

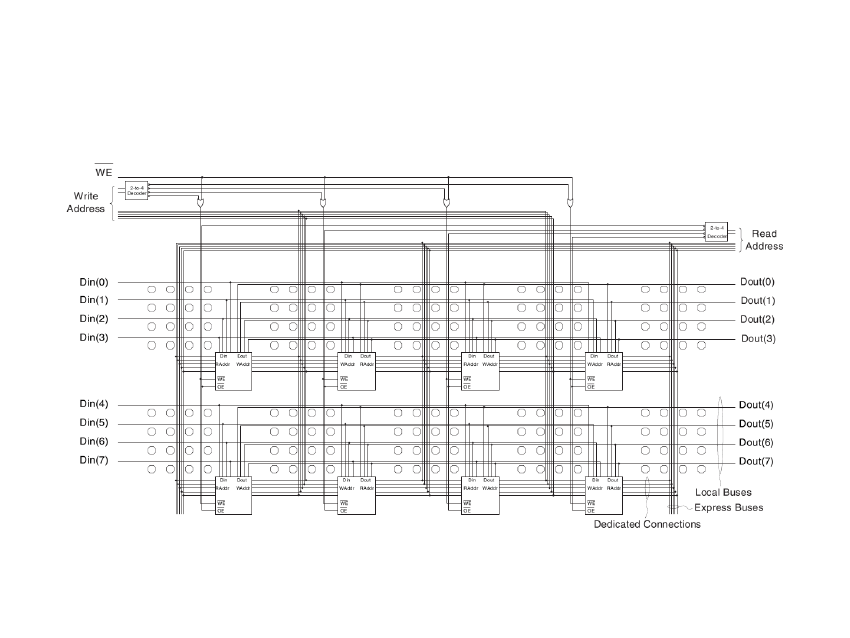

FPGA RAM Connections (One RAM Block)

40

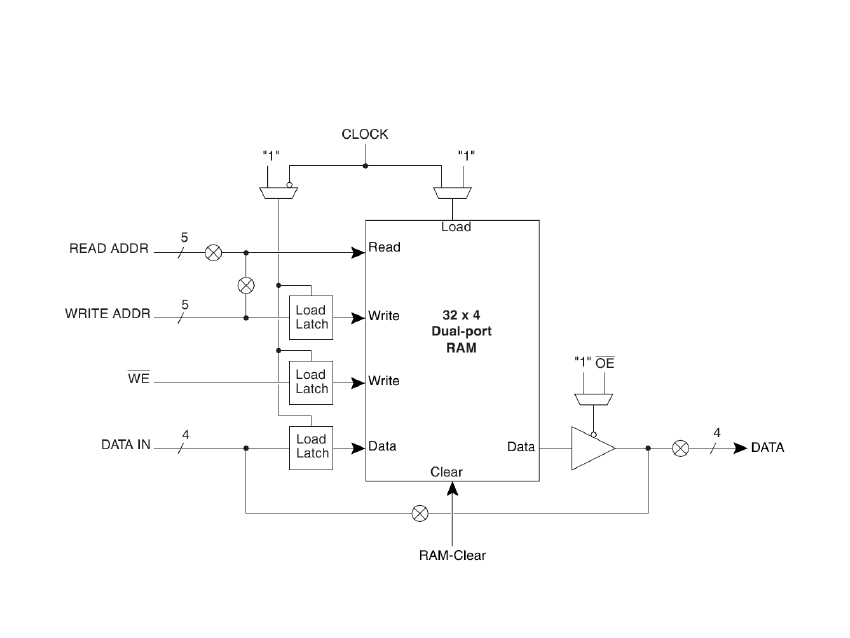

FreeRAM Logic

41

FreeRAM Example: 128 x 8 Dual-ported RAM (Asynchronous)

42

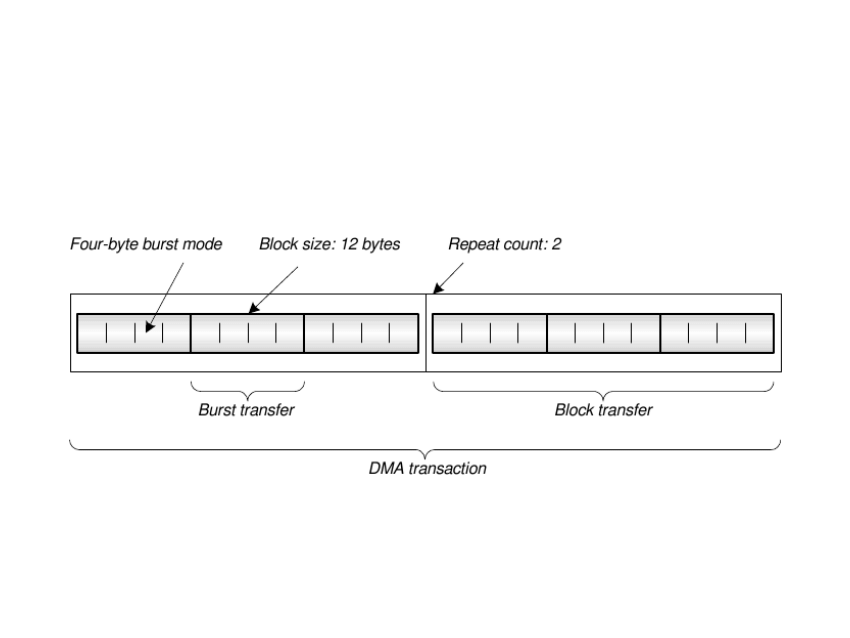

ATxmega

§ Direct Memory Access Controller

43

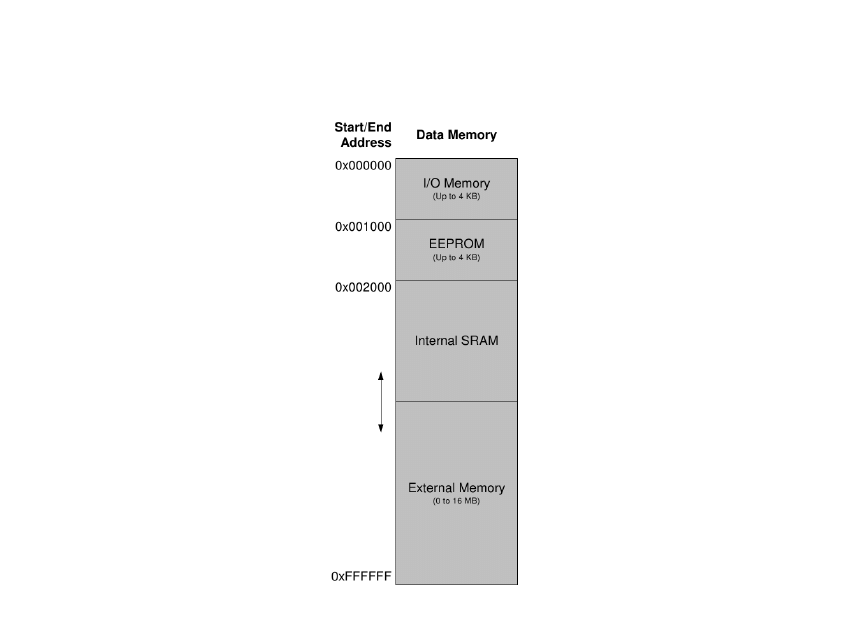

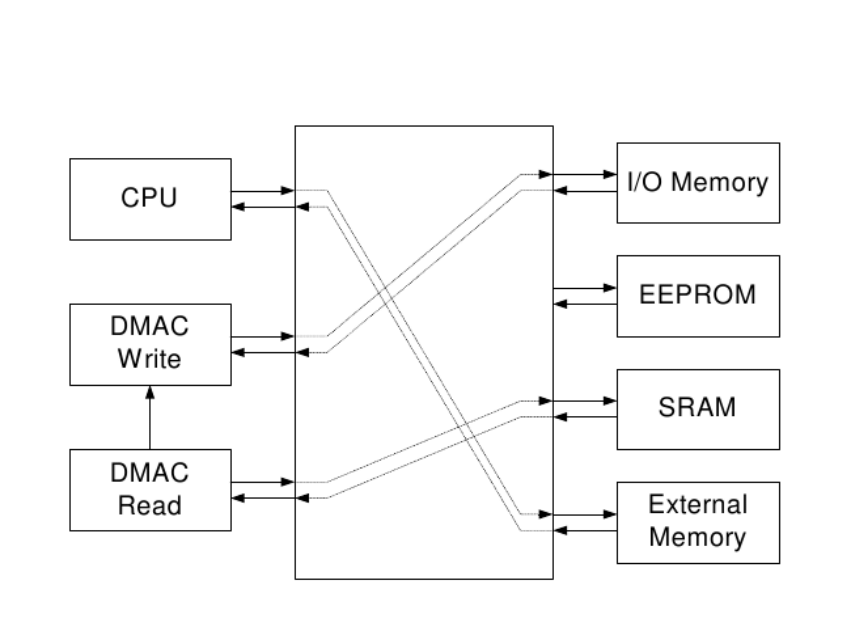

§ Data Memory Map

44

§ Bus Access

45

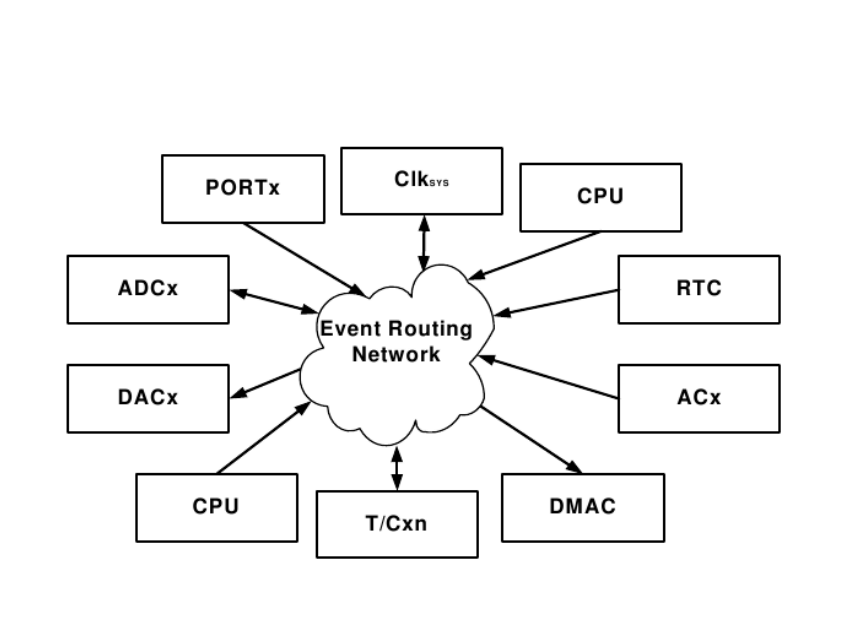

§ Event System

46

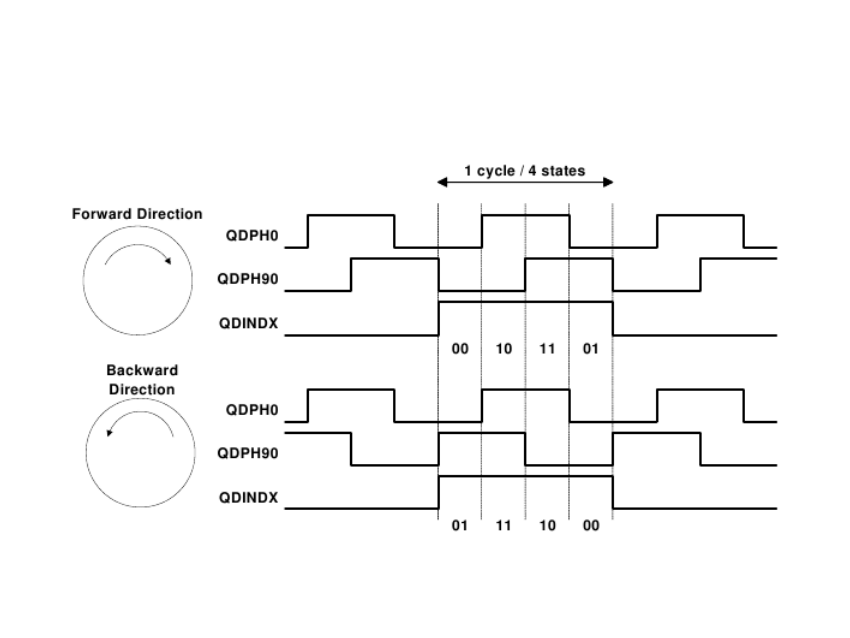

Quadrature signals from a rotary encoder

47

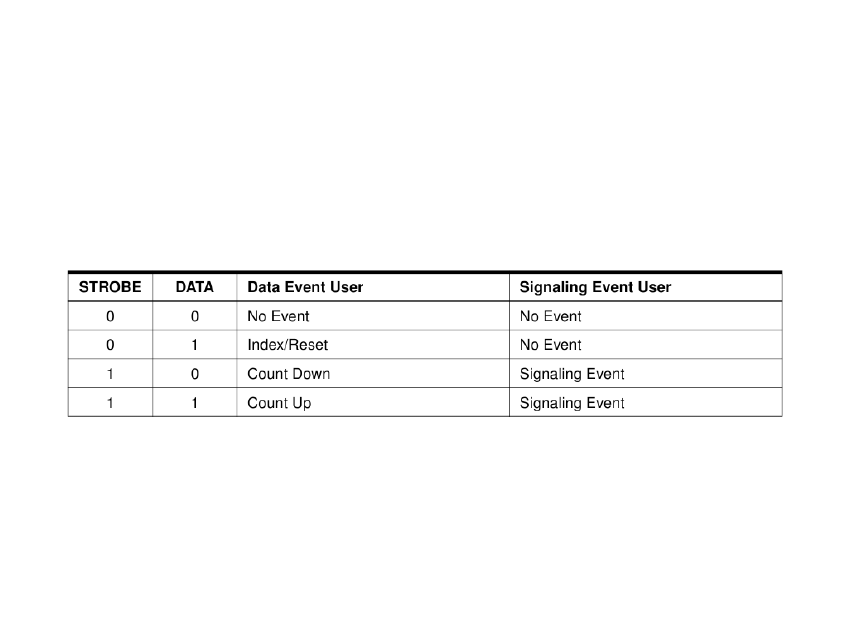

Quadrature Decoder Data Events

48

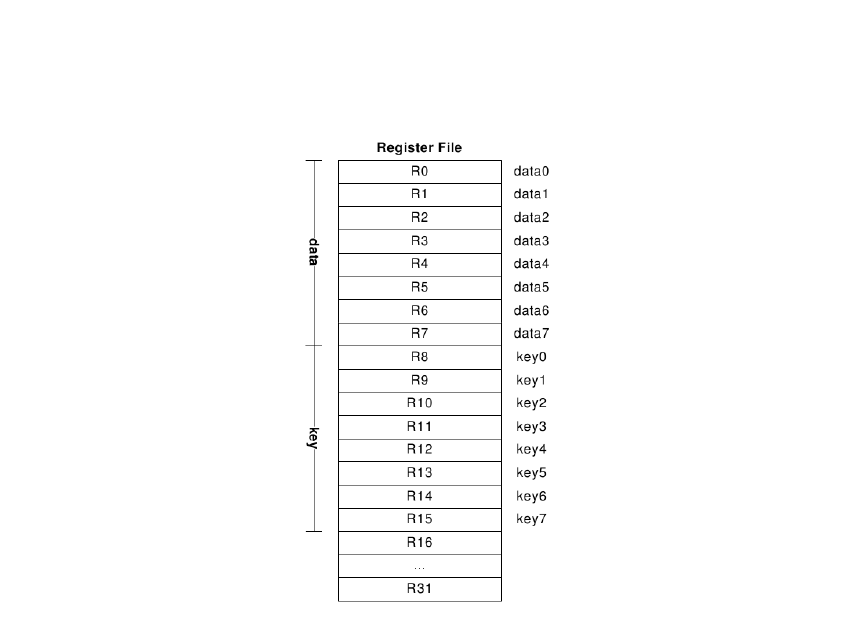

§ Crypto Engines

DES Instruction - Register file usage during DES encryption/decryption

49

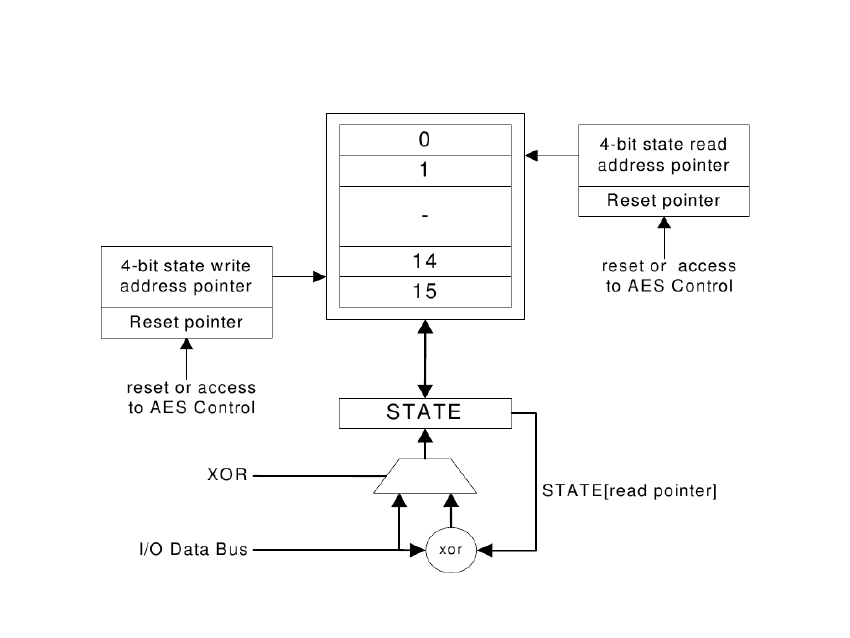

AES Crypto Module - The State memory with pointers and register

50

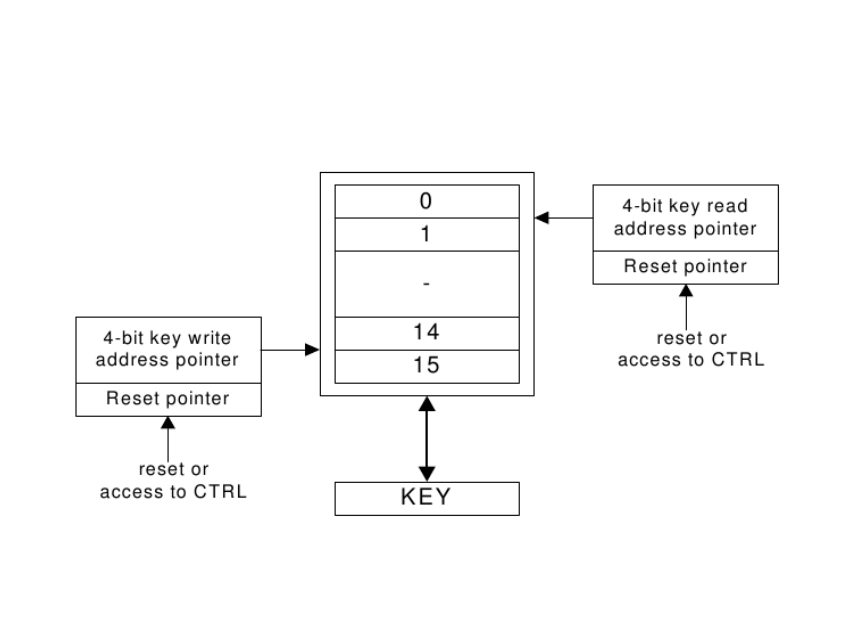

The Key memory with pointers and register

51

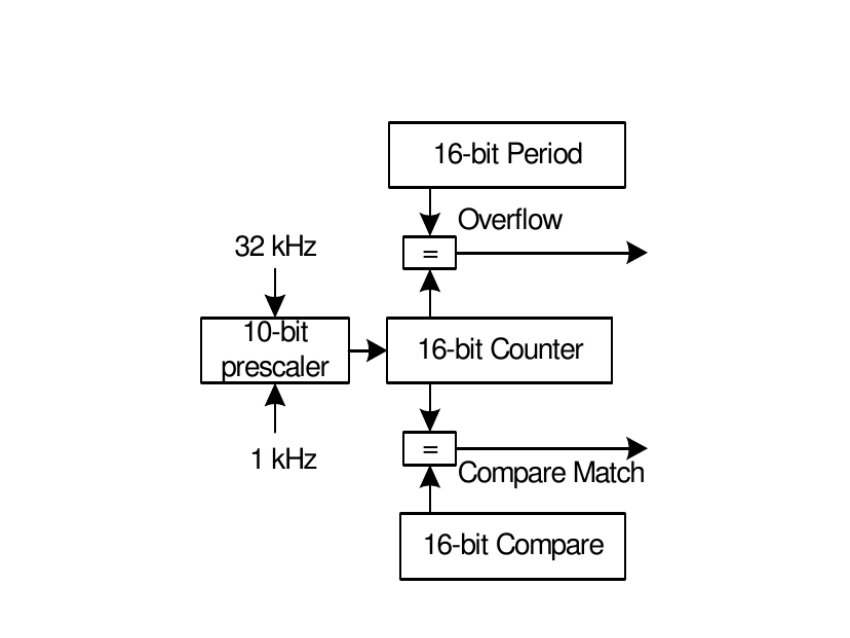

§ Real Time Counter

52

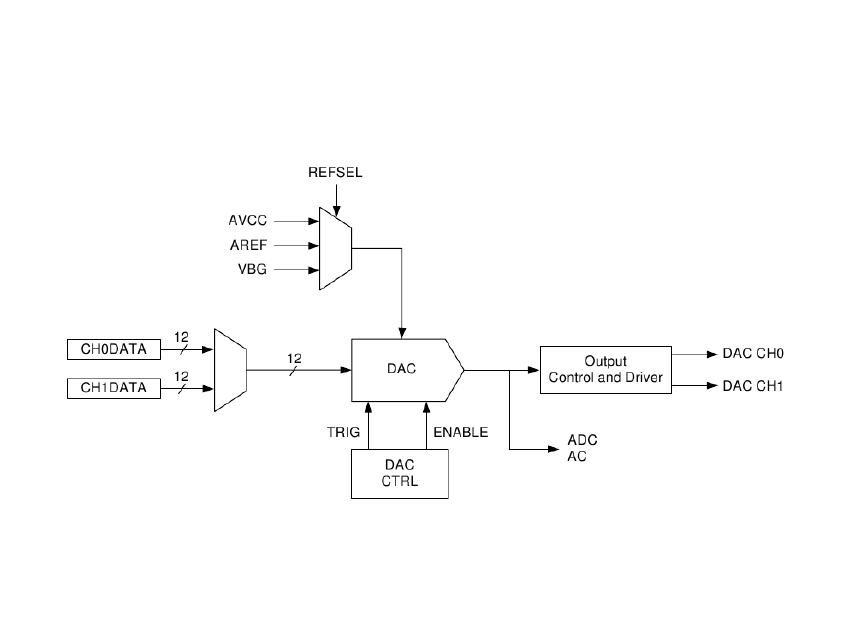

§ Digital to Analog Converter

53

AT90USB1287

54

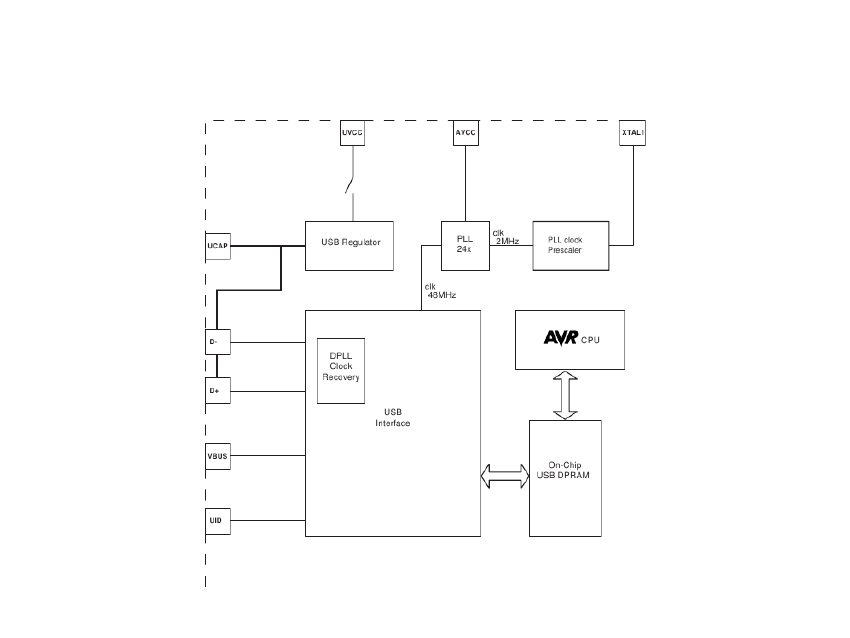

§ USB controller Block Diagram overview

55

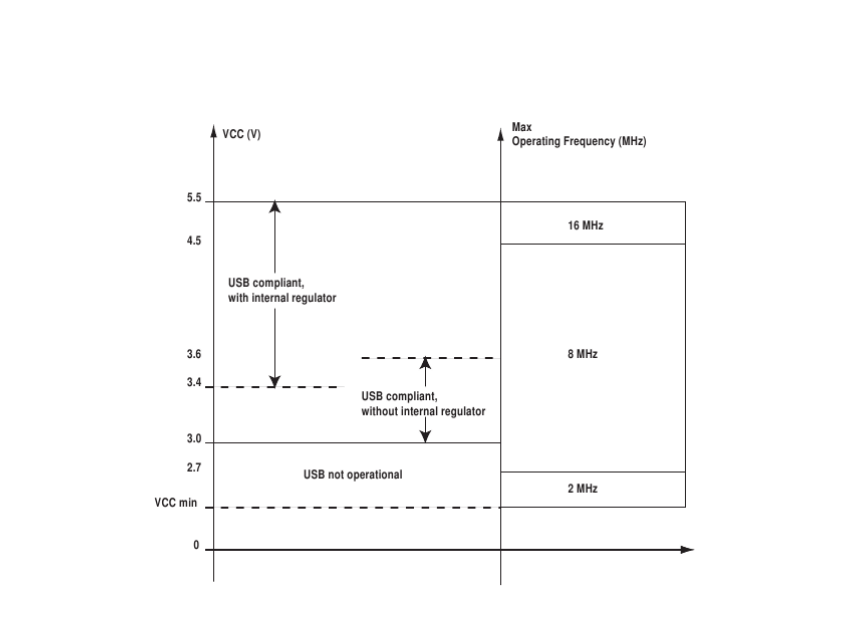

§ Operating modes versus frequency and power-supply

56

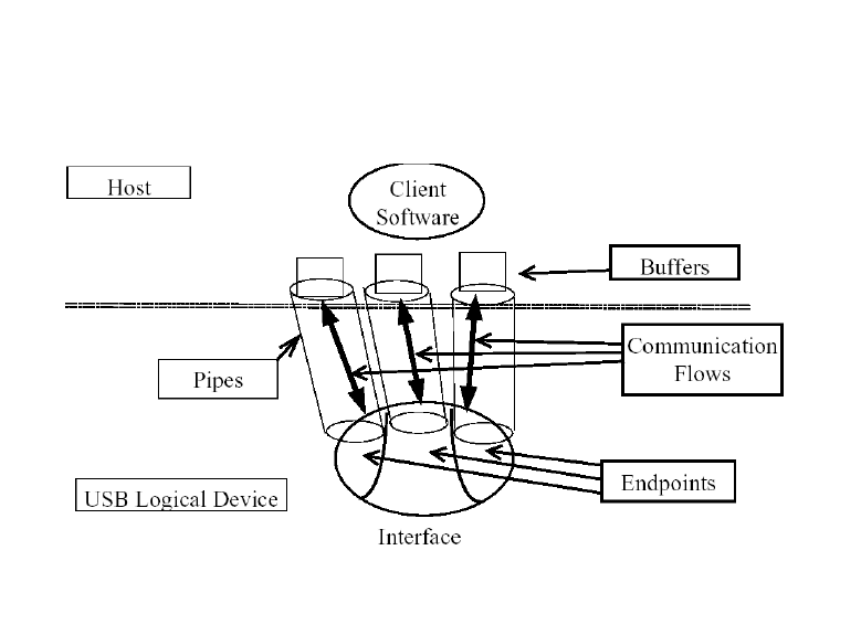

§ Pipes and Endpoints in a USB system

57

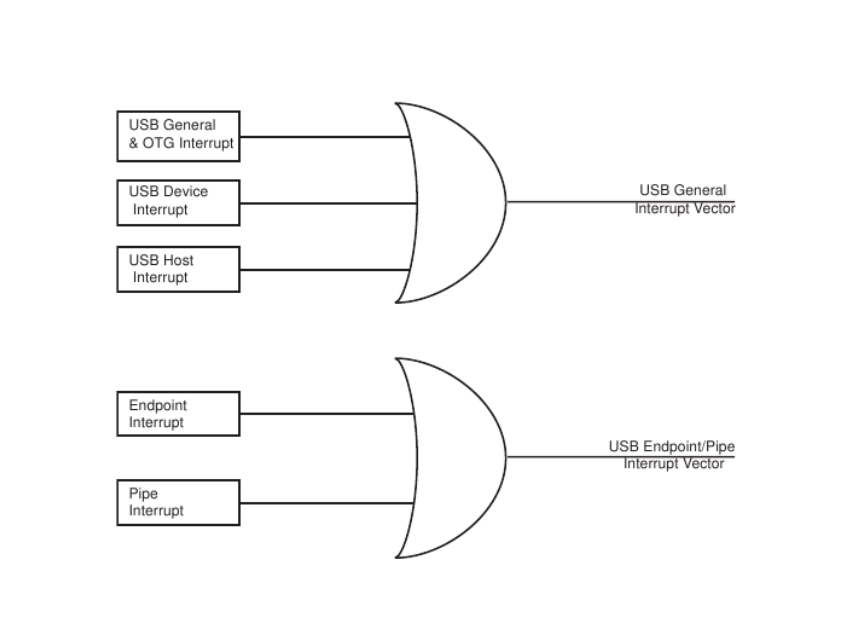

§ USB Interrupt System

58

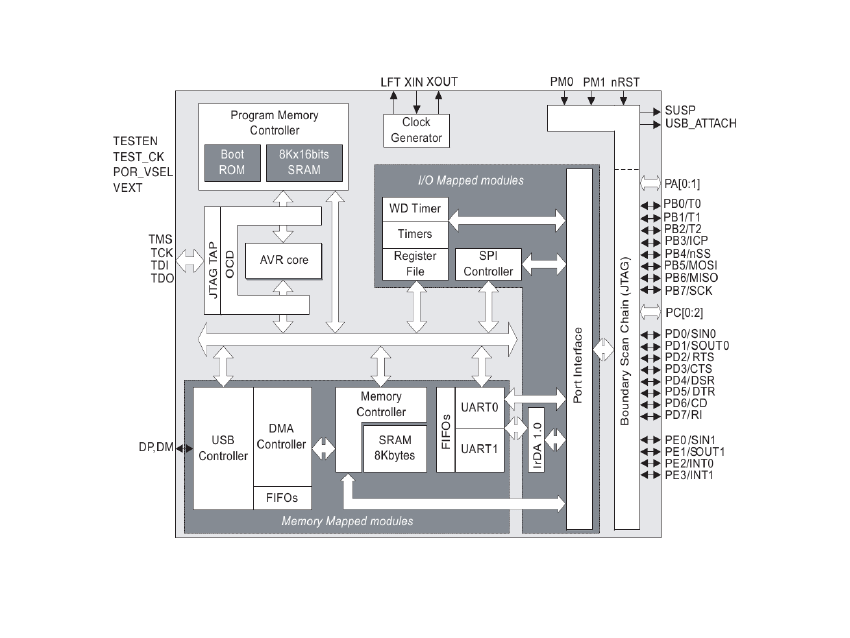

AT76C712

59

Wyszukiwarka

Podobne podstrony:

32 32 bitowe mikrokontrolery rodziny AVR

09 8 bitowe mikrokontrolery rodziny PIC

Mikrokontrolery rodziny AVR w obudowach 8 wyprowadzeniowych

Mikrokontrolery rodziny AVR w obudowach 8 wyprowadzeniowych

06 ERGONOMIA MIKROKLIMAT

fras,systemy wbudowane L, Wstęp do mikrokontrolerów rodziny MCS 51

08 mikrokontrolery rodziny 8051

10 mikrokontrolery rodziny M68

06 ERGONOMIA MIKROKLIMAT

2012 06 15 Renta rodzinna i socjalna komu się należy

Bootloader dla mikrokontrolerów AVR

evboard, Płytka testowa dla mikrokontrolerów AT89S oraz AVR

06. Czynniki ryzyka zespołu metabolicznego, Uczelnia, rodzinna

więcej podobnych podstron