Zagadnienia obowiązujące do części „Mikroprocesory”.

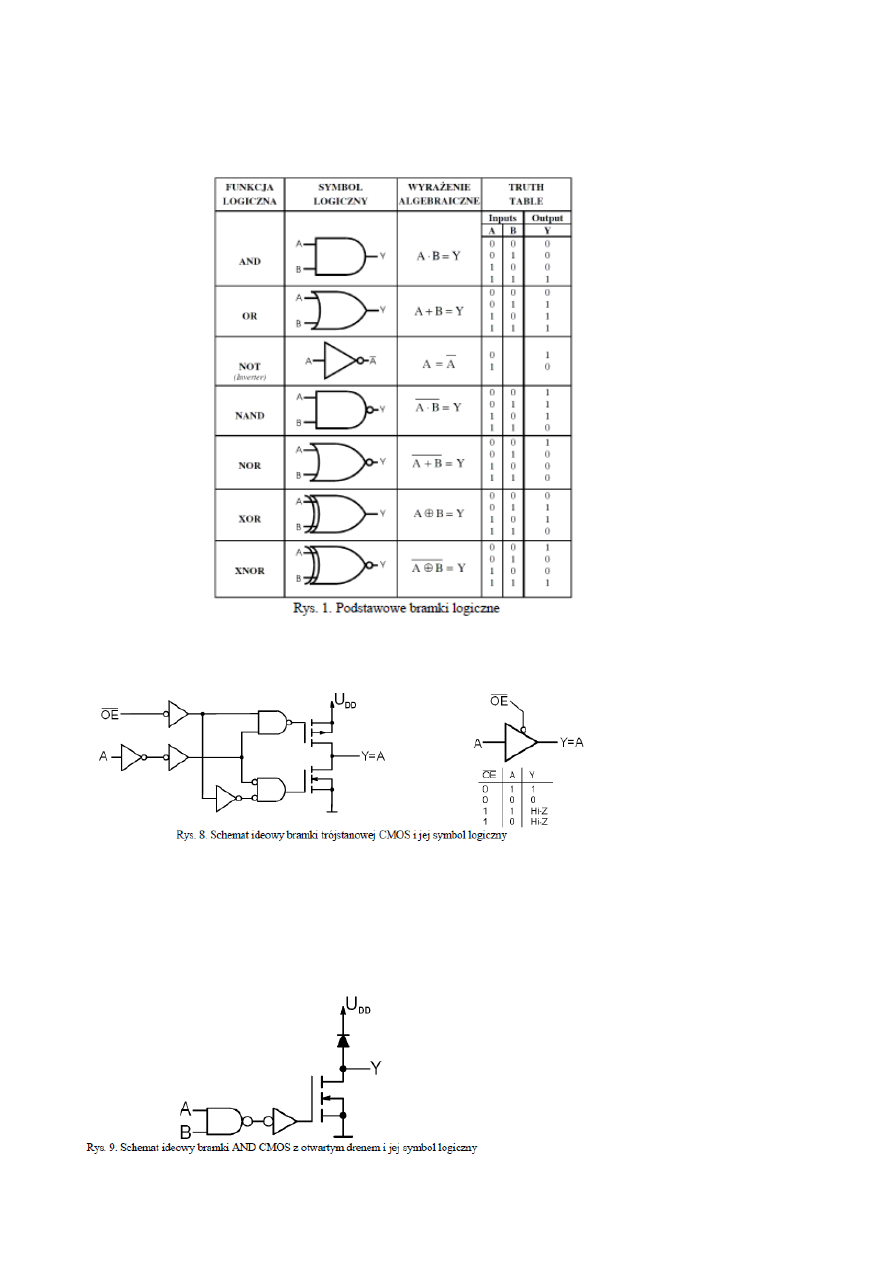

1. Podstawowe bramki logiczne (funkcja, symbol, wyrażenie logiczne).

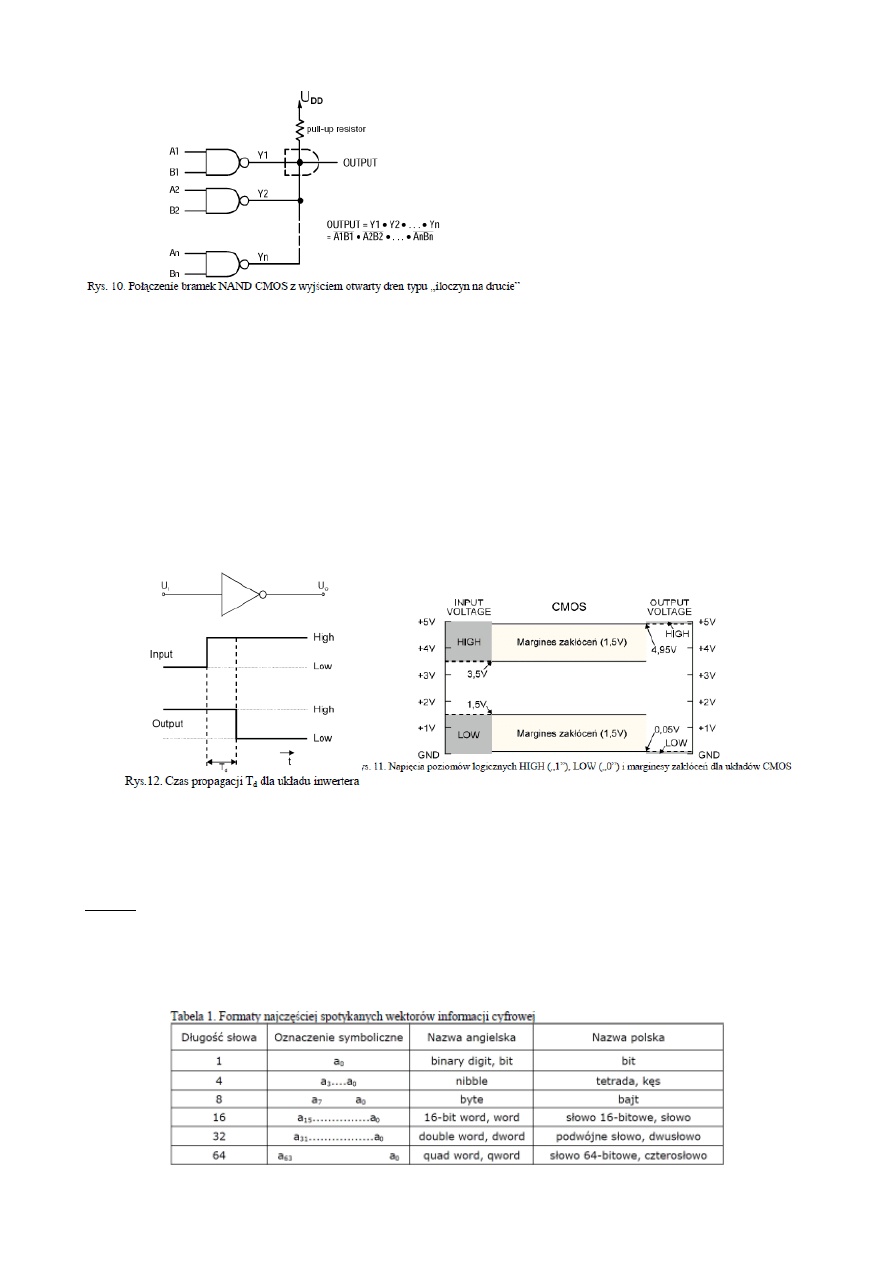

2. Zasada działania bramek trójstanowych i z otwartym drenem.

Bramka trójstanowa pełni

rolę bufora (tzn. nie realizuje

żadnej funkcji logicznej).

Posiada ona dodatkowe

wejście OE (Output Enable),

które steruje stopniem

wyjściowym (dwoma

tranzystorami CMOS).

Gdy na linii OE jest stan wysoki (OE = 1), to obydwie bramki sterujące są tak ustawione, że

tranzystory wyjściowe są odcięte a ich kanały nie mogą przewodzić prądu (niezależnie od stanu

sygnału na linii A). Tak więc wyjście bramki jest praktycznie odłączone. Mówimy wtedy o takim

wyjściu, że jest w stanie wysokiej impedancji (High-Z), lub że jest w trzecim stanie.

Gdy, OE = 0 bramka działa normalnie, tzn. stan na jej wyjściu pokrywa się ze stanem na wejściu.

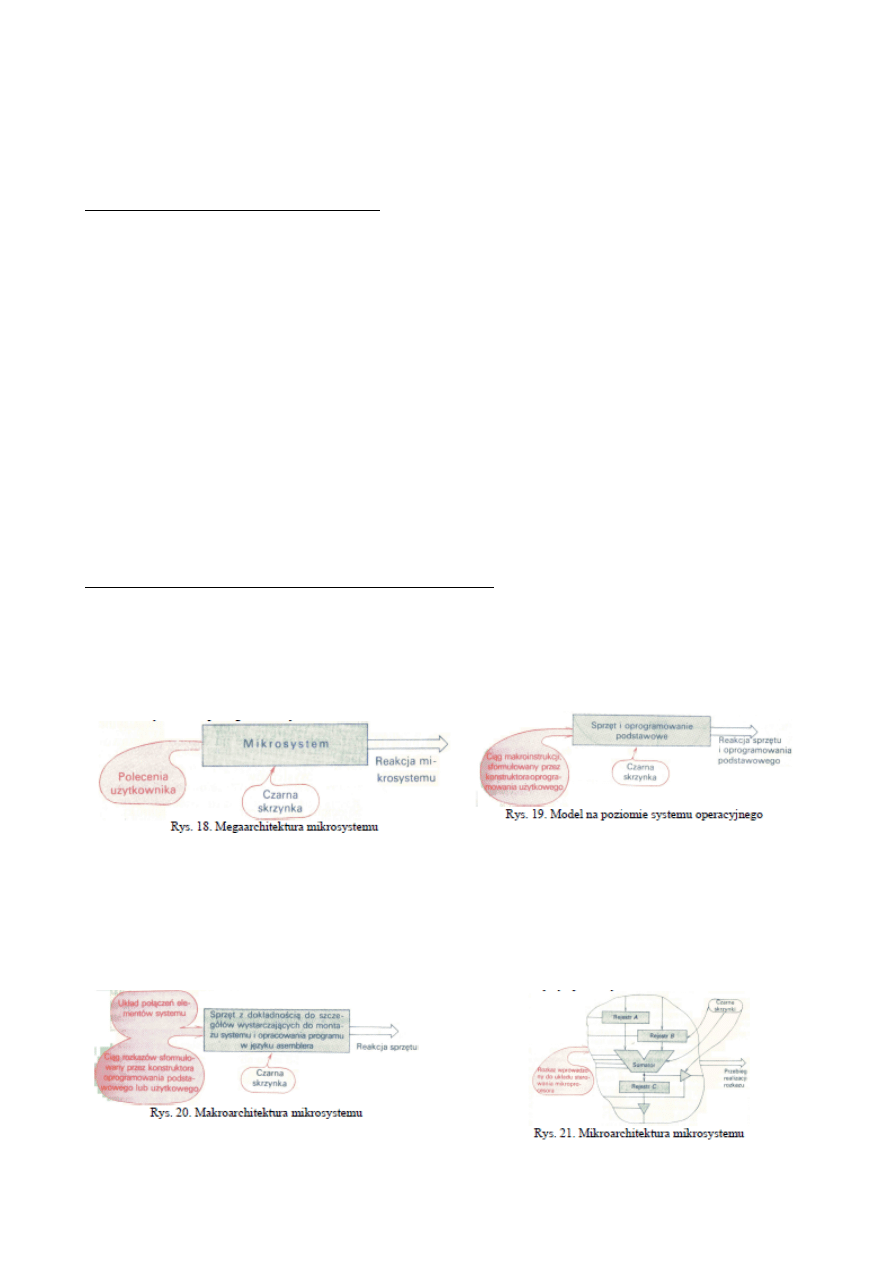

W bramce CMOS z otwartym drenem, mamy

do czynienia z takim wyjściem, gdzie z całego

stopnia wyjściowego pozostawiono jedynie

dolny tranzystor z kanałem N. Aby takie wyjście

nadawał się do użytku należy go spolaryzować

zewnętrznym rezystorem dołączonym do U

DD

.,

tzw. rezystorem podciągającym (pull-up

resistor)

Wyjścia bramek z otwartym drenem

można łączyć ze sobą bez ograniczeń.

Dla wszystkich połączonych wyjść

wystarcza jeden rezystor podciągający

(rys. 10)–typowe wartości 4,7 k

Ω

–10 k

Ω

.

Załączenie dowolnego tranzystora

powoduje niski stan na wyjściu takiego

połączenia, czyli jest realizowana funkcja

logiczna AND, zwana „iloczynem na

drucie” (wired-AND) lub iloczynem

montażowym.

3. Podstawowe parametry techniczne układów cyfrowych.

•

Obciążalność logiczna bramki (N) – maksymalna liczba bramek, jaka może być

równolegle sterowana z wyjścia pojedynczej bramki

•

Napięcia poziomów logicznych (HIGH, LOW) – zakresy napięć wejściowych oraz

wyjściowych, które układ realizuje jako gwarantowany stan 1 oraz gwarantowany stan 0.

•

Moc strat na bramkę (Pd) – określa moc pobieraną przez układ ze źródła zasilania.

•

Czas propagacji (Td) – określa czas opóźnienia odpowiedzi układu na sygnał sterujący i

jest podstawową miarą szybkości działania układu cyfrowego.

•

Margines zakłóceń (UNM) – określa dopuszczalną wartość napięcia sygnału

zakłócającego, nie powodującego jeszcze nieprawidłowej pracy układu.

4. Definicje i cechy formaty wektorów informacji cyfrowej i definicja informacji

cyfrowej.

Wektor informacji cyfrowej – uporządkowany wektor, którego elementami są zmienne binarne.

Cechy: 1. współrzędna wektora nosi nazwę bita, 2. długość (1,4,8,16,32 bity), 3. kolejność –

najczęściej od najstarszego (MSB) do najmłodszego (LSB).

Informacja cyfrowa - informacja przedstawiona za pomocą ciągu wektorów informacji

cyfrowej.

Duże zbiory informacji cyfrowej przedstawia się zwykle za pomocą matryc, których wierszami

są zdefiniowane w Tabeli 1 wektory informacji cyfrowej np. bajty.

5. Definicja pojęcia kodowania informacji cyfrowej, podział kodów.

Kodem danego zbioru symboli (np. cyfr, liter, znaków specjalnych) nazywa się

przyporządkowanie każdemu symbolowi tego zbioru jednego i tylko jednego wektora

informacji cyfrowej.

Generalnie kody możemy podzielić na:

· kody alfanumeryczne – służą do wprowadzania, wyprowadzania, przetwarzania i

przechowywania w pamięci ciągów symboli (cyfr, liter, symboli specjalnych)

przedstawiających tekst, rozkazy, instrukcje, nazwy programów, liczby (np. kod ASCII,

UNICODE).

· kody liczbowe – służące do przetwarzania liczb (np. kod binarny prosty, BCD, kody dla liczb

zmiennoprzecinkowych),

· kody sytuacji – tzw. kod prywatny tworzony doraźnie przez konstruktora dla opisania

rozmaitych sytuacji mogących zaistnieć w otoczeniu mikrosystemu.

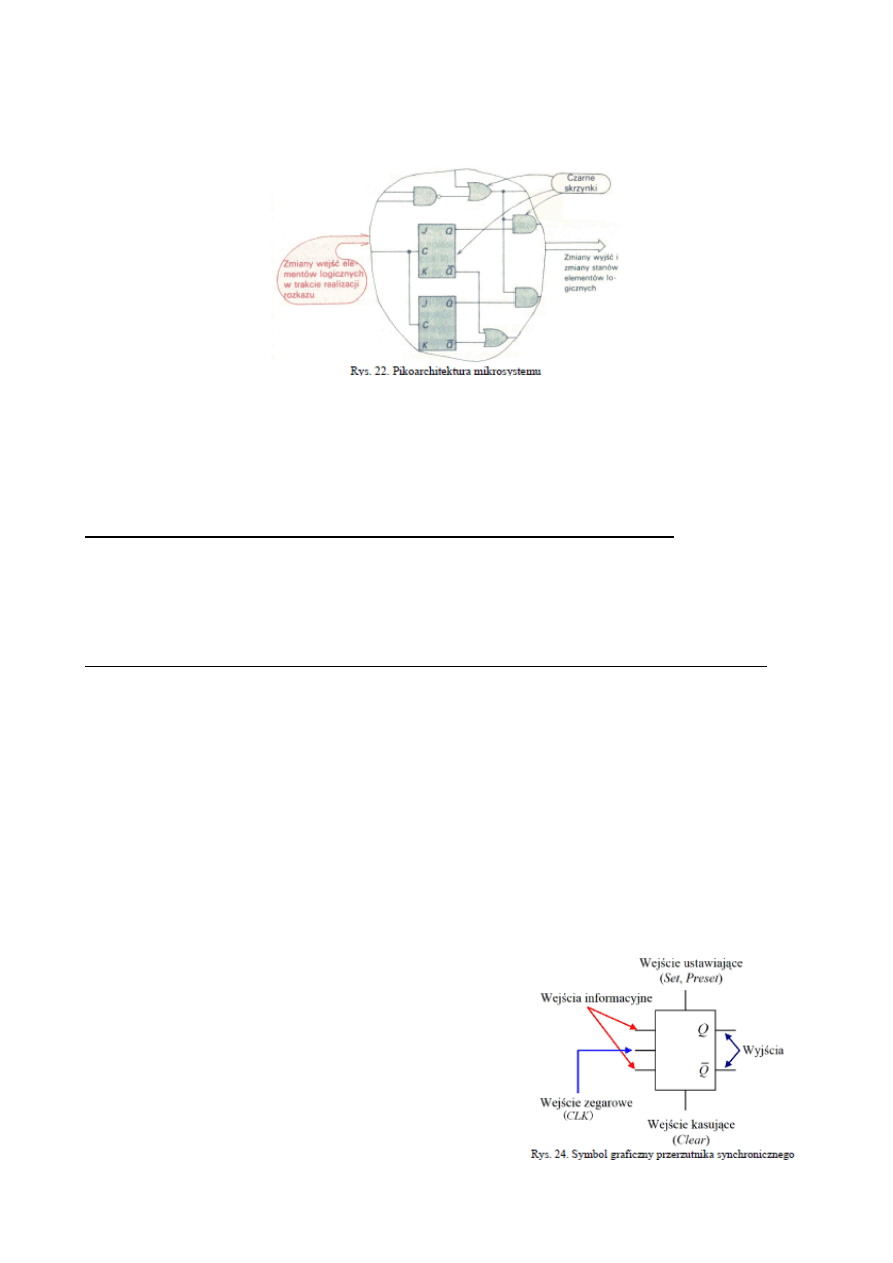

6. Modele wielopoziomowe mikrosystemów procesorowych.

Mikrosystem - system przeznaczony do realizacji dowolnego zadania dającego się sprowadzić

do przetwarzania wektorów informacji cyfrowej, w skład którego wchodzi sprzęt elektroniczny

i oprogramowanie.

Modele wielopoziomowe opisują mikrosystem na różnych poziomach abstrakcji, odpowiadających z reguły

potrzebom różnych grup ludzi nad nim pracujących lub z niego korzystających.

Mikrosystemy mo

ż na opisywa

ć

na nast

ę puj

ą cych poziomach:

•

poziom megaarchitektury – charakteryzujący sprzęt i oprogramowanie za pomocą zestawu

instrukcji i reguł, wystarczających użytkownikowi systemu do posługiwania się nim.

•

poziom systemu operacyjnego – obraz sprzętu i oprogramowania podstawowego, widziany przez

konstruktora oprogramowania użytkowego. Uzupełnienie sprzętu przez oprogramowanie

podstawowe (np. system operacyjny) daje system o możliwościach i właściwościach znacznie

przewyższających możliwości i właściwości samego sprzętu.

•

poziom makroarchitektury – obraz sprzętu mikrosystemu w oczach konstruktorów tego systemu.

Maktoarchitektura obejmuje wszystkie te i tylko te szczegóły, których znajomość jest potrzebna przy

montażu mikrosystemu ze składających się nań elementów i przy pisaniu programów dla

mikrosystemu przy użyciu np. asemblera.

•

poziom mikroarchitektury (przesłań międzyrejestrowych) – obraz sprzętu w oczach

konstruktora elementów tego sprzętu. Znajomość opisu sprzętu na tym poziomie umożliwia

określenie przebiegu realizacji każdego rozkazu z dokładnością do przesłań międzyrejestrowych.

•

poziom pikoarchitektury – obraz sprzętu w oczach konstruktora elementów cyfrowych o różnym

stopniu integracji, użytych przy jego budowie. Na tym poziomie opisuje się sprzęt w kategoriach

działania układów logicznych kombinacyjnych i sekwencyjnych, z których składają się elementy

cyfrowe użyte przez konstruktora sprzętu.

•

poziom obwodów elektronicznych – obraz sprzętu w oczach konstruktora technologa elementów

cyfrowych użytych do konstrukcji tego sprzętu.

7. Definicje układów kombinacyjnych, sekwencyjnych, synchronicznych i

asynchronicznych.

Podział układów logicznych ze względu na zależność między sygnałami we i wy:

Układ kombinacyjny - stan wejść jednoznacznie określa stan wyjść układu (np. bramki

logiczne, połączenie odpowiedniej ilości i rodzajów bramek, bez sprzężeń zwrotnych)

Układ sekwencyjny - stan jego wyjść zależy od stanu wejść oraz od poprzednich stanów

układu (czyli są to układy z pamięcią, np. przerzutniki).

Podział układów logicznych ze względu na zależność między sygnałami we i wy w czasie:

Układ asynchroniczny - układ cyfrowy, dla którego w dowolnym momencie jego

działania stan wejść oddziałuje na stan wyjść, czyli ich własności nie zależą od żadnego

przebiegu czasowego (np. asynchroniczny przerzutnik RS).

Układ synchroniczny - układ cyfrowy, dla którego stan wejść wpływa na stan wyjść jedynie w

pewnych określonych odcinkach czasu pracy układu zwanych czasem czynnym, a w

pozostałych odcinkach czasu zwanych czasem martwym stan wejść nie wpływa na stan wyjść.

Odcinki czasu czynnego i martwego wyznaczane są przez podanie specjalnego przebiegu

zwanego przebiegiem zegarowym lub taktującym na wejście zwane wejściem zegarowym lub

taktującym. Czyli własności ukł. synchr. zależą od zmian przebiegu zegarowego w funkcji

czasu. Przebieg jest z reguły prostokątny (dwa poziomy: Hi – 1, Lo – 0) ze zboczem

narastającym (stan niski → stan wysoki) i opadającym (stan wysoki → stan niski).

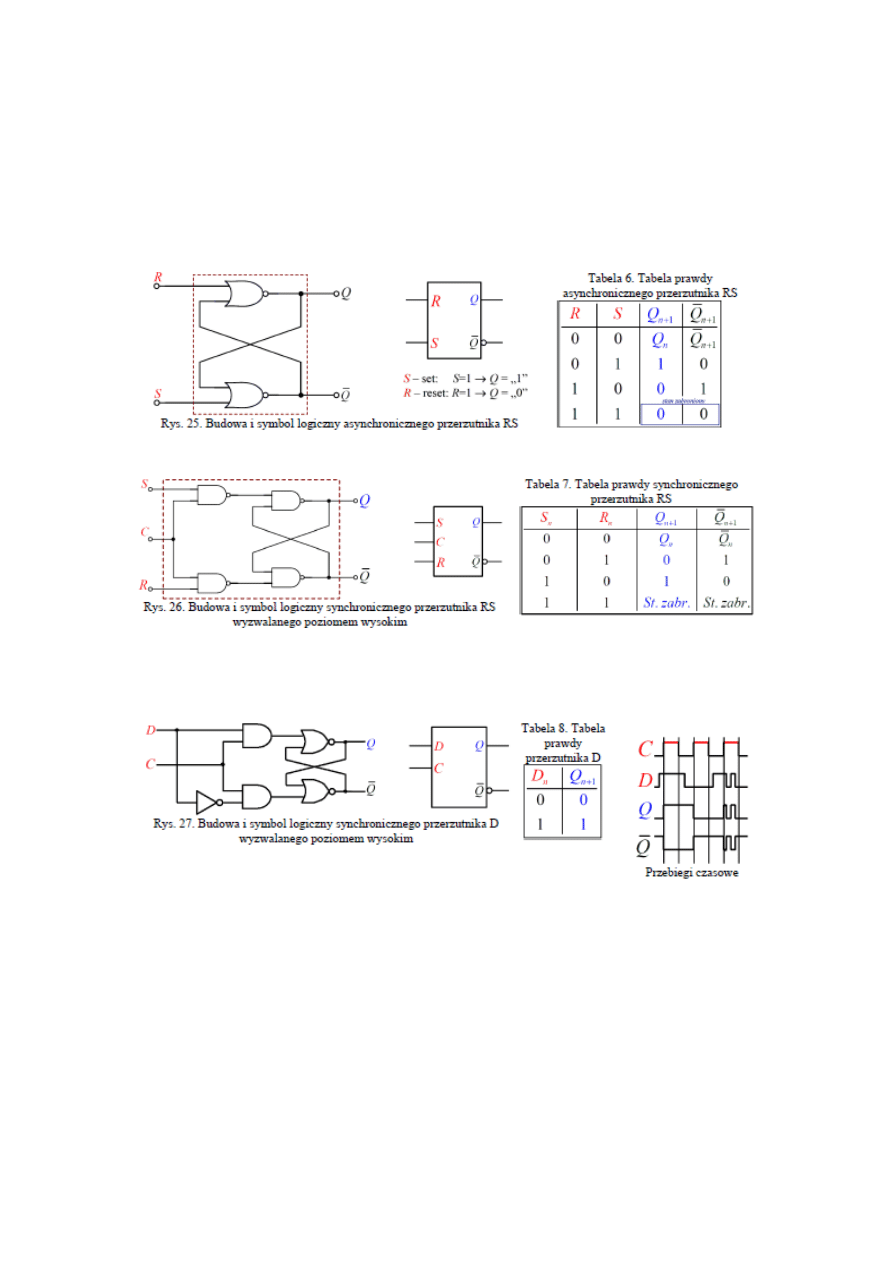

8. Definicja, symbol logiczny i zasada działania przerzutnika.

Przerzutnik - podstawowy element pamiętający każdego

układu cyfrowego, przeznaczonego do przechowywania i

ewentualnego przetwarzania informacji. Przerzutnik

zdolny jest do zapamiętania jednego bitu informacji. Np.

grupa ośmiu odpowiednio połączonych ze sobą

przerzutników tworzy układ zwany rejestrem, zdolny już

do pamiętania jednego bajta informacji. Wyróżnia się

przerzutniki RS, D, T, JK, JK-MS. Wszystkie (oprócz D)

mogą pracować w wersji asynchronicznej (przełączają

stan wyjść w momencie zmiany stanów na wejściach) lub synchronicznej (zmiana stanów na

wyjściach dodatkowo zależy od zmiany sygnału doprowadzonego do ich wejścia zegarowego).

Przerzutniki synchroniczne dzieli się ze względu na typ wejścia zegarowego na wyzwalane

zboczem i na wyzwalane odpowiednim poziomem sygnału zegarowego. Za pomocą każdego

przerzutnika i odpowiedniej liczby bramek logicznych można zrealizować inne przerzutniki.

Przerzutnik RS (w wersji podstawowej) posiada dwa wejścia R i S. Wejścia te sterują wyjściem Q,

odpowiednio: S ustawia poziom wysoki (Hi); R ustawia poziom niski (Lo). Wada RS - jednoczesne podanie

jedynek logicznych na wejścia R i S wywołuje stan logicznie sprzeczny.

Przerzutnik RS z wejściem zegarowym

Przerzutnik D - odmiana synchronicznego przerzutnika RS, w którym używane jest tylko jedno wejście

informacyjne D, połączone bezpośrednio z wejściem S (S = D) i z wejściem R poprzez negację (R = !D).

Wprowadzona w ten sposób stała zależność R = S eliminuje możliwość wystąpienia stanu zabronionego S =

R = 1 i upraszcza sterowanie przerzutnika.

9. Definicja i architektura dekodera, kodera, multipleksera, demultipleksera.

Dekoder - element, którego wektor wejściowy ma n współrzędnych, a wyjściowy ma k ≤ 2

n

współrzędnych, przy czym każda współrzędna wektora wyjściowego może być równa 1(lub 0)

dla jednego wektora wejściowego.

Jeżeli k = 2

n

, dekoder nazywa się dekoderem pełnym, jeżeli k < 2

n -

niepełnym.

Dekodery najczęściej wykorzystuje się jako dekodery adresów. W dekoderach zawsze jest aktywne (np. „1”

na wyjściu) tylko jedno wyjście. Numer tego wyjścia jest zgodny z zawartością podanego na jego wejścia

wektora informacji zwanej adresem.

Koder - element, którego wektor wejściowy ma 2

n

współrzędnych, a wektor wyjściowy ma n

współrzędnych i jest kodem numeru tego jedynego wejścia, na który wprowadzono wyróżniony

sygnał.

Multiplekser (MPX) ma zadanie, w zależności od kodu wejścia (kod binarny) połączyć ten

numer wejścia ze wspólnym wyjściem.

Demultiplekser (DMPX) działa na odwrotnie niż multiplekser, czyli łączy jedno wejście z

wyjściem o numerze wskazanym przez kod wejścia.

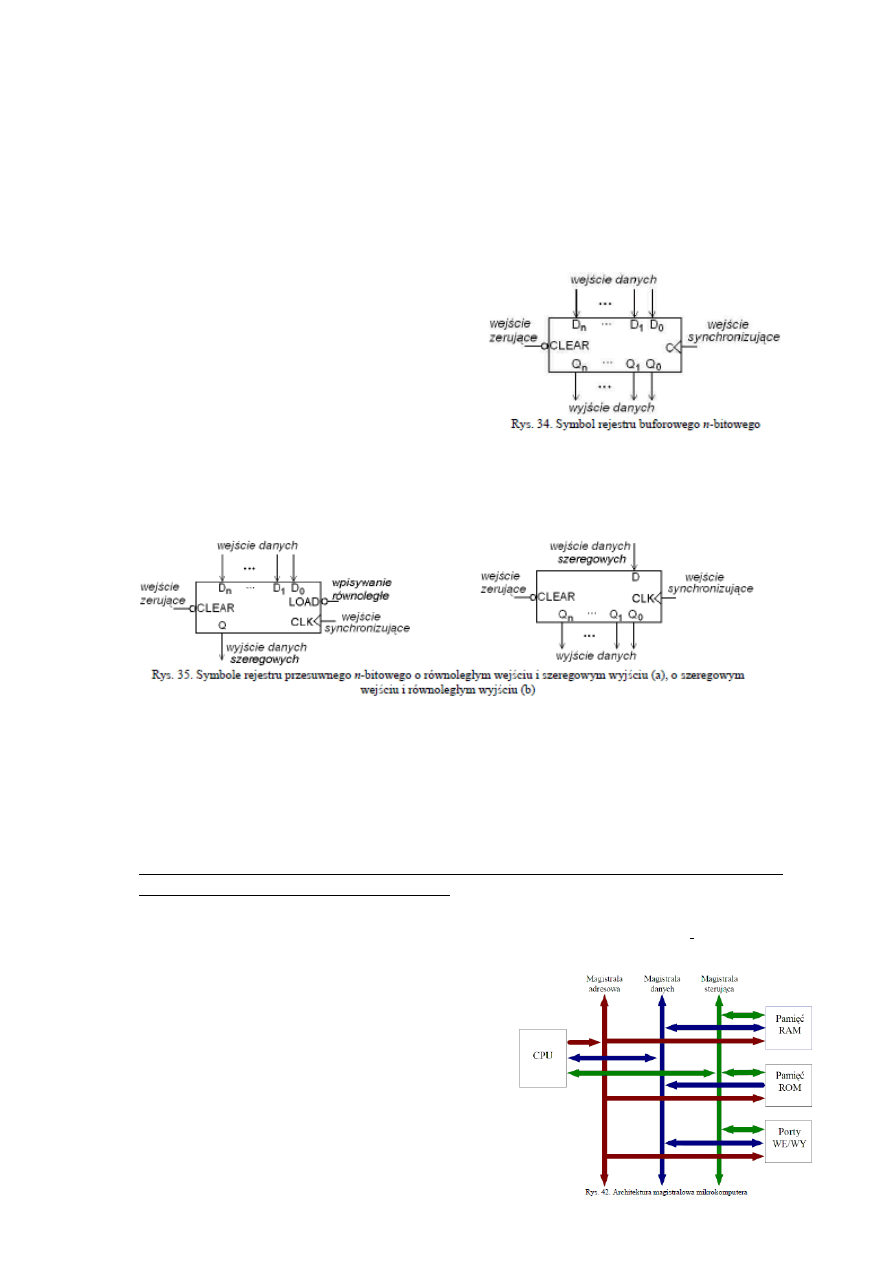

10. Definicja, budowa i zasada działania rejestru buforowego i przesuwnego oraz linii

cyfrowych.

Rejestr buforowy - zespół przerzutników

synchronicznych o wspólnym wejściu

synchronizującym i wspólnym wejściu zerującym,

przeznaczony do krótkotrwałego

przechowania wektora informacji cyfrowej, np. w

celu poddania go określonemu przetwarzaniu lub w

oczekiwaniu na chwilę przekazania go do dalszego

przetwarzania.

Rejestr przesuwny - zespół przerzutników synchronicznych, umożliwiający wprowadzanie

i wyprowadzanie wektorów informacji cyfrowej w sposób bitowo-szeregowy w czasie.

Rejestr

przesuwny korzysta z wejść/wyjść cyfrowych równoległych i szeregowych.

Wejściem/wyjściem cyfrowym równoległym nazywamy takie wejście/wyjście (składające się z n linii

cyfrowych), które umożliwia wprowadzenie/wyprowadzenie do/z układu cyfrowego wszystkich n bitów

słowa w jednym takcie zegarowym.

Wejściem/wyjściem cyfrowym szeregowym nazywamy takie wejście/wyjście, które

umożliwia wprowadzanie/wyprowadzenie informacji do układu bit po bicie. Do wprowadzenia

słowa n-bitowego potrzeba n taktów zegara.

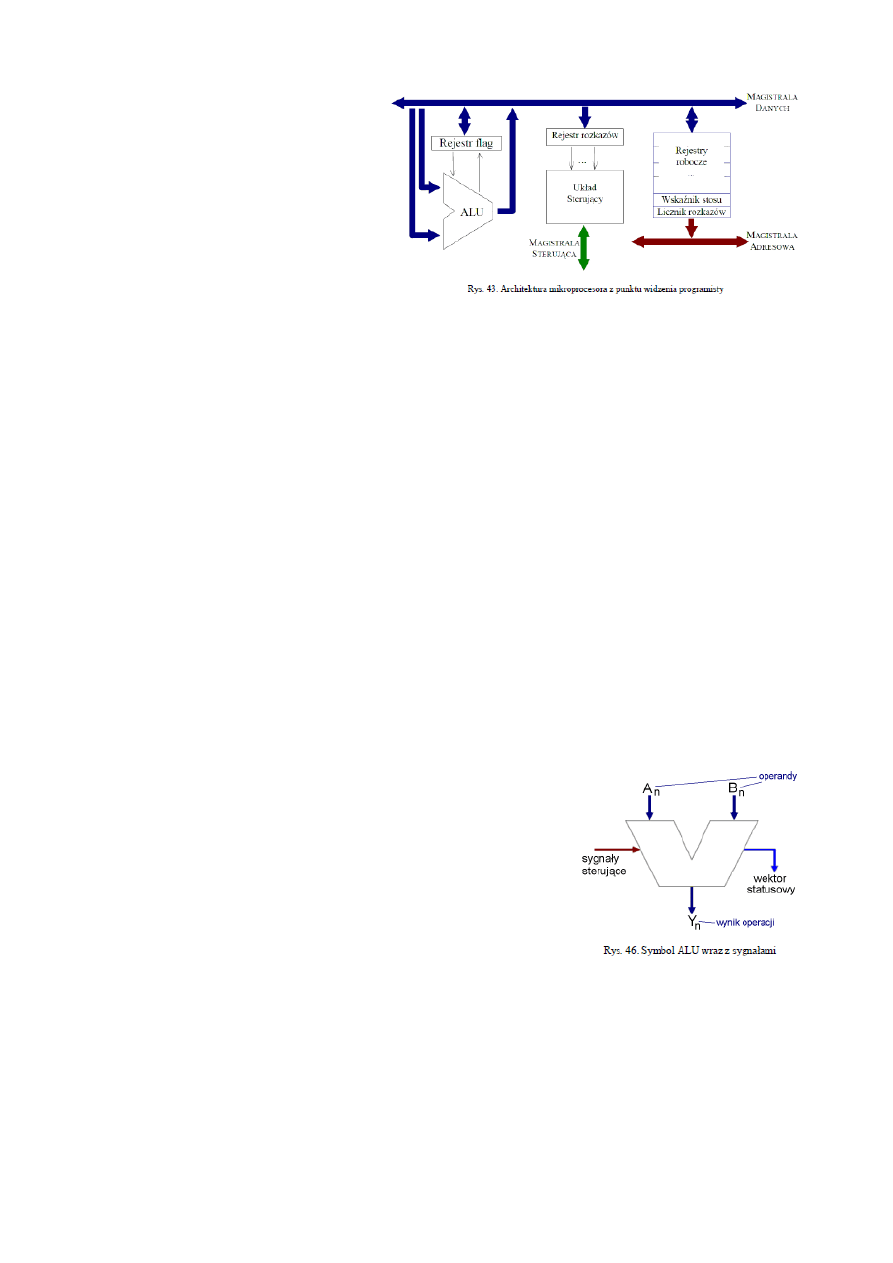

11. Definicje systemu mikroprocesorowego, mikrokomputera, mikroprocesora oraz ich

architektury, budowa i zasada działania.

System mikroprocesorowy (mikrosystem) - system przeznaczony do realizacji dowolnego

zadania dającego się sprowadzić do przetwarzania wektorów informacji cyfrowej, w skład

którego wchodzi: sprzęt elektroniczny, oprogramowanie.

Mikrokomputer - cyfrowy scalony element

elektroniczny bardzo wielkiej skali integracji lub układ

złożony z elementów dużej skali integracji, w skład

którego wchodzi: mikroprocesor, pamięć (np. ROM,

RAM), układy wejścia/wyjścia, magistrale (szyny

systemowe). Mikrokomputer stanowi kompletny

programowalny system do przetwarzania informacji

cyfrowej

Mikroprocesor (CPU) - cyfrowy układ

scalony wielkiej skali integracji,

przeznaczony do

realizacji operacji arytmetyczno-

logicznych na wektorach informacji

cyfrowej, zwanych danymi,

wprowadzanych z pamięci i rejestrów

układów wejścia-wyjścia. Rodzaj

wykonywanej operacji jest określony

przez wektory informacji cyfrowej zwane

rozkazami, które mikroprocesor pobiera z

pamięci. Wyniki wykonywanych operacji może mikroprocesor przekazywać do pamięci lub

rejestrów układów wejścia-wyjścia. Zadaniem mikroprocesora (jednostki centralnej) jest szeregowe

przetwarzanie danych poprzez kolejne wykonywanie rozkazów zapisanych przez użytkownika w

postaci programu umieszczonego w pamięci komputera. Program operuje na danych, które również

znajdują się w pamięci komputera. Z punku widzenia użytkownika najbardziej istotną cechą

jednostki centralnej jest jej lista rozkazów - zbiór elementarnych operacji. Program użytkownika

zapisany w pamięci składać się może tylko z rozkazów zawartych w liście rozkazów danej

jednostki centralnej. W skład mikroprocesora wchodzą:

•

rejestr rozkazów IR – przechowywany jest w nim kod aktualnie wykonywanego rozkazu.

•

układ sterujący – w tym bloku znajduje się dekoder rozkazów służący do dekodowania rozkazu

zawartego w rejestrze rozkazów. Na tej podstawie układ sterowania wytwarza wewnętrzne i/lub

zewnętrzne sygnały sterujące (na magistrali sterującej) realizujące dany rozkaz.

•

ALU (uniwersalna jednostka arytmetyczno logiczna) – wykonująca wszelkie operacje arytmetyczne

i logiczne.

•

rejestry dostępne programowo:

rejestr flagowy – zawierający dodatkowe cechy wyniku

wykonywanej operacji, potrzebne do podjęcia decyzji o dalszym sposobie przetwarzania informacji.

licznik rozkazów PC – rejestr mikroprocesorowy zawierający adres komórki pamięci, w której

przechowywany jest kod rozkazu przeznaczony do wykonania jako następny.

wskaźnik stosu –

rejestr zawierający adres ostatniej zapełnionej komórki stosu.

rejestry robocze lub ogólnego

przeznaczenia GPR – pewny zestaw rejestrów ogólnego przeznaczenia. Mają przechowywać

argumenty wykonanych operacji i wyniki.

12. Definicja, symbol, cechy i zasada działania układu ALU.

Układy ALU - uniwersalne, sterowalne elementy do realizacji

operacji arytmetycznych i logicznych na wektorach informacji

cyfrowej.

Uniwersalność - możliwość zastosowania do realizacji

funkcjonalnie pełnego zbioru operacji arytmetycznych i logicznych.

Sterowalność - możliwość wyboru realizowanej operacji na drodze

nastawienia właściwych sygnałów sterujących. ALU używane jest do:

operacji logicznych AND, OR, NOT, XOR; operacji arytmetycznych;

przesunięcia bitowego; porównywania liczb; mnożenia/dzielenia.

13. Definicja przesłania międzyrejestrowego, magistrali bitowo-równoległej.

Przesłanie rejestrowe - wpisywanie wektora informacji cyfrowej znajdującego się w jednym

rejestrze (zwanym rejestrem nadajnikiem) do innego rejestru (zwanego rejestrem odbiornikiem). Do

przesłań międzyrejestrowych używa się magistral. Numery rejestrów nadajników czy odbiorników

jednoznacznie identyfikujące dany rejestr podłączony do magistrali nazywa się adresami.

Magistrala bitowo-równoległa - pęk linii i zestaw elementów przełączających,

umożliwiających przekazywanie informacji cyfrowej w sposób bitowo-równoległy w

czasie, od jednego z wielu rejestrów nadajników do jednego z wielu rejestrów odbiorników,

przy czym w każdej chwili możliwe jest przekazywanie informacji tylko między jednym

określonym nadajnikiem i jednym określonym odbiornikiem.

Pomiędzy układy będące w danym momencie na magistrali nadajnikiem a odbiornikiem stosuje się

zwykle układy buforowe zbudowane z bramek trójstanowych, pośredniczące w wymianie

informacji. Zadaniem tego typu układów jest:

•

separacja układów połączonych do magistrali od magistrali możliwa przez przejście wyjść w stan

wysokiej impedancji,

•

zmniejszenie obciążenia nadajnika przez odbiornik,

•

zwiększenie prądu wyjściowego,

•

poprawa kształtu zboczy sygnałów.

14. Podział i praca szyn systemowych (magistral) oraz pełnione przez nie funkcje.

Podział:

•

szyna danych – przeznaczona do przesyłania danych, wyników oraz kodów instrukcji, jest to

magistrala dwukierunkowa z liniami trójstanowymi, o szerokości (8/16/32/64 bity).

•

szyna adresowa – przesyłane są adresy komórek pamięci lub układów we/wy z którymi chce się

komunikować mikroprocesor – magistrala jednokierunkowa adresy są generowane przez

mikroprocesor, natomiast trafiają do pamięci bądź do układów we/wy,

•

szyna sterująca– zestaw linii sterujących, które służą do sterowania pracą układów

współpracujących z mikroprocesorem oraz do sygnalizowania pewnych ich określonych stanów,

np: sygnały dostępu, sygnały stanu, zerowanie, przerwanie, obsługa transmisji DMA, sygnały

zegarowe.

Praca:

Pobranie z komórki zawartej w pamięci programu kodu z kolejnym rozkazem. Adres komórki jest

wskazywany przez licznik rozkazów i wystawiony na magistrali adresowej, za pośrednictwem

której jej zawartość jest wpisywana do dekodera rozkazów. Tam rozkaz jest dekodowany (określane

jest działanie). Jeżeli wykonywana jest operacja logiczna lub arytmetyczna, to wykonaniem rozkazu

zajmuje się ALU. Rozkaz jest wykonywany. Po jego wykonaniu CPU modyfikuje zawartość

licznika rozkazów, by wskazywał kolejny rozkaz w pamięci programu.

15. Ogólne właściwości jednostki centralnej oraz jej cechy techniczne.

Właściwości:

•

synchroniczność – wszystkie operacje wykonywane przez mikroprocesor odbywają się w

rytm sygnału zegarowego

•

sekwencyjność – stan wyjść jednostki centralnej zależy nie tylko od stanu wejść, ale też od

poprzednich stanów tego układu

•

jednostka centralna posiada własną pamięć (rejestry) – do przechowywania argumentów

rozkazów niezbędnych do wykonania operacji

Cechy techniczne:

•

szerokość szyny danych (8-bitowa, 16-bitowa lub 32-bitowa) - na podstawie tej szerokości określa

się typ mikroprocesora

•

częstotliwość sygnału taktującego (zegarowego). Im większa prędkość przetwarzania danych

(czyli większa częstotliwość sygnału zegarowego w takt którego są wykonywane rozkazy, czyli

przetwarzane dane) tym lepiej. Ale trzeba pamiętać, że ze wzrostem częstotliwości sygnału

zegarowego rośnie pobór mocy, co jest niekorzystne między innymi w urządzeniach mobilnych

(systemach bateryjnych).

16. Podstawowe zastosowania układów buforów magistrali 8-bitowej w systemach

mikroprocesorowych.

•

Zwiększenie liczby linii sterujących mk przez podłączenie buforów do portu mk. Wówczas

można sekwencyjnie ustawiać 8*N linii wyjściowych lub sekwencyjnie czytać 8*M linii

wejściowych

•

zwiękzenie wydajności prądowej linii wyjściowych – linie wyjściowe układów scalonych

buforów mają zdecydowanie większe wydajności prądowe niż linie mk, zatem nadają się do

ich buforowania

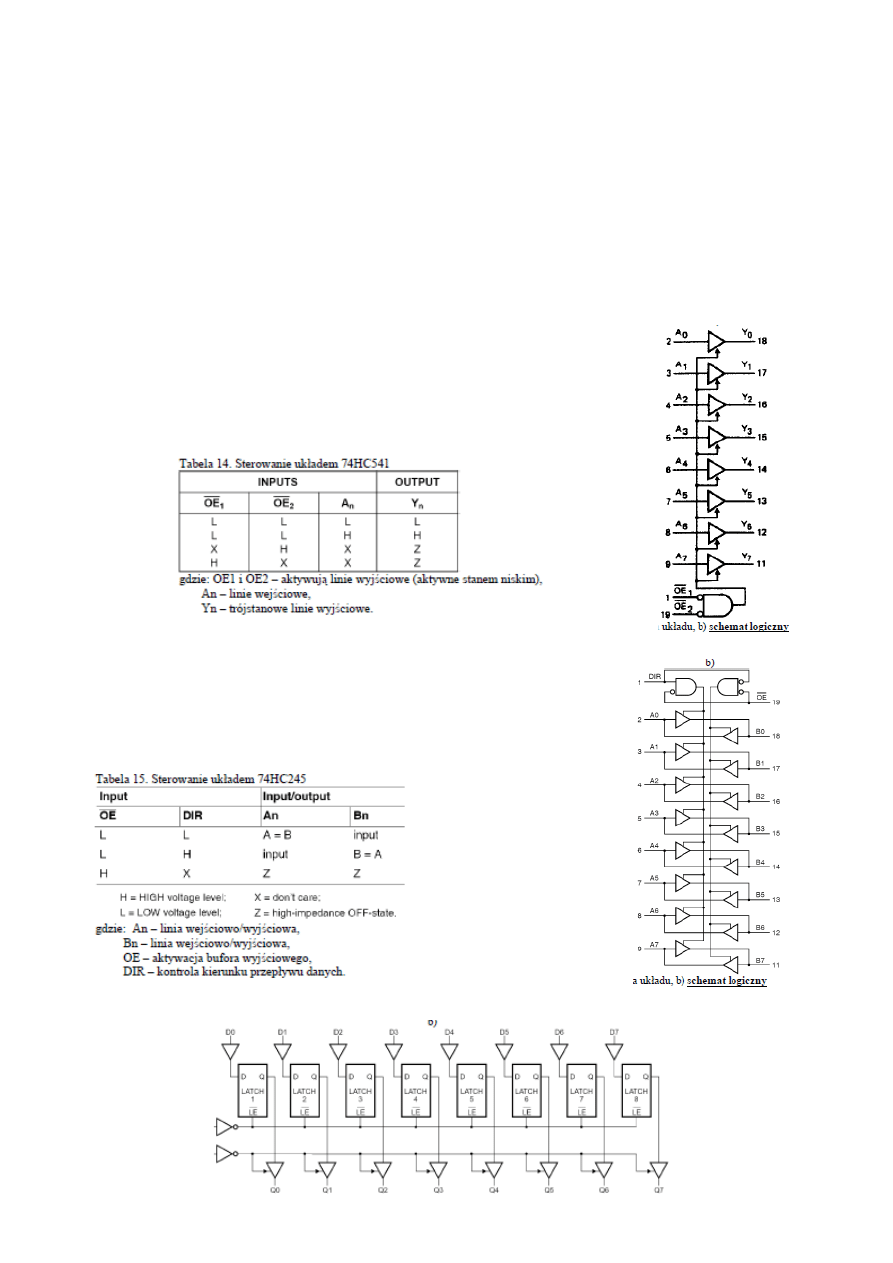

17. Schemat logiczny i zasada działania jednokierunkowego nieodwracającego bufora

74HC541.

Układ 74HC541 ma 8 trójstanowych linii wyjściowych. Stan tych linii jest

kontrolowany za pomocą wejść OE1 i OE2. Stan wysoki na linii OEn wprowadza

linie trójstanowe w stan wysokiej impedancji. Dzięki tej właściwości układ stosowany

jest w systemach magistralowych. Natomiast stan niski uaktywnia bufory, zatem to co

jest podawane na wejście układu pojawia się na jego wyjściu.

18. Schemat logiczny i zasada działania dwukierunkowego nieodwracającego bufora 74HC245.

Układ 74HCT245 posiada 8 linii, którymi dane mogą być przesyłane w obu

kierunkach. Niski poziom na linii OE (output enable input) uaktywnia bufory,

czyli to co jest na wejściu układu to pojawia się na jego

wyjściu, natomiast wysoki poziom na tej linii wprowadza wszystkie bufory w stan

wysokiej impedancji.

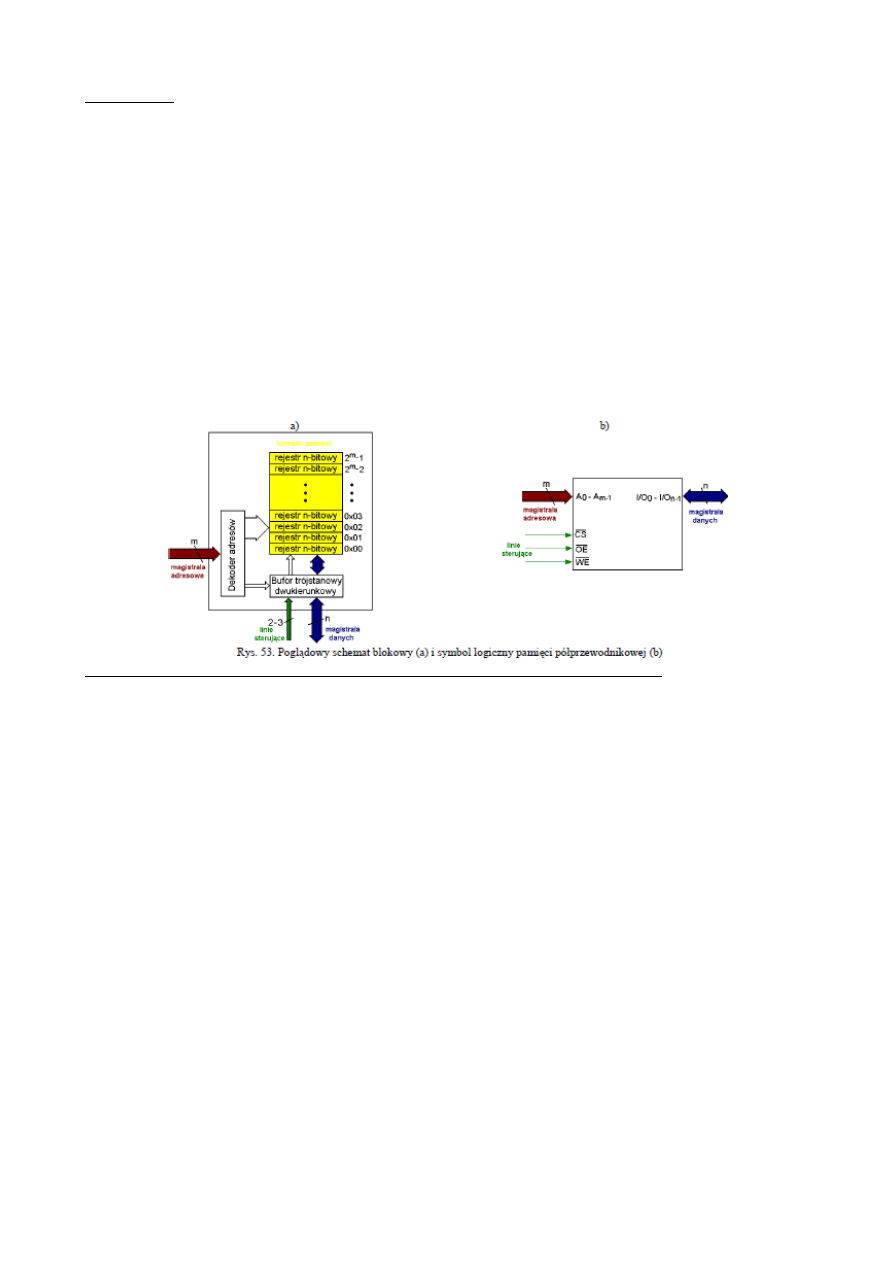

19. Schemat logiczny i zasada działania 8-bitowego rejestru zatrzaskującego 74HC573.

Wła

ś ciwo

ś ci:

•

trzystanowe nieodwracające wyjścia, co pozwala na stosowanie układu w systemach magistralowych,

•

zawiera w sobie 8-bitowy rejestr składający się z przerzutników typu D wyzwalanych poziomem niskim,

•

każdemu przerzutnikowi przyporządkowana jest linia wejściowa i wyjściowa,

•

dla wszystkich przerzutników jest wspólny sygnał wprowadzania danych LE (latch enable) i sygnał

sterowania ich buforami wyjściowymi OE.

Gdy na linii LE pojawi się poziom wysoki, to stan sygnałów na liniach wejściowych układu (D0 – D7)

zostaje zapamiętany w rejestrze. Kiedy sygnał OE jest w stanie wysokim wyjścia układu (Q0 – Q7) są w

stanie wysokiej impedancji. Stan niski na linii OE spowoduje wystawienie zawartości rejestru na linie

wyjściowe. Linia OE nie wpływa na zawartość rejestrów układu.

20.

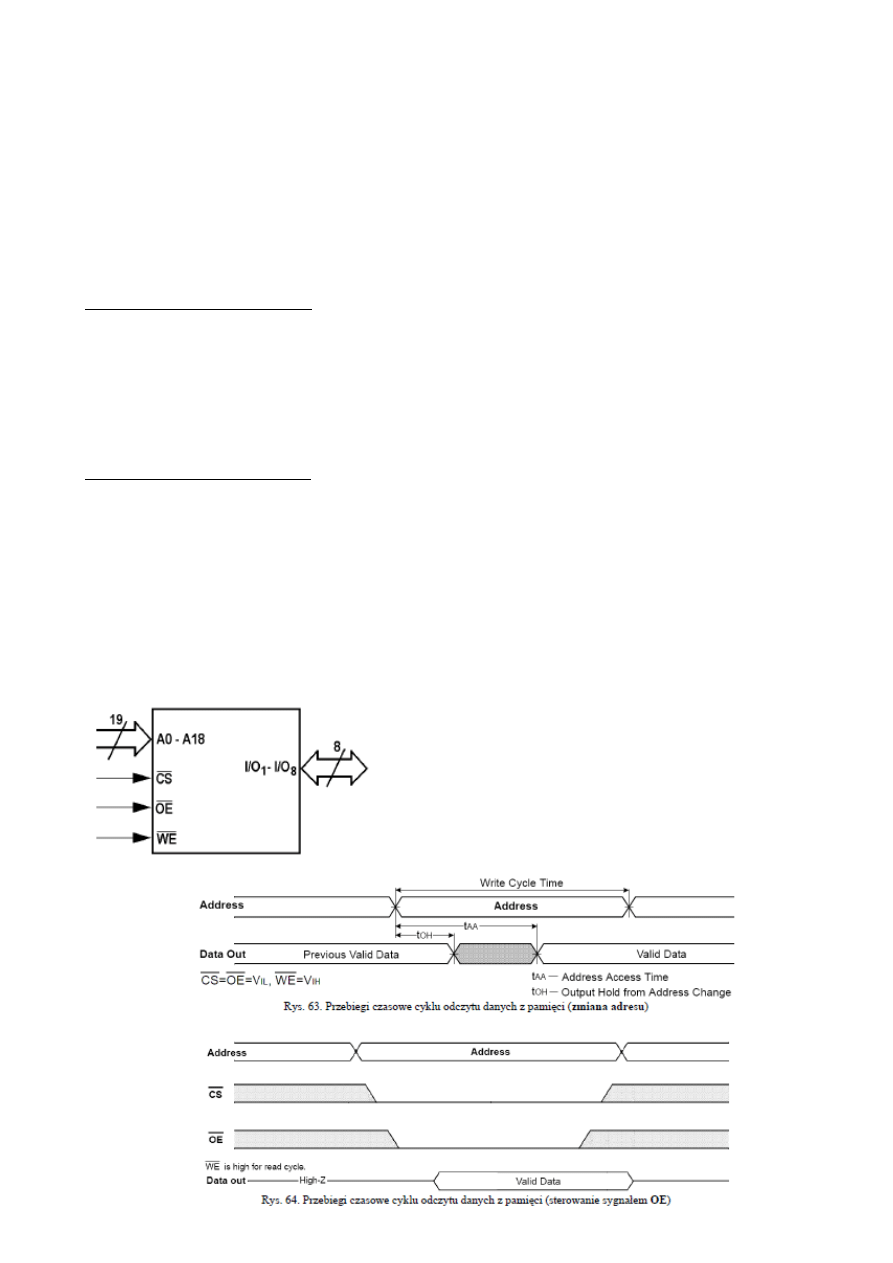

Definicja, schemat logiczny, budowa i zasada działania pamięci półprzewodnikowej w

systemach mikroprocesorowych.

Pamięć półprzewodnikowa – układ scalony służący do przechowywania zbioru wektorów

informacji cyfrowej.

Układ pamięci komunikuje się z otoczeniem za pomocą trzech magistral (szyn):

–

szyna adresowa – na niej jest wystawiany kod adres komórki pamięci, na której ma zostać

wykonana operacja zapisu lub odczytu

–

szyna danych – służy do wprowadzania i wyprowadzania danych z/do pamięciowych

–

szyna sterująca – sygnały wchodzące w skład tej szyny są zależne od typu pamięci. Często

są to 3 sygnały oznaczane jako: CE – uaktywnienie układu pamięci; możliwy jest zapis lub

odczyt z/do układu; OE – używany podczas operacji czytania z pamięci; na szynie danych

układu pamięci pojawia się zawartość tej komórki pamięci, na którą wskazywał stan szyny

adresowej przed doprowadzeniem sygnału OE; WE – używany podczas operacji

wpisywania do pamięci; do komórki pamięci, na którą wskazywał stan szyny adresowej

przed doprowadzeniem WE wpisywana jest wartość zgodna z aktualnym stanem szyny

danych.

21. Podział i charakterystyka scalonych układów pamięciowych.

•

Pamięci ulotne – trzymają dane tylko, gdy są zasilane. Zanik napięcia zasilania powoduje

utratę informacji. (Statyczne SRAM, pseudostatyczne PSRAM, dynamiczne DRAM)

•

pamięci stałe – jednokrotnie programowane; po wyłączeniu zasilania dane nie ulegają

skasowaniu. (Programowane przez producenta: ROM, mask-ROM; jednokrotnie

programowane przez użytkownika: PROM, OTPROM)

•

pamięci nieulotne – dane nie ulegają skasowaniu po wyłączeniu zasilania, można je

wielokrotnie programować. (reprogramowane w systemie docelowym EEPROM, FLASH,

F-RAM; statyczne RAM z podtrzymaniem bateryjnym NOVRAM; hybrydowe NVRAM

złożone z SRAM i EEPROM; wielokrotnie programowane przez użytkownika EPROM)

22. Definicja pamięci półprzewodnikowej stałej ROM o dostępie swobodnym RAM.

ROM – pamięć stała umożliwiająca wyłącznie odczytywanie swojej zawartości podczas

współpracy z innymi elementami mikrosystemu

RAM – pamięć półprzewodnikowa o dostępie swobodnym, która umożliwia wpisywanie i

odczytywanie informacji z czasem niezależnym od miejsca pobytu informacji w pamięci. Dwa

typy: statyczna SRAM i dynamiczna DRAM.

23. Cykle odczytu i zapisu z/do pamięci asynchronicznych o dostępie równoległym.

Schemat cyklu odczytu z pami

ę ci:

1. Mikroprocesor ustawia stan linii adresowych i sygnalizuje ważność adresu.

2. Mikroprocesor uaktywnia układ pamięci (niski stan na CS ) i ustawia strob odczytu danych (niski

stan na OE).

3. Pamięć ustawia stan linii danych.

4. Mikroprocesor odczytuje stan linii danych.

5. Mikroprocesor dezaktywuje pamięć (wysoki stan na CS ) i wycofuje strob odczytu (wysoki stan na

OE).

Schemat cyklu zapisu do pami

ę ci:

1. Mikroprocesor ustawia stan linii adresowych i sygnalizuje ważność adresu.

2. Mikroprocesor ustawia stan linii danych.

3. Mikroprocesor uaktywnia układ pamięci (niski stan na CS ) i ustawia strob zapisu danych (niski stan

na WE).

4. Pamięć odczytuje stan linii danych i go zapamiętuje.

5. Mikroprocesor dezaktywuje pamięć (wysoki stan na CS ) i wycofuje strob zapisu (wysoki stan na

WE).

24. Schemat logiczny, znaczenie linii, przebiegi czasowe cyklów odczytu i zapisu

asynchronicznej pamięci SRAM o dostępie równoległym i pojemności np. 512KB.

CS – uaktywnienie układu. Stan niski na tej linii aktywuje

układ do transmisji

OE – wykorzystywana w trakcie czytania danej. Niski

poziom na tej linii uaktywnia bufory wyjściowe pamięci

WE – niski poziom uaktywnia bufory wejściowe i

dezaktywuje wyjściowe, czyli służy do wprowadzania danej

do pamięci za pośrednictwem linii I/O1-I/O8 pod adres

wskazany przez linie A0-A18

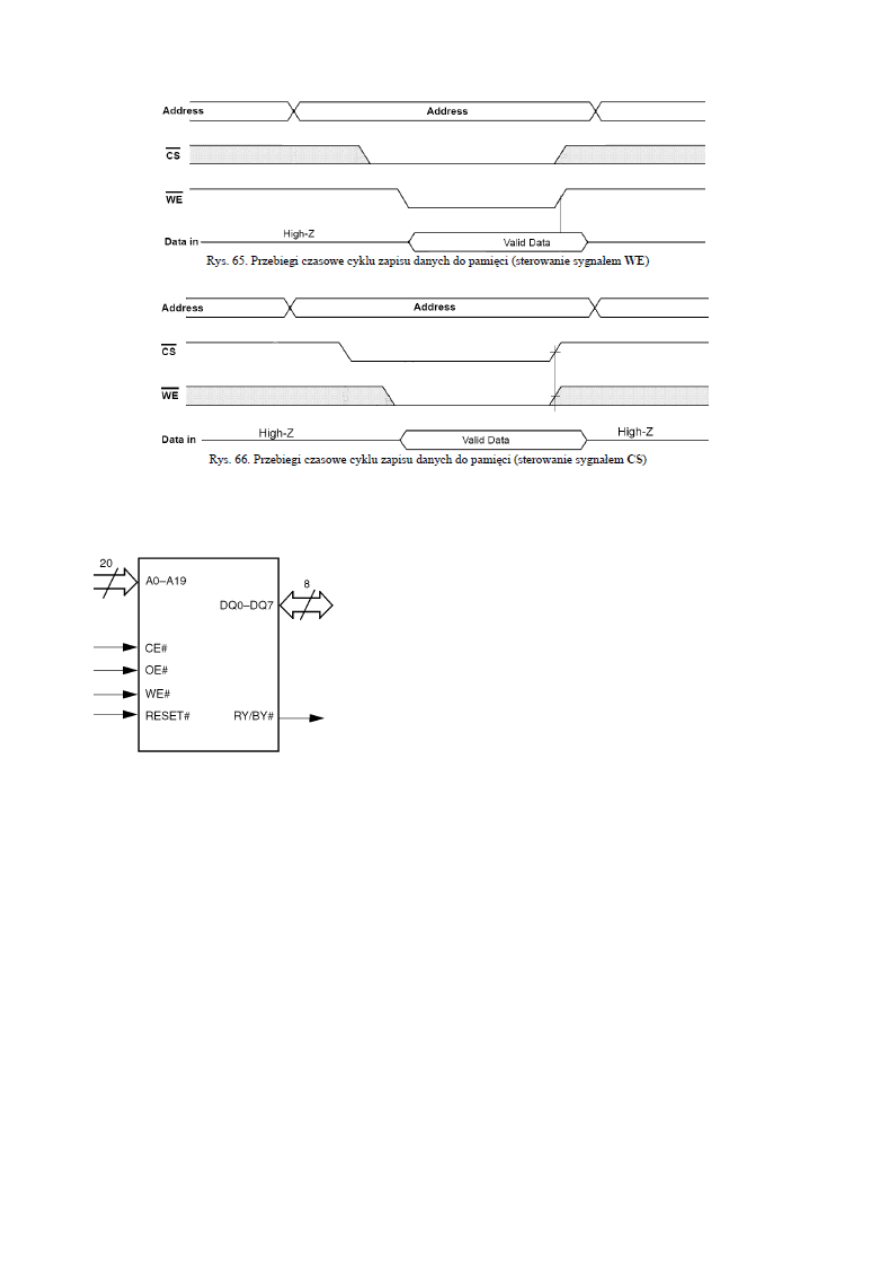

25.

Schemat logiczny, znaczenie linii pamięci FLASH typu NOR o dostępie równoległym i

pojemności np. 1MB

A0 - An - (n+1) bitowa magistrala adresowa; wystawiany jest

na niej n-bitowy adres komórki do odczytu lub zapisu

DQ0-DQ7 – 8-bitowa dwukierunkowa magistrala danych służąca

do wprowadzania i wyprowadzania danych spod adresów

ustawianych na magistrali adresowej

CE# - aktywacja układu poziomem niskim

WE# - niski poziom na tej linii powoduje zapis bajta pod

wskazany adres

OE# - niski poziom na tej linii powoduje wystawienie na

magistrali danych danej spod wskazanego adresu

RESET# - sprzętowy reset wprowadzający pamięć w tryb

odczytu, aktywny stanem niskim

RY/BY# - wyjście służące do sprawdzania czy pamięć zakończyła wewnętrzne algorytmy

kasowania/programowania. Stan wysoki oznacza gotowość na przyjęcie kolejnych poleceń, stan

niski informuje że pamięć jest zajęta

26.

Rozkazy sterujące pamięcią FLASH. Sekwencja rozkazowa poszczególnych rozkazów

pamięci FLASH.

Dla pamięci FLASH każda sekwencja rozkazowa składa się z:

•

dwóch cykli odblokowujących:

•

w pierwszym cyklu następuje wpis wartości AAh pod adres 555h,

•

w drugim cyklu wpisywana jest wartość 55 pod adres 2AAh,

•

w trzecim cyklu następuje wprowadzenie kodu polecenia do rejestru komend, czyli zapis kodu komendy

pod adres 555h, po tym cyklu pamięć znajduje się w trybie zgodnym z wydanym rozkazem,

•

czwarty cykl zależny jest od wydanej komendy:

•

w trybie autoselect następuje odczyt danych identyfikacyjnych,

•

w trybie programowania bajt PD ustawiony na magistrali danych będzie wpisany pod adres PA ustawiony

na magistrali adresowej,

•

w trybie gotowości do kasowania (po wpisie wartości 80h pod adres 555h w trzecim cyklu) cykl ten jest

ponownie pierwszym cyklem odblokowującym dla sekwencji rozkazowych kasowania sektora lub całej

pamięci.

•

cykl piąty jest drugim cyklem odblokowującym dla sekwencji rozkazowych kasowania sektora lub całej

pamięci,

•

w ostatnim szóstym cyklu wprowadzany jest kod rozkazu kasowania całej pamięci (wartość 10h pod adres

555h) lub kasowania wybranego sektora (wprowadzany kod 30h) o adresie S.A.

27. Definicja i wykorzystanie stosu oraz definicja wskaźnika stosu.

Stos - wyróżniony obszar pamięci używany według następujących reguł:

•

Wektory informacji zapisywane są na stos do kolejnych komórek (po kolei pod każdymi adresami),

przy czym żadnego adresu nie wolno pominąć.

•

Odczytujemy wektory informacji w kolejności odwrotnej do ich zapisu.

•

Wektor informacji odczytujemy z ostatnio zapełnionej komórki a zapisujemy do pierwszej wolnej.

Wskaźnik stosu - rejestr zawierający adres ostatniej zapełnionej komórki stosu (wierzchołka stosu).

28. Cechy architektury Von-Neumanna mikroprocesorów.

•

Jednolita przestrzeń adresowa - wszystkie pamięci, rejestry i układy we/wy są umieszczone w

jednej, wspólnej przestrzeni adresowej. W tym przypadku każdej komórce pamięci, niezależnie od

jej typu, przypisany jest niepowtarzalny adres. Czyli rozkazy i dane przechowywane są w tym

samym obszarze adresowania, przez co nie da się rozróżnić danych od rozkazów (instrukcji).

•

Podział przestrzeni adresowej na pamięć programu, pamięć danych oraz obszar we/wy jest

czysto umowny i zależy wyłącznie od rozmieszczenia tych elementów w obszarze adresowym

podczas projektowania systemu. Dlatego mikroprocesor ma dostęp do całej przestrzeni adresowej,

natomiast dekodery adresowe zapewniają mapowanie pamięci na rzeczywiste układy.

•

Mk ma jedną szynę danych wspólną dla danych i programu. Dzięki temu programowanie jest

ułatwione, gdyż dostęp do danych, programu i urządzeń we/wy odbywa się przy użyciu

zunifikowanych rozkazów wykorzystujących te same tryby adresowania.

•

Wykonanie instrukcji wymaga kilku przesłań danych (najpierw bajt z kodem rozkazu, a po nim

bajty z argumentami) po magistrali danych, co czyni tę architekturę zdecydowanie wolniejszą od

harwardzkiej.

29. Cechy architektury harwardzkiej mikroprocesorów wbudowanych w mikrokontrolery.

•

dwie oddzielne szyny dla danych i rozkazów, dzięki czemu w trakcie pobierania argumentów

wykonywanej właśnie instrukcji można równocześnie zacząć pobieranie następnego słowa

rozkazowego. Skraca to cykl rozkazowy i zwiększa szybkość pracy.

•

Obszary adresowe pamięci danych i programu są rozdzielone. Pociąga to za sobą

niejednoznaczność adresów, ponieważ pod tym samym adresem CPU widzi pamięć danych i

programu. W tym przypadku stosuje się inne rozkazy dla pamięci programu i inne dla pamięci

danych.

•

Magistrala danych i rozkazów mają różną szerokość (długość słowa)

•

Wadą tego rozwiązania jest utrudniony przepływ danych z pamięci programu do obszaru

pamięci operacyjnej (danych).

30. Modyfikacje architektury harwardzkiej mikroprocesorów wbudowanych w mikrokontrolery

poprawiające przepływ danych między pamięcią programu a danych.

•

szerokość magistrali programu jest krotnością szerokości magistrali danych

•

wprowadza się dodatkowe bloki pośredniczące w wymianie danych między pamięcią programu a

pamięcią danych

•

rozszerza się listę instrukcji o dodatkowe polecenia obsługujące transfer danych z/do pamięci

programu

31. Definicja, pełnione funkcje oraz obsługa układów we/wy.

Układ we/wy (I/O) - układ elektroniczny pośredniczący w wymianie informacji pomiędzy

mikroprocesorem i pamięcią systemu z jednej strony a urządzeniem peryferyjnym z drugiej. Dla

systemu mikroprocesorowego układ we/wy widoczny jest jako rejestr lub zespół rejestrów o

określonych adresach oraz jako pewien zestaw sygnałów sterujących. Czyli, podobnie jak pamięci

posiadają wejścia adresowe i sterujące.

Urządzenia peryferyjne mogą służyć do wprowadzania/wyprowadzania (np. interfejs USB), bądź

przechowywania informacji (np. karty pamięci SD) lub być układami wykonawczymi

32. Podział i charakterystyka układów we/wy.

Układy współadresowalne z pamięcią operacyjną -

układy, dla których wybór ich rejestru do

zapisu lub odczytu, jest realizowany w taki sam sposób jak komórki pamięci.

•

istnieje potrzeba wydzielenia w obszarze adresowania pamięci przestrzeni dla adresów

układów we/wy, gdyż przestrzenie adresowe pamięci i układów we/wy nie są rozdzielone

•

sygnały sterujące są wspólne dla pamięci i układów we/wy

Układy izolowane - układy, dla których operacja zapisu lub odczytu do ich rejestrów jest

realizowana za pomocą wydzielonych do tego sygnałów sterujących.

•

przestrzenie adresowe pamięci i układów wejścia-wyjścia nadal nie są rozdzielone,

•

ale układy we/wy sterowane są wydzielonymi do tego sygnałami

33. Definicja i właściwości operacji we/wy.

Operacje we/wy - całokształt działań potrzebnych do realizacji wymiany informacji pomiędzy

mikroprocesorem i pamięcią z jednej strony a układami we/wy z drugiej.

Właściwości:

•

Operacje we/wy mogą być od początku do końca sterowane przez procesor

•

Procesor może też zainicjować operację i przekazać jej kontynuowanie specjalizowanemu

układowi

•

Procesor musi komunikować się z wieloma urządzeniami.

•

Komunikacja ta powinna odbywać się często nie tylko w momentach założonych przez

program, ale też w momentach wynikających z normalnego cyklu pracy urządzenia.

•

W systemie musi więc istnieć możliwość poinformowania procesora o konieczności

wymiany danych z konkretnym urządzeniem.

34. Definicja przerwania, zadania sterownika przerwań i schemat obsługi przerwania.

Przerwanie – sygnał powodujący zmianę przepływu sterowania. Pojawienie się przerwania

powoduje wstrzymanie aktualnie wykonywanego programu i wykonanie przez procesor kodu

procedury obsługi przerwania. Realizowane przez sterownik przerwań.

Zadania sterownika przerwań:

•

pośredniczenie w przyjmowaniu zgłoszeń przerwań pomiędzy procesorem i układami

we/wy,

•

przyjmowanie zgłoszeń od wielu układów we/wy

•

wybór spośród wielu zgłoszeń tego, które zostanie obsłużone,

•

sygnalizowanie wyboru przez podanie adresu układu we/wy, z którym zostanie dokonana

wymiana

•

wygenerowanie sygnału zgłoszenia przerwania bezpośrednio do procesora.

Schemat obsługi przerwania:

•

urządzenie peryferyjne wykrywa wystąpienie określonego zdarzenia wymagającego reakcji

mikroprocesora,

•

urządzenie peryferyjne zgłasza CPU, za pośrednictwem układu przerwań, żądanie

przerwania,

•

CPU przerywa aktualnie wykonywaną sekwencję programu i zachowuje w specjalnym

obszarze pamięci – stosie, zawartość licznika rozkazów i wszystkie dane związane z

aktualnie wykonywanym programem,

•

CPU przechodzi do wykonywania programu napisanego specjalnie przez użytkownika do

obsługi danego zdarzenia

•

po wykonaniu tego programu CPU odtwarza ze stosu dane związane z przerwanym

programem i kontynuuje wykonanie przerwanego programu.

35.

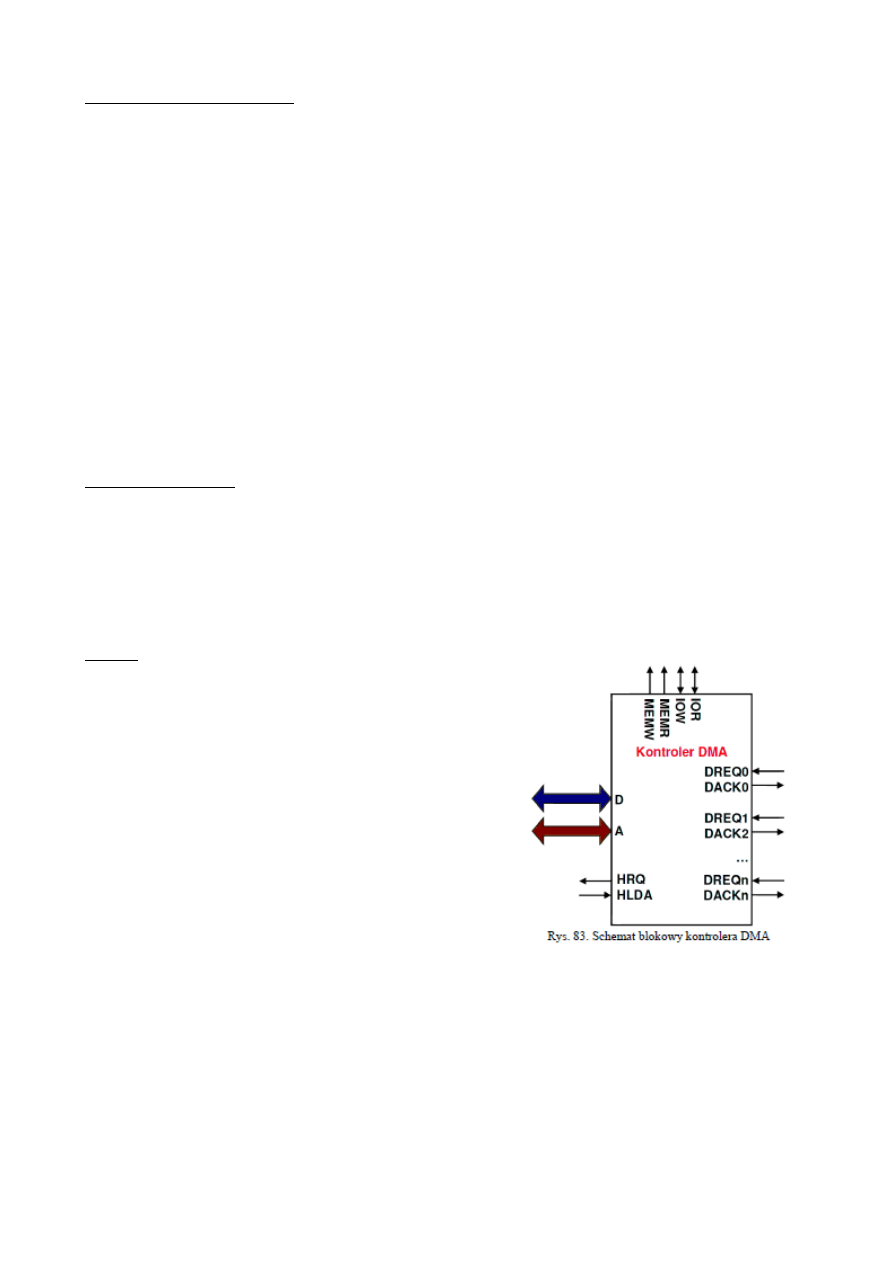

Definicja i właściwości bezpośredniego dostępu do pamięci, schemat logiczny i cechy

kontrolera DMA.

Bezpośredni dostęp do pamięci (DMA) - operacja wejścia-wyjścia inicjowana przez

mikroprocesor, który przekazuje sterowanie jej realizacją sterownikowi DMA.

Właściwości DMA:

•

Składa się ona z trzech etapów: inicjalizacji, realizacji, zakończenia.

•

Transmisja informacji przebiega pomiędzy układem wejścia-wyjścia a wydzielonym

obszarem buforowym w pamięci.

•

Przebieg operacji nadzoruje sterownik DMA, poprzez generację wszystkich sygnałów

sterujących i adresów potrzebnych do realizacji wymiany.

•

W tym celu sterownik DMA przejmuje na czas wymiany informacji kontrolę nad

magistralami, stając się zarządcą magistral

Cechy:

•

Kontroler DMA jest samodzielnym procesorem

mogącym przejąć sterowanie magistral systemu

mikroprocesorowego.

•

Kontroler DMA zazwyczaj posiada zwielokrotnione

zasoby pozwalające na realizacje kilku kanałów

DMA o różnym priorytecie.

•

Każdy kanał jest obsługiwany przez oddzielna,

wewnętrzna logikę w kontrolerze połączoną z

rejestrem adresującym pamięć i licznikiem słów

pozostałych do przesłania.

•

Kontroler jest układem programowalnym,

•

Programowanie kontrolera DMA jest realizowane

przez mikroprocesor i polega na zapisaniu

odpowiednich wartości do jego wewnętrznych

rejestrów, widzianych jako rejestry w przestrzeni I/O.

36. Definicje rozkazu, listy instrukcji, cyklu rozkazowego, maszynowego.

Rozkaz - wektor informacji cyfrowej odpowiadający danej operacji podstawowej, o jaką

wykonanie od mikroprocesora może zażądać programista.

Lista rozkazów -zestawem wszystkich rozkazów realizowanych przez mikroprocesor.

Cykl rozkazowy - ciąg czynności, które wykonuje układ sterowania jednostki centralnej w

czasie realizowania jednego rozkazu. Składa się z jednego lub kilku cykli maszynowych.

Cykl maszynowy - cykl, w którym następuje przesłanie danych (odczyt lub zapis) między:

jednostką centralną a pamięciową lub układem wejścia – wyjścia, lub rejestrami procesora.

37. Struktura rozkazu (instrukcji) oraz jego symboliczny zapis.

Struktura rozkazu:

•

kod operacji – unikatowy dla rozkazu; określa operację, jaka ma być przeprowadzona

•

odniesienie do argumentów źródłowych, którymi mogą być: dane bezpośrednie, adresy

pamięci lub układów we/wy, rejestry procesora,

•

odniesienie do argumentów przeznaczenia lub wyniku, którymi mogą być: adresy pamięci

lub układów we-wy, rejestry procesora

•

odniesienie do następnego rozkazu – określa adres następnego rozkazu, który będzie

wykonany po rozkazie bieżącym.

Symboliczny zapis rozkazu:

MNEMONIK argument_1, argument_2, .., argument_n

gdzie:

MNEMONIK – nazwa operacji podstawowej, najczęściej jest skrótem wyrazu z j. angielskiego

opisującego daną operację podstawową (ADD – dodawanie, INC – inkrementacja).

argument_x – dana albo adres rejestru lub komórki pamięci zawierającej daną, na której ma być

wykonana operacja podstawowa.

38. Definicja adresowania, trybu adresowania oraz tryby adresowania.

Adresowanie - w

yznaczanie adresu komórki pamięci zawierającej argument (operand) na

podstawie informacji zawartej w rozkazie.

Tryb adresowania - sposób wskazywania (dostępu) na argumenty wykorzystywane w trakcie

wykonania instrukcji.

•

Implikowane, np. INC A, CPL A, NOP

•

Rejestrowe, np. ADD A, R1

•

Natychmiastowe, np. ADD A, #dana, MOV A, #0F3h

•

Bezprośrednie, np. ADD A, adres, MOV A, 0F8h

•

Indeksowe

•

Pośrednie, np. MOV A, @R1, ADD A, @R0

•

Bitowe, np. SET bit, CLR bit

•

Względne, np. JNB P0.1, LOOP

39. Cechy architektury CISC mikroprocesorów.

•

duża liczba rozkazów (instrukcji), występują instrukcje wspierające języki wysokiego poziomu,

•

mała optymalizacja cyklów rozkazowych – niektóre rozkazy potrzebują dużej liczby cykli

procesora do wykonania,

•

występowanie złożonych, specjalistycznych rozkazów, które współpracują na ogół tylko z

określonymi rejestrami i wymagają stosowania określonych trybów adresowania,

•

duża liczba trybów adresowania,

•

do pamięci może się odwoływać bezpośrednio duża liczba rozkazów,

•

mniejsza od procesorów RISC częstotliwość taktowania procesora,

•

powolne działanie dekodera rozkazów,

•

każda instrukcja może wykonać kilka operacji niskiego poziomu, jak na przykład pobranie z

pamięci, operację arytmetyczną, albo zapisanie do pamięci a to wszystko w jednej instrukcji.

40. Cechy architektury RISC mikroprocesorów oraz pojęcie ortogonalności.

•

Zredukowana liczba rozkazów do niezbędnego minimum.

•

Zbiór realizowanych instrukcji jest ograniczony i spełnia warunki ortogonalności (symetrii).

•

Zmniejszona liczba trybów adresowania - kody rozkazów są prostsze, bardziej zunifikowane.

•

Zwiększenie liczby rejestrów roboczych - zmniejszenie liczby odwołań do pamięci.

•

Ograniczenie komunikacji pomiędzy pamięcią, a procesorem – do przesyłania danych

pomiędzy pamięcią, a rejestrami służą dedykowane instrukcje load oraz store; pozostałe instrukcje

mogą operować wyłącznie na rejestrach

•

Procesor jest zbudowany zgodnie z architekturą harwardzką (mikrokontrolery),

•

Procesor wykorzystuje przetwarzanie potokowe w celu zwiększenia szybkości wykonywania

programu, gdyż wszystkie rozkazy wykonują się w jednym cyklu maszynowym, co pozwala na

znaczne uproszczenie bloku wykonawczego.

Pojęcie ortogonalności oznacza unifikację instrukcji według następujących zasad:

•

każda instrukcja może operować na dowolnym rejestrze roboczym. Procesor nie ma więc

wyróżnionych rejestrów, które są specjalizowane do wykonywania określonych rodzajów operacji,

•

każda instrukcja może wykorzystywać dowolny tryb adresowania argumentów,

•

nie ma ukrytych związków między instrukcjami (efektów ubocznych), które powodowałyby

nieprzewidziane reakcje systemu w zależności od kontekstu użycia rozkazów w programie,

•

kody rozkazów i formaty instrukcji są zunifikowane. W szczególności wszystkie instrukcje

zajmują w pamięci programu taką samą liczbę bajtów.

41. Operacje podstawowe wykonywane przez mikroprocesor oraz składnia asemblera.

Operacje:

•

transferu danych

•

arytmetyczne, logiczne, przesunięcia

•

sterujące przepływem programu

•

wejścia-wyjścia

•

operacje na bitach

•

sterowania CPU

Składnia:

[etykieta:] instrukcja [operandy] [komentarz]

etykieta – odwołuje się do niej przy skokach i wywołaniach funkcji,

instrukcja – kod rozkazu mikroprocesora jak i również dyrektywa asemblera,

operandy – argumenty wymagane przez instrukcję

komentarz – najczęściej zaczyna się od średnika, opis algorytmu itp.

42. Definicja i podział koprocesorów, definicja koprocesora arytmetycznego i jego sposób

sterowania.

Koprocesory - układy scalone wielkiej skali integracji lub wewnętrzne bloki mikroprocesora

współpracujące z mikroprocesorem, wyspecjalizowane do w bardzo szybkiego wykonywania

pewnych funkcji.

Podział:

•

arytmetyczne – przyspieszenie operacji na liczbach zmiennoprzecinkowych

•

graficzne – przyspieszające tworzenie i manipulacje obrazami

•

wejścia/wyjścia – przyspieszające dostęp do danych z urządzeń zewnętrznych

Koprocesor arytmetyczny (FPU) - wyspecjalizowany układ scalony lub wewnętrzny blok

mikroprocesora realizujący sprzętowo operacje matematyczne na liczbach zmiennoprzecinkowych.

Sterowanie koprocesorem przez mikroprocesor odbywa się za pomocą trzech klas instrukcji:

•

transferu danych między rejestrami koprocesora a pamięcią,

•

transferu danych między rejestrami koprocesora a rejestrami roboczymi mikroprocesora,

•

uruchomienia przetwarzania danych przez koprocesor.

43. Sposoby zwiększania mocy obliczeniowej mikroprocesorów i ich charakterystyka.

•

potokowe przetwarzanie rozkazów przez mikroprocesor (w tym przetwarzanie superpotokowe),

•

superskalarne przetwarzanie rozkazów (wykonywanie kilku równoległych potoków przez

mikroprocesor),

•

równoległe przetwarzanie rozkazów, w tym wielowątkowość i wieloprocesorowość,

•

stosowanie podejścia VLIW i architektury mikroprocesorów EPIC

•

przyśpieszenie dostępu do pamięci przez wykorzystanie pamięci podręcznej Cache.

44. Definicja i właściwości przetwarzania potokowego.

Przetwarzanie potokowe - równoczesne przetwarzanie przez mikroprocesor grupy rozkazów,

znajdujących się w różnych fazach cyklu rozkazowego.

Właściwości:

•

rozłożenie wykonania pojedynczej instrukcji na ciąg prostych etapów (faz), z których każdy może

być wykonany w jednym cyklu zegara,

•

procesor wykonuje kilka instrukcji jednocześnie, ale w różnych fazach (obsługuje potok

instrukcji),

•

każda instrukcja musi mieć te same fazy wykonania,

•

w jednym momencie wykonuje się tyle rozkazów ile jest faz. Każdy wykonywany rozkaz

znajduje się w innej fazie,

•

w przetwarzaniu potokowym nie przyspieszamy wykonania pojedynczego rozkazu (nawet go

spowalniamy), gdyż zysk uzyskuje się tylko dzięki zrównolegleniu wykonywania operacji –

przyspieszenie w stosunku do architektury tradycyjnej jest proporcjonalne do liczby faz instrukcji,

•

podczas przetwarzania potokowego w każdym cyklu zegara wykorzystywane są wszystkie

zasoby procesora

•

występują konflikty zasobów wtedy, gdy dwie instrukcje wymagają dostępu do tych samych

zasobów procesora:

•

konflikty (hazardy) strukturalne – instrukcje chcą skorzystać z tego samego zasobu

•

konflikty danych – rozkaz potrzebuje rejestru, który zapisuje poprzedni rozkaz,

•

konflikty sterowania – np. w przypadku rozkazu skoku nie wiadomo, który rozkaz należy pobrać

jako następny

•

szczególne znaczenie ma optymalizacja kodu programu, w celu minimalizacji konfliktów.

45. Podział instrukcji na fazy w przetwarzaniu potokowym.

•

Pobranie instrukcji z pamięci (IF) – wykonuje zapis do rejestru IR i zwiększanie PC,

•

Dekodowanie instrukcji i odczyt rejestrów (ID) – spekulatywne odczytywanie rejestrów

potrzebnych do operacji,

•

Wykonanie operacji lub wyliczenie adresu (EX) – wykorzystanie ALU i zapis wyniku do rejestru

buforowego,

•

Dostęp do pamięci (MEM) – odczyt lub zapis do pamięci (do lub z rejestrów buforowych),

•

Zapis wyniku do rejestru (WB) – zapis wyniku z rejestru buforowego do rejestru procesora.

46. Definicja pamięci podręcznej Cache.

Pamięć podręczna (CACHE memory) – pamięć (o bardzo krótkim czasie dostępu i zazwyczaj

o niewielkiej pojemności) umieszczona między współpracującymi ze sobą elementami

mikrosystemu, która pośredniczy we wszystkich operacjach transmisji danych. Eliminuje się w

ten sposób zjawisko wynikające z faktu, iż szybsze urządzenia (np. mikroprocesor) muszą być

sztucznie spowalniane, aby urządzenia wolniejsze za nimi nadążały (np. zewnętrzne pamięci

DRAM).

Wyszukiwarka

Podobne podstrony:

Nasze opracowanie pytań 1 40

Opracowanie pytań z anatomii

opracowanie pytań z optyki

Maszyny Elektryczne Opracowanie Pytań Na Egzamin

opracowanie pytan id 338374 Nieznany

opracowanie pytan karafiata

Opracowanie pytań 2 kolokwium

cw 3 broma opracowanie pytan 810

Nhip opracowanie pytan id 31802 Nieznany

filozofia opracowanie pytań

opracowanie pytan Automatyka

pytania egz ekonimak II, OPRACOWANIE PYTAŃ NA EGZAMIN

Zestaw 88 Kasia Goszczyńska, materiały farmacja, Materiały 3 rok, Od Ani, biochemia, biochemia, opra

opracowane zestawy, OPRACOWANIE PYTAŃ NA EGZAMIN

Opracowanie pytań MAMET METALE

egzamin z sorbentów opracowanie pytań 1 2 JM

Opracowanie pytań na zaliczenie Opto

więcej podobnych podstron