1

ĆWICZENIE LABORATORYJNE Nr 3

Temat: Badanie bramek logicznych DTL i inwertora CMOS

Cel ćwiczenia: Poznanie budowy i zasad działania bramek logicznych zbudowanych z

elementów bipolarnych i CMOS oraz pomiary ich charakterystyk.

Tematyka sprawdzianu wstępnego:

1. Symbole graficzne i tabelki prawdy bramek logicznych: AND, OR, NOT, NAND, NOR,

EX-OR, EX-NOR.

2. Budowa (schemat ideowy), działanie, charakterystyki przejściowe U

O

=f(U

I

) i poboru

prądu ze źródła zasilania I

CC

=f(U

I

), I

DD

=f(U

I

) inwertora DTL i CMOS oraz 2- wejściowej

bramki NAND-DTL. Czas propagacji t

p

, czasy narastania t

r

i opadania t

f

zboczy impulsu,

czas trwania t

i

impulsu.

3. Charakterystyka wejściowa (przy jakiej wartości napięcia U

BE

zaczyna płynąć prąd bazy

I

B

i prąd kolektora I

C

) i wyjściowa tranzystora bipolarnego (np. BC107) występującego w

układzie DTL, jego prosta obciążenia. W jakich stanach przebywa tranzystor w układach

cyfrowych (zaznaczyć punkty pracy tranzystora na charakterystyce wyjściowej i prostej

obciążenia w stanie L i stanie H na wyjściu układu DTL)? Warunki nasycenia i zatkania

tranzystora bipolarnego. Narysować uproszczone modele tranzystora bipolarnego w

stanie a) nasycenia, b)zatkania i uzasadnić, dlaczego można takie modele stosować.

4. Charakterystyka diody krzemowej detekcyjnej i diody Shotky’ego, napięcia U

P

oraz U

F

–

nazwy i przybliżone wartości tych napięć.

5. Symbole i charakterystyki przejściowe tranzystorów MOS z kanałem indukowanym typu

# i typu P (narysować i opisać). Co oznaczają podawane w katalogach parametry

tranzystorów MOS: BV

DSS

(Breakdown V

DS

przy V

GS

=0V), V

GS(TH)

, I

D(O#)

, r

DS(O#)

, g

fs

,

t

d(O#)

, t

d(OFF)

, C

ISS

, C

OSS

, C

RSS

. Warunki włączenia i odcięcia tranzystorów N-MOS i

P-MOS z kanałem indukowanym.

6. Dołączyć do źródła zasilania: a) tranzystor N-MOS, b) tranzystor P-MOS tak, aby był: a)

w stanie nienasycenia (włączony), b) w stanie odcięcia (wyłączony) i wskazać jego

punkty pracy na charakterystyce przejściowej.

Wyposażenie stanowiska laboratoryjnego

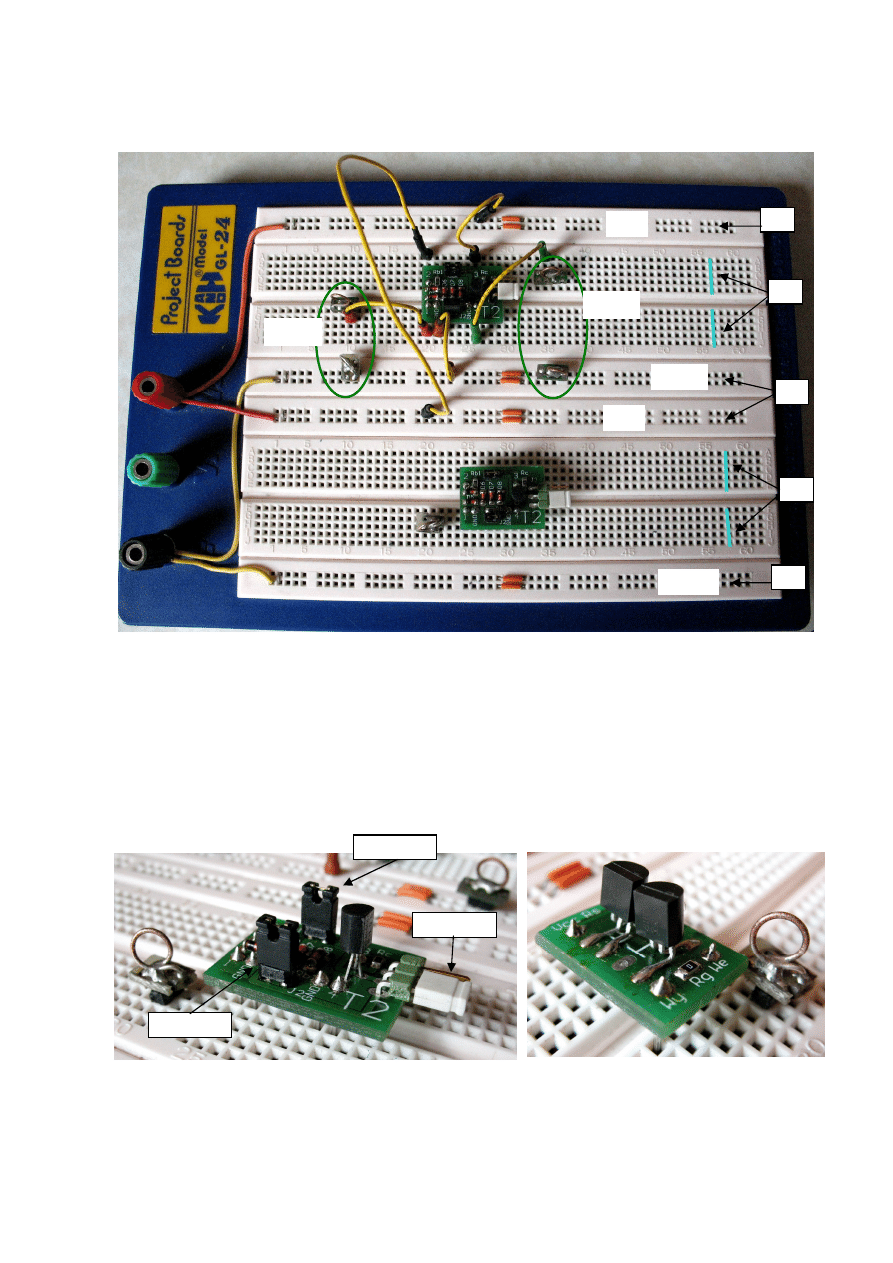

1. Panel projektowy GL-24 (lub GL-12F) z uszkami pomiarowymi.

2. Płytki drukowane T2 i T5 z badanymi układami.

3. Przewody do łączenia miernika (zamiast zwory J1) i układów pomiarowych.

4. Zasilacz stabilizowany.

5. Woltomierz cyfrowy (2 szt.).

6. Miernik uniwersalny.

7. Generator fali prostokątnej.

8. Oscyloskop dwukanałowy.

Uwaga: Panel projektowy GL24, płytki T2 i T5, uszka pomiarowe i przewody do połączeń są

pokazane w Dodatku A. Montując układ pomiarowy należy utworzyć z uszek

pomiarowych punkt pomiarowy wejściowy (PP1) z lewej strony płytki i punkt

pomiarowy wyjściowy (PP2) z prawej – jak na rys. A1. Do tych punktów

pomiarowych należy dołączać przyrządy pomiarowe (generator, oscyloskop,

woltomierze).

2

Treść ćwiczenia

3.1. Pomiar parametrów statycznych bramki DTL

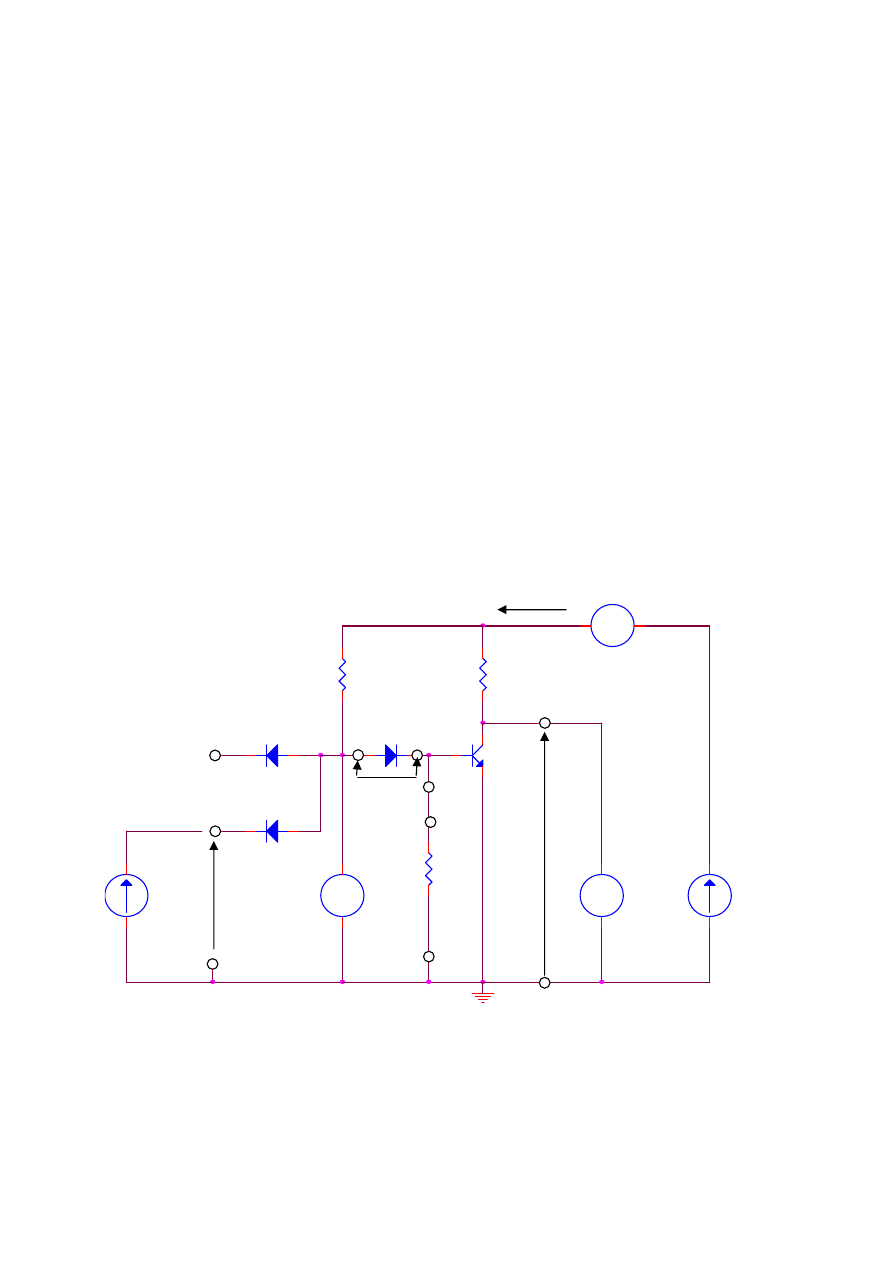

a) Na panelu GL-24 (lub GL-12F) zmontować układ pomiarowy jak na rys. 3.1.

b) Podając na wejścia A i B napięcia U

IA

i U

IB

o wartościach jak w tabl. 3.1a zmierzyć

wartości napięć U

C

i U

OF

(uzupełnić tabl. 3.1a).

c) Przyjmując konwencję dodatnią w zakresie napięć dodatnich, tzn. że zakres napięć

(0.0....+1.5V) odpowiada ‘0’, a zakres (+3.5...+5.0V) odpowiada ‘1’, uzupełnić kolumnę

F i określić jaką funkcję realizuje układ z rys. 3.1.

d) Odłączyć rezystor R

B2

(wyjmując zworę J2). Zwierając diodę D3 (zworą J1) i podając

napięcia U

IA

, U

IB

jak w tabl. 3.1 zaobserwować zmiany w działaniu układu z rys. 3.1.

Jaką rolę pełni dioda D3?

e) Wykonać pomiary napięcia wyjściowego U

OF

i prądu I

CC

pobieranego ze źródła zasilania

w funkcji napięcia wejściowego U

I

=0.0...+5.0V. Wyniki pomiarów umieścić w tabl. 3.1b.

Na podstawie wyników pomiarów wykreślić na jednym rysunku charakterystykę

przejściową U

O

=f(U

I

) oraz charakterystykę poboru prądu ze źródła I

CC

=f(U

I

) dla badanej

bramki DTL.

Rys. 3.1. Bramka logiczna NAND-DTL

A

B

D1

D2

V

V

D3

T

mA

Ucc=+5V

CC

I

O

U

1

C

R

K

=

F

2

B

R

=

5

1

K

K

C

1

B

R

= 10

5

K

K

C

U

I

U

J2

J1

3

Tabela 3.1a.

A

U

IA

[V]

B

U

IB

[V]

U

C

[V]

U

OF

[V]

F=..........

0

0.0

0

0.0

0

0.0

1

+5.0

1

+5.0

0

0.0

1

+5.0

1

+5.0

Tabela 3.1b.

U

IA(B)

[V]

U

OF

[V]

I

CC

[mA]

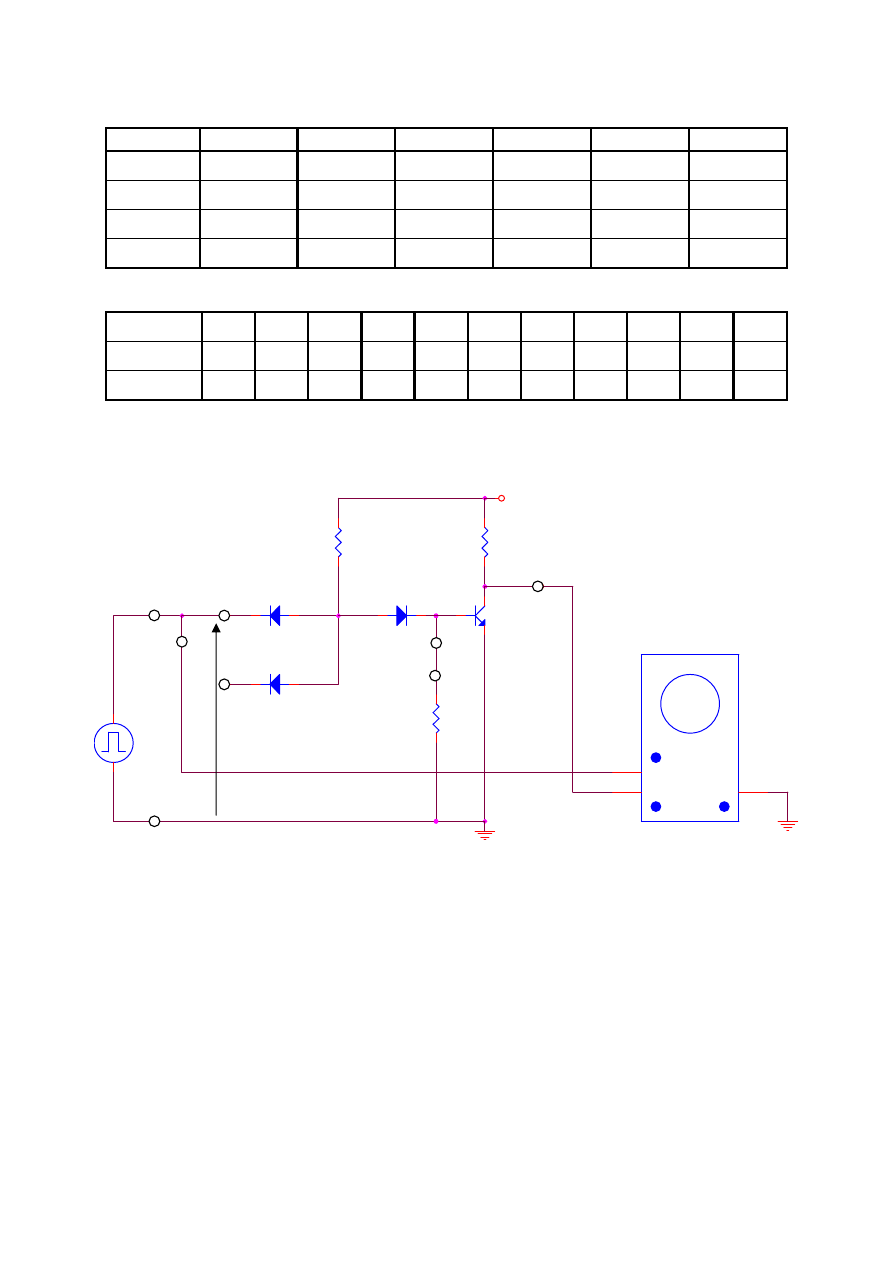

3.2. Pomiar parametrów dynamicznych bramki DTL

Rys. 3.2. Układ do pomiaru parametrów dynamicznych bramki NAND-DTL

a) Do wyjścia F układu z rys. 3.2 dołączyć kanał B (2) oscyloskopu.

b) Do wejścia informacyjnego A (lub B) dołączyć generator impulsów prostokątnych

o amplitudzie U

G

=+5V i częstotliwości ok. 10. kHz oraz kanał A (1) oscyloskopu.

Oscyloskop synchronizować z kanału A (1).

c) Podając na wejście sterujące B (lub A) poziomy ‘0’(0.0V) i ‘1’ (+5.0V) zaobserwować

działanie układu. Jak zachowuje się układ, jeśli wejście sterujące jest odłączone („wisi

w powietrzu”)?

d) Odłączyć rezystor R

B2

(wyjmując zworę J2) i zaobserwować, jaki jest wpływ rezystora

R

B2

na czas włączania i czas wyłączania tranzystora T.

e) Dołączyć do wyjścia F obciążenie R

L

=1k, C

L

=56pF i zaobserwować wpływ dołączonego

obciążenia na poziom i kształt sygnału wyjściowego.

Ucc=+5V

A

B

A

B

D1

D2

D3

T

G

OSC

A

B

GND

A

U

F

2

B

R

=

5

1

K

K

1

B

R

=

10

5

K

K

1

C

R

K

=

J2

4

f) Naszkicować obserwowane przebiegi na wejściu A i wyjściu F oraz zmierzyć parametry

impulsu wyjściowego (wpisać do tabeli 3.2):

Tabela 3.2.

R

B2

=5k

R

B2

odłączony

t

i

[ns]

t

r

[ns]

t

f

[ns]

t

pHL

[ns]

t

pLH

[ns]

f

max

[MHz]

•

t

r

– czas narastania zbocza na wyjściu,

•

t

f

– czas opadania zbocza na wyjściu,

•

t

i

– czas trwania impulsu wyjściowego,

•

t

pHL

– czas propagacji zbocza opadającego,

•

t

pLH

– czas propagacji zbocza narastającego,

•

f

max

– maksymalną częstotliwość sygnałów przenoszoną przez bramkę bez

zniekształceń przy R

B2

=5k i R

B2

odłączonym.

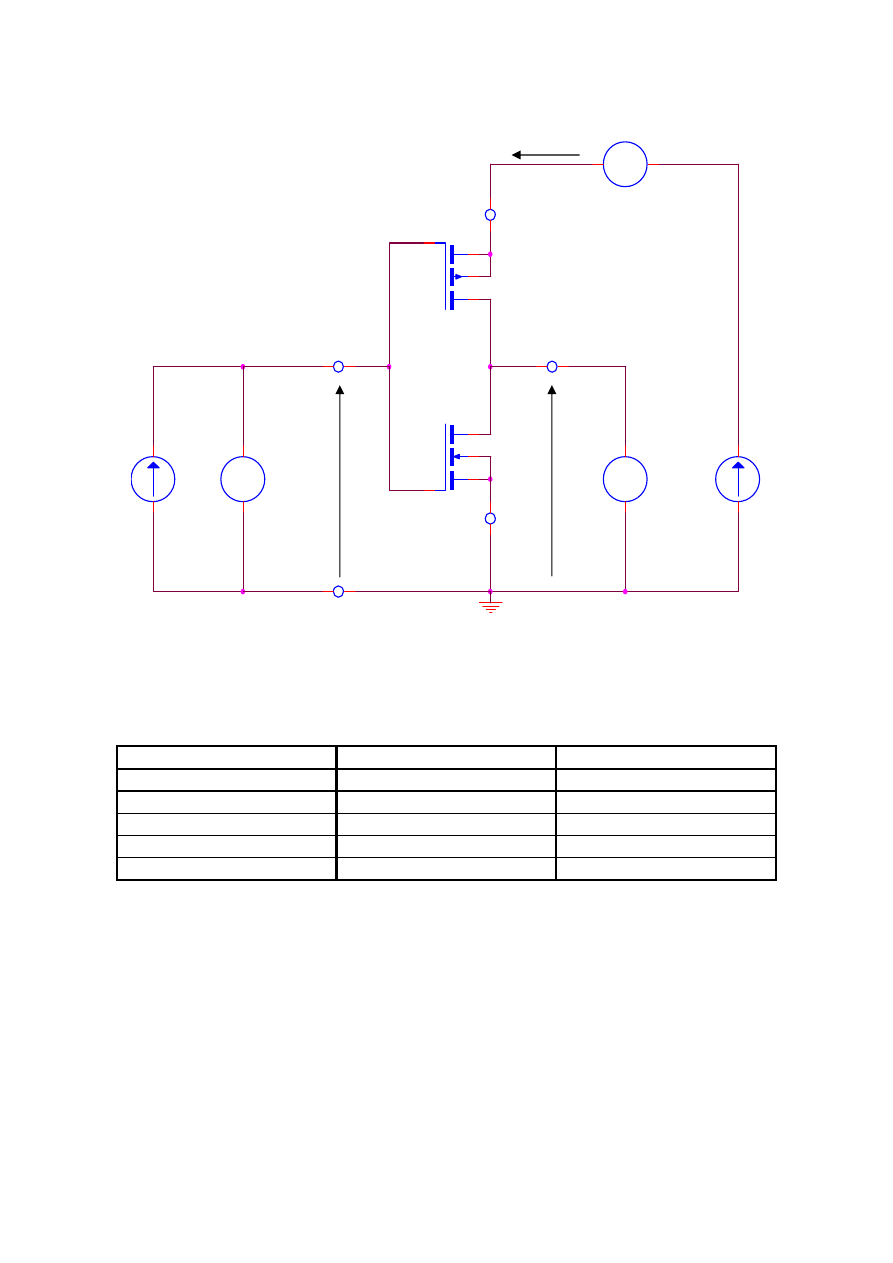

3.3. Pomiar parametrów statycznych inwertora CMOS

a) Na panelu GL24 (lub GL12F) zmontować układ pomiarowy jak na rys. 3.3.

b) Ustawiając wartości U

I

wg tabl. 3.3a i mierząc wartości U

O

sprawdzić działanie inwertora

(uzupełnić tabl. 3.3a) i zaobserwować zjawisko zatrzaskiwania w układzie CMOS. Na

czym to zjawisko polega?

c) Przeprowadzić pomiary napięcia wyjściowego U

O

oraz prądu I

DD

pobieranego ze źródła

zasilania w funkcji napięcia wyjściowego U

I

. Wyniki wpisać do tabeli 3.3b.

d) Na podstawie wyników pomiarów z tabeli 3.3b wykreślić na jednym rysunku

charakterystyki U

O

=f(U

I

) oraz I

DD

=f(U

I

) i wyjaśnić ich kształt.

Tabela 3.3a.

A

U

I

[V]

U

O

[V]

F=

0

1

Tabela 3.3b.

U

I

[V]

U

O

[V]

I

DD

[mA]

[µA]

5

Rys. 3.3. Inverter CMOS

Tranzystory:……………

T1

T2

Typ

Kanał

U

Ddmax

[v]

I

Dmax

[mA]

U

Gsmax

[V]

U

TH

[V]

..

..

..

mA

V

V

..

..

T1

.

.

.

.

T2

.

.

.

.

O

U

5

DD

U

V

= +

DD

I

I

U

F

A

Uwaga:

T1: VP 2206, T2: VN 2224 – U

DD

=+4V

T1: IRFD9120, T2: IRFD110 - U

DD

=+6V

6

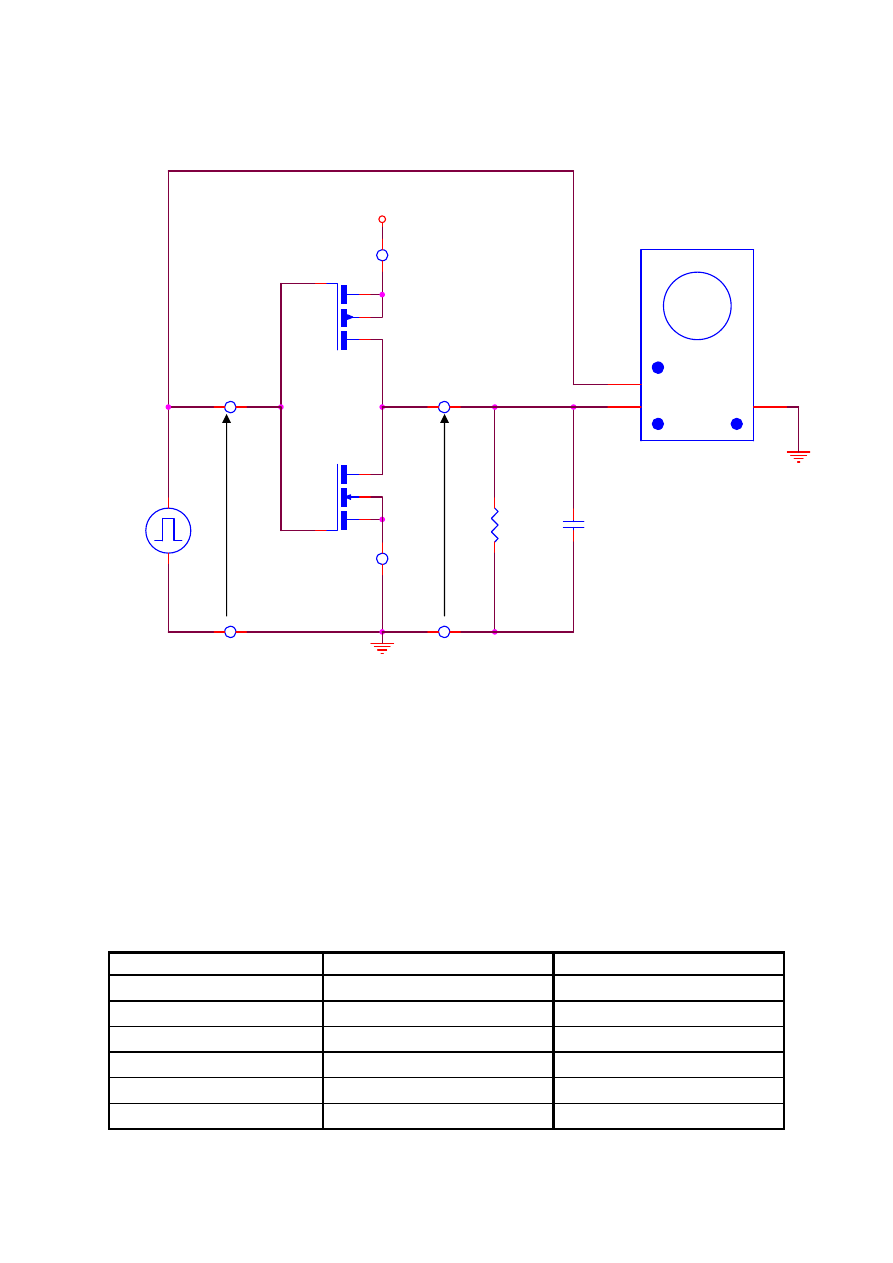

3.4. Pomiar parametrów dynamicznych inwertora CMOS

Rys. 3.4. Układ do pomiaru parametrów dynamicznych invertera CMOS

a) Na panelu GL24 (lub GL12F) połączyć układ pomiarowy jak na rys. 3.4.

b) Zmieniając poziom sygnału z generatora G fali prostokątnej w granicach 0V....U

DD

obserwować kształt napięcia U

O

. Przy jakim poziomie U

I

inwertor działa poprawnie?

c) Dołączyć do wyjścia F obciążenie R

L

=1k, C

L

=56pF i zaobserwować wpływ obciążenia

na poziom i kształt sygnału wyjściowego.

d) Naszkicować przebiegi U

I

oraz U

O

w poprawnie działającym układzie bez obciążenia i z

obciążeniem i pomierzyć parametry dynamiczne inwertora (tabl. 3.4).Jak wpływa

obciążenie na kształt impulsu wyjściowego - dlaczego?

LL

Tabela 3.4.

Bez obciążenia

Z obciążeniem

t

i

[ns]

t

r

[ns]

t

f

[ns]

t

pHL

[ns]

t

pLH

[ns]

f

max

[MHz]

Udd=+5V

A

B

..

..

..

..

..

Gen

OSC

A

B

GND

..

T1

.

.

.

.

T2

.

.

.

.

SS

U

O

U

F

A

I

U

Patrz Uwaga na

rys. 3.3

R

L

C

L

R

L

=1kΩ

C

L

=56pF

7

Dodatek A

1 – na tych listwach wszystkie punktu są zwarte

2 – na tych listwach te punkty są zwarte w każdej kolumnie i służą do łączenia układów

PP1, PP2 – punkty pomiarowe wejściowy i wyjściowy

+U – na tych listwach będzie napięcie zasilania po dołączeniu panelu do zasilacza

G#D – na tych listwach będzie masa zasilacza (GROUND)

Rys. A1 Panel projektowy GL-24 z płytką T2

Rys A2. Płytki T2 (NAND-DTL) i T5 (NOT-CMOS)

zwora J1

zwora J3

zwora J2

PP2

PP1

1

1

2

1

+U

+U

GND

GND

2

Wyszukiwarka

Podobne podstrony:

wykład 6 instrukcje i informacje zwrotne

Instrumenty rynku kapitałowego VIII

05 Instrukcje warunkoweid 5533 ppt

Instrukcja Konwojowa

2 Instrumenty marketingu mix

Promocja jako instrument marketingowy 1

Promocja jako instrument marketingowy

T3 KONSUMENCI I ICH ZACHOWANIE pokaz

t3 Mix PRODUKT

ryzyko zawodowe t3

więcej podobnych podstron