RISC/CISC

1/30

CISC / RISC

1. CISC - IBM System 360

2/30

1

2

3

4

5

Problemy z pierwszymi pamięciami

1. CISC - IBM System 360

3/30

1

2

3

4

5

Architektura komputerów mainframe System/360 1

¾ Ok. 304 instrukcji o zmiennej długości i

czasie wykonania

¾ 3 różne możliwe długości instrukcji

¾ 16 trybów adresowania

System/360 Model 64,

Źródło: wikipedia

1. CISC - IBM System 360

4/30

1

2

3

4

5

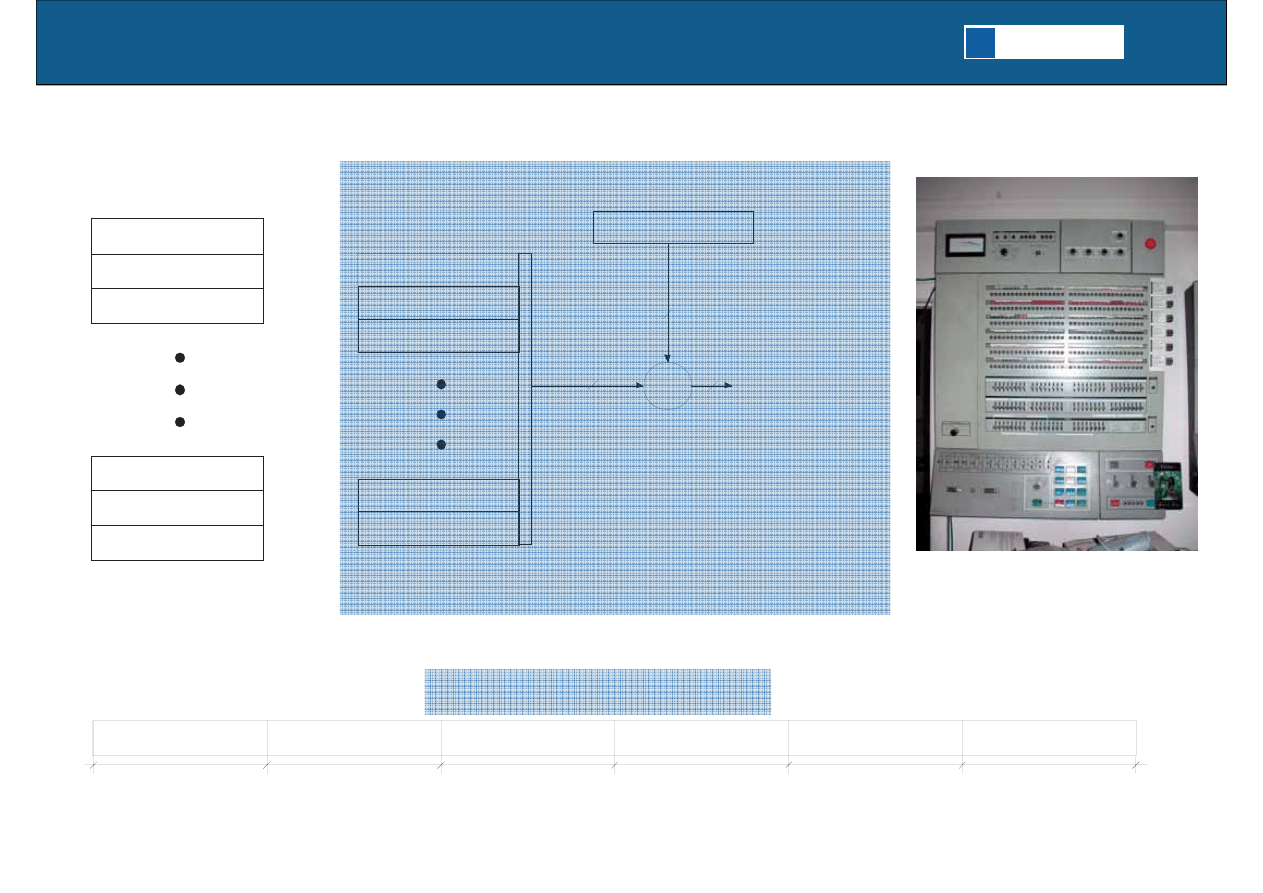

Architektura komputerów mainframe System/360 2

offset

2

3

E

F

Base Reg.

1

+

Instrukcja...

12

Szyna

adresowa

32

24

General Purpose Reg.

R0

R1

R2

R13

R14

R15

GPR

OP CODE

par0

par0/1

par1/2

par2/3

par2/3

1B

1B

1B

1B

1B

1B

INSTRUKCJA:

ZMIENNA DŁUGOŚĆ

SEGMENT + OFFSET

Rozszerzenia: Commercial Instruction Set, Scientific Instruction Set

1. CISC - IBM System 360

5/30

1

2

3

4

5

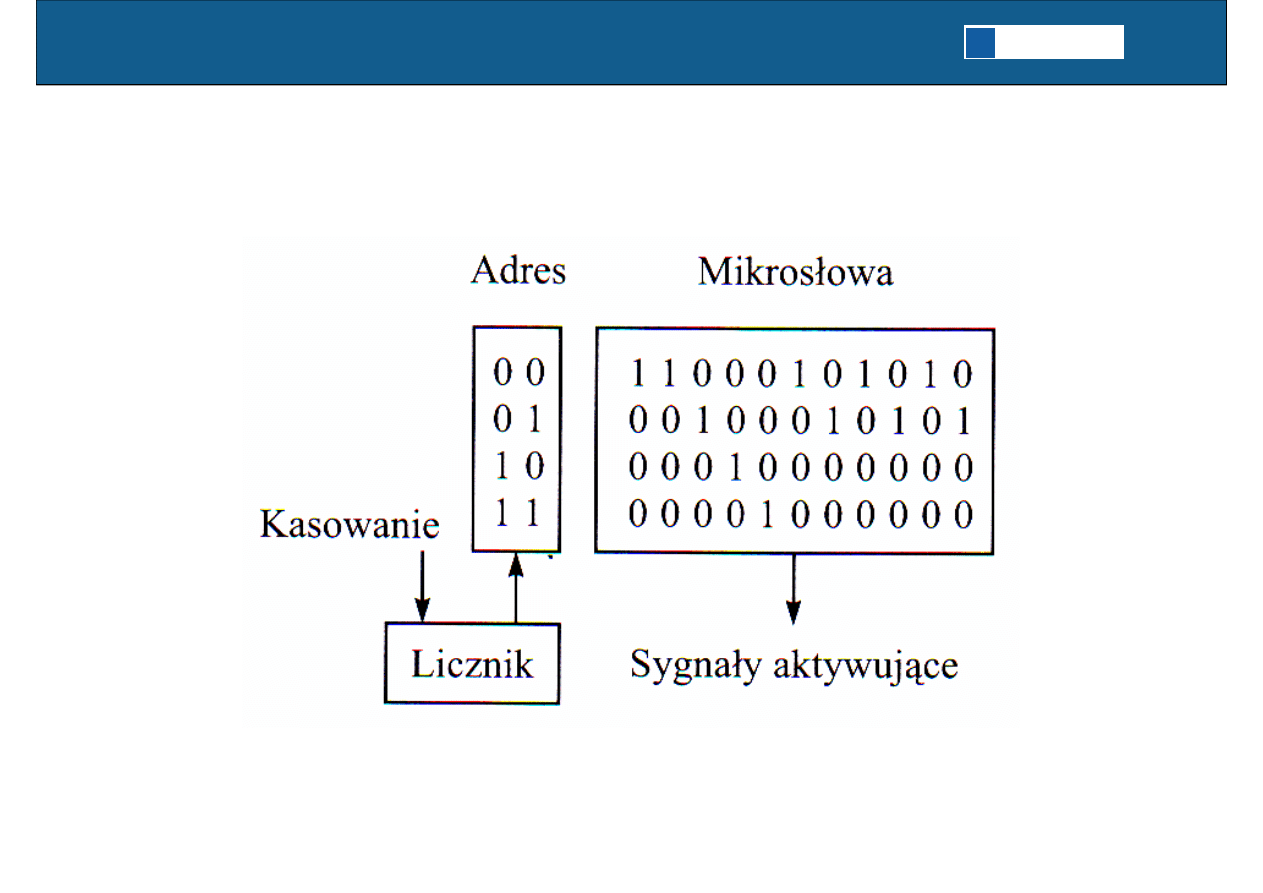

Mikroprogram

1. CISC - IBM System 360

6/30

1

2

3

4

5

Architektura komputerów mainframe System/360 3

KANAŁ wejścia/wyjścia (IO):

Byte Multiplexer Channel – urządzenia o niskiej prędkości

Selector Channel – urządzenia o dużej prędkości

Tryb: 1-byte, 2-byte, 4-byte, „burst”

w stronę koncepcji DMA – Direct Memory Access

1. CISC - IBM System 360

7/30

1

2

3

4

5

Architektura komputerów mainframe System/360 4

System operacyjny:

BOS/360 –Basic Operating System / 360

DOS/360 – Disk Operating System / 360

OS/360 MVT – Operating System

2. CISC - 8086

8/30

1

2

3

4

5

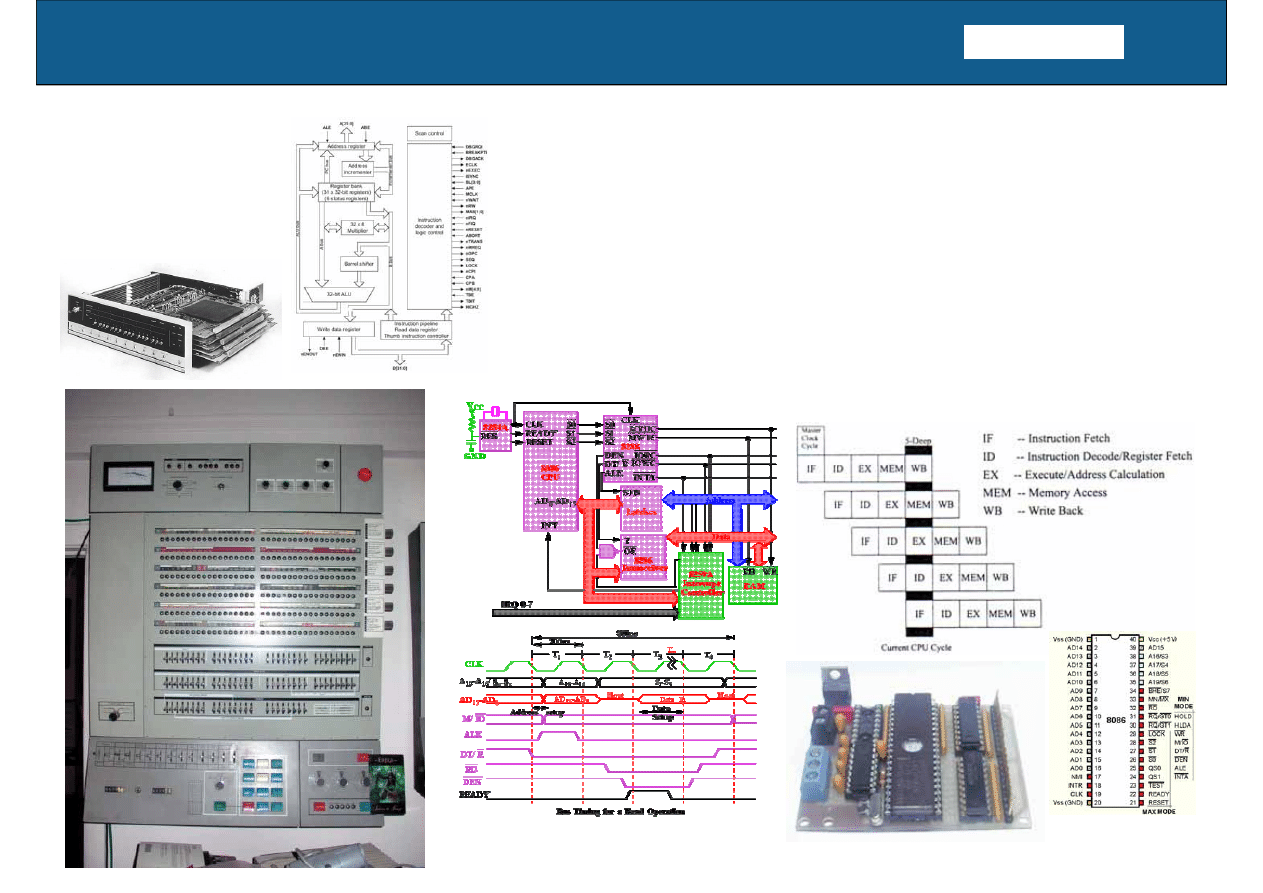

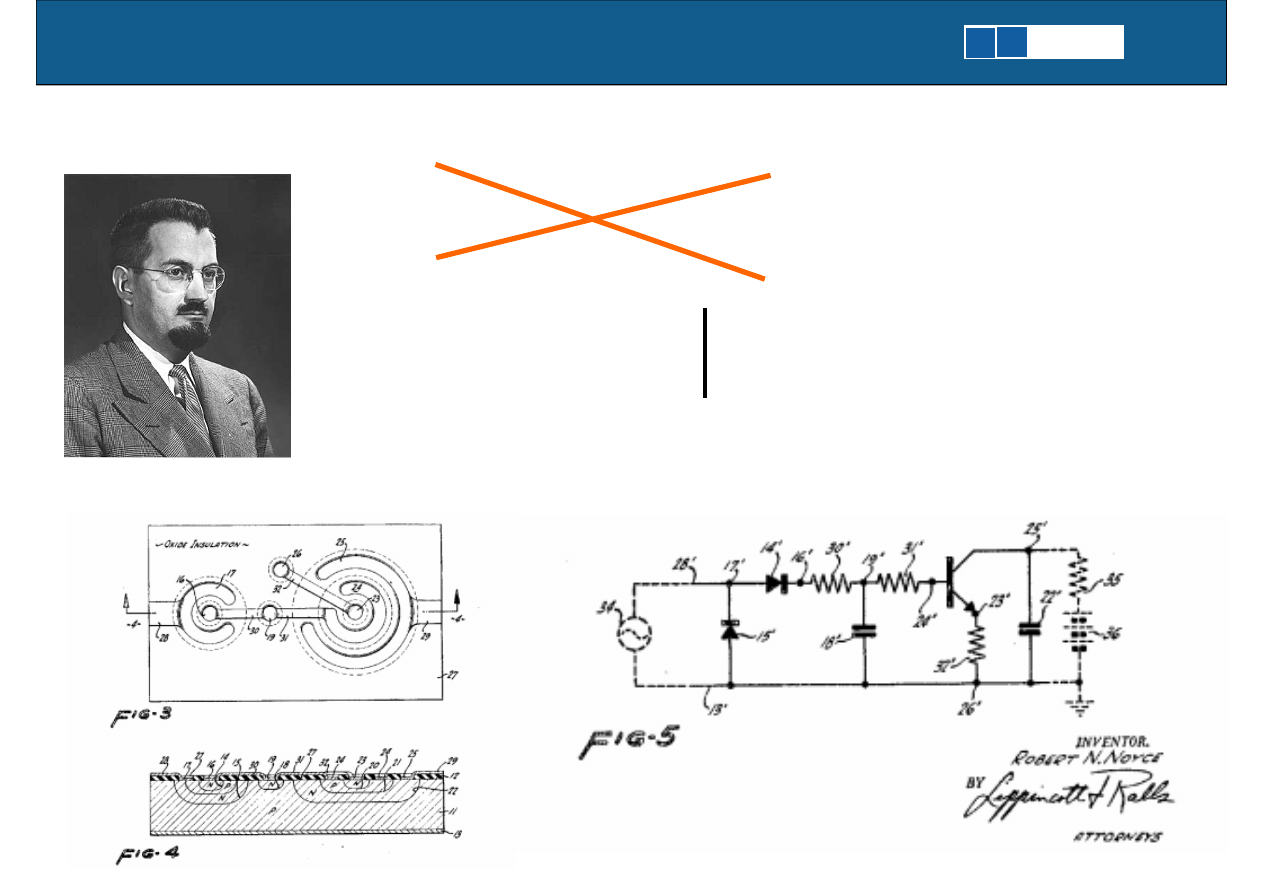

Chip, komputery generacja III

H. Grosch, 1955

Prawo Groscha – Zakup komputera większego i dwa razy

droższego skutkuje cztery razy większą mocą obliczeniową.

J. Kilby, Texas Instruments.

R. Noice, Fairchild Semiconductor.

Pierwszy patent na układ scalony

zawierający więcej niż jeden

element w środku

P.E. Ceruzzi, A History of Modern Computing, MIT Press 2003

2. CISC - 8086

9/30

1

2

3

4

5

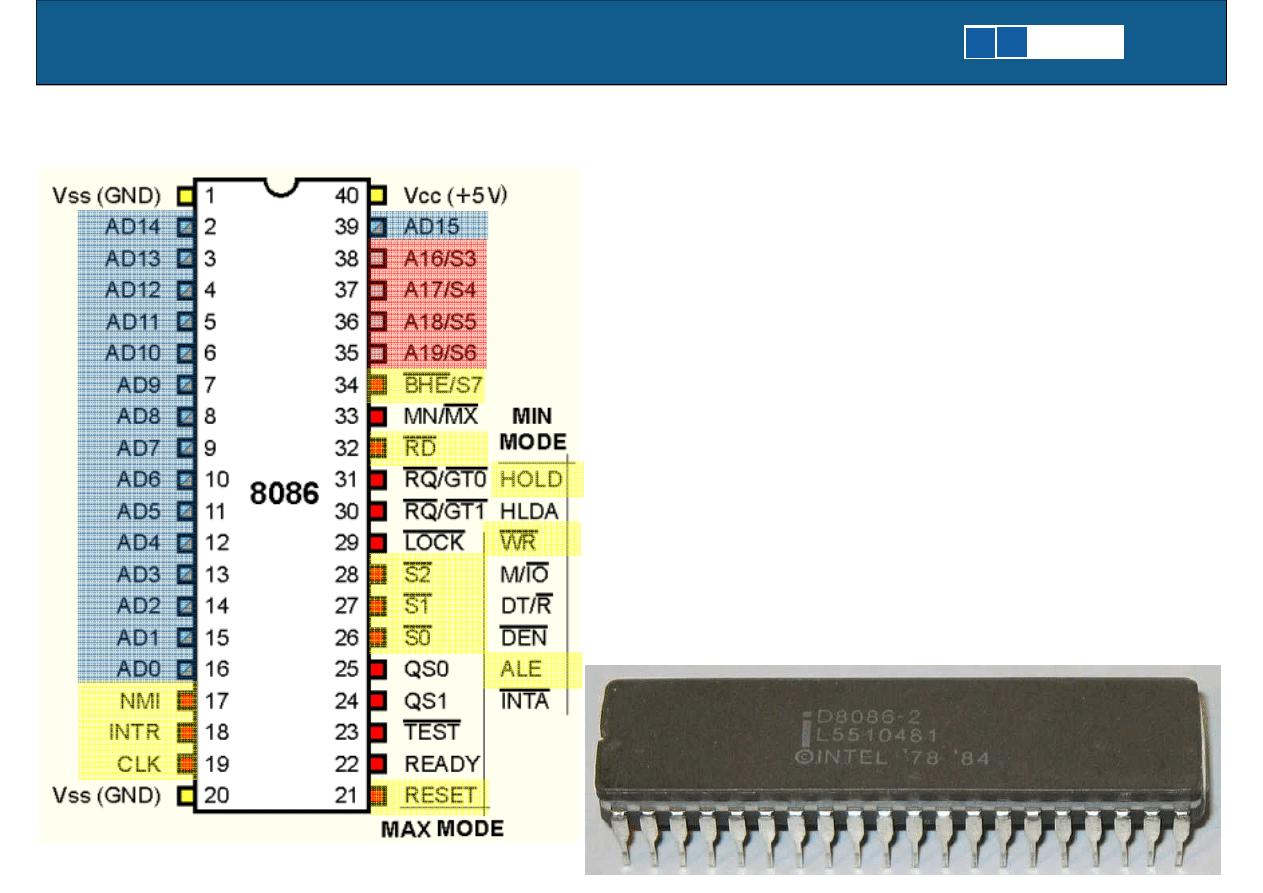

Architektura 8086 , 1978

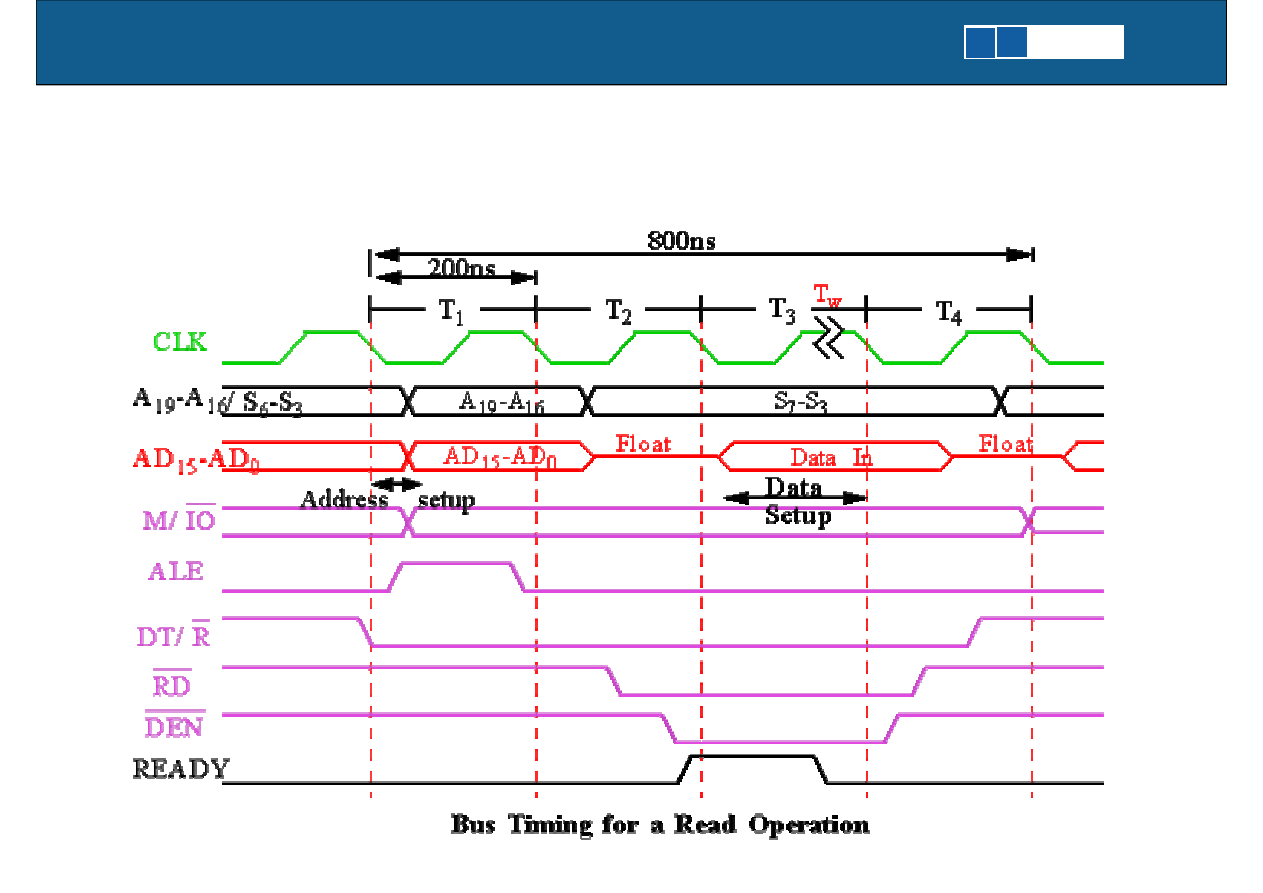

AD15-AD0 - Multipleksowane adres(ALE=1)/dane(ALE=0).

A19/S6-A16/S3 (multipleksowane) - Starsze 4 bity adresu lub

status S6-S3

S7 – S0 – sygnalizuje parametry działania procesora.

INTR, INTA - Przerwanie i potwierdzenie przerwania

WR, RD – Zapis/Odczyt dla szyny

ALE – gdy 1, szyna zawiera adres (nie daną).

DT/R (Data Transmit/Receive) – Szyna danych zawiera dane.

HOLD – prośba o DMA

2. CISC - 8086

10/30

1

2

3

4

5

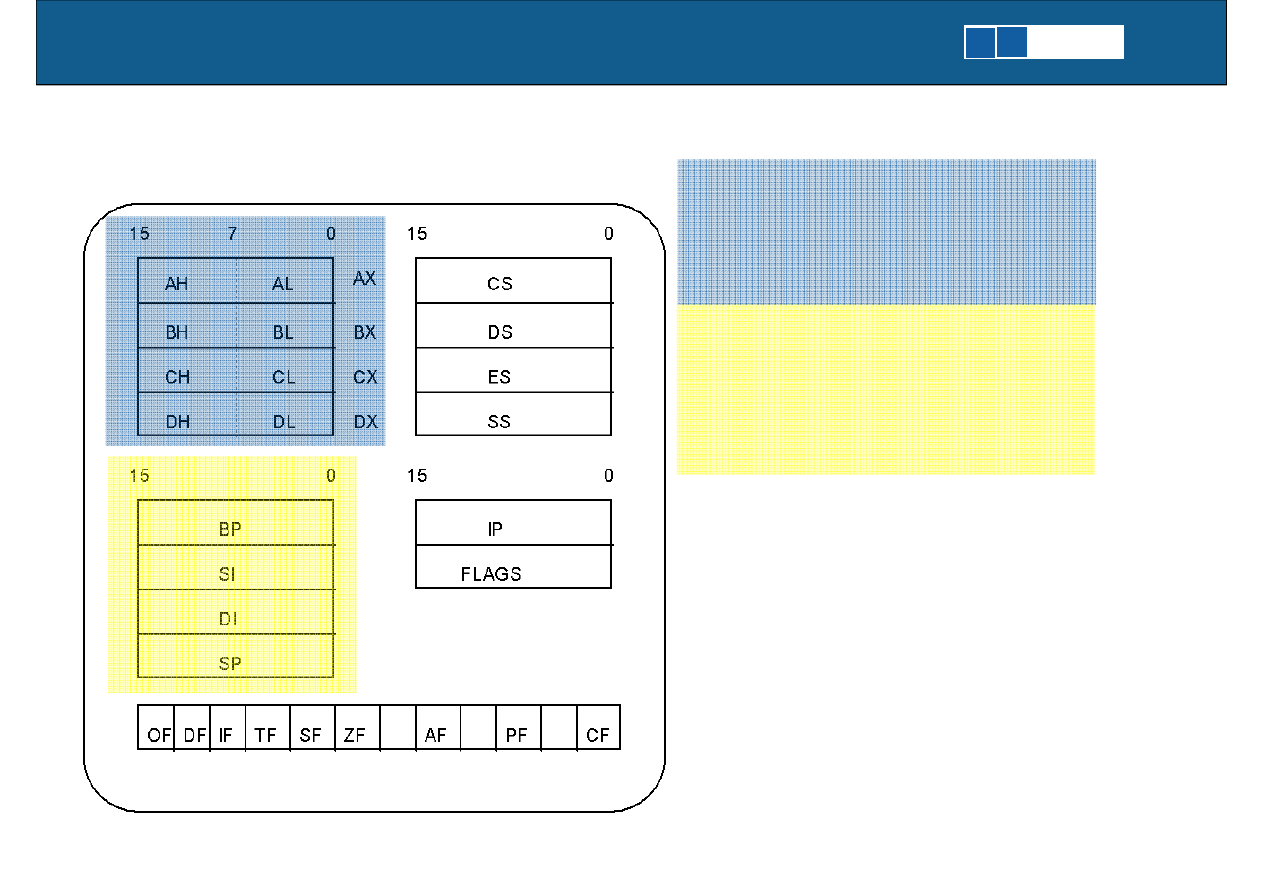

Rejestry 8086

AX – Accumulator Register

BX – Base Address Register

CX – Count Register

DX – Data Register

BP – Base Pointer

SP – Stack Pointer

SI – Source Index Register

DI – Destination Index Register

IP – Instruction Pointer

FLAGS:

OF – Overflow Flag

DF – Direction Flag

IF – Interrupt Enable Flag

TF – Trap Flag

SF – Sign Flag

ZF – Zero Flag

AF – Auxiliary Flag

PF – Parity Flag

CF – Carry Flag

2. CISC - 8086

11/30

1

2

3

4

5

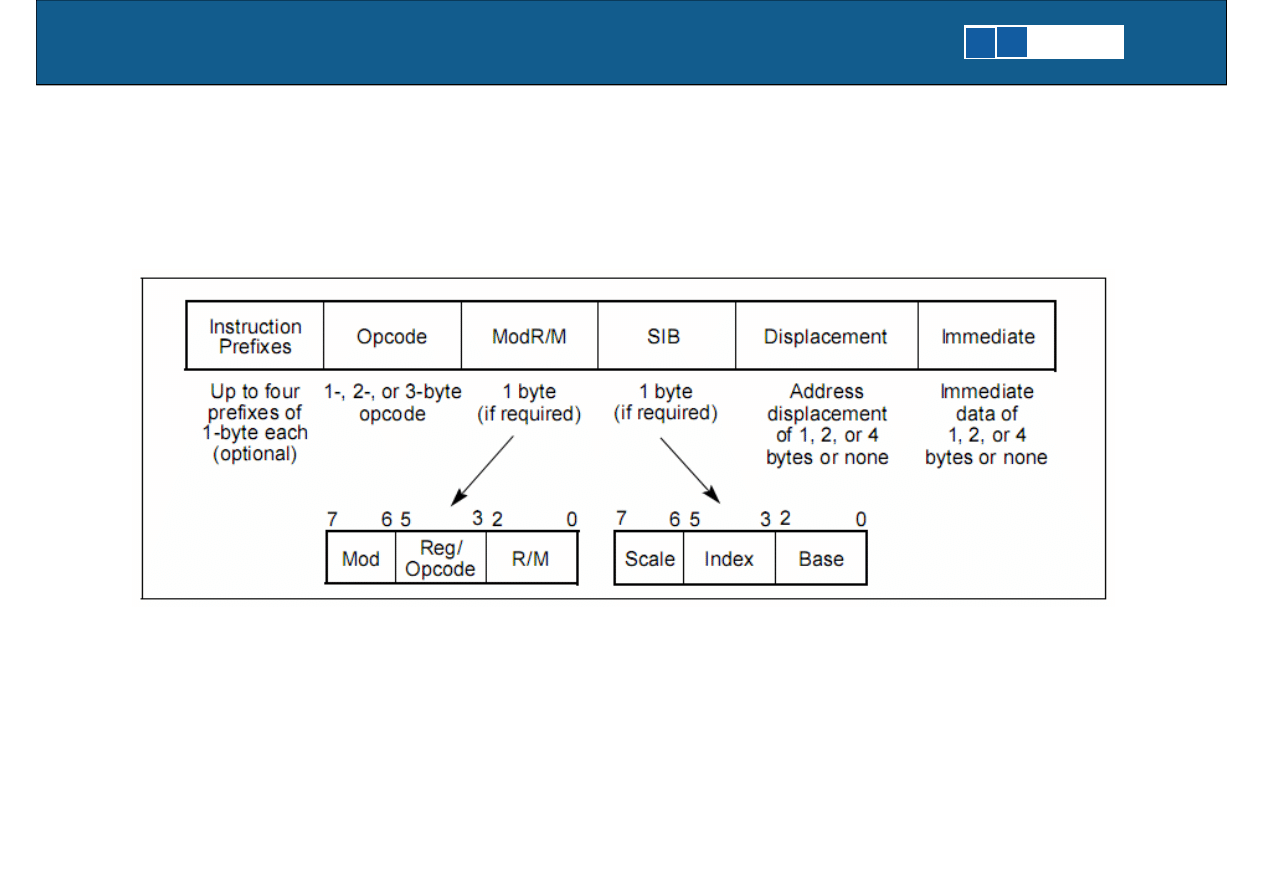

Format Instrukcji 8086

2. CISC - 8086

12/30

1

2

3

4

5

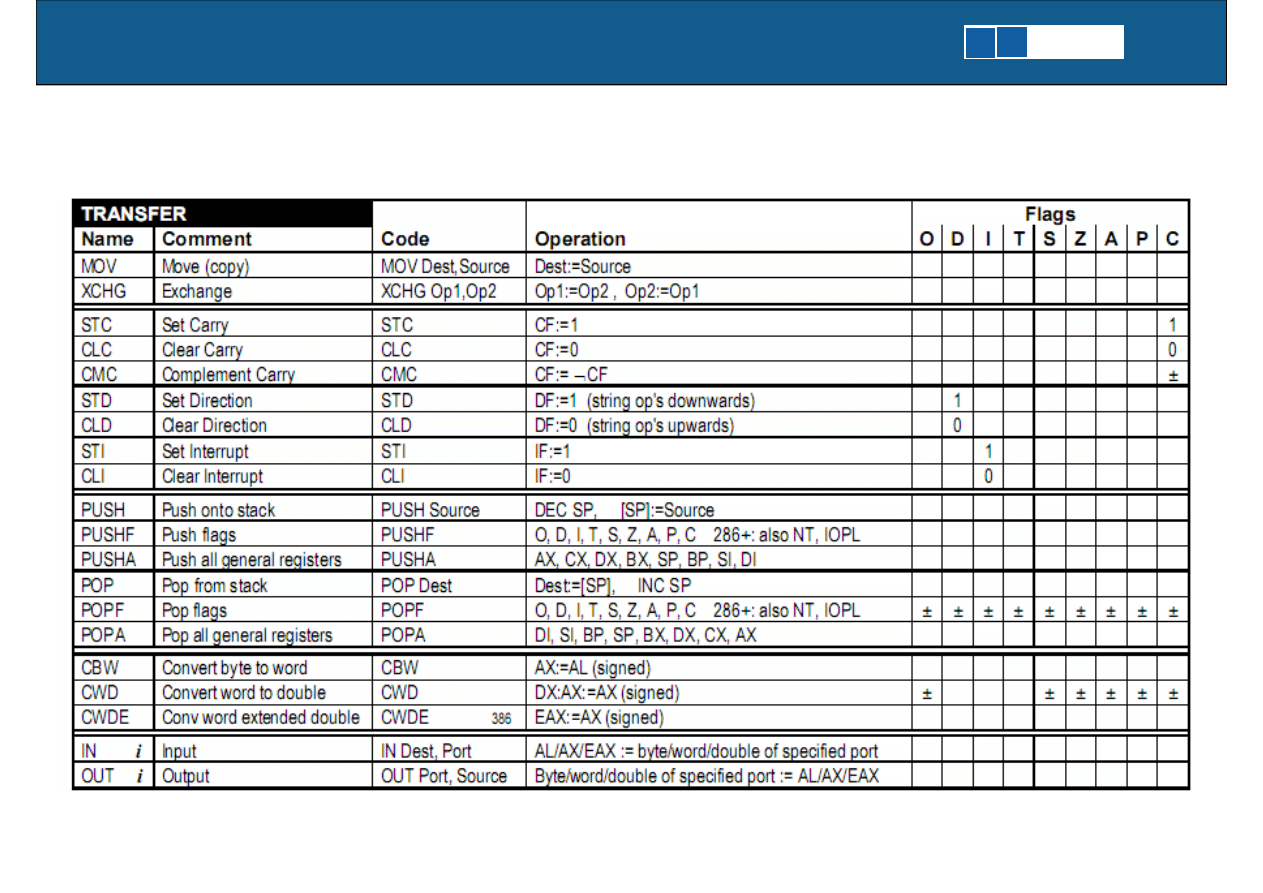

Lista instrukcji 8086 – instrukcje transferu

2. CISC - 8086

13/30

1

2

3

4

5

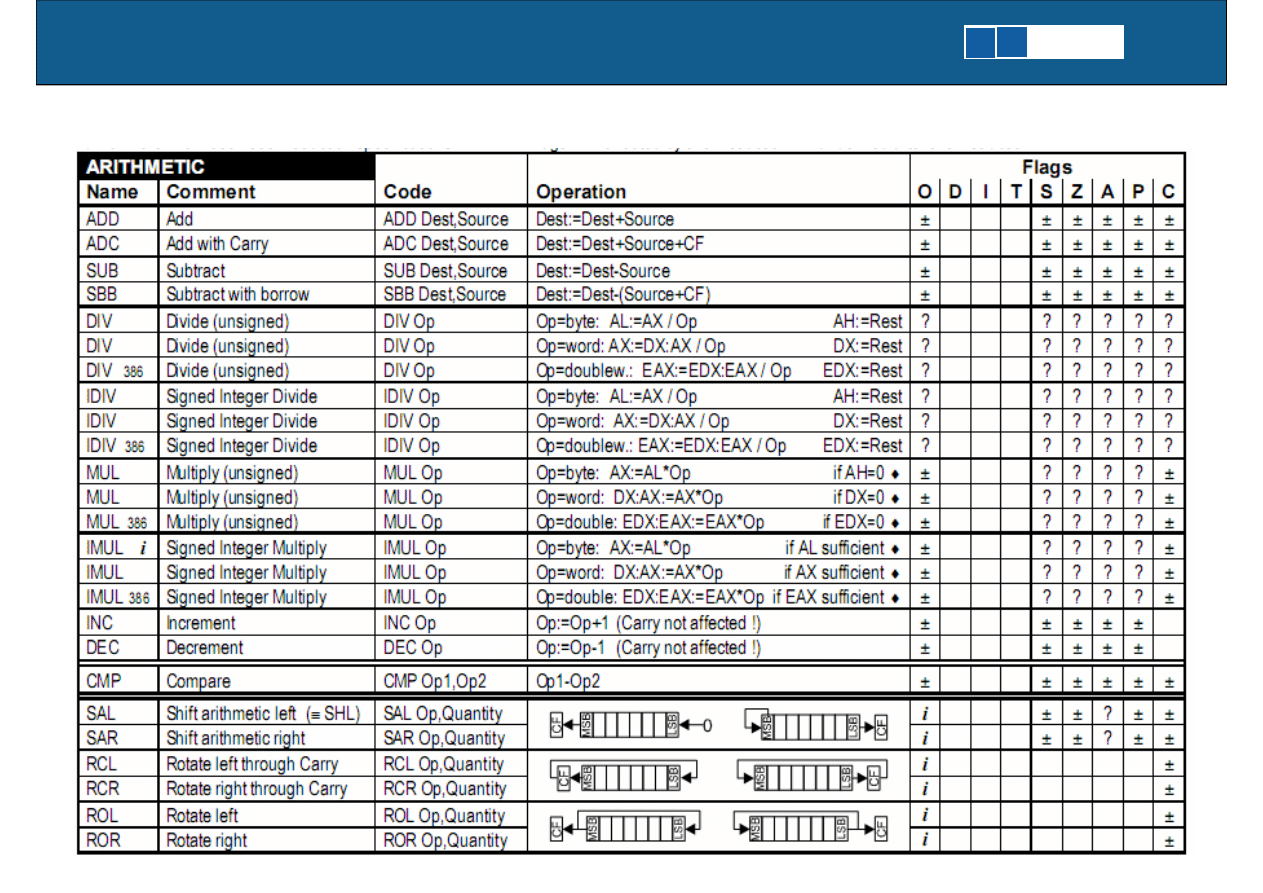

Lista instrukcji 8086 – instrukcje arytmetyczne

2. CISC - 8086

14/30

1

2

3

4

5

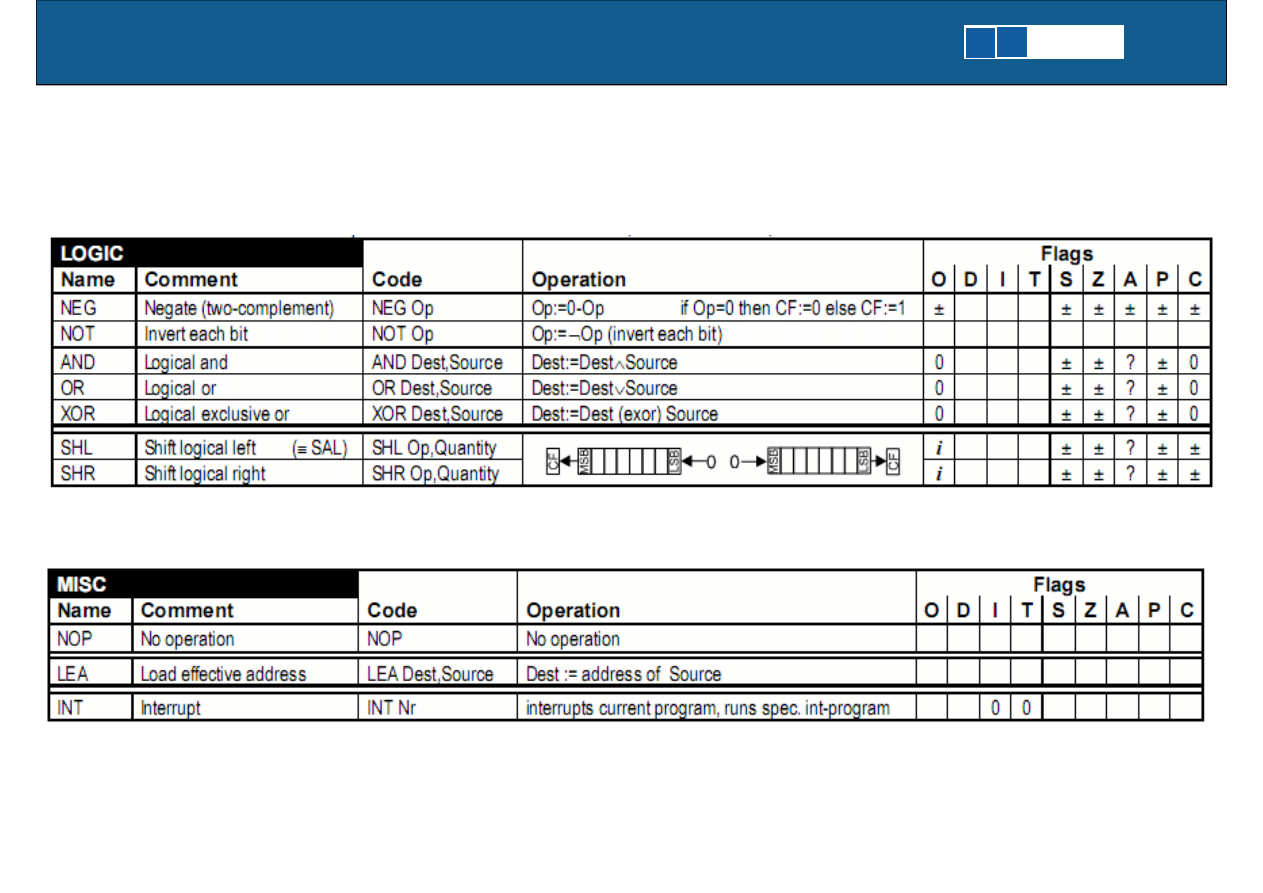

Lista instrukcji 8086 – instrukcje logiczne

2. CISC - 8086

15/30

1

2

3

4

5

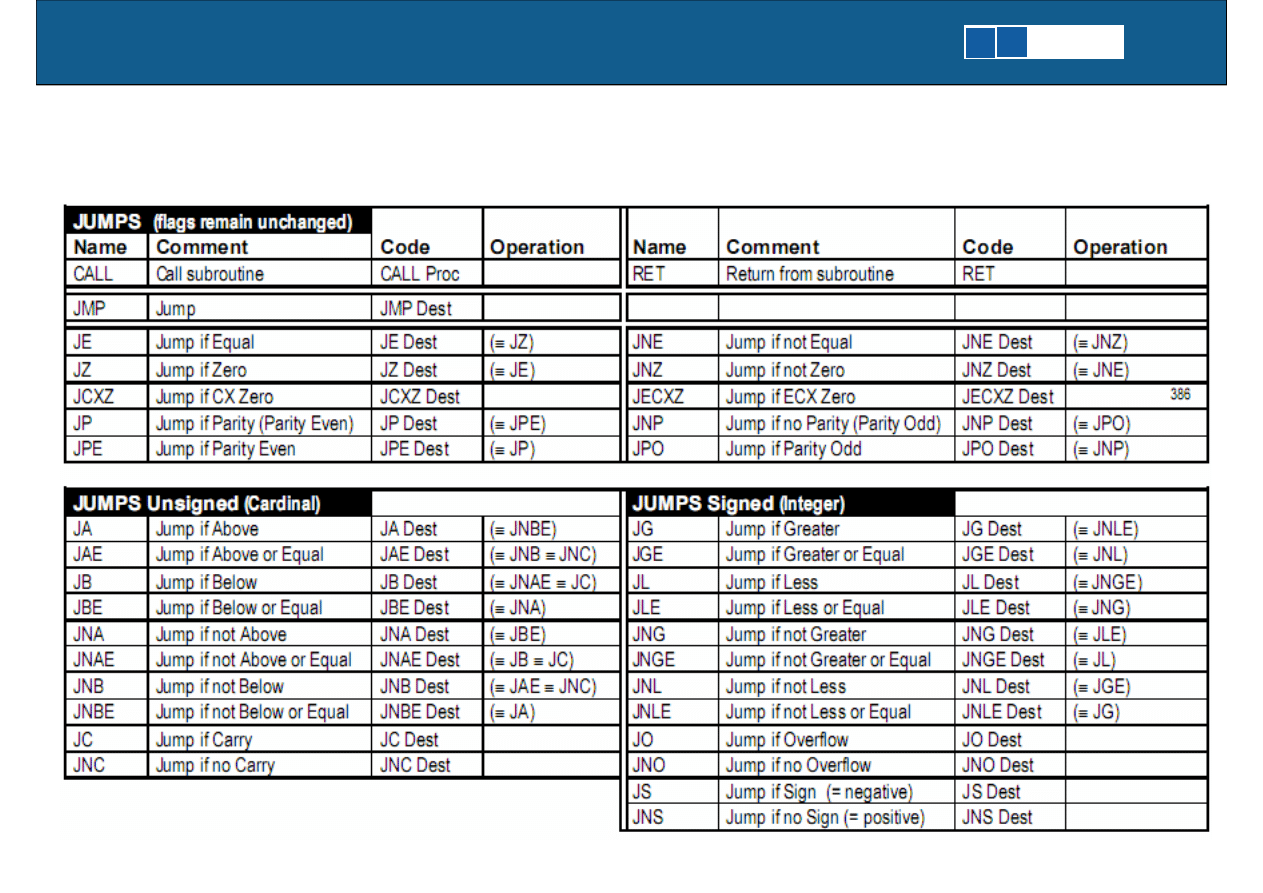

Lista instrukcji 8086 – instrukcje skoku

2. CISC - 8086

16/30

1

2

3

4

5

Lista instrukcji 8086 – tryby adresowania

Implied (implikowane) – argument związany jednoznacznie z nazwą instrukcji.

Register (rejestrowe) – argument dotyczy jednego z rejestrów procesora

Immediate (natychmiastowe) – wartość danej zawarta jest w kodzie instrukcji

Direct (bezpośrednie) – instrukcja zawiera adres do pamięci, pod którym znajduje się

wartość argumentu

Register indirect (pośrednie rejestrowe) – instrukcja zawiera adres rejestru, który

zawiera adres do pamięci, pod którym znajduje się wartość danej. Dotyczy to

rejestrów SI, DI, BX oraz BP.

Indexed (indeksowe) – instrukcja zawiera stałą, która dodawana jest do rejestru

bazowego (BX, BP) lub indeksowego (SI, DI), tworząc adres do pamięci, pod którym

znajduje się wartość danej.

Based Indexed (bazowe indeksowe) – zawartość rejestru bazowego (BX, BP) jest

dodawana do zawartości rejestru indeksowego (SI, DI), tworząc adres do pamieci, pod

którym znajduje się wartość danej.

Based Indexed with displacement (bazowe indeksowe z przemieszczeniem) – stała

jest dodawana do rejestru bazowego (BX, BP) oraz rejestru indeksowego (SI, DI),

tworząc adres do pamięci, pod którym znajduje się wartość danej.

RET

MOV AX, BX

JMP 0x0100

JMP AX, licznik

ADD [DI], AX

ADD [DI+8], AX

NOT [BX+DI]

NOT [BX+DI+8]

2. CISC - 8086

17/30

1

2

3

4

5

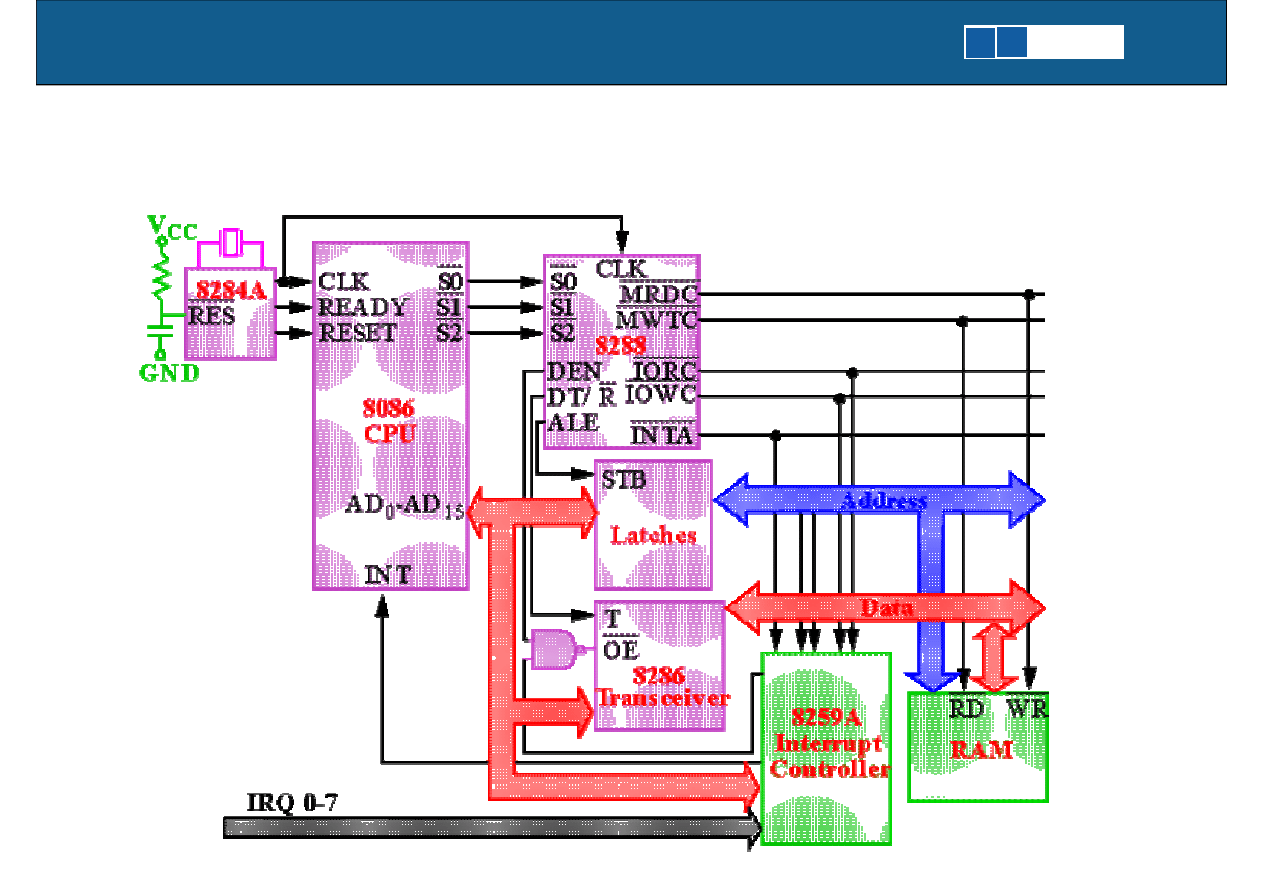

8086 – „płyta główna”

8284A – Generator zegara

8288 – Kontroler szyny

8286 – Transceiver szyny danych

8259 – Kontroler przerwań

2. CISC - 8086

18/30

1

2

3

4

5

8086 – sygnały na szynie

3. CISC - 8051

19/30

1

2

3

4

5

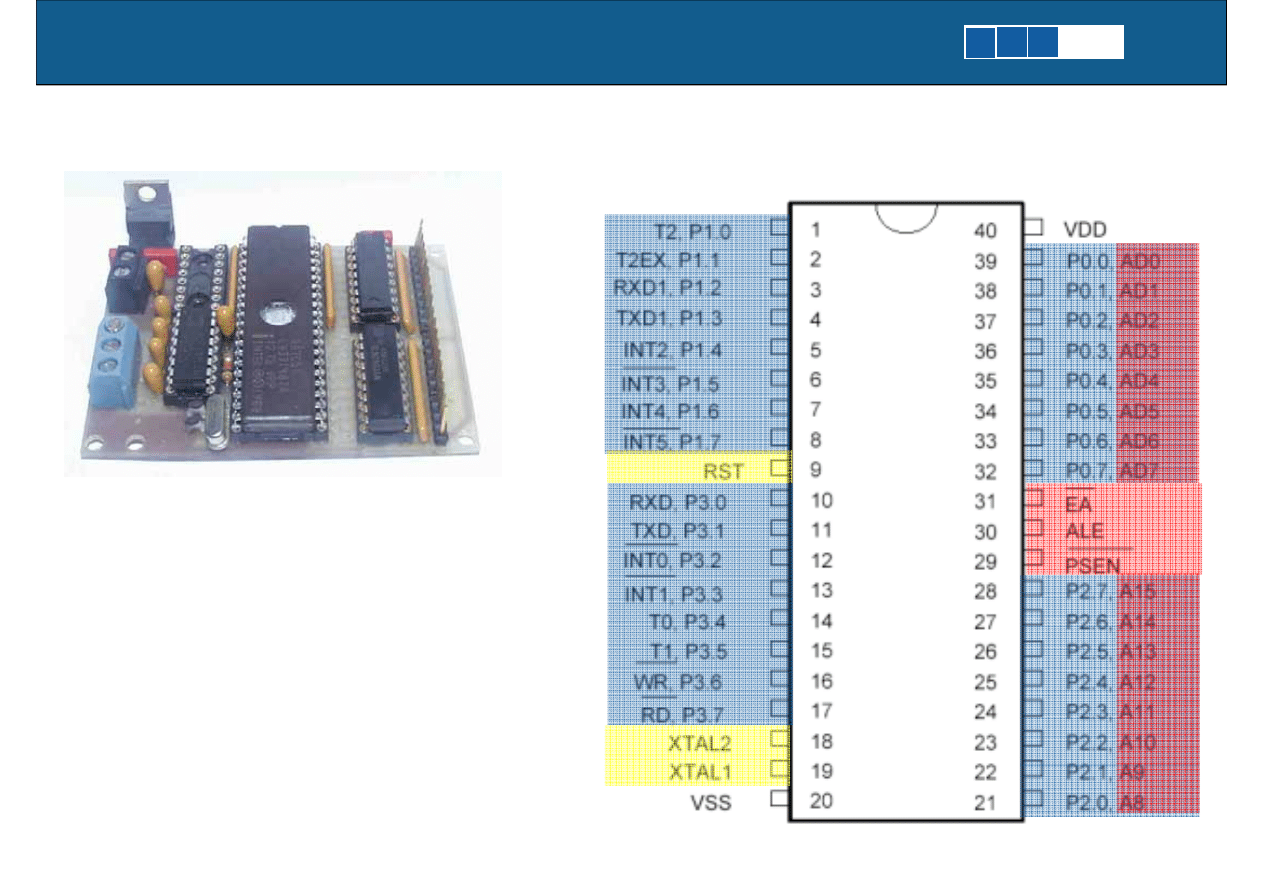

8051 – CISC dla systemów wbudowanych

110 różnych formatów instrukcji

7 rejestrów GPR w 4 bankach

R0 – R7

20/30

1

2

3

4

5

4. RISC

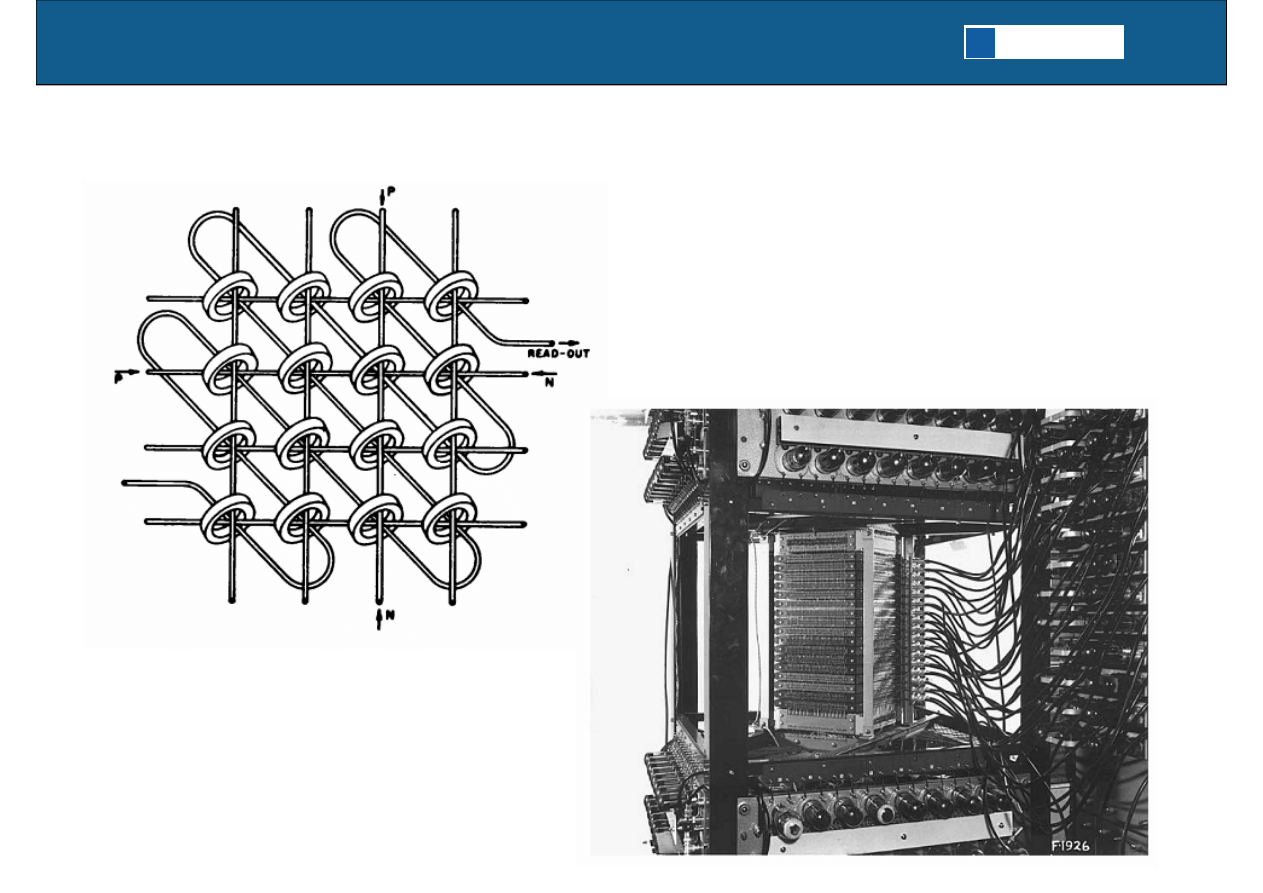

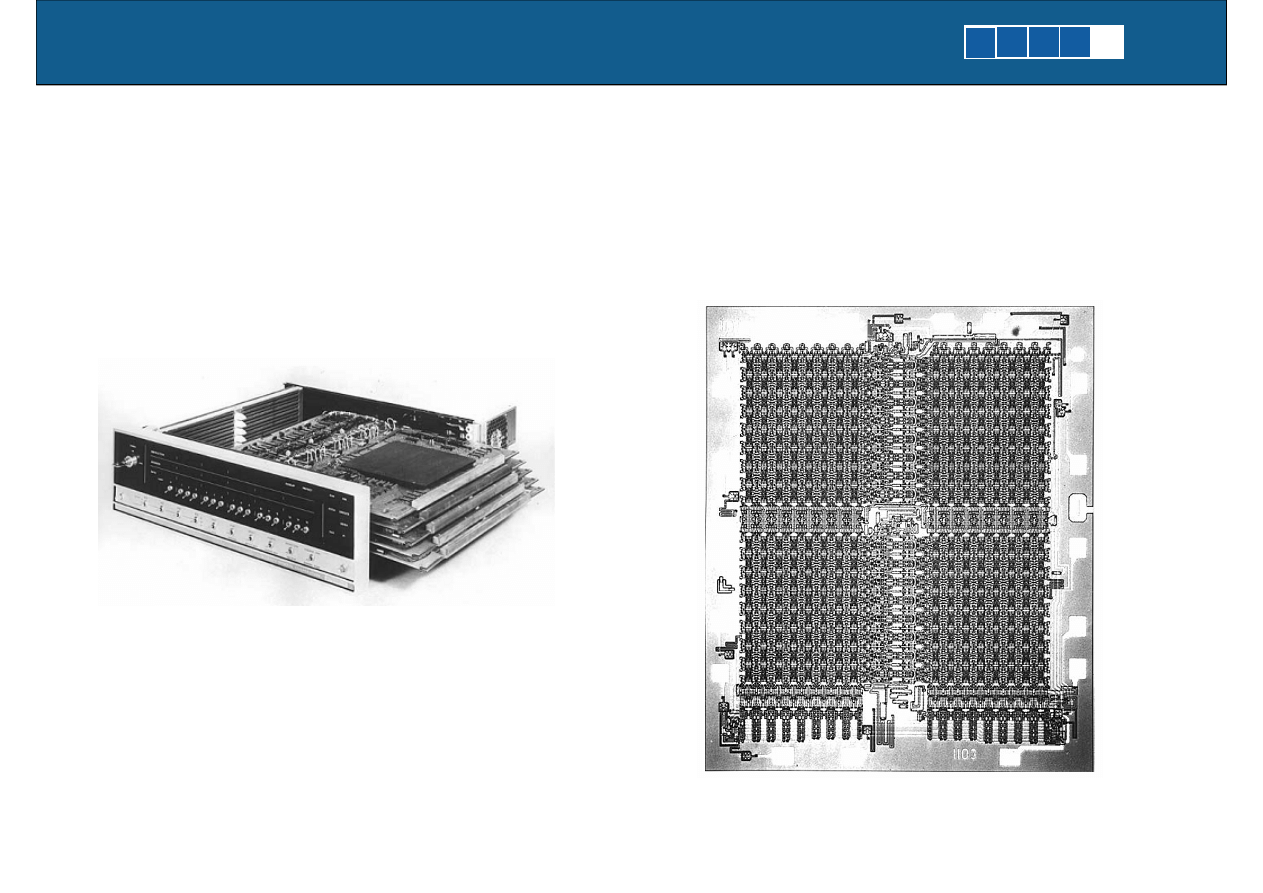

Przesłanki do powastania RISC – pamięć RAM

RAM – Random Access Memory

Super Nova, Data General (założone przez inżynierów/buntowników z DEC),

połowa 1971

Data General Super Nova, 256 bitów

1970, Intel 1103, RAM 1024 bit

P.E. Ceruzzi, A History of Modern Computing, MIT Press 2003

21/30

1

2

3

4

5

4. RISC

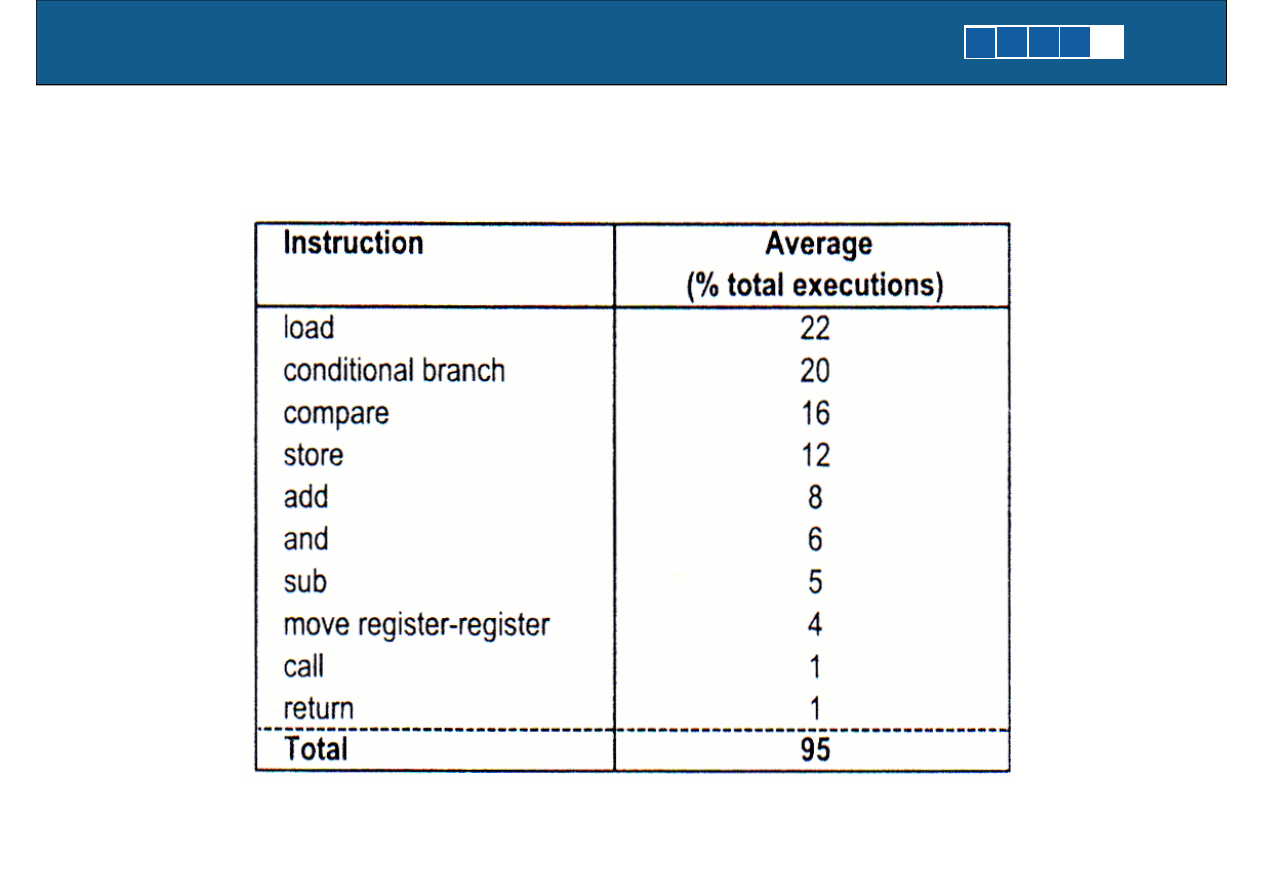

Przesłanki do powastania RISC – statystyki

wykorzystania instrukcji

Statystyki wykorzystania instrukcji dla procesorów o architekturze 8086

22/30

1

2

3

4

5

4. RISC

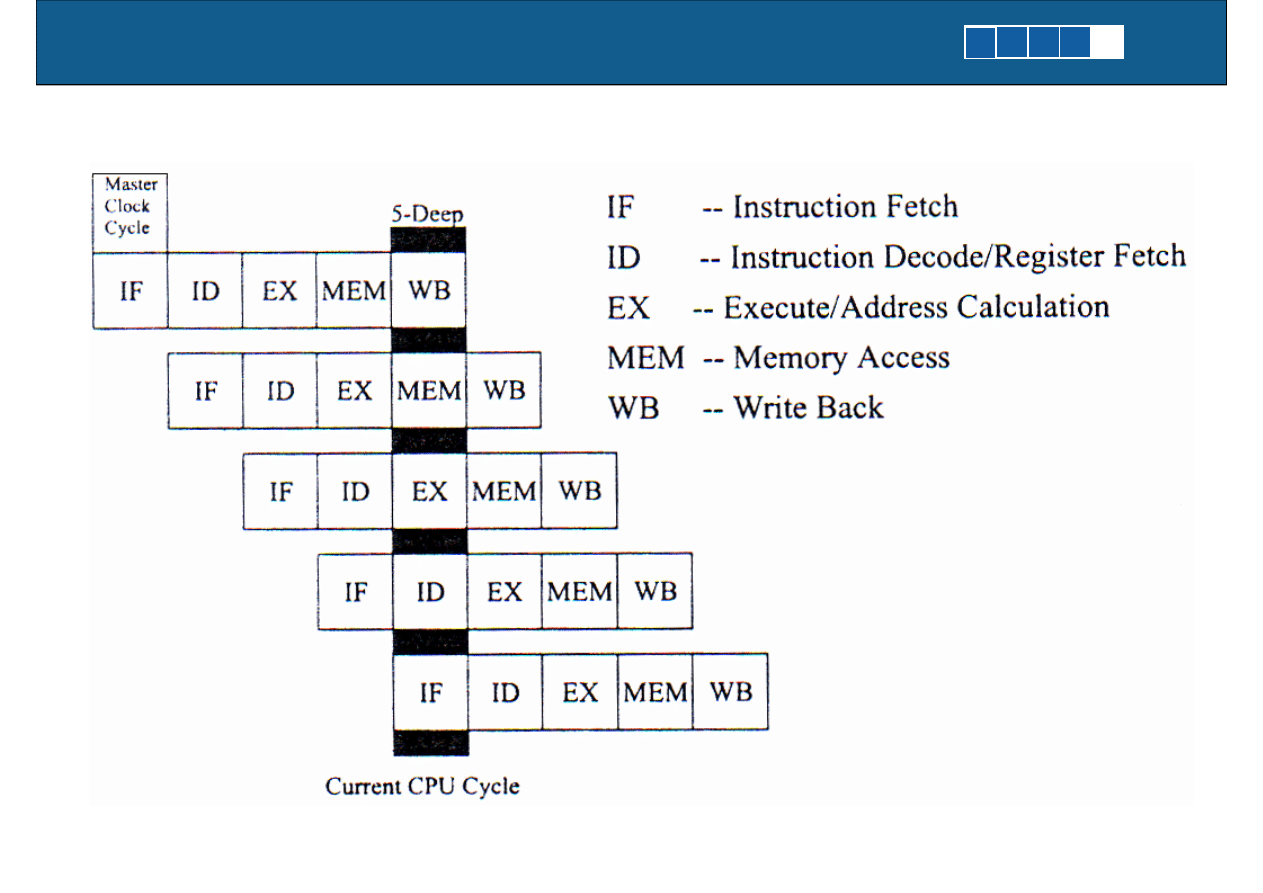

Przesłanki do powastania RISC - POTOK

23/30

1

2

3

4

5

4. RISC

Powstanie i krótka historia powszechnych

architektur RISC

1975 - IBM 801, 32 32-bit GPR

1980 – Berkeley RISC I/II, projekt badawczy: wielozadaniowość

1981 – Stanford MIPS, projekt badawczy: eliminacja konfliktów na rejestrach przez

kompilator, wiele jednostek funkcjonalnych

SPARC – otwarta architektura RISC

1986 – ARM, Advanced RISC Machine, projekt badawczy: nisko-mocowość, wysokie

częstotliwości

1991 – PowerPC, IBM/Motorola/Apple, projekt badawczy: równoległość wykonania

5. RISC – przegląd architektur

24/30

1

2

3

4

5

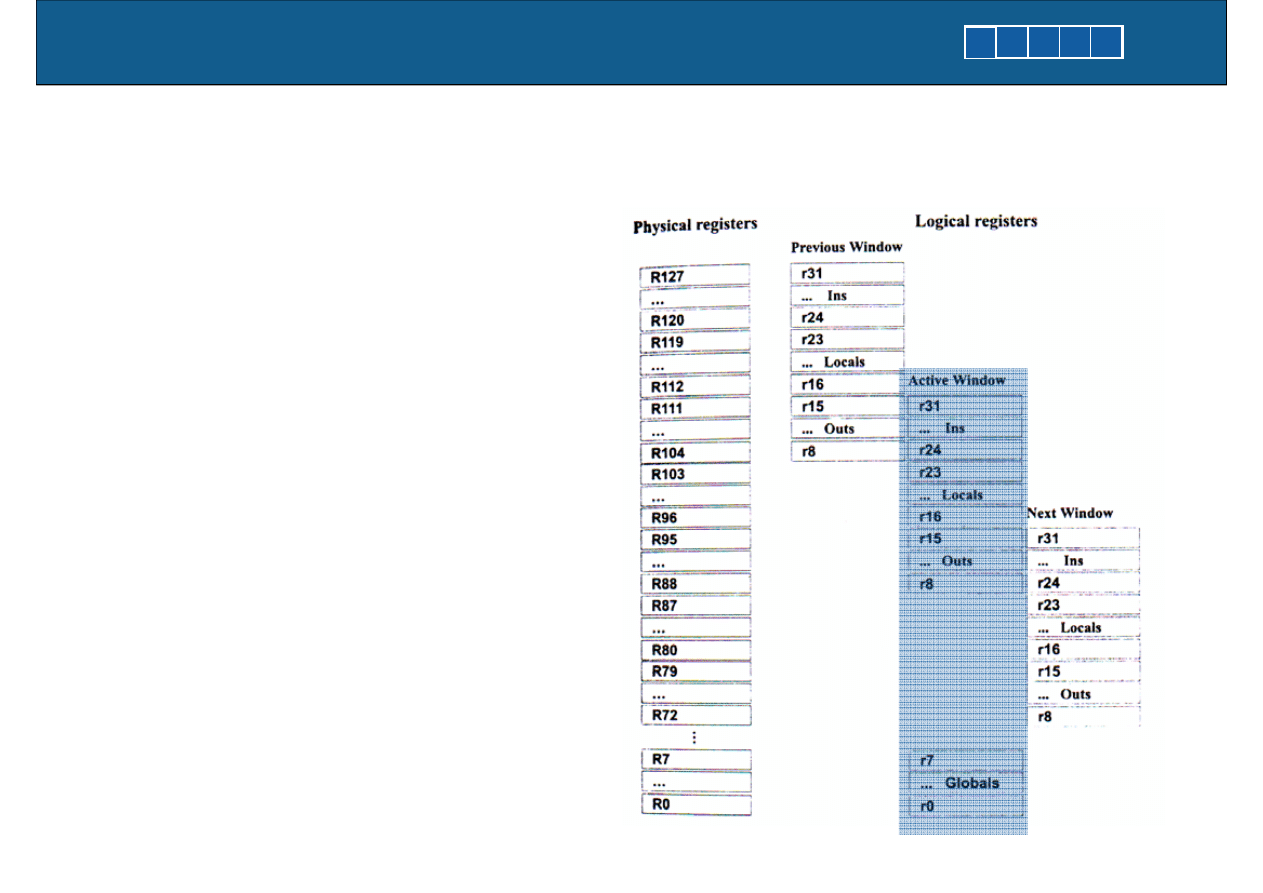

SPARC

Scalable Processor ARChitecture

Skoncentrowano się na efektywnej

metodzie przekazywania parametrów do

procedur. Zaproponowano koncepcje

okien rejestrów.

Przykładowe procesory:

Sun microSPARC-II

Sun superSPARC

Fujitsu turboSPARC

Fujitsu SPARClite

HAL Computer Sys. SPARC 64

5. RISC – przegląd architektur

25/30

1

2

3

4

5

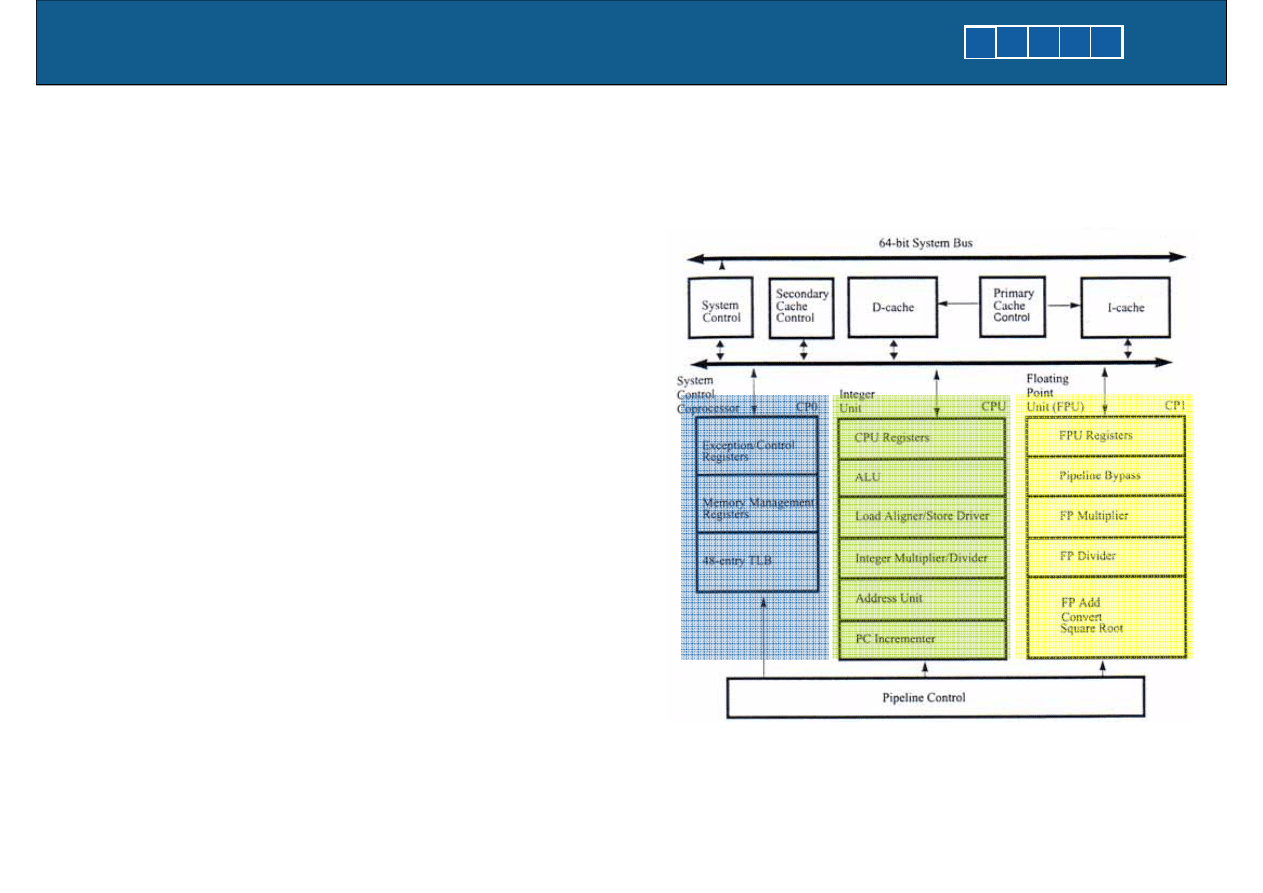

MIPS

Microprocessor without Interlocking Pipeline Stages

Potok wykorzystywany do aktywowania

na raz więcej niż jednej operacji. Ciężar

zapewnienia poprawności wykonania

spoczywa na kompilatorze.

MIPS I (1984, R2000, R3000)

MIPS II (1990, R6000)

MIPS III (1991, R4000, R4400)

MIPS IV (1994, R5000, R7000, R8000, R10000)

MIPS V ( 1996, R12000)

Architektura MIPS R4400

J. Silc, B. Robic, T Ungerer, Processor Architecture, Springer Verlag 1999

5. RISC – przegląd architektur

26/30

1

2

3

4

5

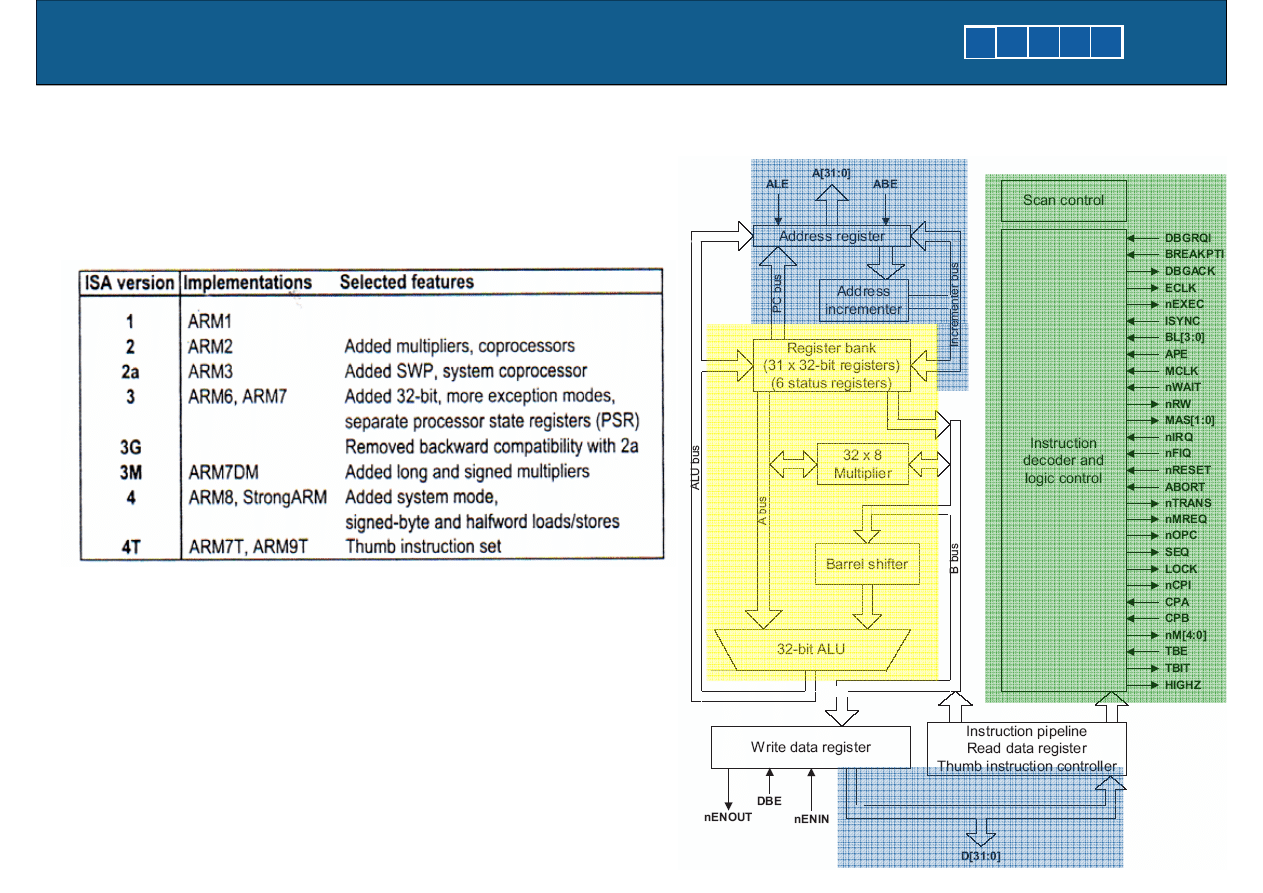

ARM

Advanced RISC Machine

Niskomocowa architektura, pracująca z

dużymi częstotliwościami.

www.arm.com

5. RISC – przegląd architektur

27/30

1

2

3

4

5

PowerPC

Performance Optimization With Enhanced RISC PC

1990 – IBM POWER ISA

Architektura przewidująca jasny podział względem funkcji.

Wyraźnie oddzielone funkcje kontroli wykonania programu,

ogliczeń stałoprzecinkowych, obliczeń zmiennoprzecinkowych

itp. . Każdy z takich bloków mógł pracować równolegle.

1991 – IBM/Motorola/Apple

PowerPC ISA

Rozszerzona, 64-bitowe wersja architektury POWER.

5. RISC – przegląd architektur

28/30

1

2

3

4

5

RISC - podsumowanie

¾ Proste instrukcje i możliwie niewiele trybów adresowania

¾ Większość isntrukcji operuje tylko na rejestrach. Do odwołania do pamięci

instrukcje load/store

¾ Dość głęboki potok w układzie sterującym

¾ Mikroprogram praktycznie nie stosowany

¾ Duża część zadań pozostawiona kompilatorowi do zaplanowania

¾ Rozbudowana hierarchia pamięci

RISC/CISC

29/30

Polecana literatura

1) J. Silc, B. Robic, T Ungerer, Processor Architecture From Dataflow to Superscalar and

Beyond, Springer Verlag 1999

Rozdział 1. Basic Pipelining and Simple RISC Processors

strony 1 - 53

2) W. Stallings, Organizacja i architektura systemu komputerowego, WNT 2003

Rozdział 12. str 497-543

53 strony

46 stron

3) P.E. Ceruzzi, A History of Modern Computing, MIT Press 2003

Rozdział 1-7

strony 1 - 242

242 strony

RISC/CISC

30/30

KONIEC

dr inż. Mariusz Kapruziak

mkapruziak@wi.ps.pl

pok. 107, tel. 449 55 44

Wyszukiwarka

Podobne podstrony:

ASK 05 PiotrGębala MateuszMacięga

ASK 05 Apache

ASK 05 Apache

podrecznik 2 18 03 05

regul praw stan wyjątk 05

05 Badanie diagnostyczneid 5649 ppt

Podstawy zarządzania wykład rozdział 05

05 Odwzorowanie podstawowych obiektów rysunkowych

05 Instrukcje warunkoweid 5533 ppt

05 K5Z7

05 GEOLOGIA jezior iatr morza

05 IG 4id 5703 ppt

05 xml domid 5979 ppt

Świecie 14 05 2005

Wykł 05 Ruch drgający

więcej podobnych podstron