PC

Memory

Address

Instruction

or data

Data

Instruction

register

Registers

Register #

Data

Register #

Register #

ALU

Memory

data

register

A

B

ALUOut

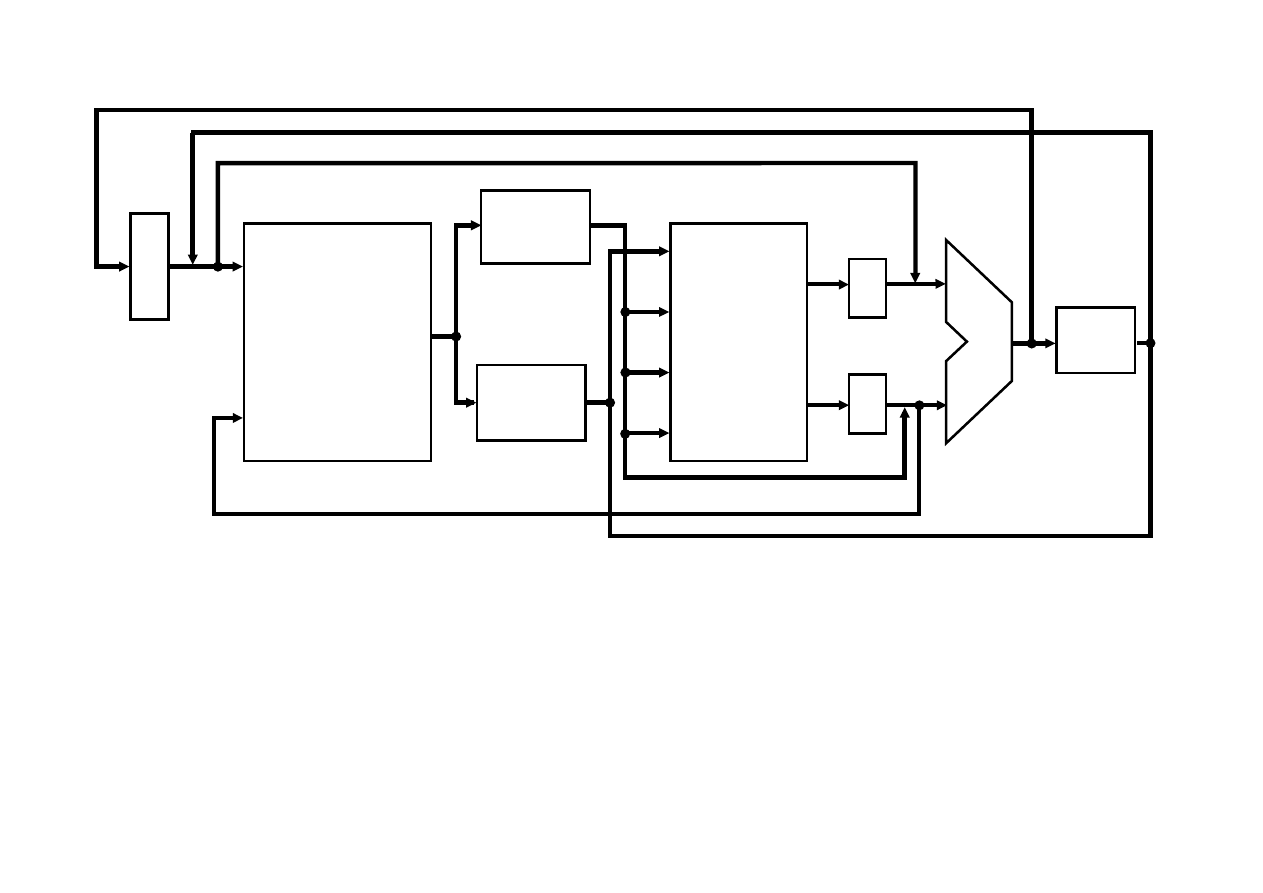

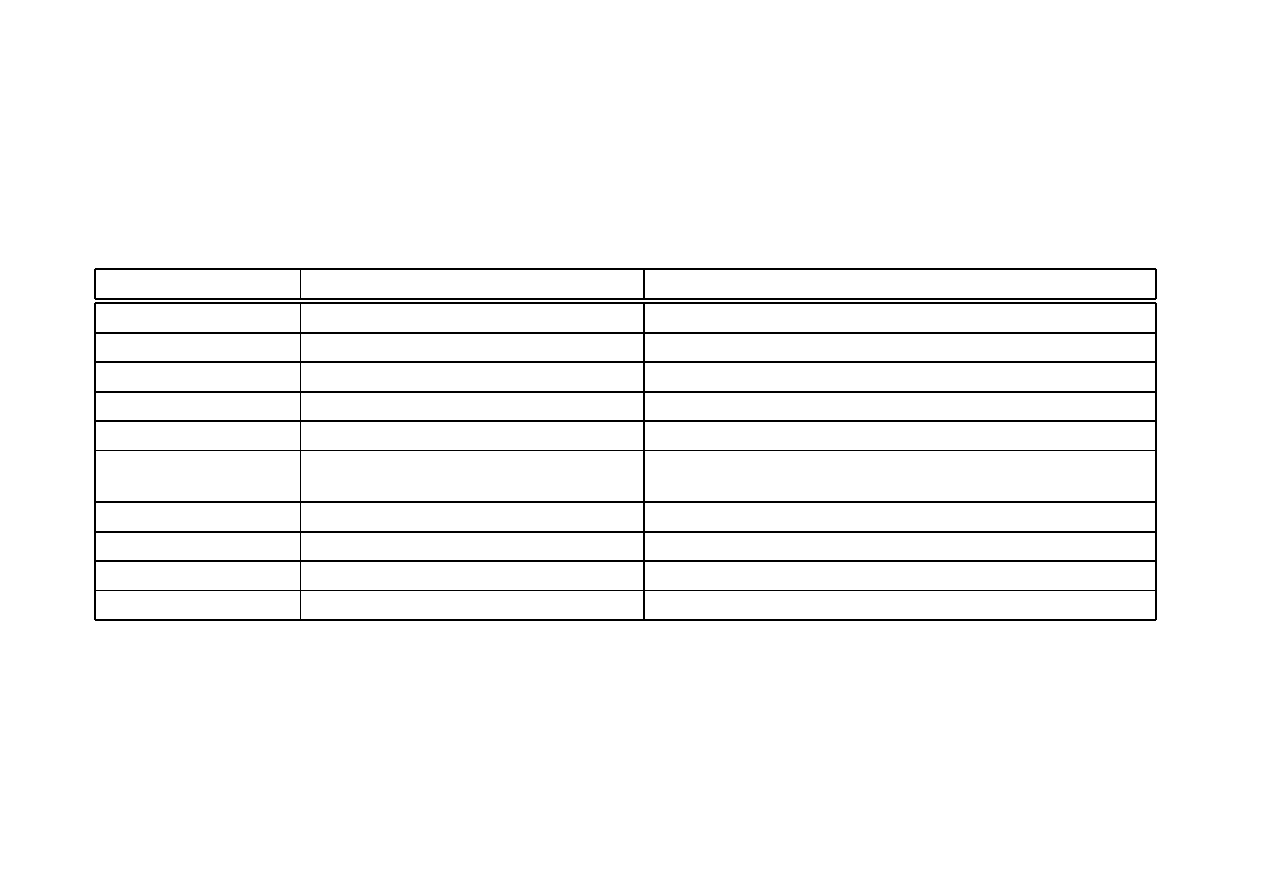

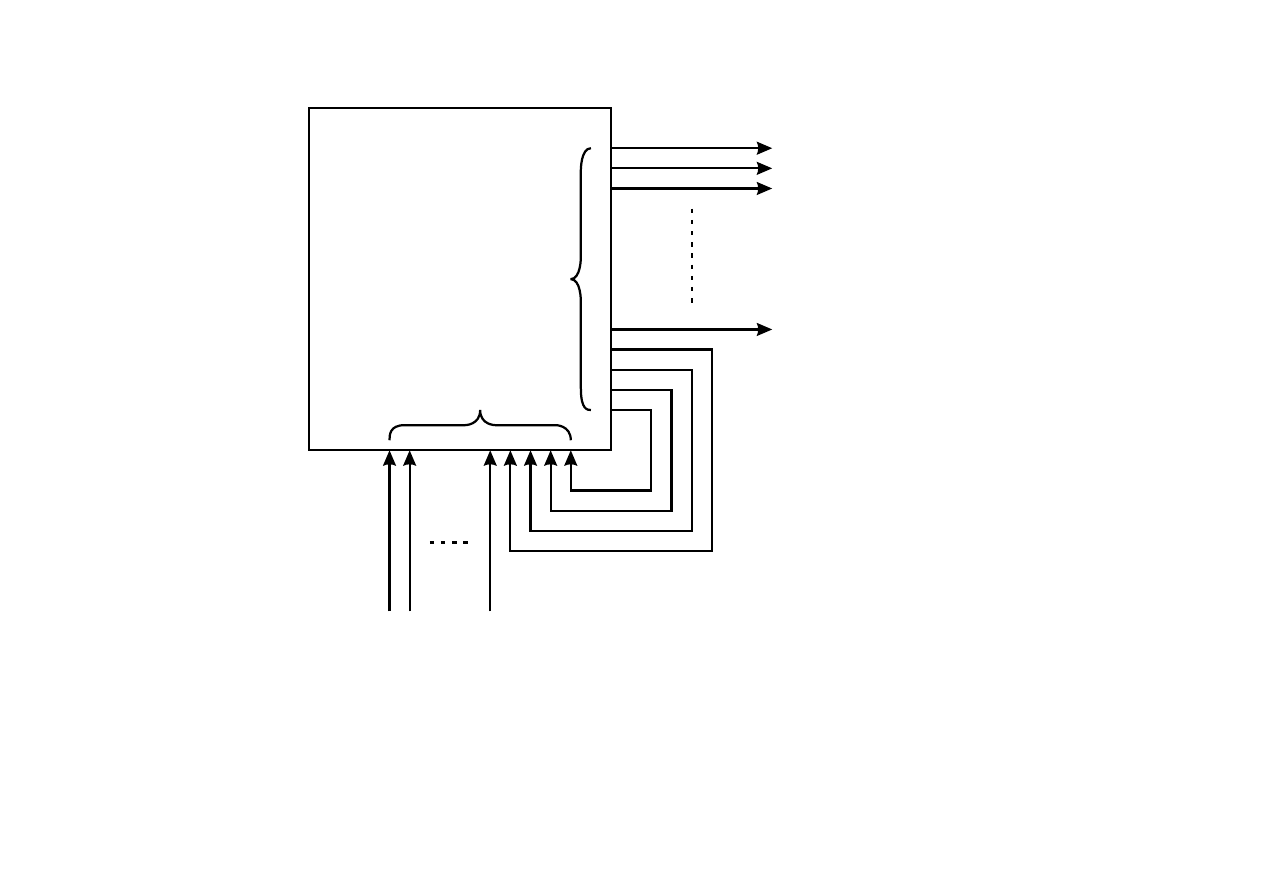

Elementy architektury typu multi–cycle

Architektura Multi-cycle

• każda instrukcja wykonuje się w kilku cyklach zegara

• instrukcje wymagają różnej liczby cykli zegara

• dane wykorzystywane przez jedną instrukcję, umieszczane są w rejestrach pośred-

nich i wykorzystywane w następnych cyklach zegara tej samej instrukcji

• dane będące końcowym wynikiem instrukcji, umieszczane są w pliku rejestrów,

pamięci zewnętrznej lub w PC

• redukcja dużych bloków architektury i dodanie rejestrów pośrednich

Bloki architektury:

• jednolita pamięć (instrukcje programu + dane)

• blok pliku rejestrów

• jeden element wykonawczy — ALU

• dodatkowe rejestry pośrednie, na wyjściu każdego bloku

Rejestry pośrednie (niewidoczne dla programisty):

IR — instruction register — przechowuje kod instrukcji w czasie jej wykonywania

MDR — memory data register — przechowuje dane odczytane z pamięci

A,B — rejestry przechowujące odczytane wartości z pliku rejestrów mikroprocesora

ALUOut — rejestr przechowujący wynik działania ALU

Shift

left 2

PC

Memory

MemData

Write

data

M

u

x

0

1

Registers

Write

register

Write

data

Read

data 1

Read

data 2

Read

register 1

Read

register 2

M

u

x

0

1

M

u

x

0

1

4

Instruction

[15-0]

Sign

extend

32

16

Instruction

[25-21]

Instruction

[20-16]

Instruction

[15-0]

Instruction

register

1 M

u

x

0

3

2

M

u

x

ALU

result

ALU

Zero

Memory

data

register

Instruction

[15-11]

A

B

ALUOut

0

1

Address

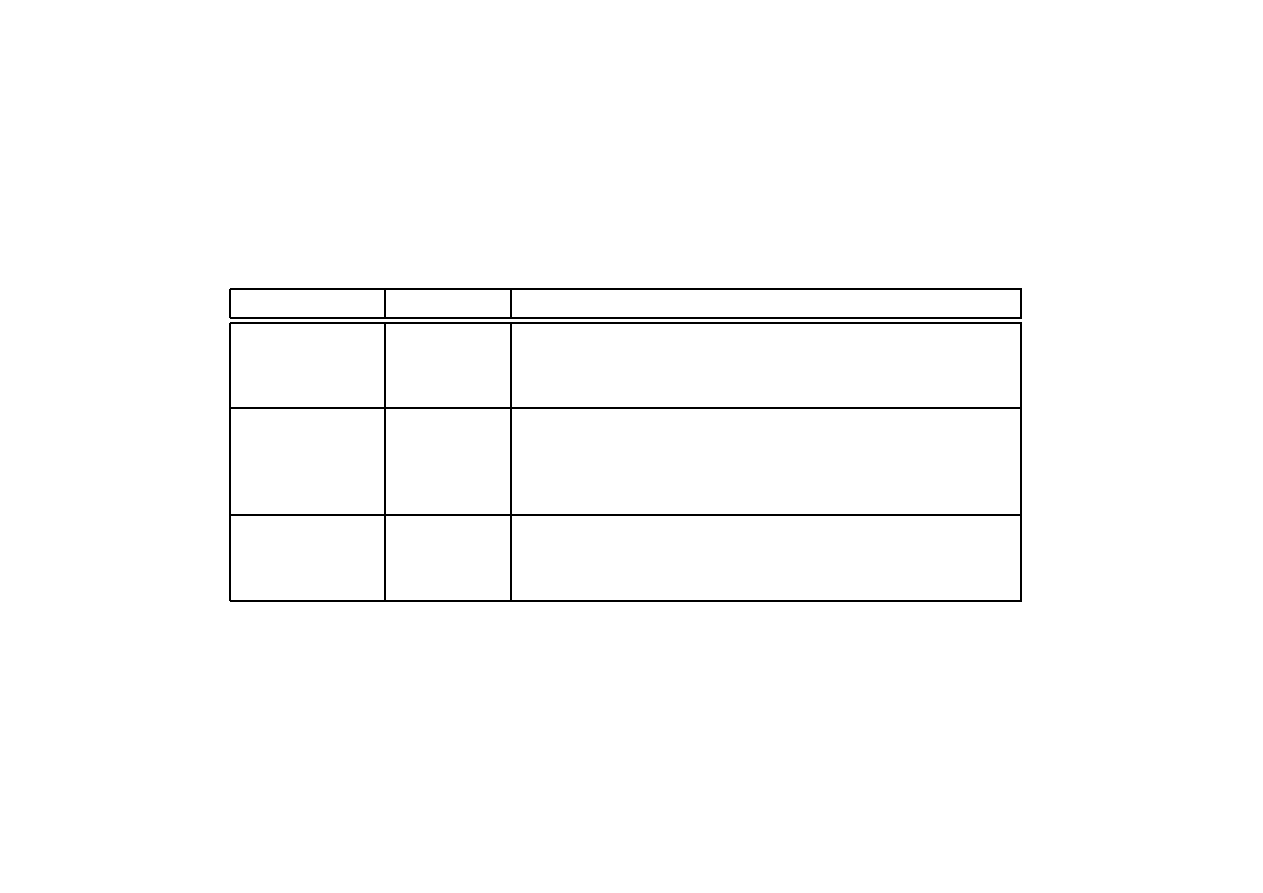

Dodatkowe multiplexery przed ALU są konieczne do realizacji wszystkich typów

instrukcji oraz inkrementacji PC za pomocą tylko jednej jednostki wykonawczej

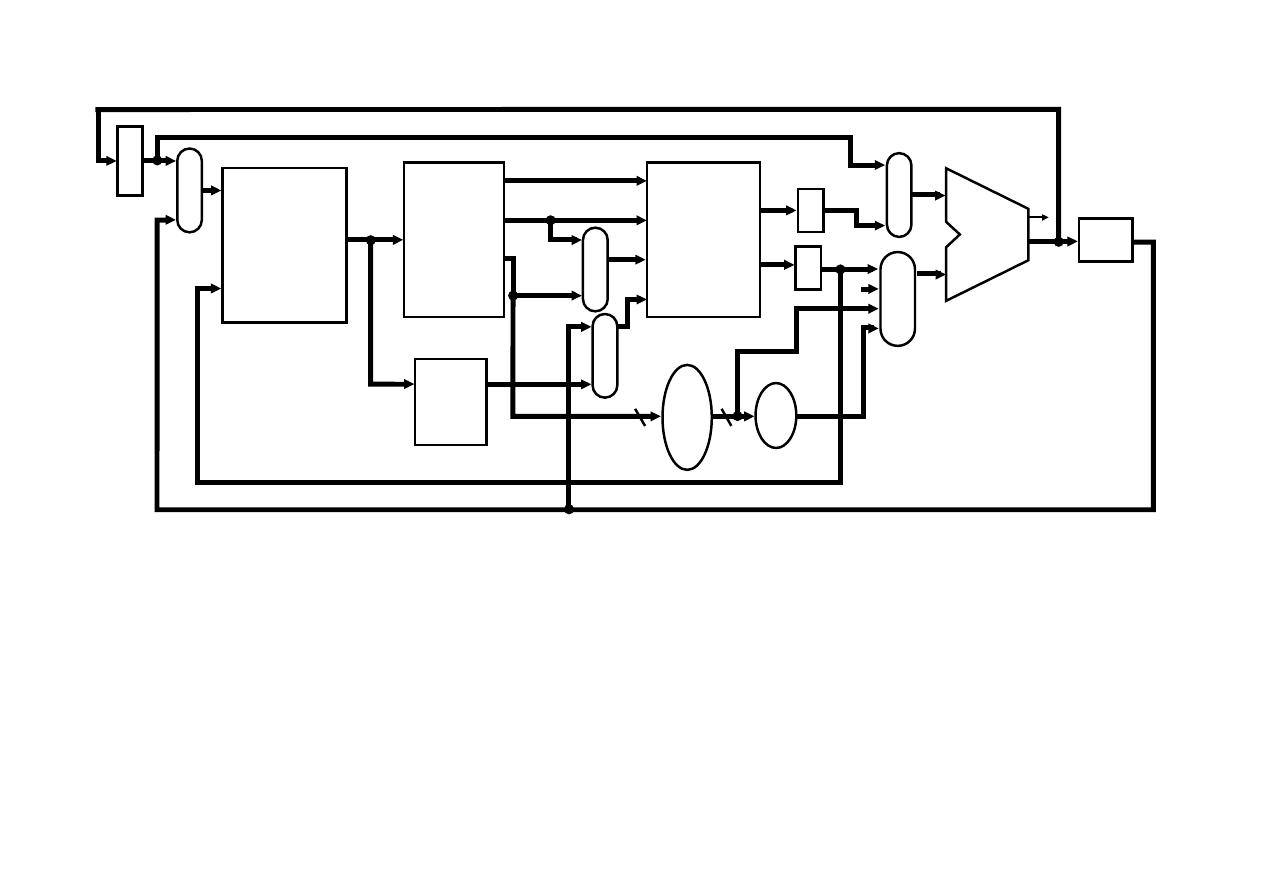

Ścieżki danych architektury multi–cycle

Shift

left 2

MemtoReg

IorD

MemRead

MemWrite

PC

Memory

MemData

Write

data

M

u

x

0

1

Registers

Write

register

Write

data

Read

data 1

Read

data 2

Read

register 1

Read

register 2

Instruction

[15-11]

M

u

x

0

1

M

u

x

0

1

4

ALUOp

ALUSrcB

RegDst

RegWrite

Instruction

[15-0]

Instruction [5-0]

Sign

extend

32

16

Instruction

[25-21]

Instruction

[20-16]

Instruction

[15-0]

Instruction

register

1 M

u

x

0

3

2

ALU

control

M

u

x

0

1

ALU

result

ALU

ALUSrcA

Zero

A

B

ALUOut

IRWrite

Address

Memory

data

register

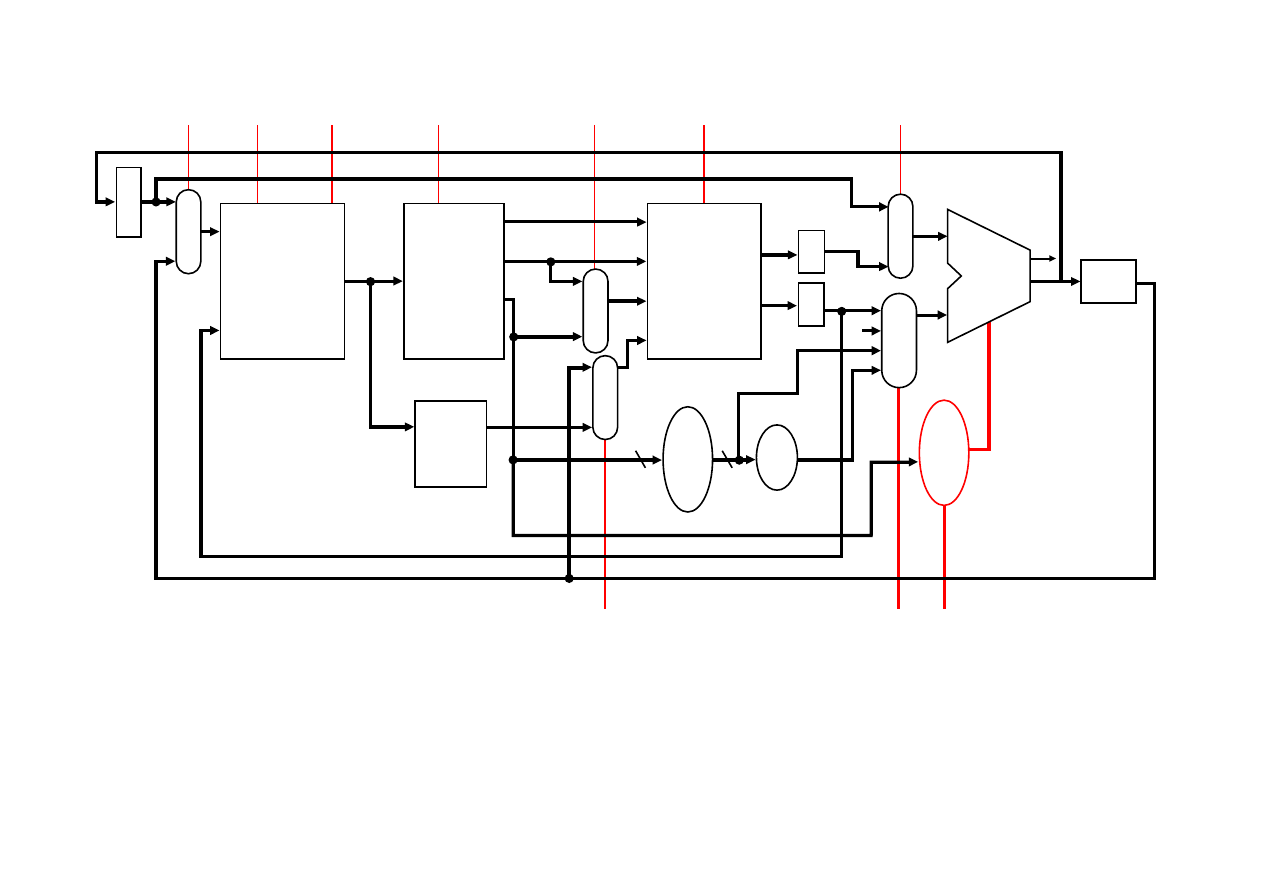

Sygnały sterujące architektury multi–cycle

Shift

left 2

PC

M

u

x

0

1

Registers

Write

register

Write

data

Read

data 1

Read

data 2

Read

register 1

Read

register 2

Instruction

[15-11]

M

u

x

0

1

M

u

x

0

1

4

Instruction

[15-0]

Sign

extend

32

16

Instruction

[25-21]

Instruction

[20-16]

Instruction

[15-0]

Instruction

register

ALU

control

ALU

result

ALU

Zero

Memory

data

register

A

B

IorD

MemRead

MemWrite

MemtoReg

PCWriteCond

PCWrite

IRWrite

ALUOp

ALUSrcB

ALUSrcA

RegDst

PCSource

RegWrite

Control

Outputs

Op

[5-0]

Instruction

[31-26]

Instruction [5-0]

M

u

x

0

2

Jump

address [31-0]

Instruction [25-0]

26

28

Shift

left 2

PC [31-28]

1

1 M

u

x

0

3

2

M

u

x

0

1

ALUOut

Memory

MemData

Write

data

Address

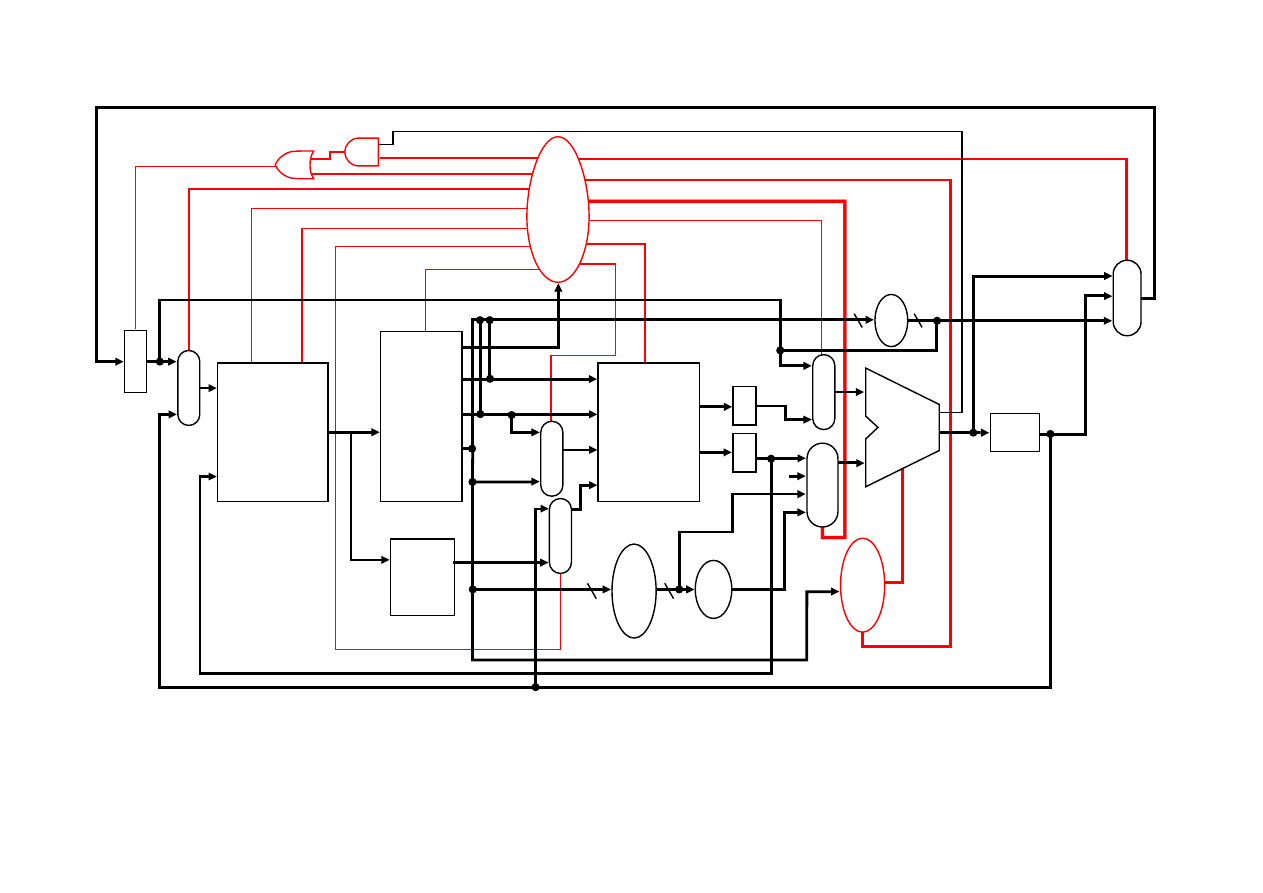

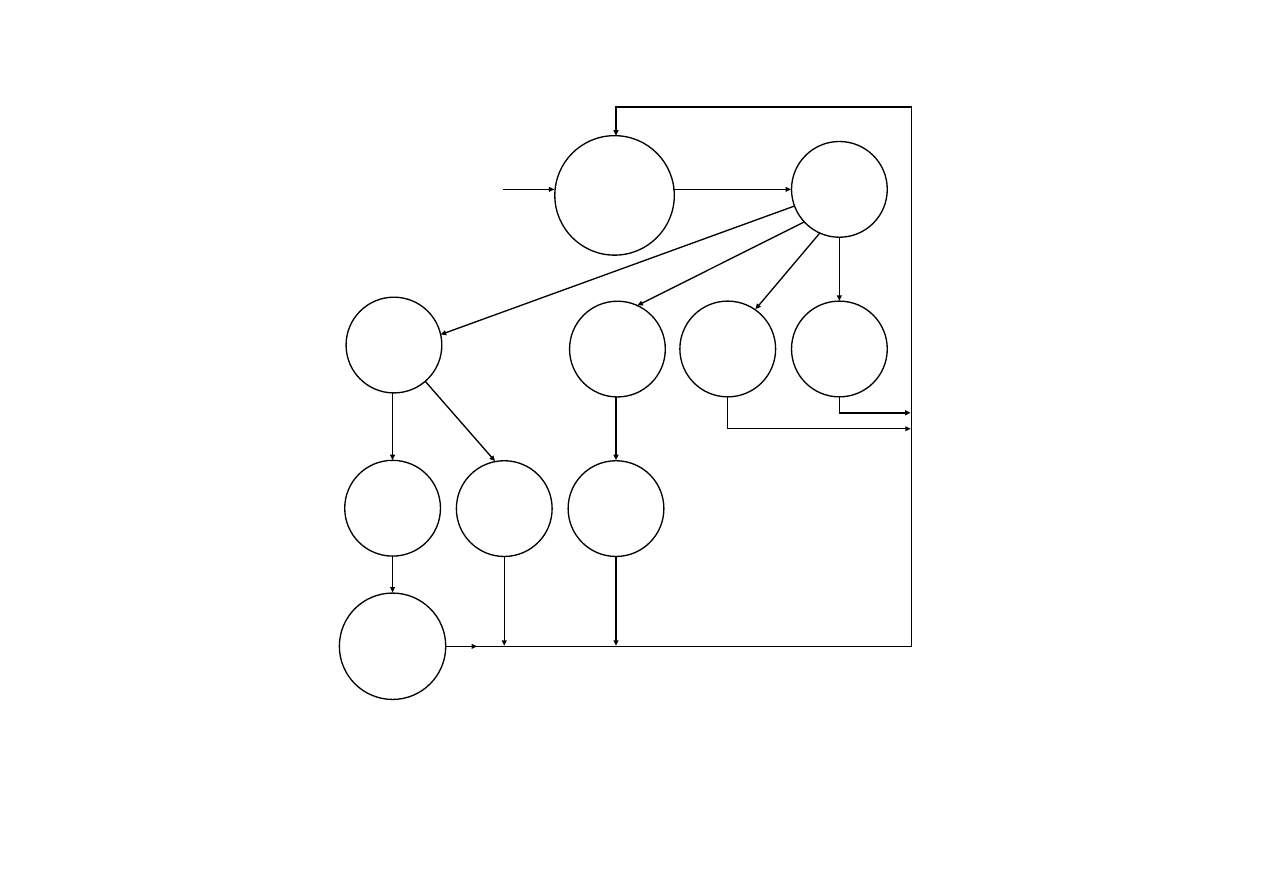

Kompletna architektura multi–cycle

Sygnał

0

1

RegDst

numer rejestru do zapisu

numer rejestru do odczytu

RegWrite

—

zezwolenie na zapis od pliku rejestrów

ALUSrcA

PC do ALU

A do ALU

MemRead

—

zezwolenia na odczyt z pamięci

MemWrite

—

zezwolenia na zapis do pamięci

MemToReg

dane do zapisu w pliku

rejestrów z ALUOut

dane do zapisu w pliku

rejestrów z MDR

IorD

pamięć adresowana PC

pamięć adresowana ALUOut

IRWrite

—

zezwolenia na zapis do IR

PCWrite

—

zezwolenia na zapis do PC

PCWriteCond

—

warunkowy zapis do PC

1-bitowe sygnały sterujące architektury multi–cycle

Sygnał

wartość

Działanie

ALUOp

00

01

10

dodawanie (load-store)

odejmowanie (branch)

zależnie od pola Function (R-type)

ALUSrcB

00

01

10

11

B (R-type) do ALU

4 do ALU

instrukcja[15-0] (load-store) do ALU

instrukcja[15-0]«2 (branch) do ALU

PCSource

00

01

10

ALU (PC+4) do PC

ALUOut (branch) do PC

PC[31-26]+IR[25-0]«2 (jump) do PC

2-bitowe sygnały sterujące architektury multi–cycle

PCWrite

PCSource = 10

ALUSrcA = 1

ALUSrcB = 00

ALUOp = 01

PCWriteCond

PCSource = 01

ALUSrcA =1

ALUSrcB = 00

ALUOp = 10

RegDst = 1

RegWrite

MemtoReg = 0

MemWrite

IorD = 1

MemRead

IorD = 1

ALUSrcA = 1

ALUSrcB = 10

ALUOp = 00

RegDst= 0

RegWrite

MemtoReg=1

ALUSrcA = 0

ALUSrcB = 11

ALUOp = 00

MemRead

ALUSrcA = 0

IorD = 0

IRWrite

ALUSrcB = 01

ALUOp = 00

PCWrite

PCSource = 00

Instruction fetch

Instruction decode/

register fetch

Jump

completion

Branch

completion

Execution

Memory address

computation

Memory

access

Memory

access

R-type completion

Write-back step

(Op

= 'L

W')

or (Op

= 'SW

')

(Op

= R-type)

(Op

=

'BEQ

')

(Op=

'J')

(Op

=

'SW

')

(Op=

'L

W

')

4

0

1

9

8

6

2

7

5

3

Start

Kompletny diagram stanów bloku sterowania

Rej. Stanu

Outputs

Inputs

(nastêpny stan)

Q[3-0]

Q(t+1) = F( Q(t), Opcode)

Control = F( Q(t), Opcode)

Blok logiki

kombinacyjnej

Opcode

instrukcji

Instr[31-26]

Sygna³y

steruj¹ce

Control[n-0]

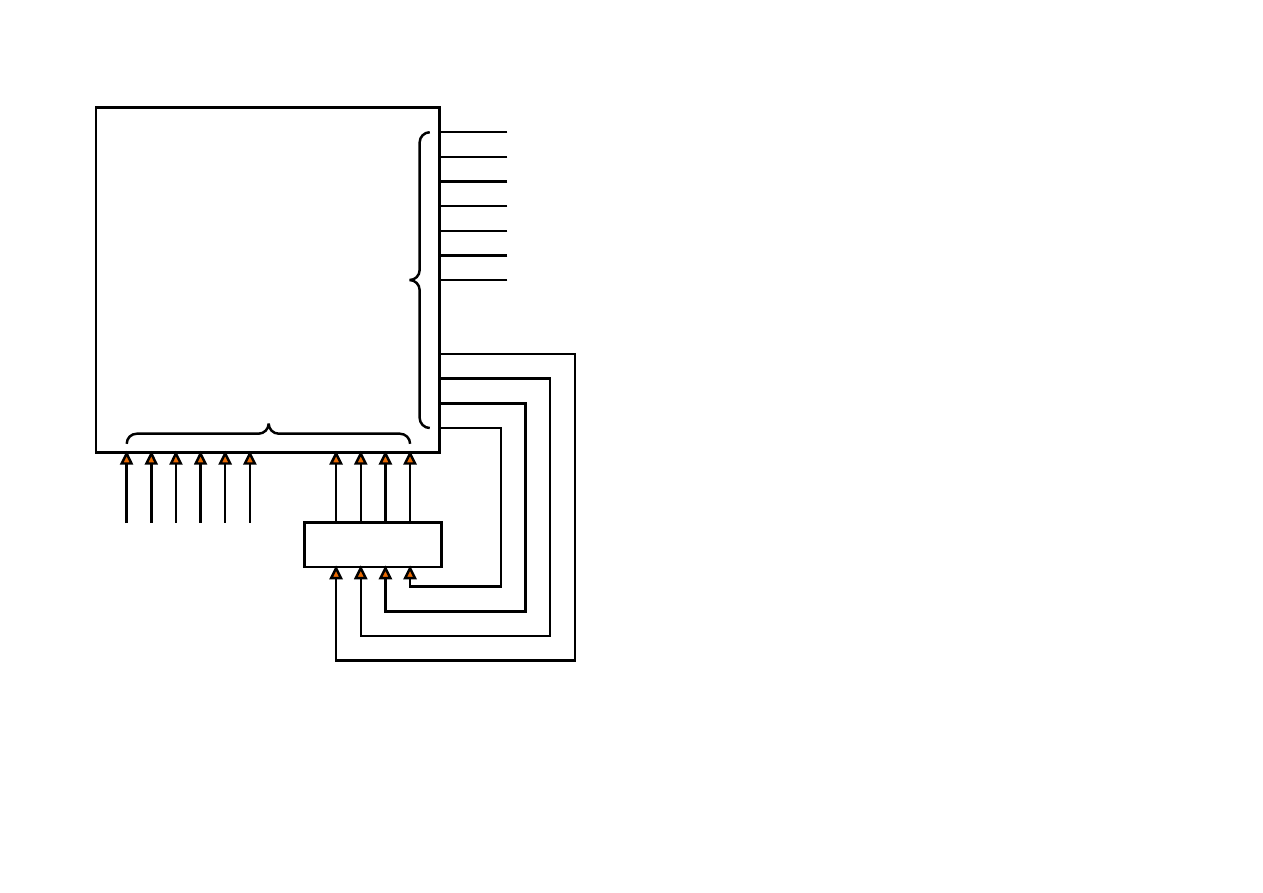

Realizacja sterowania w postaci maszyny stanowej

Pamiêæ ROM

adres

dane

Opcode

Sygna³y steruj¹ce

Realizacja sterowania w postaci pamięci ROM

Wyszukiwarka

Podobne podstrony:

multi demultiplekser

LG MULTI V

ALAN42 MULTI component side

Cell Cycle

Multi PIN AEGON Firma 2008

Karta katalogowa Klimatyzator typu Multi Split V

Castles & Crusades Multi Classing

NDT 52517 a novel 5 category multi modal t1 and t2wi mri based strati 031914

Multi X english

CHIGO MULTI

multi 6, AGH

porozumienie 2010, Mechatronika AGH IMIR, semestr 6, Elementy wyk. robotów 2, ARTAS.SAM.v6.0.45.Mult

Cwiczenia 3 Multi wyniki

Karta katalogowa Klimatyzator typu Multi Split V (2)

cycle of the werewolf EITNCPGGIBOBU4OC7WR4L5LXCBZM7ZE6QFOTQVQ

racismz int (2) , Racism has become one of the many burdens amongst multi-cultural worlds like Canad

Obrona na multi

więcej podobnych podstron