Jarosław Mróz, Jacek Mostowicz – Układy logiczne TTL

1

WFiIS

Imię i nazwisko:

1.

2.

ROK GRUPA

ZESPÓŁ

LABORATORIUM

Z ELEKTRONIKI

TEMAT:

NR ĆWICZENIA

Data wykonania:

Data oddania:

Zwrot do poprawy:

Data oddania: Data

zliczenia: OCENA

CEL ĆWICZENIA

Badanie działania bramki NAND wykonanej w technologii TTL oraz układów zbudowanych

w oparciu o tę bramkę.

WSTĘP TEORETYCZNY

Układy logiczne TTL (transistor-transistor logic) są jedną z najbardziej znanych rodzin

układów cyfrowych opartych na tranzystorach bipolarnych.

Główne parametry technologii TTL:

-zasilanie:

5 ( 5%)

V

+

±

-krótki

czas

propagacji:

~ 10ns

-stosunkowo duża moc strat:

~ 10mW

-układ rozumie jako logiczny stan niski (L) napięcie na wejściu:

0

0,8

in

V U

V

<

<

-układ rozumie jako logiczny stan wysoki (H) napięcie na wejściu:

2

5

in

V U

V

<

<

-otrzymywane napięcie na wyjściu dla stanu niskiego (L):

0, 4

out

U

V

≤

-otrzymywane napięcie na wyjściu dla stanu wysokiego (H):

2, 4

out

U

V

≥

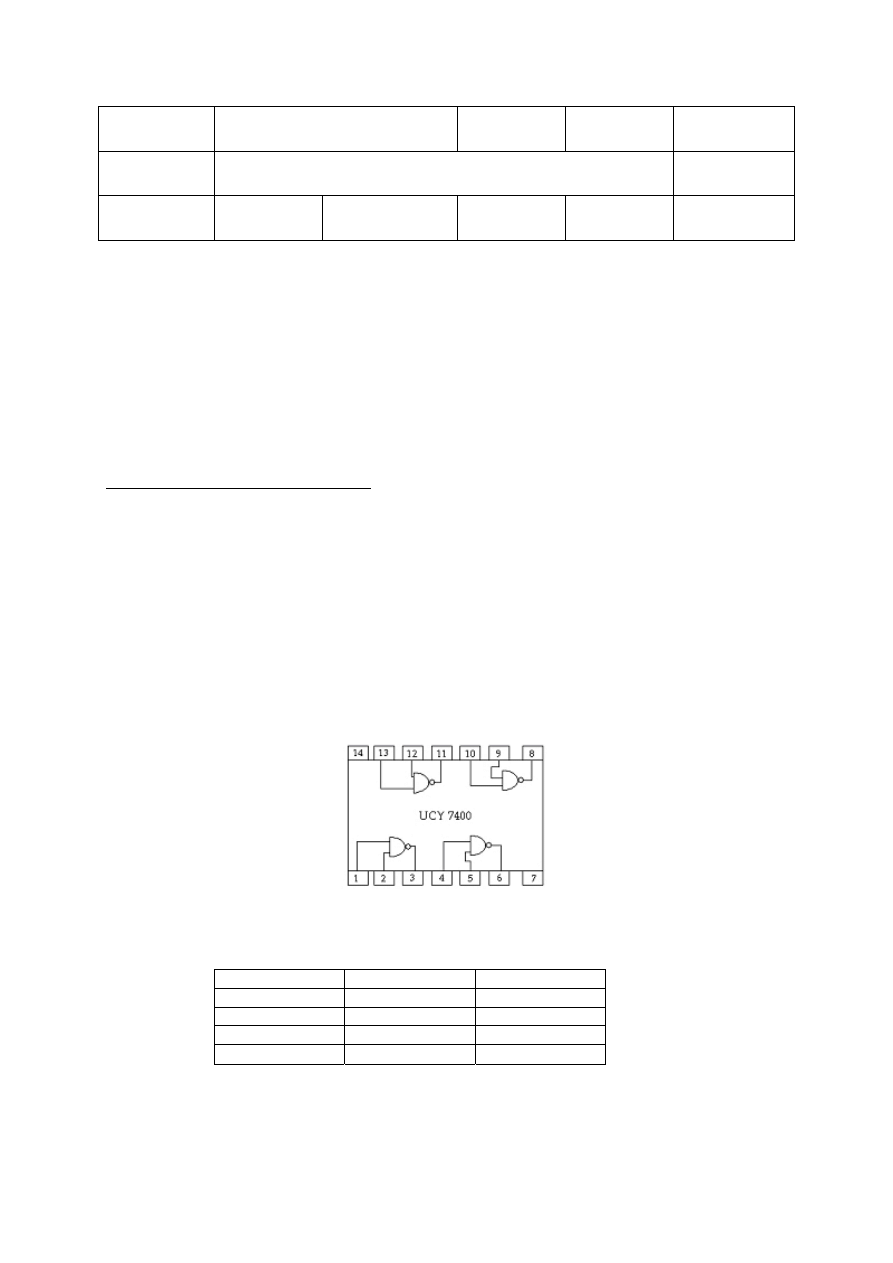

Na zajęciach korzystano z układu UCY7400, który zawiera cztery dwuwejściowe bramki

NAND. Poniżej przedstawiono schemat wewnętrzny tego układu.

Tablica prawdy dla bramki logicznej NAND (stan LOW=L, stan HIGH=H) :

IN1 IN2 OUT

L L H

L H H

H L H

H H L

Jarosław Mróz, Jacek Mostowicz – Układy logiczne TTL

2

Zalety układów TTL:

• duża szybkość przełączenia

• duży współczynnik powielania logicznego

• małe impedancje wyjściowe w stanie L i H

• pojedyncze źródło napięcia zasilania

• duża odporność na zakłócenia

• praca w szerokim zakresie temperatur

• duża pewność działania

Wady układów TTL:

• wejścia układów TTL w stanie niskim są źródłem prądu, utrudnia to stosowanie

układów opóźniających RC

• układy TTL wymagają napięcia zasilania: +5V ±5% przy stosunkowo dużym

poborze mocy

• ponieważ ich stopnie wyjściowe wytwarzają w chwilach przełączeń szpilki prądu

zasilającego o dużym natężeniu, wymaga to hojnego szafowania pojemnościami

zwierającymi szpilki (najlepiej w liczbie jednego kondensatora

0,1 F

μ

)

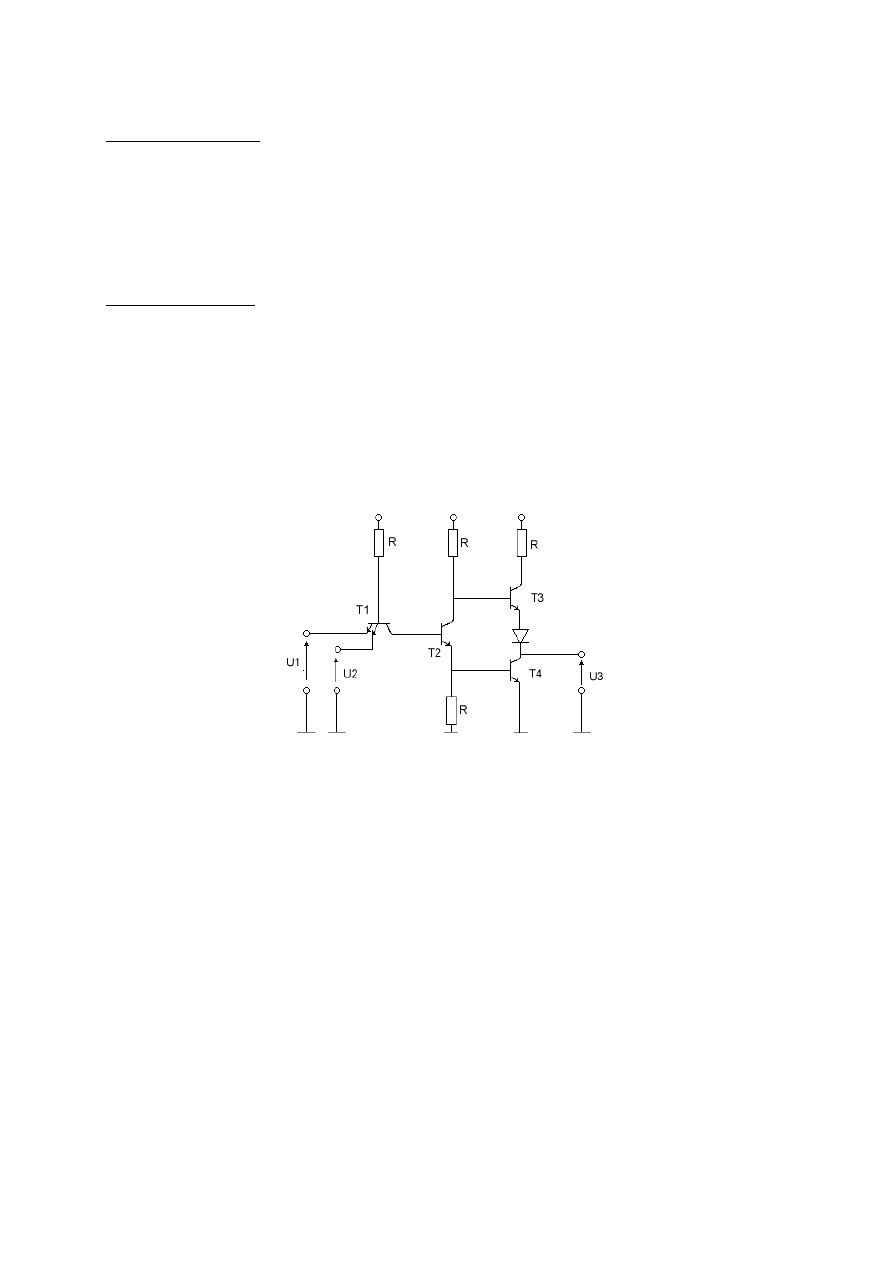

Realizacja standardowej bramki NAND w technologii TTL typu 7400

Jarosław Mróz, Jacek Mostowicz – Układy logiczne TTL

3

OPRACOWANIE POMIARÓW

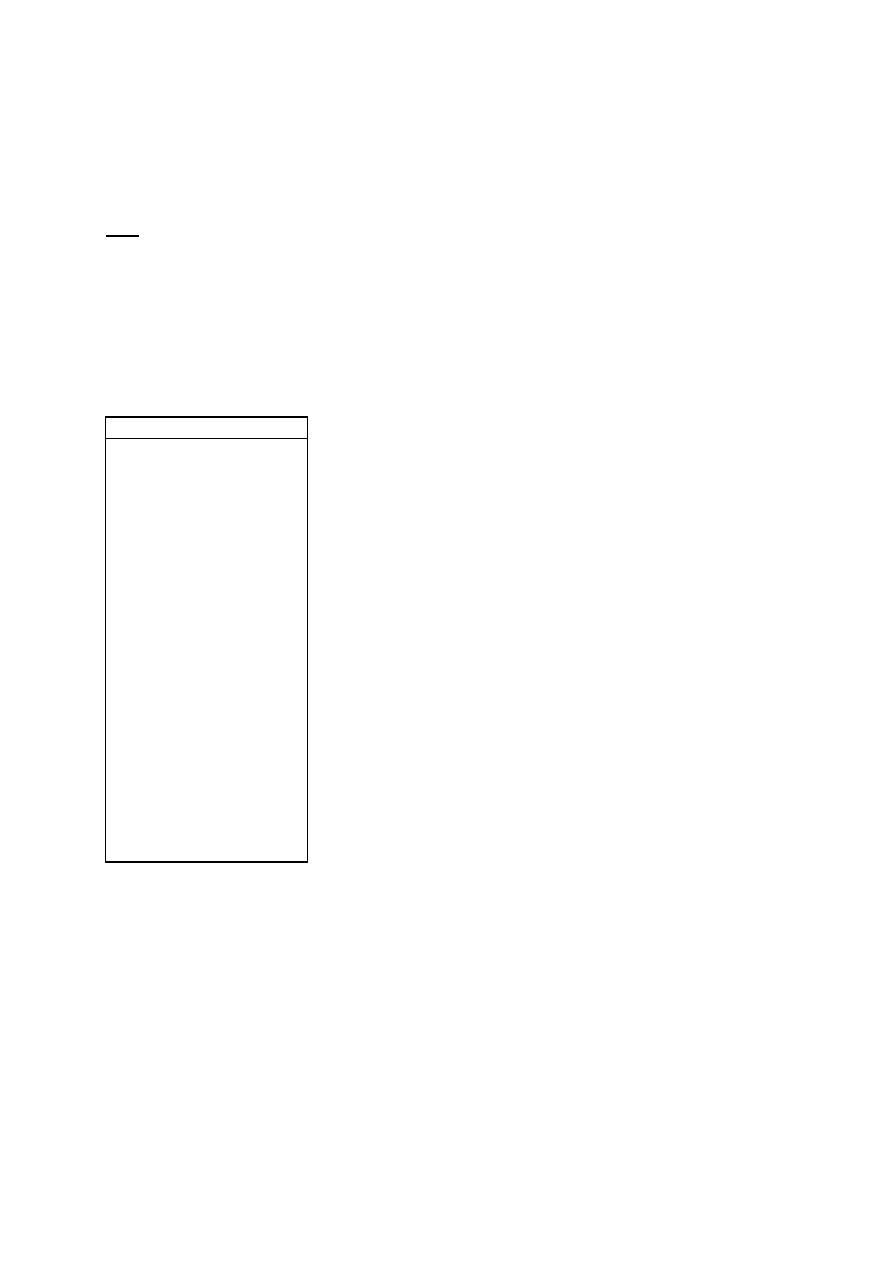

1.1. Dla jednej z bramek logicznych układu UCY7400 badano charakterystykę

(

)

out

in

U

f U

=

(zależność napięcia wyjściowego

out

U

od napięcia wejściowego

in

U

).

Pomiaru dokonano dla następującego zakresu napięć wejściowych

0 2, 5V

−

.

Wejścia pozostałych bramek zostały zwarte do masy.

W pierwszej kolumnie poniższej tabeli znajduje się wartość napięcia wejściowego, w

drugiej wartość napięcia wyjściowego.

Uin [V]

Uout [V]

0,007 3,94

0,300 3,93

0,500 3,92

0,600 3,85

0,700 3,72

0,800 3,59

0,900 3,45

1,000 3,31

1,100 3,12

1,200 2,80

1,250 2,62

1,300 1,82

1,350 1,32

1,400 0,97

1,410 0,95

1,420 0,41

1,430 0,29

1,440 0,03

1,450 0,03

1,500 0,03

2,000 0,03

2,500 0,03

tabela 1.1 – rezultaty pomiaru zależności

out

U od

in

U

;

Jarosław Mróz, Jacek Mostowicz – Układy logiczne TTL

4

Zależność Uout=f(Uin)

0,0

0,5

1,0

1,5

2,0

2,5

3,0

3,5

4,0

4,5

0

0,2

0,4

0,6

0,8

1

1,2

1,4

1,6

1,8

2

2,2

2,4

2,6

2,8

Uin [V]

Uo

ut [

V

]

pomiary

wykres 1.1

Na powyższym wykresie można zauważyć, że stan wysoki odpowiada napięciu na wyjściu

4

out

U

V

≈

(znaczony jako stan HIGH), a stan niski odpowiada wartości

0, 03

in

U

V

=

(oznaczony jako LOW).

LOW

HIGH

Jarosław Mróz, Jacek Mostowicz – Układy logiczne TTL

5

1.2. Dla jednej z bramek badano charakterystykę

(

)

cc

in

I

f U

=

. Napięcie wejściowe

zmieniane było w zakresie

0 2, 5V

−

jednocześnie mierząc prąd wpływający

cc

I

.

Wejścia pozostałych bramek były zwarte do masy.

Dodatkowo w celu otrzymania prądu pobieranego przez jedną bramkę zmierzono prąd

wszystkich bramek zwartych do masy, podzielono ten wynik przez 4 (ilość bramek w

układzie) i pomnożono przez 3 (ilość bramek zwartych do masy podczas pomiaru).

Prąd wszystkich bramek zwartych do masy:

0

4,1

cc

I

mA

=

W pierwszej kolumnie poniższej tabeli znajduje się wartość napięcia wejściowego, w

drugiej zmierzony prąd, a w trzeciej prąd pobierany przez jedną bramkę

(

0

1

3

4

c

cc

cc

I

I

I

=

−

).

Uin [V]

Icc [mA]

Ic1 [mA]

0,007 4,10 1,03

0,300 4,04 0,97

0,500 4,00 0,93

0,600 4,02 0,95

0,700 4,08 1,01

0,800 4,14 1,07

0,900 4,20 1,13

1,000 4,27 1,20

1,100 4,34 1,27

1,200 4,43 1,36

1,250 4,56 1,49

1,300 11,83 8,76

1,350 18,18 15,11

1,400 24,60 21,53

1,410 25,30 22,23

1,420 29,10 26,03

1,430 29,60 26,53

1,440 6,30 3,23

1,450 6,30 3,23

1,500 6,30 3,23

2,000 6,30 3,23

2,500 6,30 3,23

tabela 1.2 – rezultaty pomiaru zależności

cc

I

od

out

U

Jarosław Mróz, Jacek Mostowicz – Układy logiczne TTL

6

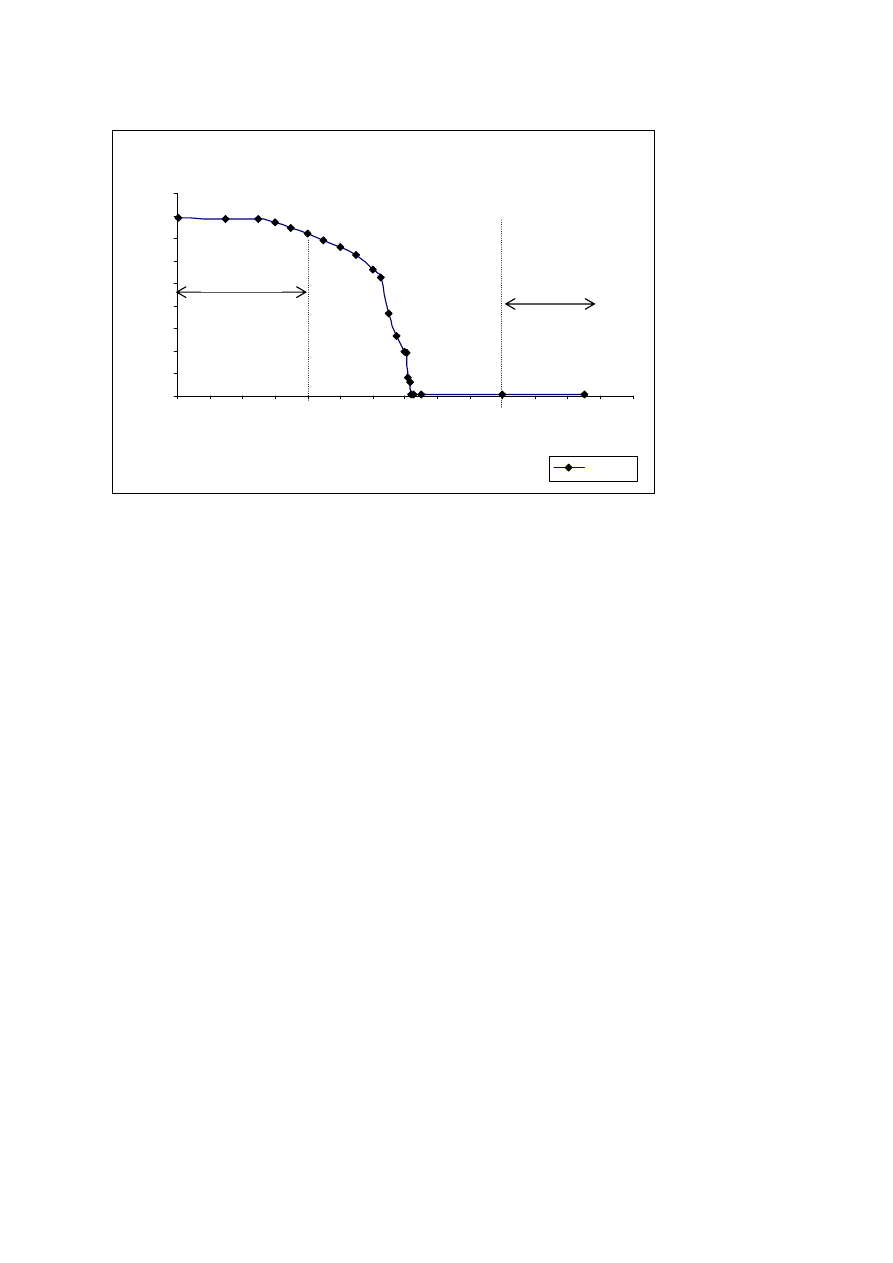

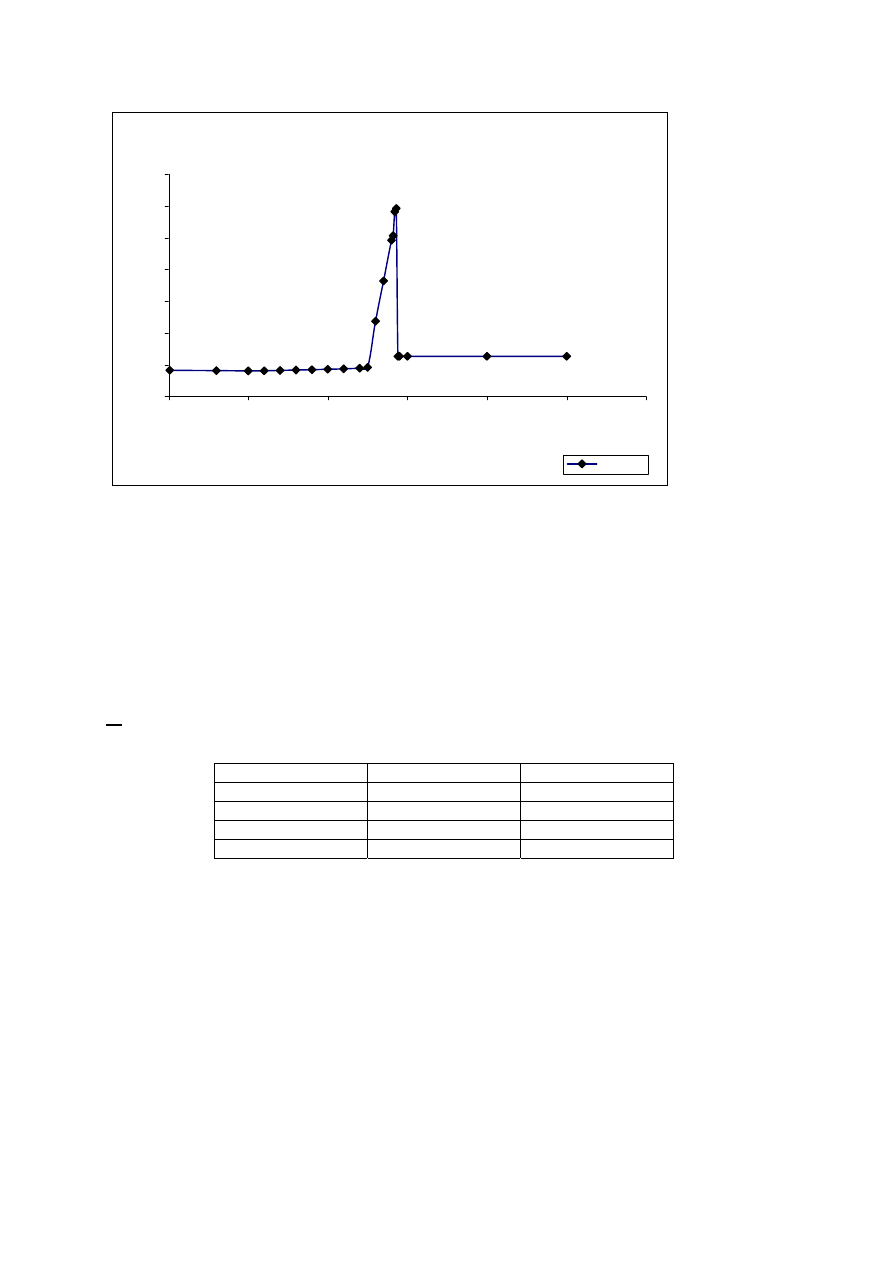

Zależność Icc=f(Uin)

0

5

10

15

20

25

30

35

0

0,5

1

1,5

2

2,5

3

Uin [V]

Icc [m

A]

pomiary

wykres 1.2

Dla stanu wysokiego bramka pobiera prąd

1

1

c

I

mA

≈

, a w stanie niskim pobór jest

większy i wynosi

1

3

c

I

mA

≈

. Można łatwo zauważyć, że maksymalny prąd jest pobierany

w czasie przełączania tranzystorów

2. Sprawdzenie tablicy prawdy dla bramki NAND. Jako logiczne zero wejście zwierano do

masy, a jako logiczne jeden wejście zwierano do linii zasilania (5V).

wejście A [V]

wejście B [V]

wyjście Y [V]

0 0

3,98

0 5

3,97

5 0

3,98

5 5

0,03

tablica 2 – tablica prawdy dla bramki NAND

Jarosław Mróz, Jacek Mostowicz – Układy logiczne TTL

7

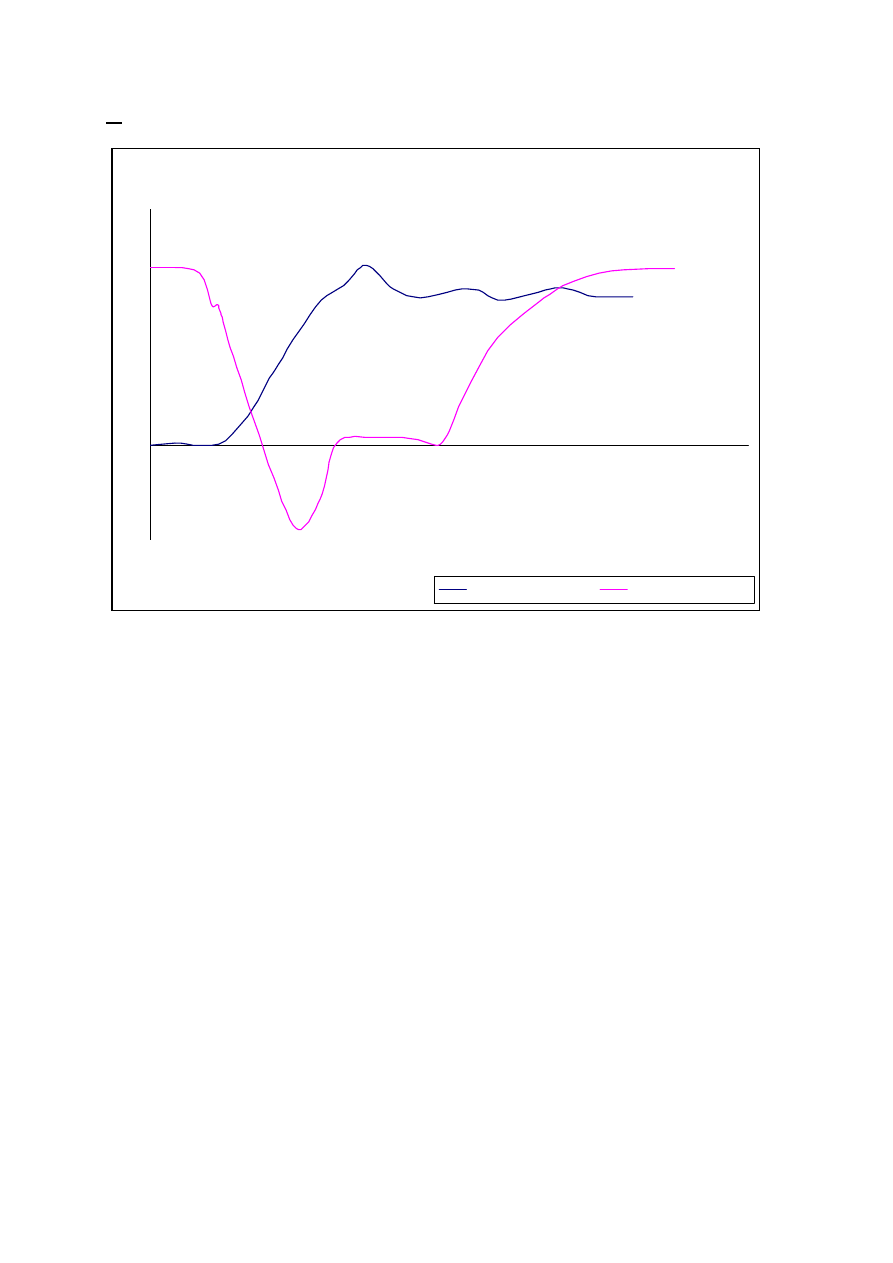

3. Odpowiedź bramki na impuls prostokątny

odpowiedź bramki na impuls prostokatny

t [ns]

U [

V

]

impuls prostokątny

odpowiedź bramki

wykres 2 – odpowiedź bramki na impuls prostokątny

Na wykresie 2 przedstawiono odpowiedź bramki NAND na sygnał prostokątny. Za pomocą

oscyloskopu odczytano czas propagacji

pHL

t

oraz czas opadania impulsu

oLH

t

:

14, 4

pHL

t

ns

=

8,8

oLH

t

ns

=

Podobnie postąpiono ze zboczem opadającym sygnały wyjściowego. Czas

pLH

t

to czas

propagacji, a

nHL

t

to czas narastania zbocza:

20,8

pLH

t

ns

=

23, 2

nHL

t

ns

=

Średni czas propagacji można policzyć za pomocą średniej arytmetycznej

pHL

t

i

pLH

t

:

17, 6

pŚR

t

ns

=

Świadczy to o szybkości bramek NAND wykorzystywanych przy budowie szybkich

układów cyfrowych.

Jarosław Mróz, Jacek Mostowicz – Układy logiczne TTL

8

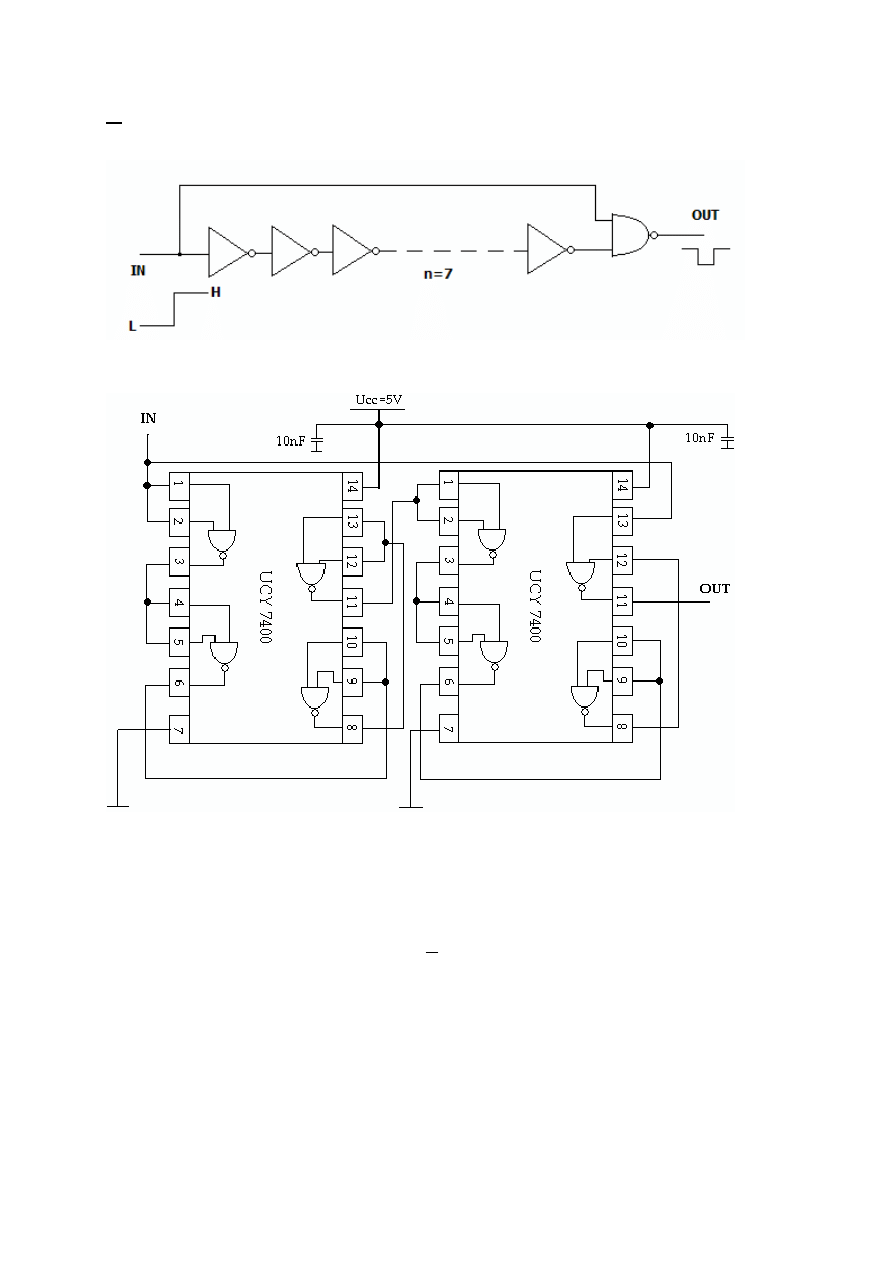

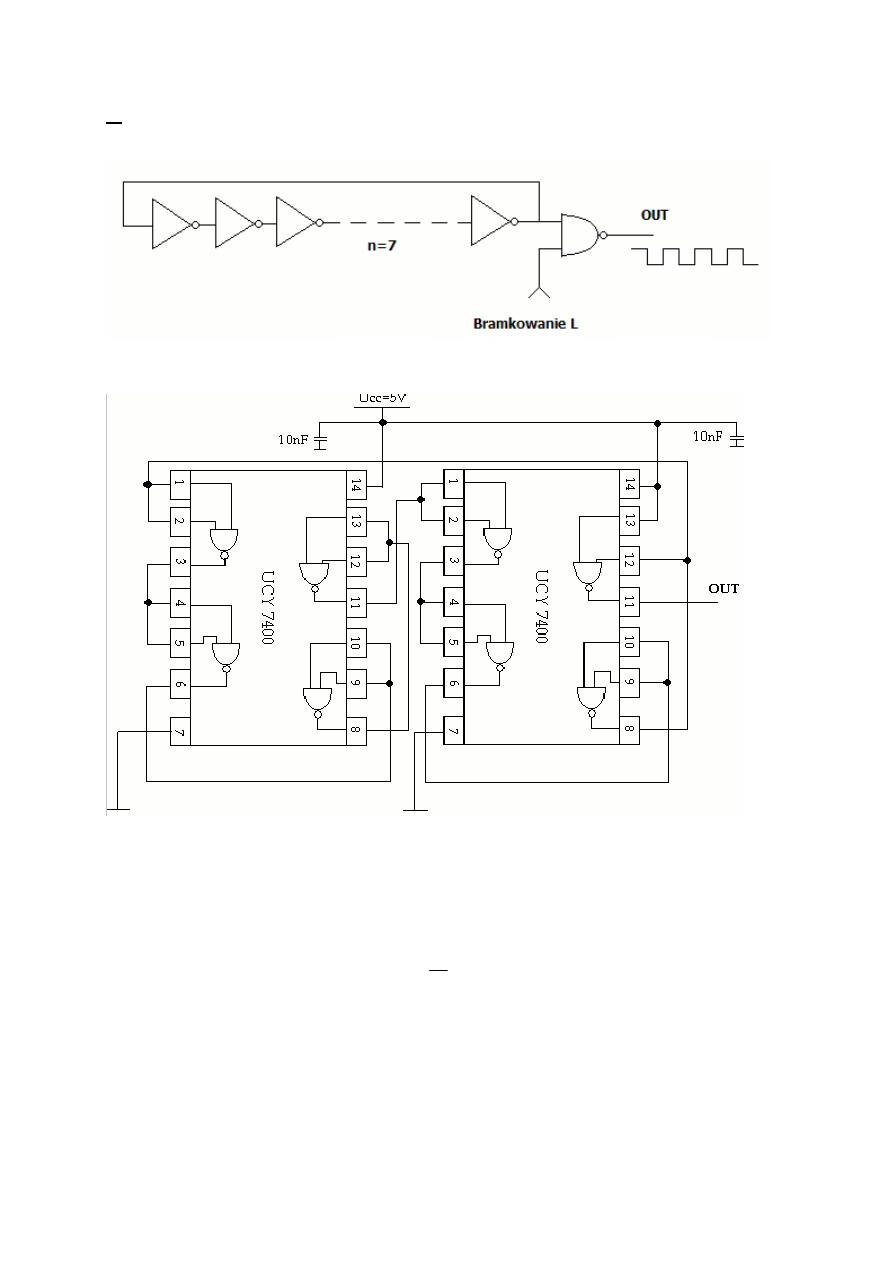

4. Badanie działania układu złożonego z 7 inwerterów.

Układ jest realizowany przez dwa układy UCY7400.

schematyczne przedstawienie układu siedmiu inwerterów

realizacja układu na płytce montażowej

Czas trwania sygnału obserwowanego na wyjściu układu to

66, 4

i

t

ns

=

. Znając ten czas

oraz liczbę inwerterów w układzie można w prosty sposób obliczyć średni czas propagacji

sygnału przez jeden inwerter:

9, 49

7

i

iŚR

t

t

ns

= ≈

Impuls podawany na wejściu układu potrzebuje więcej czasu na przejście przez 7

inwerterów i dotarcie do bramki niż impuls biegnący bezpośrednio do niej. Ponieważ jest

nieparzysta ilość inwerterów na drugim wejściu dostajemy impuls przeciwny logicznie, ale

ze względu na opóźnienie inwerterów, przez krótki okres czasu na wejściach bramki

NAND jest ten sam stan logiczny, co powoduje powstanie na wyjściu stanu L.

Jarosław Mróz, Jacek Mostowicz – Układy logiczne TTL

9

5. Badanie działania generatora.

Układ jest realizowany za pomocą dwóch układów UCY7400.

schematyczne przedstawienie generatora

realizacja układu na płytce montażowej

Za pomocą oscyloskopu wyznaczono okres generowanego impulsu:

135

T

ns

=

W celu wyznaczenia średniego czasu propagacji należy podzielić okres

T

przez 14 (7

inwerterów):

9, 6

14

pŚR

T

t

ns

=

≈

Jarosław Mróz, Jacek Mostowicz – Układy logiczne TTL

10

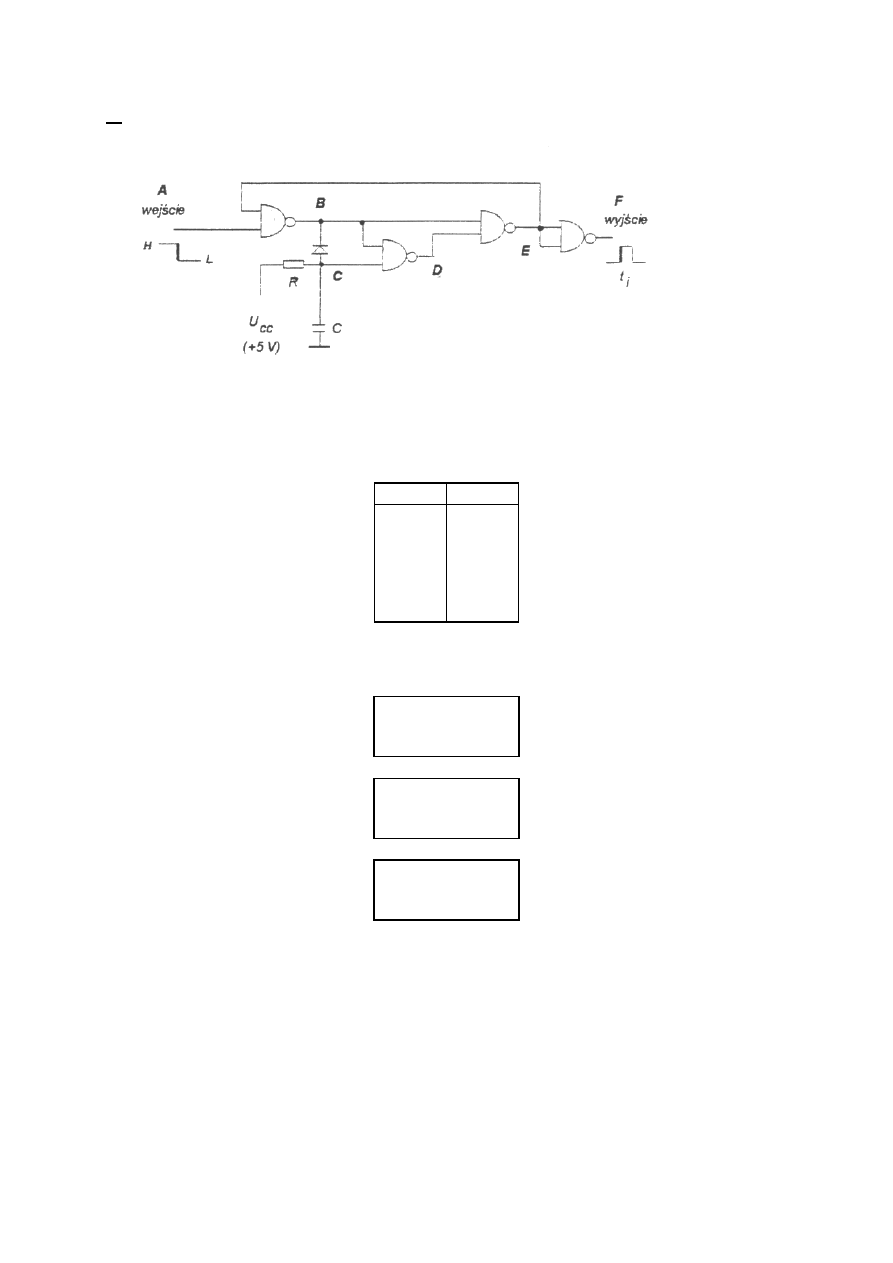

6. Badanie działania multiwibratora monostabilnego.

schematyczne przedstawienie multiwibratora monostabilnego

Dla wartości

10

R

k

=

Ω

oraz

1

C

nF

=

zmierzono wartość napięcia w punktach od A do F

(rysunek powyżej). Wyniki zestawiono w tabeli:

U [V]

A

2,00

B

1,88

C

1,06

D

2,45

E

3,14

F

0,61

Następnie wyznaczono czas trwania impulsów wyjściowych dla różnych wartości

rezystora R i kondensatora C. Wyniki zestawiono w poniższych tabelach:

R [

Ω]

100

C [nF]

10

t [ns]

314

R [

Ω]

100

C [nF]

100

t [ns]

522

R [

Ω]

100

C [

μF]

1

t [

μs]

4,92

Jarosław Mróz, Jacek Mostowicz – Układy logiczne TTL

11

WNIOSKI

Układy serii TTL pomimo swoich zalet ustępują innym technologiom używanym w

układach o dużej komplikacji i jednocześnie małych wymiarach. Wynika z tego

zminimalizowane zużycie prądu. Układy TTL pobierają znaczne zużycie energii

(polaryzacja tranzystorów) co pokazało ćwiczenie 1.2. Powoduje to nadmierne grzanie się

układów, które jest wielce niepożądane przy budowie mikroprocesorów.

Największy pobór prądu zaobserwowano w czasie przełączania tranzystorów

(wykres 1.2), a dokładnie mówiąc przeładowania pojemności.

Na podstawie ćwiczenia 1.1 oraz 2 zaobserwowano, że układy TTL nie trzymają na

wejściach dokładnych stanów logicznych. Dzięki temu otrzymano pewne marginesy dla

sygnałów wejściowych, które nie mają czystego stanu logicznego. Z drugiej strony na

wyjściu otrzymujemy bardzo dokładne stany logiczne.

Dodatkowo za pomocą bramek NAND można realizować dowolne funkcje logiczne, co jest

dowodem ich uniwersalności w zastosowaniach.

LITERATURA

1) Układy Półprzewodnikowe U.Tietze, C.Schenk;

ZAŁĄCZNIKI

1) zestaw wyników pomiarów z laboratorium;

Wyszukiwarka

Podobne podstrony:

Cw 21 Bramka NAND

Cw 21 Bramka NAND id 122412 Nieznany

Cw 21 Bramka NAND

Badanie bramki NAND, BRAMKAnand, RADOM

Badanie bramki NAND, BRAMKAnand, RADOM

Wykład VII hazard, realizacja na NAND i NOR

C1 BramkaNAND

KONSPEKT TRENINGU BRAMKARSKIEGO chwyt pilki

gra bramkarza przy wrzutkach

Projekt P09 Sterowanie bramka Instrukcja id 399298

KONSPEKT TRENINGU BRAMKARSKIEGO chwyt po pod

74F10 NAND 3 inp

CIERPIENIA BRAMKARZA Q?SS

badanie bramki NAND CMOS, -1-

więcej podobnych podstron