9 Podać różnice pomiędzy mikrokontrolerami 8051, 8052 oraz AduC812.

8051

8052

ADuC812

wersja z wewnętrzną pamięcią

programu typu ROM, której

zawartość jest nieznana z naszego

punktu widzenia, toteż układ

możemy wykorzystać do pracy

tylko z dołączona zewnętrzną

pamięcią np. EPROM do której

zapiszemy nasz program (wtedy

pamięć ROM jest wyłączona −

nieaktywna)

-128B RAM

-2 liczniki/timery

-8-bitowa ALU

jest to procesor identyczny z 8051

tyle że posiada dodatkowy

trzeci programowalny

licznik/timer (nazywany jako

“T2”) i dwa

razy więcej pamięci RAM

(256B) .

-pamieć programu flash/EEPROM

8kB

-pamiec danych flash/EEPROM

640B

-256B RAM

-kanał DMA

-przetworniki A/C i D/C

18 Tryb rzeczywisty, tryb chroniony oraz tryb wirtualny V86 procesorów i386 i wyższych.

Tryb wirtualny (zwany także V86 lub Virtual 8086) — specjalny tryb pracy procesorów o architekturze

IA-32, dostępny w trybie chronionym, który umożliwia uruchamianie programów przeznaczonych dla trybu

rzeczywistego. W trybie wirtualnym symulowane jest działanie analogiczne dla procesora Intel 8086

(faktycznie można uruchamiać kod także dla 8088, 80186 i 80188), tzn. otrzymuje dostęp do 1 MB pamięci i

rejestrów procesora i może wykonywać te rozkazy, które mają sens w takim otoczeniu.

Natomiast w odróżnieniu od "prawdziwego" trybu rzeczywistego, wszelki dostęp do portów procesora jest

sankcjonowany przez system operacyjny pracujący w trybie chronionym. Podobnie przerwania są

obsługiwane przez system operacyjny. To umożliwia bezkonfliktową pracę zwykłych zadań systemu i zadań

V86. Możliwe jest ponadto jednoczesne uruchmienie wielu zadań V86.

Ponieważ to na system operacyjny spada obsługa dostępu do portów oraz przerwań, system musi emulować

sprzęt, jak i udostępniać określoną funkcjonalność 16-bitowego systemu operacyjnego. Innymi słowy system

musi tłumaczyć żądania zadania V86, np. zapis do określonego portu na akcję sterownika sprzętu.

Tryb V86 jest wykorzystywany do uruchamiania programów DOS-owych. System Windows posiada

wbudowane mechanizmy umożliwiające uruchomienie takich programów (w Windows NT jest to NTVDM),

natomiast dla systemu Linux istnieje specjalny program dosemu.

Tryb chroniony (ang. protected mode) – to tryb pracy mikroprocesorów serii x86 wprowadzony w

mikroprocesorze Intel 80286. Tryb chroniony umożliwia adresowanie pamięci w większym zakresie niż

1MB (tryb rzeczywisty), wprowadza wiele nowych udogodnień wspierających wielozadaniowość, takich

jak: sprzętowa ochrona pamięci (układ MMU), wsparcie przełączania kontekstu procesora i wiele innych.

Większość nowoczesnych systemów operacyjnych wykorzystuje procesory serii x86 właśnie w trybie

chronionym. Zaliczają się do nich m.in.: Linux, Windows w wersji 3.0 i wyższych, systemy z rodziny BSD.

Tryb chroniony został wprowadzony do mikroprocesora Intel 80286 wraz z trybem rzeczywistym (ang. real

mode) dla zachowania zgodności z poprzednimi mikroprocesorami rodziny x86. W mikroprocesorze Intel

80286 w trybie chronionym 16-bitowe rejestry segmentowe CS, SS, DS, ES zawierają selektory, które

jednoznacznie określają deskryptor (8-bajtowa struktura w pamięci) opisujący segment. Deskryptor

dysponuje następującymi informacjami o segmencie: fizyczna lokalizacja segmentu w pamięci (24-bitowy

adres bazowy, 16-bitowa długość segmentu w bajtach), prawa dostępu do segmentu i numer uprawnienia

segmentu. W odróżnieniu od trybu chronionego w trybie rzeczywistym rejestry segmentowe CS, SS, DS, ES

zawierają adresy bazowe (początków) segmentów. Procesor zaczyna pracę trybie chronionym po ustawieniu

bitu PE (ang. Protection Enable) na jeden, wyzerowanie tego bitu powoduje powrót do trybu rzeczywistego

(bit PE to najmłodszy bit rejestru CR0 (ang. Control Register)).

Tryb rzeczywisty to tryb pracy mikroprocesorów z rodziny procesorów x86, w którym procesor pracuje tak

jak procesor Intel 8086.

Nowym trybem pracy procesora Intel 80286 był tryb chroniony.

W trybie tym brak ochrony pamięci przed użyciem przez inny proces i brak obsługi wielozadaniowości. W

trybie rzeczywistym pracowały programy w systemie operacyjnym DOS, na przełomie lat 80 i 90

dwudziestego wieku prowadzono działania nad pracą programów w systemie DOS w trybie chronionym,

pozostawiając sam system w trybie rzeczywistym, zbudowano kilka systemów umożliwiających taką pracę

systemu.

W trybie rzeczywistym dostępna jest 1-megabajtowa przestrzeń adresowa. Adres logiczny (programowy)

składa się z dwóch liczb 16-bitowych: segmentu (numeru segmentu) oraz przemieszczenia względem

początku segmentu (ang. offset). Adres fizyczny jest liczony jako segment * 16 + przemieszczenie. Ponieważ

segmenty nie są rozłączne, wiele różnych adresów logicznych może odwoływać się do tej samej komórki

pamięci (dokładnie - jeden adres fizyczny jest opisywany przez 4096 różnych adresów logicznych).

Ponieważ segment i przemieszczenie mają 16 bitów, dlatego w trybie rzeczywistym można maksymalnie

zaadresować 1088 kB pamięci, ale procesory Intel 8086, 8088, 80188 oraz 80186 posiadają 20-bitową szynę

adresową i z tego powodu mogą zaadresować tylko 1024 kB pamięci – przy próbie sięgnięcia do adresu

powyżej 1024 kB w rzeczywistości odwołają się do adresu o 1 MB niższego.

Procesory nowsze, tzn. i286, i386 itd., mają szersze szyny adresowe (24-, 32- lub 36-bitowe) toteż pracując

w trybie rzeczywistym mogą adresować całe 1088 kB pamięci. System DOS począwszy od wersji 4.0

potrafił wykorzystać te dodatkowe 65536-16 B pamięci, która została nazwana pamięcią wysoką (HMA —

High Memory Area).

Jednak powoduje to niepełną zgodność z procesorami Intel 8086 i dlatego w komputerach zgodnych z

IBM/PC została wprowadzona możliwość blokowania 21. linii adresowej nowszych procesorów, co sprawia,

że programy pracujące w trybie rzeczywistym mają dostęp do 20 linii. Blokowanie i odblokowywanie linii

21 jest udostępniane przez ustawienie w biosie komputera bramkę A20 (ang. A20 gate; A20 to numer linii

adresowej, liczony od 0).

17 Co to jest pamięć wirtualna oraz układ zarządzania pamięcią MMU.

Pamięć wirtualna jest techniką programową a także sprzętową gospodarowania pamięcią operacyjną RAM

pozwalającą na przydzielanie pamięci dla wielu procesów, zwalnianie jej i powtórne przydzielanie.

Mechanizm umożliwia przydzielenie procesom więcej pamięci niż rzeczywista ilość pamięci fizycznej

zainstalowanej w komputerze poprzez przeniesienie danych z ostatnio nie używanej pamięci do pamięci

masowej (np. twardego dysku), w sytuacji gdy procesor odwołuje się do danych z pamięci przeniesionej na

dysk przesuwa się te dane do pamięci w wolne miejsce, a gdy brak wolnej pamięci zwalnia się ją przez

wyżej opisane przerzucenie jej na dysk.

MMU (Memory Management Unit), to zestaw układów realizujących dostęp do pamięci fizycznej żądanej

przez CPU. Wśród zadań tych układów znajdują się funkcje translacji pamięci wirtualnej do pamięci

fizycznej, ochronę pamięci, obsługę pamięci podręcznej, zarządzanie szynami danych oraz, w prostszych

(szczególnie 8-bitowych) systemach, przełączanie banków pamięci.

Obecne układy MMU dzielą przestrzeń logiczną (wirtualną) pamięci na strony, których rozmiar wynosi 2

N

,

zazwyczaj kilka kilobajtów. Młodsze N bitów adresu (przesunięcie - ang. offset) pozostaje niezmienione,

podczas gdy starsze bity adresu określają numer (logiczny) strony pamięci. MMU tłumaczy adresy logiczne

(wirtualne) na adresy fizyczne za pomocą asocjacyjnej pamięci podręcznej nazywanej TLB — Translation

Lookaside Buffer. Jeżeli TLB nie posiada odpowiedniego przypisania (rozmiar pamięci TLB jest

ograniczony) uruchamiane są wolniejsze, sprzętowe mechanizmy procesora przeszukujące struktury danych

znajdujące się w pamięci, co wymaga niekiedy pomocy ze strony oprogramowania (systemu operacyjnego).

Pozycje w tych strukturach nazywają się wpisami (elementami) tablicy stron pamięci (PTEs - Page Table

Entries) a cała struktura nazywana jest tablicą stron pamięci (ang. Page Table). Kompletny adres w pamięci

fizycznej jest ustalany poprzez dodanie bitów przesunięcia (ang. offset) do przetłumaczonego numeru strony.

Wpisy w TLB lub PTE mogą także przechowywać informację o tym, czy dostęp do strony odbył się w trybie

zapisu (ang. dirty bit) czy w trybie odczytu (ang. accessed bit - bit pomocny algorytmom wymiatania

pamięci), bity uprawnień do operacji na stronie pamięci (prawa dla trybu nadzorcy lub trybu użytkownika)

lub informację o tym, czy strona może być przeniesiona do pamięci wymiany.

Jeżeli w strukturach TLB lub PTE nie znajduje się odpowiedni opis aktualnie wykorzystywanej logicznej

strony pamięci lub znajdujący się wpis zabrania dostępu w danym trybie, MMU sygnalizuje CPU wyjątek

związany z błędnym dostępem do strony pamięci, tzw. page fault. System operacyjny może wtedy podjąć

akcje związane z wyjątkiem, np. uzupełnić wpisy w tablicy stron lub w TLB, ew. przerwać proces, którego

działanie spowodowało wystąpienie wyjątku.

19 Co to jest segmentacja pamięci, jaka jest różnica przy stosowaniu rejestrów

segmentowanych i indeksowych, podać przykłady.

Segmentacja pamięci - jedna z metod ochrony pamięci, używana przy wielozadaniowości. Każdy proces

otrzymuje swój własny obszar pamięci, realizowany poprzez rejestry segmentowe.

Segmentacja pamięci polega na podzieleniu przez system operacyjny pamięci fizycznej na fragmenty o

określonym początku, rozmiarze, atrybutach i identyfikatorze. System tworzy takie segmenty na żądanie

aplikacji, przekazując jej jedynie identyfikatory nie pozwalające na odczytanie parametrów segmentów.

Programy odwołują się zatem do kolejnych komórek pamięci w ramach należących do nich segmentów, nie

wiedząc nic o tym, w jakie miejsca pamięci fizycznej trafiają ich odwołania. Procesy nie mają też prawa

„widzieć” segmentów należących do innych programów — w czasie przekazywania kontroli procesowi

system musi zablokować definicje segmentów należących do pozostałych procesów, przy każdym

przełączeniu blokując segmenty wyłączanego programu i na nowo uaktywniając segmenty programu

aktywowanego.

Segmenty mają swoje zalety. Największą jest prostota relokacji kodu i danych; ponieważ nie jest ważne

gdzie w pamięci fizycznej zakotwiczony jest segment, program może odwoływać się do kolejnych słów

pamięci w ramach segmentu zawsze licząc od zera do końca segmentu. Konieczne dodawanie adresów

realizuje sprzętowo układ zarządzający pamięcią.

Okazuje się jednak, że wady segmentacji przeważyły nad zaletami. Pierwsze implementacje segmentowanej

pamięci wirtualnej narzucały dość poważne ograniczenia na rozmiary segmentów, zmuszając programistów

do dzielenia kodu programów oraz bloków danych w sposób nienaturalny i utrudniając tworzenie naprawdę

dużych struktur danych. Nawet po zniesieniu tego ograniczenia okazało się, że nikt nie chce bawić się w

dzielenie programu na logiczne części, a normalną pracę systemu i programu można osiągnąć znacznie

prostszymi środkami.

Segmentacja jest rozwiązaniem bardzo eleganckim, lecz na tyle kłopotliwym, że obecnie praktycznie się jej

nie stosuje. W mikroprocesorach 80386 i wyżej nie można wyłączyć mechanizmu segmentacji. Aby

segmentację uczynić niewidoczną, Linux wykorzystuje jeden segment o adresie bazowym 0x0 i rozmiarze

4GB. W celu ochrony pamięci zamiast segmentacji stosuje się mechanizm stronicowania, który jest

niezależny od segmentacji.

7 Różnice pomiędzy architekturą harwardzką oraz von Neumana.

W zależności od typu struktury mapy pamięci wyróżniamy architektury: harwardzką, zmodyfikowaną

harwardzką i von-Neumanna. Mikrokontrolery w większości zbudowane są według architektury von-

Neumanna. Architektura ta zakłada, że podział przestrzeni adresowej na pamięć programu i pamięć danych

jest czysto umowny. Takie podejście charakteryzuje się prostotą i przejrzystością. Dodatkowo upraszcza się

proces pisania programów, gdyż dostęp do danych programu i do rozkazów odbywa się za pomocą tych

samych instrukcji i tych samych trybów adresowania. Architektura von-Neumanna posiada jednak wady,

takie jak spowolnienie wykonywania cyklu. Wada ta stała się przyczyną coraz częstszego wykorzystywania

architektury harwardzkiej przy budowie mikrokontrolerów. Architektura ta jest bardziej złożona, gdyż

wykorzystuje dwie szyny adresowe. Jedna dedykowana jest dla kodu programu, druga dla danych. Trzeci typ

architektury – zmodyfikowana architektura harwardzka jest rozwiązaniem pośrednim. Architektura ta

próbuje połączyć pozytywne cechy obu wcześniej wymienionych. Obszary pamięci RAM i ROM są

rozdzielone ale charakteryzują się taką samą długością słowa.

28 Podać tryby adresowania.

Przez tryby adresowania rozumie się sposób wskazywania na argumenty wykorzystywane w trakcie

wykonywania instrukcji. Standardowe mikrokontrolery wykorzystują kilka różnych sposobów adresowania.

Jednak ciągły rozwój techniki mikroprocesorowej powoduje wzbogacanie o nowe możliwości adresowania.

Nowe mikrokontrolery typu embedded posiadają tak rozbudowane możliwości adresowania jak procesory

stosowane we współczesnych komputerach.

Adresowanie implikowane dotyczy instrukcji jednobajtowych, dla których zarówno operand jak i miejsce

przeznaczenia są określone przez dany rozkaz. Ten tryb adresowania jest używany wyłącznie w odniesieniu

do wewnętrznych rejestrów mikrokontrolera, szczególnie w odniesieniu do akumulatora. Ze względu na

krótki format instrukcji tryb ten jest bardzo efektywny, a ograniczeniem jest tylko liczba dostępnych

rejestrów.

W adresowaniu natychmiastowym operand jest podany w sposób jawny w postaci kodu instrukcji. Ten tryb

może być zatem używany wyłącznie w odniesieniu do stałych. Instrukcje wykorzystujące ten tryb

adresowania zajmują w pamięci więcej miejsca i wykonują się wolniej niż instrukcje bazujące na

adresowaniu implikowanym.

Adresowanie bezpośrednie ma zastosowanie dla instrukcji wielobajtowych, w których po kodzie rozkazu

następuje adres argumentu umieszczonego w pamięci danych. Mikrokontrolery dopuszczają stosowanie tego

typu adresowania w ograniczonym zakresie do pamięci danych. Np. mikrokontroler serii 80C51 dopuszcza

adresowanie w tym trybie tylko pamięci w zakresie adresów od 0 do 255, natomiast mikrokontroler 16-

bitowy 80C51 XA tylko pierwsze 1kB pamięci danych.

Adresowanie indeksowe nie jest stosowane we wszystkich mikrokontrolerach. Nie występuje m. in. w

mikrokontrolerach serii x51. Adresowanie to polega na obliczaniu adresu przez sumowanie zawartości

specjalnie przeznaczonego do indeksowania rejestru, zwanego rejestrem indeksowym z adresem

bezpośrednim, zapisanym w instrukcji. Obliczony w ten sposób adres jest adresem efektywnym. Tryb ten

jest korzystny, gdy operujemy na blokach danych.

W adresowaniu pośrednim część instrukcji wskazuje na komórkę pamięci zawierającą adres efektywny.

Adresowanie względne służy natomiast do adresowania pamięci względem adresu aktualnie wykonywanej

instrukcji w pamięci programu. Adres ten jest przechowywany w specjalnie do tego przeznaczonym rejestrze

zwanym wskaźnikiem instrukcji (IP). Tryb ten jest wykorzystywany przez rozkazy skoku.

Dzisiaj mikrokontrolery opierają adresowanie na segmentacji pamięci. Segmentacja polega na podziale

przestrzeni adresowej na segmenty, które najczęściej mają rozmiar 64kB. W najprostszej wersji zakłada się

stałą liczbę segmentów i stałe ich umiejscowienie. Najbardziej zaawansowane rozwiązania bazują natomiast

na wykorzystaniu rejestrów segmentowych dzięki czemu można swobodnie definiować położenie

segmentów.

50 Co to jest WATCHDOG.

Licznik nadzorcy - czyli watchdog to blok funkcjonalny stosowany w mikrokontrolerach, które pracują przez

długi czas w systemach pozbawionych obsługi. Ich zadanie polega na bieżącym odliczaniu czasu i

oczekiwaniu na sygnały zerujące, które oznaczają że system działa poprawnie.

11 Co oznacza , że architektura jest zewnętrznie 16, a wewnętrznie 32 bitowa, podać zalety

i wady takich rozwiązań.

386 DX - pierwszy w pełni 32-bitowy procesor, pracował w trybie chronionym oraz mił dostęp do

pamięci powyżej 1 MB. Płyty główne pod niego wyposażone były w cache L2. Produkowały go

firmy Intel i AMD w wersjach 16, 20, 25, 33 ,40 MHz.

386 SX - młodszy brat 386 DX, początkowo był montowany na płytach AT jako upgrade.

Wewnętrznie 32-bitowy ale z 16-bitową szyną danych.

32 Co to jest pamięć CACHE, jaka jest zaleta stosowania tej pamięci w przypadku

bezpośredniego dostępu do pamięci.

Możliwe jest budowanie szybkich układów, ale stosunkowo drogich i o małej pojemności. Istnieją też duże

pamięci o małych kosztach w przeliczeniu na bajt, ale cechujące się mniejszą efektywnością w zakresie

czasu dostępu.

We współczesnych procesorach stosuje się rozwiązanie kompromisowe, polegające na zastosowaniu pamięci

wewnętrznej dwupoziomowej. Mikroprocesor wyposaża się we względnie dużą i wolniejszą pamięć główną,

oraz w mniejszą, ale szybszą pamięć podręczną cache. Takie rozwiązanie pozwala na korzystanie z pamięci

o dużej pojemności, jednocześnie możliwe jest umieszczenie najpotrzebniejszych danych, w szybkiej

pamięci podręcznej.

Sprzętowa pamięć podręczna (ang. Cache memory) jest pamięcią typu SRAM (Static Random Access

Memory). Układy tej pamięci są zbudowane z tranzystorów, które trwale przechowują zapisane dane.

Pamięć podręczna zawiera kopię części zawartości pamięci głównej. Gdy procesor zamierza odczytać słowo

z pamięci, najpierw następuje sprawdzenie, czy słowo to nie znajduje się w pamięci podręcznej. Jeśli tak, to

słowo to jest szybko dostarczane do procesora. Jeśli nie, to blok pamięci głównej RAM zawierający

określoną liczbę kolejnych słów jest wczytywany do pamięci podręcznej, a następnie potrzebne słowo

(zawarte w tym bloku) jest dostarczane do procesora. Następne odwołania do tego samego słowa i sąsiednich

zawartych w przepisanym bloku będą realizowane już znacznie szybciej.

Organizacja współpracy procesora z takimi pamięciami wymaga zastosowania dodatkowego układu -

kontrolera cache, który steruje tym procesem.

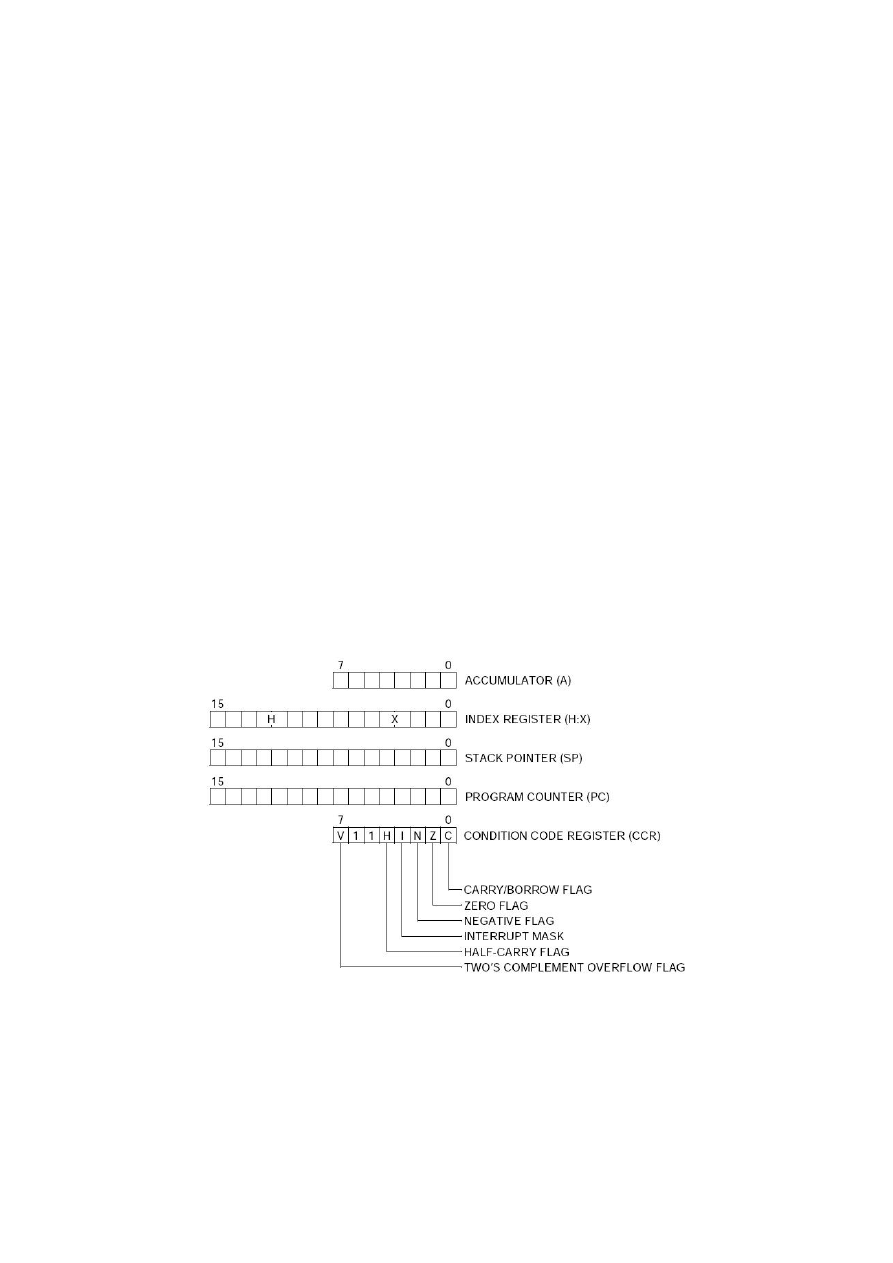

11 Opisać architekturę Motorola M68.

MC68HC08AZ60/48 –

2K RAM

60K FLASH

1K EEPROM

6-CH + 2-CH 16-Bit IC, OC, or PWM timer

48 I/O

SCI SPI serial

15-CH 8-Bit ADC

5.0 napięcie

8.0MHz max częstotliwość magistrali

Rejestry jednostki centralnej:

Wyszukiwarka

Podobne podstrony:

Nasze opracowanie pytań 1 40

Opracowanie pytań z anatomii

opracowanie pytań z optyki

Maszyny Elektryczne Opracowanie Pytań Na Egzamin

opracowanie pytan id 338374 Nieznany

opracowanie pytan karafiata

Opracowanie pytań 2 kolokwium

cw 3 broma opracowanie pytan 810

Nhip opracowanie pytan id 31802 Nieznany

filozofia opracowanie pytań

opracowanie pytan Automatyka

pytania egz ekonimak II, OPRACOWANIE PYTAŃ NA EGZAMIN

Zestaw 88 Kasia Goszczyńska, materiały farmacja, Materiały 3 rok, Od Ani, biochemia, biochemia, opra

opracowane zestawy, OPRACOWANIE PYTAŃ NA EGZAMIN

Opracowanie pytań MAMET METALE

egzamin z sorbentów opracowanie pytań 1 2 JM

więcej podobnych podstron