Politechnika Rzeszowska

Wydział Elektrotechniki i Informatyki

Zakład Systemów Rozproszonych

L a b o r a t o r i u m E L i A K

Ćwiczenie 4: Projektowanie i symulacja układów kombinacyjnych

Obowiązujące zagadnienia:

Realizacja funkcji logicznych za pomocą multiplekserów.

Dekodery, transkoder, enkodery.

Wyświetlacz siedmiosegmentowy.

Kody typu: NB, 1 z n, BCD, BCD+.

Układy generacji i kontroli bitu parzystości.

Komparatory równoległe.

Sumatory szeregowe oraz carry-look-ahead.

Realizacja tego ćwiczenia polega na wykonaniu tylko zadań wskazanych przez prowadzącego

1. Dokonać minimalizacji funkcji wykorzystując multipleksery o wskazanej liczbie wejść

adresowych:

a) F(A,B,C,D) = (1,3,7,10,11) - (4, 3, 2 wejścia);

b) G(A,B,C,D) = (0,2,4,8,9,10,14) - (4, 3, 2 wejścia);

c) X(A,B,C,D,E) = (1,3,7,10,11,14,15,20,21,27,28,29) - (4, 3, 2 wejścia);

d) Y(A,B,C,D,E) = (1,2,3,4,6,9,10,11,,14,18,19,20,22,27,28,29) - (4, 3 wejścia);

e) Z(A,B,C,D,E) = (0,1,2,3,6,7,8,9,20,21,22,23) - (4, 3 wejścia);

f) H(A,B,C,D) = (1,3,5,7,9,11) - (4, 3, 2 wejścia);

g) I(A,B,C,D) = (0,2,5,7,8,10,13,15) - (4, 3, 2 wejścia);

h) X(A,B,C,D,E) = (1,3,7,10,11,13,14,15,20,21,27,28,31) - (4, 3 wejścia);

i) Z(A,B,C,D,E) = (0,1,2,3,6,7,8,9,20,21,22,23) - (4, 3 wejścia);

2. Zaprojektować układ pozwalający na zamianę kodu BCD na kod BCD+3.

3. Zaprojektować dekodery wskazane przez prowadzącego:

a) BCD na 1 z 10, BCD+3 na 2 z 5;

b) BCD na 2 z 5, BCD+3 na 1 z 10;

c) NB na kod Gray’a; Gray’a na kod NB.

4. Zaprojektować koder kodu BCD (lub NB) na kod wyświetlacza siedmiosegmentowego. W celu

eliminacji problemu kombinacji sygnałów wejściowych odpowiadających liczbom 10 – 15 należy

przyjąć następujące rozwiązania:

a) wyświetlać E(rror)

b) wyświetlać

–

c) wyświetlać kody szesnastkowe, czyli odpowiednio A, b, C, d, E ,F

d) nie wyświetlać nic

5. Zaprojektować układ pozwalający na generowanie (i kontrolę) bitu parzystości dla danych

przesyłanych w kodzie 8421.

6. Zaprojektować układ komparatora równoległego pozwalający na porównywanie dwóch

czterobitowych liczb.

7. Zaprojektować układ sumatora szeregowego

VERTE

8. Zaprojektować układ sumatora carry-look-ahead.

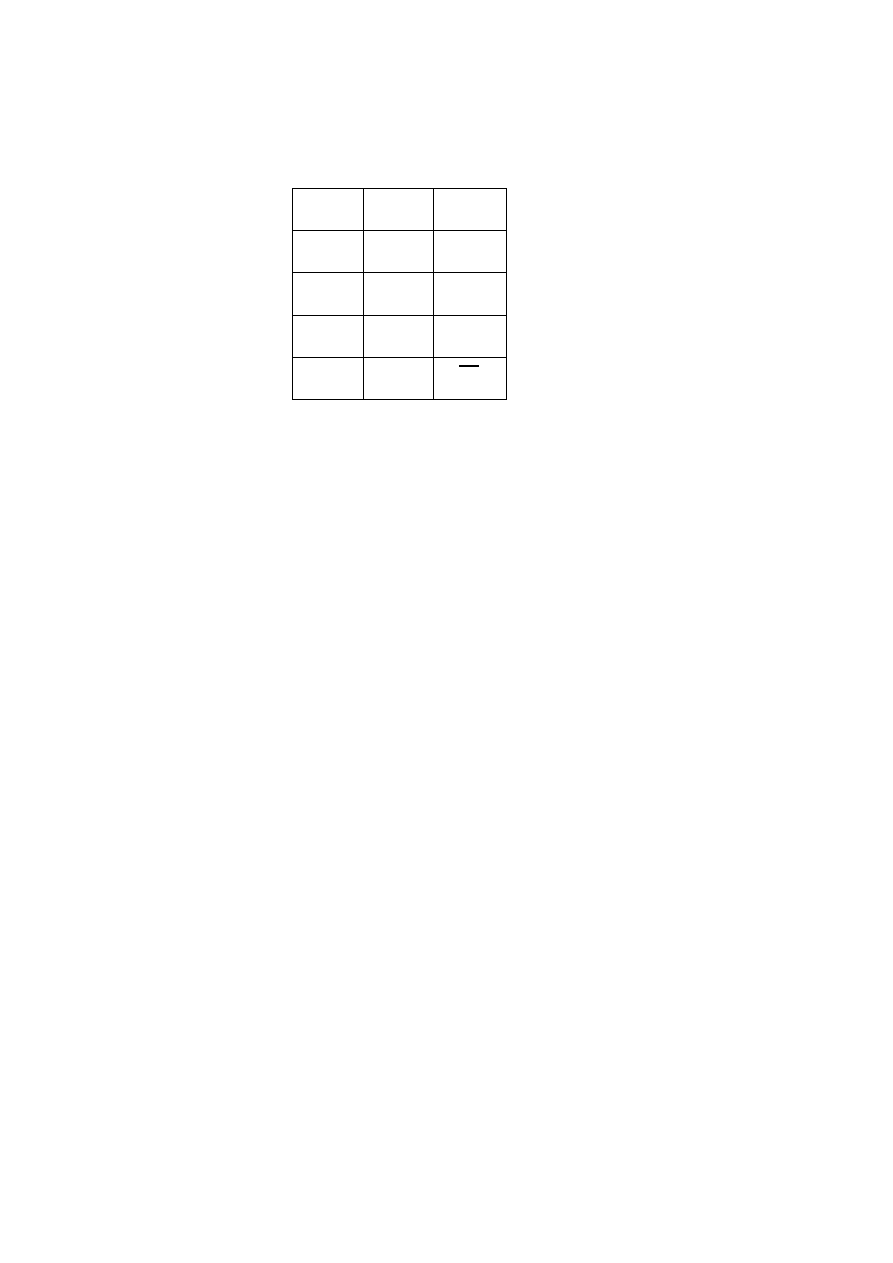

9. Zaprojektować układ posiadający dwa wejścia sterujące X i Y oraz cztery wejścia i wyjścia

informacyjne opisany następującą tablicą prawdy:

Projektowanie wszystkich w/w układów należy zrealizować w następujących etapach:

- tablice prawdy;

- minimalizacje;

- równania;

- projekty układów w postaci funktorów logicznych (schematy zrealizowane na bramkach);

- symulacje układów w programie MiltiSim.

Wejście

X

Wejście

Y

Wyjścia

wy

i

0

0

0

0

1

1

1

0

we

i

1

1

we

i

Wyszukiwarka

Podobne podstrony:

instrukcja cwiczenie 7

Instruktaz cwiczen domowych Sc,Thdex

instrukcja cwiczenie 6

LAB instrukcje, Ćwiczenie 13, Przebieg _wiczenia:

INSTRUKCJE Cwiczenie 1 id 71952 Nieznany

Zał 1 instrukcja cwiczenia

Instrukcja cwiczenia 9 id 21649 Nieznany

Analiza instrumentalna ćwiczenia, Zootechnika, Analiza instrumentalna

INSTRUKCJE Ćwiczenie 3

instrukcja cwiczenie 3

LAB instrukcje, Ćwiczenie 76, Ćwiczenie 76

LAB instrukcje, Ćwiczenie 15, Ćwiczenie 15

instrukcja 3, Ćwiczenia laboratoryjne z Podstaw Informatyki nr 3

iGrafx 2007 instrukcja ćwiczeńJG 2011

instrukcje ćwiczeń

Instrukcja ćwiczenie 1 elektroliza ver2

Laboratorium instrukcje ćwiczeń

więcej podobnych podstron